### WIND RIVER

Wind River®Workbench for On-Chip Debugging

**CONFIGURATION OPTIONS REFERENCE**

2.6.1

Copyright © 2007 Wind River Systems, Inc.

All rights reserved. No part of this publication may be reproduced or transmitted in any form or by any means without the prior written permission of Wind River Systems, Inc.

Wind River, the Wind River logo, Tornado, and VxWorks are registered trademarks of Wind River Systems, Inc. Any third-party trademarks referenced are the property of their respective owners. For further information regarding Wind River trademarks, please see:

http://www.windriver.com/company/terms/trademark.html

This product may include software licensed to Wind River by third parties. Relevant notices (if any) are provided in your product installation under the following directory: <code>installDirlproduct\_name/3rd\_party\_licensor\_notice.pdf</code>.

### **Corporate Headquarters**

Wind River Systems, Inc. 500 Wind River Way Alameda, CA 94501-1153 U.S.A.

toll free (U.S.): (800) 545-WIND telephone: (510) 748-4100 facsimile: (510) 749-2010

For additional contact information, please visit the Wind River URL:

http://www.windriver.com

For information on how to contact Customer Support, please visit the following URL:

http://www.windriver.com/support

Wind River Workbench for On-Chip Debugging Configuration Options Reference, 2.6.1

## Contents

| 1 | Intr | oduction                                    | 1  |

|---|------|---------------------------------------------|----|

|   | 1.1  | The CF Options View                         | 1  |

|   | 1.2  | Changing CF Options with Low-Level Commands | 3  |

|   | 1.3  | CF Options View Buttons                     | 4  |

|   | 1.4  | Other Resources                             | 4  |

| 2 | AMO  | CC 40x Processors                           | 5  |

|   |      | 403 Folding (FOLDING)                       | 5  |

|   |      | Check for Bus Error (BUSERRCHECK)           | 5  |

|   |      | Debug Mode (DEBUGMODE)                      | 6  |

|   |      | Delay After Reset N*1ms (DRST)              | 6  |

|   |      | Drive TReset Line (TRESET)                  | 6  |

|   |      | Emulator HALT Command Control (CMDRST)      | 7  |

|   |      | Except Handlers Available (HANDLERS)        | 7  |

|   |      | External Trigger In (TRGIN)                 | 7  |

|   |      | External Trigger In Mode (TRGINMODE)        | 8  |

|   |      | External Trigger Out (TRGOUT)               | 8  |

|   |      | FPU Available (FPU)                         | 9  |

|   |      | Flash Burst Mode (FLASHBURSTMODE)           | 9  |

|   |      | Instruction-side On-chip Memory (ISOCM)     | 9  |

|   |      | Issue an IN on Coldstart (INCOLD)           | 10 |

|   |      | JTAG Clock Rate (MHz) (CLK)                 | 10 |

|   |      | Little-endian Mode (LENDIAN)                | 10 |

|                       | Load Boot Table on IN (BL)                                      | 10             |

|-----------------------|-----------------------------------------------------------------|----------------|

|                       | Logic Analyzer Trace (LATRACE)                                  | 11             |

|                       | Memory Management Unit Mode (MMU)                               | 11             |

|                       | Monitor Target Reset (RST)                                      | 11             |

|                       | Real Time Preservation (RTP)                                    | 11             |

|                       | Reset Option (RESET)                                            | 12             |

|                       | Retry Establishing Connection on IN/INN (RETRYIN)               | 12             |

|                       | Set Breakpoint (SB)                                             | 12             |

|                       | Set SDRAM/SRAM Data Address Range (DATA)                        | 13             |

|                       | Set Stack Range (STACK)                                         | 13             |

|                       | Set Work Space (WSPACE)                                         | 13             |

|                       | Target Console Redirection (TGTCONS)                            | 14             |

|                       | Target CPU (TAR)                                                | 14             |

|                       | Timer Options (TIMERS)                                          | 15             |

|                       | Trap Exception (TRPEXP)                                         | 15             |

|                       | Trigger in Filter Mode (TRGINFILTER)                            | 15             |

|                       | Trigger Out Mode (TRGOUTMODE)                                   | 16             |

|                       | (USENVRAMFLASHVALUES)                                           | 16             |

|                       | Validate Memory Access (MEMCHECK)                               | 16             |

|                       | Vector Table Location (VECTOR)                                  | 16             |

| 2.1 CF O <sub>F</sub> | Acquire Trace on GO (TRCAQU)  Clear Trace Buffer on GO (TRCCLR) | 17<br>17<br>17 |

| AMCC 44x              | Processors                                                      | 19             |

|                       | Check for Bus Error (BUSERRCHECK)                               | 19             |

|                       | Debug Mode (DEBUGMODE)                                          | 19             |

|                       | Delay After Reset N*1ms (DRST)                                  | 20             |

|                       | Drive TReset Line (TRESET)                                      | 20             |

|                       | Emulator HALT Command Control (CMDRST)                          | 20             |

|                       | Except Handlers Available (HANDLERS)                            | 21             |

|                       | External Trigger In (TRGIN)                                     | 21             |

|                       | External Trigger In Mode (TRGINMODE)                            | 21             |

|                       | External Trigger Out (TRGOUT)                                   | 22             |

|                       | Flash Burst Mode (FLASHBURSTMODE)                               | 22             |

|                       | FPU Available (FPU)                                             | 22             |

|                       | Invalidate Instruction Cache on GO (INVICACHEONGO)              | 23             |

|                       | Invalidate Instruction Cache on Single Step (INVICACHEONSTEP)   | 23             |

|                       | Issue an IN on Coldstart (INCOLD)                               | 23             |

|                       | JTAG Clock Rate (MHz) (CLK)                                     | 23             |

|                       | Little-endian Mode (LENDIAN)                                    | 24             |

3

|   | Load Boot Table on IN (BL)                         |

|---|----------------------------------------------------|

|   | Logic Analyzer Trace (LATRACE)                     |

|   | Memory Management Unit Mode (MMU)                  |

|   | Monitor Target Reset (RST)                         |

|   | Real Time Preservation (RTP)                       |

|   | Reset Chip for CPC0_SYS0/1 Updates (UPDATESYSREGS) |

|   | Reset Configuration Word Location (RSTCONF)        |

|   | Reset Option (RESET)                               |

|   | Retry Establishing Connection on IN/INN (RETRYIN)  |

|   | Set Breakpoint (SB)                                |

|   | Set SDRAM/SRAM Data Address Range (DATA)           |

|   | Set Stack Range (STACK)                            |

|   | Set Work Space (WSPACE)                            |

|   | Target Console Redirection (TGTCONS)               |

|   | Target CPU (TAR)                                   |

|   | Timer Options (TIMERS)                             |

|   | Transparent Mode Driver (TMD)                      |

|   | Trap Exception (TRPEXP)                            |

|   | Trigger in Filter Mode (TRGINFILTER)               |

|   | Trigger Out Mode (TRGOUTMODE)                      |

|   | Use NVRAM Flash Values (USENVRAMFLASHVALUES)       |

|   | Validate Memory Access (MEMCHECK)                  |

|   | Vector Table Location (VECTOR)                     |

|   | 3.1 CF Options for Wind River Trace                |

|   | Acquire Trace on GO (TRCAQU)                       |

|   | Clear Trace Buffer on GO (TRCCLR)                  |

|   | Trace Output Source (TRCSRC) 32                    |

|   | nace output source (TRESRE)                        |

| 4 | PowerPC 5xx Processors                             |

|   | 29-31 Bits of ICTRL Register (ICTRLVAL)            |

|   | BDM Clock Rate (CLK)                               |

|   | Enable Target Machine Check (TRPMC)                |

|   | External Trigger In (TRGIN)                        |

|   | External Trigger Out (TRGOUT)                      |

|   | Logic Analyzer Trace (LATRACE)                     |

|   | Memory Management Unit (MMU)                       |

|   | Monitor Target Reset (RST)                         |

|   | Real Time Preservation (RTP)                       |

|   | Set Breakpoint (SB)                                |

|   | Set Work Space (WSPACE)                            |

|   | Software Breakpoint Emulation Method (SBE)         |

|   |                                                    |

|   | Target Console Redirection (TGTCONS)        |

|---|---------------------------------------------|

|   | Target CPU (TAR)                            |

|   | Trap Exception (TRPEXP)                     |

|   | Trigger in Filter Mode (TRGINFILTER)        |

|   | Trigger In Report Mode (BRKREP)             |

|   | Trigger Out Mode (TRGOUTMODE)               |

|   | Vector Table Location (VECTOR)              |

|   | Wait to Enter Background Mode N*100ms (FRZ) |

|   |                                             |

| 5 | PowerPC 5xxx Processors41                   |

|   | CPU Reset Type (RESET) 4                    |

|   | Delay After Reset N*1ms (DRST) 4            |

|   | Display L2 Data Cache Warning (L2WARNING)   |

|   | Download Mode (DLD)                         |

|   | Drive TReset Line (TRESET)                  |

|   | Emulator HRESET Control (HRESET)            |

|   | Emulator HRESET Command Control (CMDRST) 42 |

|   | Enable Checkstop Interrupt (CHECKSTOP)      |

|   | External Trigger In (TRGIN)                 |

|   | External Trigger Out (TRGOUT) 4.            |

|   | Invalidate Instruction Cache on GO (INVCI)  |

|   | Issue an IN on Coldstart (INCOLD)           |

|   | JTAG Clock Rate (MHz) (CLK)                 |

|   | Load Boot Table on IN (BL)                  |

|   | Little-endian Mode (LENDIAN) 45             |

|   |                                             |

|   |                                             |

|   | • • • • • • • • • • • • • • • • • • • •     |

|   | Monitor Target Reset (RST)                  |

|   |                                             |

|   |                                             |

|   | Real Time Preservation (RTP)                |

|   |                                             |

|   |                                             |

|   | 1 ' '                                       |

|   | <b>1</b>                                    |

|   | Target CPU (TAR)                            |

|   | Target Console Redirection (TGTCONS)        |

|   | Trap Exception (TRPEXP) 49                  |

|   | Trigger In Mode (TRGINMODE)                 |

|   | Trigger in Filter Mode (TRGINFILTER)        |

|   | Trigger In Report Mode (BRKREP)             |

|   | Trigger Out Mode (TRGOUTMODE)50             |

|   | Vector Table Location (VECTOR)           |

|---|------------------------------------------|

| 6 | PowerPC 55xx Processors 55               |

|   | CPU Reset Type (RESET)5                  |

|   | Delay After Reset N*1ms (DRST)           |

|   | Download Mode (DLD)                      |

|   | Drive TReset Line (TRESET)               |

|   | Emulator HRESET Command Control (CMDRST) |

|   | Emulator HRESET Control (HRESET)         |

|   | Enable Checkstop Interrupt (CHECKSTOP)   |

|   | External Trigger In (TRGIN)              |

|   | External Trigger Out (TRGOUT)            |

|   | Issue an IN on Coldstart (INCOLD)        |

|   | JTAG Clock Rate (MHz) (CLK)5             |

|   | Little-endian Mode (LENDIAN)5            |

|   | Load Boot Table on IN (BL)               |

|   | MMU Support Control (MMU)5               |

|   | Monitor Target Reset (RST)               |

|   | Power On Reset Length N*1ms (PONR)5      |

|   | Real Time Preservation (RTP)             |

|   | Reset Pulse Length N*1ms (RPL)           |

|   | Sense Power via HRESET (SPOWER)5         |

|   | Set Breakpoint (SB)5                     |

|   | Set Work Space (WSPACE)5                 |

|   | Target CPU (TAR)                         |

|   | Target Console Redirection (TGTCONS)     |

|   | TMD Mode (TMD)                           |

|   | Trap Exception (TRPEXP)6                 |

|   | Trigger in Filter Mode (TRGINFILTER)     |

|   | TTrigger Out Mode (TRGOUTMODE)           |

| 7 | PowerPC 6xx Processors                   |

|   | CPU Reset Type (RESET)6                  |

|   | Data Parity Checking (PAR)               |

|   | Delay After Reset (DRST)                 |

|   | Download Mode (DLD)6                     |

|   | Drive TReset Line (TRESET)               |

|   | Emulator HRESET Command Control (CMDRST) |

|   | Emulator HRESET Control (HRESET)         |

|   | External Trigger In (TRGIN)              |

|   | External Trigger Out (TRGOUT)            |

|   | Invalidate Instruction Cache on GO (INVCI) |

|---|--------------------------------------------|

|   | Issue an IN on Cold Start (INCOLD)         |

|   | JTAG Clock Rate (MHz) (CLK)6               |

|   | Little-endian Mode (LENDIAN)               |

|   | Load Boot Table on IN (BL)                 |

|   | Logic Analyzer Trace (LATRACE)             |

|   | Memory Management Unit Mode (MMU)          |

|   | Monitor Target Reset (RST)                 |

|   | Power On Reset Length N*1ms (PONR)         |

|   | Processor Mode (MODE)                      |

|   | Real Time Preservation (RTP)               |

|   | Reset Pulse Length (RPL)                   |

|   | Sense Power via HRESET (SPOWER)            |

|   | Set Breakpoint (SB)                        |

|   | Set Stack Range (STACK)                    |

|   | Set Work Space (WSPACE)                    |

|   | Target Console Redirection (TGTCONS)       |

|   | Target CPU (TAR)                           |

|   | TMD Mode (TMD)                             |

|   | Trap Exception (TRPEXP)                    |

|   | Trigger in Filter Mode (TRGINFILTER)       |

|   | Trigger In Report Mode (BRKREP)            |

|   | Trigger Out Mode (TRGOUTMODE)              |

|   | Vector Table Location VECTOR)              |

|   | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,    |

|   | DD0 7 D                                    |

| 8 | PowerPC 7xx Processors                     |

|   | Application IMMR Exclusion Range (AIMMRER) |

|   | Application IMMR Value (AIMMRVAL)          |

|   | CPU Reset Type (RESET)                     |

|   | Data Parity Checking (PAR)                 |

|   | Delay After Reset N*1ms (DRST)             |

|   | Display L2 Data Cache Warning (L2WARNING)  |

|   | Download Mode (DLD)                        |

|   | Drive TReset Line (TFRESET)                |

|   | Emulator HRESET Command Control (CMDRST)   |

|   | Emulator HRESET Control (HRESET)           |

|   | External Trigger In (TRGIN)                |

|   | External Trigger Out (TRGOUT)              |

|   | Invalidate Instruction Cache on GO (INVCI) |

|   | Issue an IN on Coldstart (INCOLD)          |

|   | JTAG Clock Rate (MHz) (CLK)                |

|   | Load Boot Table on IN (BL)                 |

|   | Load boot lable off in (bL)                |

|   | Little-endian Mode (LENDIAN)               |

|---|--------------------------------------------|

|   | Logic Analyzer Trace (LATRACE)             |

|   | Memory Management Unit Mode (MMU)          |

|   | Monitor Target Reset (RST)                 |

|   | Power On Reset Length N*1ms (PONR)         |

|   | Processor Mode (MODE)                      |

|   | Real Time Preservation (RTP)               |

|   | Reset Pulse Length N*1ms (RPL)             |

|   | Run Counter Length (RCL) 80                |

|   | Sense Power via HRESET (SPOWER)            |

|   | Set Breakpoint (SB)80                      |

|   | Set Stack Range (STACK)                    |

|   | Set Work Space (WSPACE)8                   |

|   | Slave IMMR Reset Value (SLIMMRVAL)         |

|   | Target CPU (TAR)82                         |

|   | Target CPU (Slave) (SLAVE)                 |

|   | Target Console Redirection (TGTCONS)       |

|   | TMD Mode (TMD)                             |

|   | Trap Exception (TRPEXP)                    |

|   | Trigger in Filter Mode (TRGINFILTER)       |

|   | Trigger In Report Mode (BRKREP)            |

|   | Trigger Out Mode (TRGOUTMODE)              |

|   | Vector Table Location (VECTOR)             |

|   |                                            |

| _ | Dawar DO 74 Duananana                      |

| 9 | PowerPC 74xx Processors 87                 |

|   | Application IMMR Exclusion Range (AIMMRER) |

|   | Application IMMR Value (AIMMRVAL)          |

|   | CPU Reset Type (RESET)88                   |

|   | Data Parity Checking (PAR)                 |

|   | Delay After Reset N*1ms (DRST)             |

|   | Display L2 Data Cache Warning (L2WARNING)  |

|   | Download Mode (DLD)                        |

|   | Drive TReset Line (TRESET)                 |

|   | Emulator HRESET Command Control (CMDRST)   |

|   | Emulator HRESET Control (HRESET)           |

|   | External Trigger In (TRGIN)                |

|   | External Trigger Out (TRGOUT)              |

|   | Invalidate Instruction Cache on GO (INVCI) |

|   | Issue an IN on Cold Start (INCOLD)         |

|   | JTAG Clock Rate (MHz) (CLK)                |

|   | Little-endian Mode (LENDIAN)               |

|   | Load Boot Table on IN (BL)                 |

|   |                                            |

|    | Logic Analyzer Trace (LATRACE)        | 92 |

|----|---------------------------------------|----|

|    |                                       | 92 |

|    |                                       | 93 |

|    |                                       | 93 |

|    |                                       | 93 |

|    |                                       | 93 |

|    |                                       | 94 |

|    |                                       | 94 |

|    |                                       | 94 |

|    |                                       | 94 |

|    |                                       | 95 |

|    |                                       | 95 |

|    |                                       | 95 |

|    |                                       | 95 |

|    |                                       | 96 |

|    |                                       | 96 |

|    |                                       | 96 |

|    |                                       | 97 |

|    |                                       | 97 |

|    |                                       | 98 |

|    |                                       | 98 |

|    |                                       | 98 |

|    | · · · · · · · · · · · · · · · · · · · | 98 |

|    | • • • • • • • • • • • • • • • • • • • | 99 |

|    |                                       | 99 |

| 10 | PowerPC 8xx Processors                | )1 |

|    |                                       |    |

|    | 0 \                                   | 01 |

|    |                                       | 01 |

|    |                                       | 02 |

|    | External Trigger In (TRGIN)           |    |

|    | , , , , , , , , , , , , , , , , , , , | 02 |

|    | Logic Analyzer Trace (LATRACE)        |    |

|    |                                       | 03 |

|    | 0 \ /                                 | 03 |

|    |                                       | 04 |

|    | 1 ' '                                 | 04 |

|    | 1 ' '                                 | 04 |

|    | 1                                     | 05 |

|    |                                       | 05 |

|    | ·                                     | 05 |

|    | Target CPU (TAR) 10                   | 06 |

|    | 0                                     |    |

|    | Trap Exception (TRPEXP)                       | 106        |

|----|-----------------------------------------------|------------|

|    | Trigger in Filter Mode (TRGINFILTER)          | 107        |

|    | Trigger In Report Mode (BRKREP)               | 107        |

|    | Trigger Out Mode (TRGOUTMODE)                 | 107        |

|    | Vector Table Location (VECTOR)                | 107        |

|    | Wait to Enter Background Mode N*100ms (FRZ)   | 107        |

| 11 | PowerPC 82xx Processors                       | 100        |

| •• |                                               |            |

|    | Application IMMR Exclusion Range (AIMMRER)    | 109        |

|    | Application IMMR Value (AIMMRVAL)             | 109        |

|    | CPU Reset Type (RESET)                        | 110        |

|    | CPU Type (TAR)                                | 110        |

|    | Delay After Reset N*1ms (DRST)                | 110        |

|    | Download Mode (DLD)                           | 110        |

|    | Drive TReset Line (TRESET)                    | 111        |

|    | Emulator HRESET Command Control (CMDRST)      | 111        |

|    | Emulator HRESET Control (HRESET)              | 111        |

|    | Enable Checkstop Interrupt (CHECKSTOP)        | 112        |

|    | External Trigger In (TRGIN)                   | 112        |

|    | External Trigger Out (TRGOUT)                 | 113        |

|    | IMMR Base Address Location At Reset (RSTIMMR) | 113        |

|    | Invalidate Instruction Cache on GO (INVCI)    | 113        |

|    | Issue an IN on Coldstart (INCOLD)             | 114        |

|    | JTAG Clock Rate (MHz) (CLK)                   | 114        |

|    | Little-endian Mode (LENDIAN)                  | 114        |

|    | Load Boot Table on IN (BL)                    | 114        |

|    | Logic Analyzer Clocking Type (CLKTYPE)        | 115        |

|    | Logic Analyzer Trace (LATRACE)                | 115        |

|    | Memory Management Unit Mode (MMU)             | 115        |

|    | Monitor Target Reset (RST)                    | 115        |

|    | Power On Reset Length N*1ms (PONR)            | 116        |

|    | Processor Mode (MODE)                         | 116        |

|    | Real Time Preservation (RTP)                  | 116        |

|    | Reset Configuration Word Location (RSTCONF)   | 116        |

|    | Reset Pulse Length N*1ms (RPL)                | 117        |

|    | Sense Power via HRESET (SPOWER)               | 117        |

|    | Set Godo Pango (CP)                           | 117        |

|    | Set Code Range (CR)                           | 117        |

|    | Set Work Space (MSDACE)                       | 118        |

|    | Set Work Space (WSPACE)                       | 118        |

|    | Target Console Redirection (TGTCONS)          | 118<br>119 |

|    | Target Console Redirection (1C-1CONS)         | 119        |

|    | TMD Mode (TMD)                                | 119 |

|----|-----------------------------------------------|-----|

|    | Trap Exception (TRPEXP)                       | 119 |

|    | Trigger in Filter Mode (TRGINFILTER)          | 120 |

|    | Trigger In Report Mode (BRKREP)               | 120 |

|    | Trigger Out Mode (TRGOUTMODE)                 | 120 |

|    | Vector Table Location (VECTOR)                | 121 |

|    |                                               |     |

| 12 | PowerPC 83xx Processors                       | 123 |

|    | Application IMMR Exclusion Range (AIMMRER)    | 123 |

|    | Application IMMR Value (AIMMRVAL)             | 124 |

|    | Configure Reset Configuration Word (RCW)      | 124 |

|    | CPU Reset Type (RESET)                        | 124 |

|    | CPU Type (TAR)                                | 125 |

|    | Delay After Reset N*1ms (DRST)                | 125 |

|    | Download Mode (DLD)                           | 125 |

|    | Drive TReset Line (TRESET)                    | 125 |

|    | Emulator HRESET Command Control (CMDRST)      | 126 |

|    | Emulator HRESET Control (HRESET)              | 126 |

|    | Enable CheckStop Interrupt (CHECKSTOP)        | 126 |

|    | External Trigger In (TRGIN)                   | 127 |

|    | External Trigger Out (TRGOUT)                 | 127 |

|    | IMMR Base Address Location At Reset (RSTIMMR) | 128 |

|    | Invalidate Instruction Cache on GO (INVCI)    | 128 |

|    | Issue an IN on Coldstart (INCOLD)             | 128 |

|    | JTAG Clock Rate (MHz) (CLK)                   | 129 |

|    | Little-endian Mode (LENDIAN)                  | 129 |

|    | Load Boot Table on IN (BL)                    | 129 |

|    | Memory Management Unit Mode (MMU)             | 129 |

|    | Monitor Target Reset (RST)                    | 129 |

|    | Power On Reset Length N*1ms (PONR)            | 130 |

|    | Processor Mode (MODE)                         | 130 |

|    | Real Time Preservation (RTP)                  | 130 |

|    | Reset Configuration Word Location (RSTCONF)   | 130 |

|    | Reset Pulse Length N*1ms (RPL)                | 131 |

|    | Sense Power via HRESET (SPOWER)               | 131 |

|    | Set Breakpoint (SB)                           | 131 |

|    | Set Work Space (WSPACE)                       | 131 |

|    | Target Console Redirection (TGTCONS)          | 132 |

|    | TMD Mode (TMD)                                | 132 |

|    | Trap Exception (TRPEXP)                       | 133 |

|    | Trigger in Filter Mode (TRGINFILTER)          | 133 |

|    | Trigger In Report Mode (BRKREP)               | 133 |

|    | Trigger Out Mode (TRGOUTMODE)               | 134 |

|----|---------------------------------------------|-----|

|    | Vector Table Location (VECTOR)              |     |

|    |                                             |     |

| 13 | PowerPC 85xx Processors                     | 135 |

|    | Acquire Trace on GO (TRCAQU)                | 135 |

|    | Clear Trace Buffer on GO (TRCCLR)           |     |

|    | CPU Reset Type (RESET)                      |     |

|    | Delay After Reset N*1ms (DRST)              |     |

|    | Download Mode (DLD)                         |     |

|    | Drive TReset Line (TRESET)                  |     |

|    | Emulator HRESET Command Control (CMDRST)    |     |

|    | Emulator HRESET Control (HRESET)            |     |

|    | Enable Checkstop Interrupt (CHECKSTOP)      | 138 |

|    | Exception Taken Mask Value (ETM)            | 138 |

|    | Execute PowerOnReset ABIST Test (PORABIST)  |     |

|    | External Trigger In (TRGIN)                 | 138 |

|    | External Trigger Out (TRGOUT)               | 139 |

|    | Flush Data Cache on Read (FLUSH_DCACHE)     |     |

|    | Issue an IN on Coldstart (INCOLD)           |     |

|    | JTAG Clock Rate (MHz) (CLK)                 | 140 |

|    | L2 TLB Base Address for INN (L2TLB)         | 141 |

|    | Little-endian Mode (LENDIAN)                | 141 |

|    | Load Boot Table on IN (BL)                  | 141 |

|    | Local Bus Clock Frequency > 133 MHz (LBCLK) | 141 |

|    | MMU Support Control (MMU)                   | 141 |

|    | Monitor Target Reset (RST)                  | 142 |

|    | Override Boot Mode (BOOTMODE)               | 142 |

|    | Override DDR DLL (DDR DLL)                  | 143 |

|    | Power On Reset Length N*1ms (PONR)          |     |

|    | Real Time Preservation (RTP)                |     |

|    | Reset Pulse Length N 1*ms (RPL)             | 143 |

|    | Sense Power via HRESET (SPOWER)             | 143 |

|    | Set Breakpoint (SB)                         | 144 |

|    | Set Work Space (WSPACE)                     |     |

|    | Target Console Redirection (TGTCONS)        | 145 |

|    | Target CPU (TAR)                            |     |

|    | TMD Mode (TMD)                              | 146 |

|    | Trap Exception (TRPEXP)                     | 146 |

|    | Trigger in Filter Mode (TRGINFILTER)        | 146 |

|    | Trigger In Report Mode (BRKREP)             |     |

|    | Trigger Out Mode (TRGOUTMODE)               |     |

| 14 | PowerPC 86xx Processors 149                               |

|----|-----------------------------------------------------------|

|    | Acquire Trace on GO (TRCAQU) 14                           |

|    | Clear Trace Buffer on GO (TRCCLR)                         |

|    | CPU Reset Type (RESET)                                    |

|    | Delay After Reset N*1ms (DRST)                            |

|    | Download Mode (DLD)                                       |

|    | Drive TReset Line (TRESET)                                |

|    | Emulator HRESET Command Control (CMDRST)                  |

|    | Emulator HRESET Control (HRESET)                          |

|    | Enable Checkstop Interrupt (CHECKSTOP)                    |

|    | Exception Taken Mask Value (ETM)                          |

|    | Execute PowerOnReset ABIST Test (PORABIST) 15.            |

|    | External Trigger In (TRGIN)                               |

|    | External Trigger Out (TRGOUT)                             |

|    | Flush Data Cache on Read (FLUSH_DCACHE) 15                |

|    | Issue an IN on Coldstart (INCOLD)                         |

|    | JTAG Clock Rate (MHz) (CLK)                               |

|    | L2 TLB Base Address for INN (L2TLB)                       |

|    | Little-endian Mode (LENDIAN)                              |

|    | Load Boot Table on IN (BL)                                |

|    | Local Bus Clock Frequency > 133 MHz (LBCLK)               |

|    | MMU Support Control (MMU)                                 |

|    | Monitor Target Reset (RST)                                |

|    | Override Boot Mode (BOOTMODE)                             |

|    | Override DDR DLL (DDR DLL)                                |

|    | Power On Reset Length N*1ms (PONR)                        |

|    | Real Time Preservation (RTP)                              |

|    | Reset Pulse Length N 1*ms (RPL)                           |

|    | Sense Power via HRESET (SPOWER)                           |

|    | Set Breakpoint (SB)                                       |

|    | Set Work Space (WSPACE)                                   |

|    | Target Console Redirection (TGTCONS)                      |

|    | Target CPU (TAR)       15         TMD Mode (TMD)       16 |

|    | Trap Exception (TRPEXP)                                   |

|    | Trigger in Filter Mode (TRGINFILTER)                      |

|    | Trigger In Report Mode (BRKREP)                           |

|    | Trigger Out Mode (TRGOUTMODE)                             |

|    | ingger out wode (1Root 1910bl)                            |

| 15 | ColdFire Processors                                       |

|    | BDM Clock Rate (CLK)                                      |

|    | Length of Reset Pulse N x 10ms (PLS)                      |

|    | Length of Reset Labert A Tollo (LES)                      |

|        | Load PC and A7 Registers on IN or INN Command (LOAD_PC_A7 | )                 |

|--------|-----------------------------------------------------------|-------------------|

|        | 164                                                       |                   |

|        | Mask Interrupts While Stepping (SIL)                      | 164               |

|        | Monitor Target Reset (RST)                                | 164               |

|        | Preserve Registers on INN Command (PRINN)                 | 165               |

|        | PST Signals Available (PST)                               | 166               |

|        | Real Time Preservation (RTP)                              | 166               |

|        | Remap Software Breakpoint (SB)                            | 167               |

|        | Set VBR (SET_VBR)                                         | 168               |

|        | Set Work Space (WSPACE)                                   | 168               |

|        | Step Over ISR (SOI)                                       | 169               |

|        | Target Console Redirection (TGTCONS)                      | 169               |

|        | Target CPU (TAR)                                          | 170               |

|        | Wait to Enter Background Mode (FRZ)                       | 170               |

| 15.1   | CF Options for Wind River Trace                           | <b>171</b>        |

|        | Acquire Trace on GO (TRCAQU)                              | 171               |

|        | Clear Trace Buffer on GO (TRCCLR)                         | 171               |

|        | Code Range (CR)                                           | 171               |

|        | Emit Operands on DDATA Pins (TRCREPORT)                   | 172               |

| l6 ARM | l Processors                                              | 173               |

|        | Cache Configuration File Name (CACHECONF)                 | 173               |

|        | Drive TReset Line (TRESET)                                | 173               |

|        | Emulator HRESET Command Control (CMDRST)                  | 174               |

|        | Emulator HRESET Control (HRESET)                          | 174               |

|        | External Trigger In (TRGIN)                               | 174               |

|        | External Trigger Out (TRGOUT)                             | 175               |

|        | Invalidate Instruction Cache on GO (INVCI)                | 175               |

|        | JTAG Clock Rate (MHz) (CLK)                               | 176               |

|        | Little-endian Mode (LENDIAN)                              | 176               |

|        | Monitor Target Reset (RST)                                | 176               |

|        | Project Register Configuration File Name (REGFILE)        | 176               |

|        | Real Time Preservation (RTP)                              | 177               |

|        | Reset and TRST Tied Together (TIED)                       | 177               |

|        | Reset Pulse Length N*1ms (RPL)                            | 177               |

|        | Set Breakpoint (SB)                                       | 177               |

|        | Set WRS Work Space (WSPACE)                               | 178               |

|        |                                                           | 170               |

|        | Target Console Redirection (TGTCONS)                      | 178               |

|        | Target Console Redirection (TGTCONS)                      |                   |

|        | Target Console Redirection (TGTCONS)                      | 178<br>179<br>179 |

|    | Trigger In Filter (TRGINFILTER)                     | 180   |

|----|-----------------------------------------------------|-------|

|    | Trigger Out Mode (TRGOUTMODE)                       | 180   |

|    | Wait to Enter Background Mode N*1ms (FRZ)           |       |

| 17 | ARMX (XScale) Processors                            | . 181 |

|    | Cache Configuration File Name (CACHEFILE)           | 181   |

|    | Catch Vector Update Breakpoint (0x1234) (CATCHBKPT) |       |

|    | Disable OS Timers on Breakpoint Entry (TCTRL)       |       |

|    | Drive TReset Line (TRESET)                          |       |

|    | Emulator HRESET Control (HRESET)                    |       |

|    | External Trigger In (TRGIN)                         |       |

|    | External Trigger Out (TRGOUT)                       |       |

|    | Invalidate Instruction Cache on GO (INVCI)          |       |

|    | Internally Trap All Exceptions (INTRAP)             | 184   |

|    | JTAG Clock Rate (MHz) (CLK)                         | 184   |

|    | Little-endian Mode (LENDIAN)                        | 184   |

|    | Monitor Target Reset (RST)                          | 184   |

|    | Preserve PCI Bridge Setup Across Reset (BRIDGE)     | 185   |

|    | Project Register Configuration File Name (REGFILE)  | 185   |

|    | RAM Size to Scrub (SCRUB)                           |       |

|    | Real Time Preservation (RTP)                        | 186   |

|    | Set Breakpoint (SB)                                 |       |

|    | Set Debug Handler Virtual Address (DHVA)            |       |

|    | Set Stack Range (STACK)                             |       |

|    | Set WRS Work Space (WSPACE)                         |       |

|    | Software Trace Mode (TRACE)                         |       |

|    | Target Console Redirection (TGTCONS)                |       |

|    | Target CPU (TAR)                                    |       |

|    | Transparent Mode Driver (TMD)                       |       |

|    | Trap Exceptions (TRPEXP)                            |       |

|    | Trigger In Filter (TRGINFILTER)                     |       |

|    | Trigger In Mode (TRGINMODE)                         |       |

|    | Trigger Out Mode (TRGOUTMODE)                       |       |

|    | Wait to Enter Background Mode N*100ms (FRZ)         |       |

|    | Wait to Release HOLD_RST Bit N*1000ms (HOLD_RST)    | 190   |

| 18 | MIPS32 Processors                                   | . 191 |

|    | BDM Clock Rate (CLK)                                | 191   |

|    | Check ROCC Bit During Reset (ROCC)                  |       |

|    | Delay After Reset (DRST)                            | 192   |

|    | Download Mode (DLD)                                 | 192   |

|    | Drive TReset Line (TRESET)                             | 192 |

|----|--------------------------------------------------------|-----|

|    | EJTAG Handshaking During Download (DLDHSHG)            | 192 |

|    | Emulator ECR Reset Control (ECRRST)                    | 193 |

|    | Emulator HRESET Command Control (CMDRST)               | 193 |

|    | Emulator HRESET Control (HRESET)                       | 193 |

|    | Exception Vector Table Location (VECTOR)               | 194 |

|    | External Trigger In (TRGIN)                            | 194 |

|    | External Trigger Out (TRGOUT)                          | 195 |

|    | Idle Time Between Processor Accesses (N*32 tck) (ITPA) | 195 |

|    | Invalidate Cache When Initialize (INVCA)               | 195 |

|    | Little-endian Mode (LENDIAN)                           | 196 |

|    | Load Boot Table on IN (BL)                             | 196 |

|    | Memory Management Unit (MMU)                           | 196 |

|    | Monitor Target Reset (RST)                             | 196 |

|    | Processor Mode (MODE)                                  | 197 |

|    | Reset Pulse Length N*1ms (RPL)                         | 197 |

|    | Set Breakpoint (SB)                                    | 197 |

|    | Set Stack Range (STACK)                                | 197 |

|    | Set Work Space (WSPACE)                                | 198 |

|    | Step in Delayed Slot (SIDS)                            | 198 |

|    | Target Break Type (TGTBRK)                             | 198 |

|    | Target Console Redirection (TGTCONS)                   | 199 |

|    | Target CPU (TAR)                                       | 199 |

|    | Transparent Mode Driver (TMD)                          | 200 |

|    | Trap Debug Exception (TRPEXP)                          | 200 |

|    | Trigger In Filter Mode (TRGINFILTER)                   | 200 |

|    | Trigger Out Mode (TRGOUTMODE)                          | 200 |

|    | Use Current MMU Settings (USEERL)                      | 201 |

|    |                                                        |     |

| 19 | MIPS64 Processors                                      | 203 |

|    | BDM Clock Rate (CLK)                                   | 203 |

|    | Check ROCC Bit During Reset (ROCC)                     | 203 |

|    | Delay After Reset (DRST)                               | 204 |

|    | Download Mode (DLD)                                    | 204 |

|    | Drive TReset Line (TRESET)                             | 204 |

|    | Emulator HRESET Command Control (CMDRST)               | 204 |

|    | Emulator HRESET Control (HRESET)                       | 205 |

|    | Exception Vector Table Location (VECTOR)               | 205 |

|    | External Trigger In (TRGIN)                            | 205 |

|    | External Trigger Out (TRGOUT)                          | 206 |

|    | Invalidate Cache When Initialize (INVCA)               | 207 |

|    | Little-endian Mode (LENDIAN)                           | 207 |

|    |                                                        |     |

|    | Load Boot Table on IN (BL)                  | 207 |

|----|---------------------------------------------|-----|

|    | Memory Management Unit (MMU)                | 207 |

|    | Monitor Target Reset (RST)                  | 207 |

|    | Reset Pulse Length N*1ms (RPL)              | 208 |

|    | Set Breakpoint (SB)                         | 208 |

|    | Set Stack Range (STACK)                     | 208 |

|    | Set Work Space (WSPACE)                     | 209 |

|    | Step in Delayed Slot (SIDS)                 | 209 |

|    | Target Break Type (TGTBRK)                  | 209 |

|    | Target Console Redirection (TGTCONS)        | 210 |

|    | Target CPU (TAR)                            | 210 |

|    | Transparent Mode Driver (TMD)               | 211 |

|    | Trap Debug Exception (TRPEXP)               | 211 |

|    | Trigger In Filter Mode (TRGINFILTER)        | 211 |

|    | Trigger Out Mode (TRGOUTMODE)               | 211 |

|    | Use Current MMU Settings (USEERL)           | 212 |

| 20 | PWRficient Processors                       | 213 |

|    | Acquire Trace on GO (TRCAQU)                | 213 |

|    | Delay After Reset N*1ms (DRST)              | 214 |

|    | Drive TReset Line (TRESET)                  | 214 |

|    | Emulator HRESET Command Control (CMDRST)    | 214 |

|    | Emulator HRESET Control (HRESET)            | 215 |

|    | Enable Physical Memory Access (MEMPHYSICAL) | 215 |

|    | Enable MBIST FPU Access (MBISTFPU)          | 215 |

|    | External Trigger In (TRGIN)                 | 215 |

|    | External Trigger Out (TRGOUT)               | 216 |

|    | Invalidate Cache When Initialize (INVCA)    | 217 |

|    | Issue an IN on Coldstart (INCOLD)           | 217 |

|    | JTAG Clock Rate (MHz) (CLK)                 | 217 |

|    | Little-endian Mode (LENDIAN)                | 218 |

|    | Load Boot Table on IN (BL)                  | 218 |

|    | MMU Support Control (MMU)                   | 218 |

|    | Monitor Target Reset (RST)                  | 218 |

|    | Power On Reset Length N*1ms (PONR)          | 219 |

|    | Real Time Preservation (RTP)                | 219 |

|    | Reset Pulse Length N 1*ms (RPL)             | 219 |

|    | Sense Power via HRESET (SPOWER)             | 219 |

|    | Set Breakpoint (SB)                         | 220 |

|    | Set Stack Range (STACK)                     | 220 |

|    | Set Work Space (WSPACE)                     | 220 |

|    | Synchronized Halt (SYNCHALT)                |     |

|    |                                             |     |

|    | TMD Mode (TMD)                        | 221 |

|----|---------------------------------------|-----|

|    | ·                                     | 221 |

|    |                                       | 222 |

|    |                                       | 222 |

|    |                                       | 222 |

|    | Trigger Out Mode (TRGOUTMODE)         |     |

|    |                                       |     |

| 21 | SyByte Processors22                   | 25  |

|    |                                       |     |

|    |                                       | 225 |

|    |                                       | 225 |

|    |                                       | 226 |

|    |                                       | 226 |

|    |                                       | 226 |

|    | · · · · · · · · · · · · · · · · · · · | 227 |

|    |                                       | 227 |

|    |                                       | 228 |

|    | Issue an IN on Coldstart (INCOLD)     | 228 |

|    |                                       | 228 |

|    |                                       | 229 |

|    | Load Boot Table on IN (BL)            | 229 |

|    | Memory Management Unit (MMU)          | 229 |

|    |                                       | 229 |

|    | No Assertion of TRSET on IN/INN       | 230 |

|    | Reset Pulse Length N 1*ms (RPL)       | 230 |

|    | Set Breakpoint (SB)                   | 230 |

|    | Set Stack Range (STACK)               | 230 |

|    |                                       | 231 |

|    |                                       | 231 |

|    | Transparent Mode Driver (TMD)         | 231 |

|    |                                       | 232 |

|    |                                       | 232 |

|    |                                       | 233 |

|    |                                       | 233 |

|    |                                       | 233 |

|    |                                       | 233 |

|    |                                       | 234 |

Wind River Workbench for On-Chip Debugging Configuration Options Reference, 2.6.1

### 1 Introduction

- 1.1 The CF Options View 1

- 1.2 Changing CF Options with Low-Level Commands 3

- 1.3 CF Options View Buttons 4

- 1.4 Other Resources 4

This document describes the configuration options that are available for each target architecture that Wind River Workbench currently supports.

Configuration options change periodically, and may vary slightly depending on your architecture variant. This document is intended to provide you with general information about most of the CF options that are available for your target architecture.

Available configuration options for a given target may vary depending on whether you are connecting to the target with a Wind River ICE SX or a Wind River Probe.

### 1.1 The CF Options View

To see the configuration options for your target architecture, use the **CF Options** view in Workbench. In the Workbench toolbar, select **Window** > **Show View** > **CF Options**.

**NOTE:** You must have your emulator connected to your host computer to see its CF options.

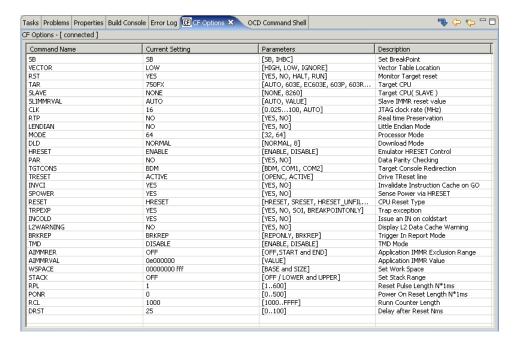

Figure 1-1 shows the available CF options for a Wind River Probe connected to a PPC750FX target.

Figure 1-1 CF Options View

The **CF Options** view has four columns: **Command Name**, **Current Setting**, **Parameters**, and **Description**. An example entry is shown below:

Table 1-1 CF Option Example

| Command Name | Current Setting | Parameters | Description                |

|--------------|-----------------|------------|----------------------------|

| CHECKSTOP    | YES             | [YES, NO]  | Enable Checkstop Interrupt |

**Command Name** shows the low-level command you would use in the **OCD Command Shell** to change the configuration option.

**Current Setting** shows the parameter to which the option is currently set.

**Parameters** shows the available range of option parameters.

**Description** provides a description of the configuration option.

Choose an option and click on its entry under the **Current Settings** heading. A drop-down list will appear; scroll down the list to the parameter you want and click on it to reset the option. For example, to disable the Checkstop Interrupt, click on that option in the **Current Settings** column. The list of parameters (in this case **YES** and **NO**) will appear; click on **NO** to disable the option.

After you change the CF options, click the **Send All CF Options to Target** icon.

**NOTE:** Most CF options do not take effect until you issue a reset, either through the GUI or by entering the IN or RST command in the **OCD Command Shell**.

### 1.2 Changing CF Options with Low-Level Commands

You can also work with configuration options by using the CF command in the OCD Command Shell. At a >BKM> or >ERR> prompt, enter the command CF. This will bring up a list of your emulator's configuration options. You can change them using the syntax

**CF** CommandName Parameter

*CommandName* is the name given in the **Command Name** column in the **CF Options** view.

*Parameter* is the value you wish to change to.

In the example shown in Table 1-1, if the Checkstop Interrupt option is enabled and you wish to disable it, you would enter

### CF CHECKSTOP NO

Enter CF again to see the list of options with the parameters changed. Most changes will not take effect until you issue a reset with the IN or RST command.

### 1.3 **CF Options View Buttons**

| Button            | Description                                                 |

|-------------------|-------------------------------------------------------------|

| ₽                 | Send all CF options to the target                           |

| $\Leftrightarrow$ | Restore selected CF option to the most recent valid setting |

| *                 | Restore all CF options to the most recent valid settings    |

| 00                | Reset all CF options to target defaults                     |

### 1.4 Other Resources

For more information on Workbench low-level commands, see the *Wind River Workbench On-Chip Debugging Command Reference*.

For more information on Wind River Workbench, see the *Wind River Workbench User's Guide*.

For more information on on-chip debugging, see the *Wind River Workbench On-Chip Debugging Guide*.

For more information on the Wind River ICE SX and Wind River Probe, see the Wind River ICE SX for Wind River Workbench Hardware Reference and the Wind River Probe for Wind River Workbench Hardware Reference.

For Tech Tips and Application Notes dealing with Workbench, the Wind River ICE SX and Wind River Probe tools, and various processor-specific issues, go to <a href="http://www.windriver.com/support">http://www.windriver.com/support</a>.

# AMCC 40x Processors

This chapter describes the CF options that are available for AMCC 40x processors (formerly IBM 40x.).

Not all of these CF options apply to all target processors; in general, only applicable options will be visible for any given processor. Which options are visible also depends on whether you are using a Wind River Probe or Wind River ICE SX.

### 403 Folding (FOLDING)

### CF FOLDING [YES, NO, ONRUN]

- YES -- (403GCX processors only) Folding is enabled on CPU, allowing multiple CPU instructions in its piped-in-queue.

- NO -- Folding is disabled, allowing conventional single-step operation through the emulator.

- ONRUN -- Folding is disabled during single-stepping, but allowed during code execution in >RUN> mode.

### Check for Bus Error (BUSERRCHECK)

### CF BUSERRCHECK[YES, NO]

This option configures the Check & Clear Bus Error Exception function.

When set to YES (the default), then when the target processor has a read/write Bus Error, the emulator will detect and clear exception to avoid another exception on a single step or GO command.

To disable the Check & Clear Bus Error Exception function, set this option to NO.

### **Debug Mode (DEBUGMODE)**

### CF DEBUGMODE[EXTERNAL, INTERNAL, BOTH]

This option determines whether Debug Mode relies on target codes' exception handlers.

When set to EXTERNAL (the default) Debug Mode does not rely on target codes' exception handlers. The emulator starts, stops, and freezes the CPU as required.

When set to INTERNAL, Debug Mode relies on target codes' exception handlers. This is typically used when running with ROM monitors in code.

When set to BOTH, Debug Mode uses the setup defined in the DBCR0 register.

### Delay After Reset N\*1ms (DRST)

### CF DRST[0..100]

This option allows you to modify the delay after the release of **HRESET**. Delay can be set in milliseconds, from 0 to 100.

### **Drive TReset Line (TRESET)**

### CF TRESET[OPENC, ACTIVE]

This parameter controls the logic applied to the TRESET signal on the target. Selecting OPENC uses an open collector approach in which the active driver is released by tri-stating the line and allowing conditioning resistors on the target to return the signal to the non-active state. Selecting ACTIVE in this option causes the emulator to drive the TRESET signal to both active and inactive states. This is sometimes required on targets in which the conditioning resistors cause excessive rise or fall time on the signal when returning to an inactive state. This excessive time can cause the processor to come out of reset in an incorrect state.

### **Emulator HALT Command Control (CMDRST)**

### CF CMDRST[IN,RST,BOTH]

This configuration option is used for multicore debugging, and is used to define when the HRESET line is asserted during a reset. If the option is set to BOTH, any time an IN or a RST command is issued, all of the processors that are running are reset. If the option is set to IN, then all of the processors reset only when an IN command is issued. If a RST command is issued, only the processor that is being used is reset and the other ones are left running. If the option is set to RST, then all of the processors will reset if a RST command is issued. However, if an IN command is issued, only the processor that you are using will reset.

### **Except Handlers Available (HANDLERS)**

### CF HANDLERS [YES, NO]

This option indicates whether or not Exception Handler code is available to run if an exception occurs. The default is **YES**.

If this option is set to NO, and an Exception occurs, an error message will appear.

### External Trigger In (TRGIN)

(Wind River ICE SX only)

### CF TRGIN[OFF, LEVELHI, LEVELLO, EDGEHI, EDGELO]

This option sets the trigger input signal sense detection. When activated, **Trigger In** stops the target upon detection. **Trigger In** does not work with any events.

The following table describes the available settings for this option.

Table 2-1 Trigger In Settings

| Setting | Description                                                       |

|---------|-------------------------------------------------------------------|

| OFF     | Trigger signal detection is off.                                  |

| LEVELHI | The trigger input level is set to a value of 1.8 volts or higher. |

| LEVELLO | The trigger input level is set below 1.8 volts.                   |

Table 2-1 Trigger In Settings

| Setting | Description                                                      |

|---------|------------------------------------------------------------------|

| EDGEHI  | Configures the system to trigger on the rising edge of a pulse.  |

| EDGELO  | Configures the system to trigger on the falling edge of a pulse. |

### External Trigger In Mode (TRGINMODE)

(Wind River ICE SX only)

### CF TRGINMODE[AUTO, BOTH]

This option allows users to determine where the trigger input signal sense detection come from when Wind River Trace is being used. When set to **AUTO**, the system automatically detects whether the source of the **TRGIN** is from the Wind River ICE SX or the Wind River Trace. When set to **BOTH**, the system will accept **TRGIN**s from both Wind River ICE SX and Wind River Trace. By default, this option is set to **AUTO**.

### **External Trigger Out (TRGOUT)**

(Wind River ICE SX only)

### CF TRGOUT[LEVELHI, LEVELLO, PULSEHI, PULSELO]

This option allows you to set the trigger output signal type and level. The following table describes the available settings for this option.

Table 2-2 Trigger Out Settings

| Setting | Description                                                                             |

|---------|-----------------------------------------------------------------------------------------|

| LEVELHI | The trigger output level is set to a value of 1.8 volts or higher.                      |

| LEVELLO | The trigger output level is set below 1.8 volts.                                        |

| PULSEHI | Trigger Out signal pin will be a pulse from LOW to HIGH and back to LOW when triggered. |

Table 2-2 Trigger Out Settings

| Setting | Description                                                                              |

|---------|------------------------------------------------------------------------------------------|

| PULSELO | Trigger Out signal pin will be a pulse from HIGH to LOW and back to HIGH when triggered. |

### FPU Available (FPU)

### CF FPU [YES, NO]

Use this option to configure availability for Floating Point Units. The default is NO.

### Flash Burst Mode (FLASHBURSTMODE)

### CF FLASHBURST MODE [ENABLE, DISABLE]

When set to **DISABLE**, this option adds delays for downloads and commands to allow for slow devices whose settings have bursting disabled. When set to **ENABLE**, the option does not add delays.

The option is set to **DISABLE** by default.

### **Instruction-side On-chip Memory (ISOCM)**

CF ISOCM [OFF, START and END]

The default is **OFF**.

Setting this option to **START and END** allows you to read and write the instruction-side on-chip memory (ISOCM), using device control registers (DCR) to display memory and set software breakpoints, on the Xilinx Virtex-4 processor.

**START** = starting address of the ISOCM

**END** = ending address of the ISOCM

### Issue an IN on Coldstart (INCOLD)

### CF INCOLD[YES,NO]

This option configures the emulator boot sequence.

Set this option to **YES** to issue an **IN** command, which asserts a reset on the target during a boot sequence.

Set this option to **NO** to issue a **SYNC** command instead of asserting reset on the target. The **SYNC** command does not reset the board. It establishes JTAG communications and captures the current context. This option is best if you want to hot plug the emulator into a running target.

The default is **NO**.

### JTAG Clock Rate (MHz) (CLK)

### CF CLK[0.025...100, AUTO]

This option configures the rate at which debug commands are clocked to the target. The default setting is **16**.

### Little-endian Mode (LENDIAN)

### CF LENDIAN[YES,NO]

This configuration value determines whether the debugger treats memory contents as little-endian (bits ordered 0..63) or big-endian (bits ordered 63..0.) This affects display and interpretation of opcodes in the debugger window, as well as the effects of symbolic manipulation of variables. Setting this option to **YES** means that little-endian is used; setting the option to **NO** means that big-endian is used.

### Load Boot Table on IN (BL)

### CF BL [ENABLE, DISABLE]

This option enables or disables the Linux bootline commands.

### Logic Analyzer Trace (LATRACE)

### CF LATRACE[NONE, AGILENT, TEKTRONIX]

This configuration option is necessary if you are using a Logic Analyzer for trace acquisition. Configuring and controlling the logic analyzer is dependant upon the manufacturer of the logic analyzer. Current support is available for Agilent and Tektronix solutions only. If you are not using a Logic Analyzer, set this option to NONE.

### Memory Management Unit Mode (MMU)

### CF MMU[ENABLE, DISABLE]

Use this option to enable or disable Linux Memory Management support.

### **Monitor Target Reset (RST)**

### CF RST[YES, NO, HALT, RUN]

This function continuously monitors the target reset signal. If a reset occurs, one of the following actions may be taken:

- YES If a target reset occurs it is reported to the user and BDM control is lost.

- NO If a target reset occurs it is ignored. This is normally used if the code contains a reset instruction, which causes a reset to the external hardware, but not reset the core.

- HALT If the reset occurs in this mode the target is trapped at the restart vector.

- RUN If the reset occurs in this mode the target is restarted and BDM control is maintained.

By default, this option is set to YES. It should only be changed to NO if you have a RESET instruction in your code.

### **Real Time Preservation (RTP)**

### CF RTP[YES, NO]

When this option is enabled, real-time preservation allows the target to run without the emulator stopping the target inadvertently.

### Reset Option (RESET)

### CF RESET[SYSTEM, CHIP, CORE]

This option determines the scope of the reset performed when you issue an IN or INN command.

- SYSTEM --The IN or INN command will assert the target processor's System Reset, which typically resets the entire target.

- CHIP -- The IN or INN command will assert the target processor's Chip Reset only.

- CORE --The IN or INN command will assert the target processor's Core Reset only.

### Retry Establishing Connection on IN/INN (RETRYIN)

### CF RETRYIN[YES, NO]

This option configures whether the emulator will continue trying to connect to the target board after it has failed to connect. When set to YES, the emulator will try again after an IN or INN command fails. When set to NO, the emulator will try to connect only once.

The option is set to **NO** by default.

### Set Breakpoint (SB)

### CF SB[SB,IHBC]

This option remaps traditional software breakpoints to internal hardware breakpoints. It is set to Software Breakpoint (SB) by default. Setting it to IHBC means that all software breakpoints are translated to internal hardware breakpoints. This option is useful when you are debugging code out of Flash or PROM.

Setting this option to **IHBC** may cause limitations in the number of breakpoints that can be set, depending on the target processor.

### Set SDRAM/SRAM Data Address Range (DATA)

### CF DATA[OFF, LOWER and UPPER]

Set this option to **LOWER and UPPER** to set the SDRAM/SRAM data address range.

The option is set to **OFF** by default.

### Set Stack Range (STACK)

### CF STACK[OFF/Lower and Upper]

This setting is **OFF** by default. When stack limits are set, it prevents the emulator from walking through the stack, past the specified range, and causing accidental bus errors.

### **Set Work Space (WSPACE)**

### CF WSPACE[BASE and SIZE]

Flash programming requires a small amount of target RAM to program the flash algorithm. You must tell your emulator where writable RAM is located on your target for this purpose.

As part of the configuration process, the emulator will indicate exactly how much of the RAM workspace is required. Depending on the device family and type, this space is limited to under 2 KB. Note that more memory improves the speed of programming.

To configure the workspace for flash programming the parameters should be entered in hex, where **BASE** is the start address, and **SIZE** is the minimum bytes of target RAM required, as displayed in the **Flash Programmer** view. This command allocates memory on the target system that is used by the emulator for various functions, including flash programming.

### **Target Console Redirection (TGTCONS)**

CF TGTCONS [TGTCONS, BDM] (for the Wind River ICE SX)

### Wind River Probe

Target Console Redirection is not currently supported for the Wind River Probe. You do not need to set this option.

### Wind River ICE SX

**BDM** -- Use this setting to connect I/O on a target board, using the Transparent Mode Driver, to the target's BDM connector. When **BDM** is selected, the Wind River ICE SX is in Transparent Mode, and all I/O data is redirected to the port 1237 of the Wind River ICE SX's IP address. You can then read and write the I/O data remotely by using an application such as a **telnet** window connected to the TGTCONS port (1237) with the Wind River ICE SX's IP address.

For this type of connection to work, the target application must be linked to the Transparent Mode Driver. Refer to the *Wind River Workbench On-Chip Debugging Guide: Using the WDB Transparent Mode Driver* for more information.

TGTCONS -- Use this setting to connect a COM port on a target board to the TGTCONS port of a Wind River ICE SX. All I/O data is then redirected to port 1237 of the Wind River ICE SX's IP address. You can then read and write the I/O data remotely by using an application such as a **telnet** window connected to the TGTCONS port (1237) with the Wind River ICE SX's IP address.

### Target CPU (TAR)

### **CF TAR** target processor

This option allows you to configure the emulator for the target that you are using. *target processor* is the name of your processor. For example, to configure the emulator for a PowerPC 405GP target, type:

CF TAR 405GP

### **Timer Options (TIMERS)**

### CF TIMERS[ON, OFF, OFFSTEP\_ONGO]

This option controls the timers on the internal processor.

**ON** -- The timers on the internal processor are left on.

OFF --The timers on the internal processor are forced (held) off while in Debug Mode (that is, when a >BKM> prompt is visible in the OCD Command Shell) and only application code can re-enable them.

**OFFSTEP\_ONGO** -- The timers on the internal processor are held off while in Debug Mode and while code stepping, and released on a **GO** command.

### Trap Exception (TRPEXP)

### CF TRPEXP[YES, NO, YES\_LEAVEMSR\_ONSTEP, NO\_LEAVEMSR\_ONSTEP, YES\_ALL]

This option allows you to configure which run time exceptions are trapped.

- YES -- All exceptions or interrupts detected by the emulator will be trapped and the CPU will be halted.

- **NO** -- All exceptions will be ignored.

- YES\_LEAVEMSR\_ONSTEP -- The emulator will trap interrupts and exceptions but leave/restore the MSR as is when single-stepping.

- NO\_LEAVEMSR\_ONSTEP -- The emulator will ignore interrupts and exceptions, and allow the code's interrupt handlers to run on a GO. The emulator will leave/restore the MSR as is when single-stepping.

- YES\_ALL -- The emulator will trap all exceptions and set Vector Location to allow stepping through exception vector code.

### Trigger in Filter Mode (TRGINFILTER)

(Wind River ICE SX only)

### CF TRGINFILTER[OFF,ON]

This option provides a filtering option for the Trigger In function. When set to **ON**, a detected signal is required for at least 2 clock periods, or 40ns. This option ensures that noise does not cause a trigger.

### **Trigger Out Mode (TRGOUTMODE)**

(Wind River ICE SX only)

### CF TRGOUTMODE[OFF, ONALLSTOPS, ONBREAKPOINT]

This option allows you to set the type of events that will cause a trigger output to occur.

**OFF** -- Trigger output is off.

**ONALLSTOPS** -- Triggers whenever the target stops running.

**ONBREAKPOINT** -- Triggers whenever a breakpoint is encountered.

### (USENVRAMFLASHVALUES)

### CF USENVRAMFLASHVALUES [YES, NO]

When set to **NO**, this option will use default reset flash values.

Default reset flash values usually have bursting disabled and may cause errors at the default clock speed. When set to YES, this option will use the default NVRAM register values, which normally have bursting enabled.

The option is set to **YES** by default.

### Validate Memory Access (MEMCHECK)

### CF MEMCHECK[YES, NO]

When this option is set to **YES** (the default), the emulator will check memory addresses for validity prior to accessing the target processor, to avoid target hangs.

To disable the memory check, set this option to NO.

### **Vector Table Location (VECTOR)**

### CF VECTOR[HIGH, LOW, IGNORE]

This command specifies the location of the exception vector that is used by the software breakpoints. Please note that this setting must match the MSR register setting for software breakpoints to function correctly.

### 2.1 **CF Options for Wind River Trace**

AMCC 40x processors use several configuration options that are only available when connected to a Wind River Trace.

### **Acquire Trace on GO (TRCAQU)**

### CF TRCAQU [OFF, ON]

Use this option to configure how Wind River Trace starts to store trace information.

When the target begins running code, Wind River Trace can either wait until an event occurs to start storing trace information, or it can start immediately.

When this option is set to **ON**, Wind River Trace starts acquiring trace information as soon as a **GO** command is issued, and does not stop until an event occurs to disable trace.

When this option is set to **OFF**, Wind River Trace does not begin acquiring trace information until an event occurs to turn trace on.

### Clear Trace Buffer on GO (TRCCLR)

### CF TRCCLR [YES, NO]

Use this option to control where to start saving trace data in the trace memory.

**YES** -- When a **GO** command is issued, all newly captured trace data will be stored starting at the first trace memory location. All previously stored trace data will be overwritten and lost.

**NO** -- When a **GO** command is issued, all newly captured trace data will be stored starting at the next trace memory location. Previously stored trace data will not be overwritten.

Wind River Workbench for On-Chip Debugging Configuration Options Reference, 2.6.1

# 3 AMCC 44x Processors

This chapter describes the CF options that are available for AMCC 44x processors (formerly IBM 44x.)

Not all of these CF options apply to all target processors; in general, only applicable options will be visible for any given processor. Which options are visible also depends on whether you are using a Wind River Probe or Wind River ICE SX.

### Check for Bus Error (BUSERRCHECK)

### CF BUSERRCHECK[YES, NO]

This option configures the Check & Clear Bus Error Exception function.

When set to YES (the default), then when the target processor has a read/write Bus Error, the emulator will detect and clear exception to avoid another exception on a single step or **GO** command.

To disable the Check & Clear Bus Error Exception function, set this option to NO.

### **Debug Mode (DEBUGMODE)**

### CF DEBUGMODE[EXTERNAL, INTERNAL, BOTH]

This option determines whether Debug Mode relies on target codes' exception handlers.

When set to EXTERNAL (the default) Debug Mode does not rely on target codes' exception handlers. The emulator starts, stops, and freezes the CPU as required. When set to INTERNAL, Debug Mode relies on target codes' exception handlers. This is typically used when running with ROM monitors in code.

When set to BOTH, Debug Mode uses the setup defined in the DBCR0 register.

### Delay After Reset N\*1ms (DRST)

### CF DRST[0..100]

This option allows you to modify the delay after the release of **HRESET**. Delay can be set in milliseconds, from 0 to 100.

### **Drive TReset Line (TRESET)**

### CF TRESET[OPENC, ACTIVE]

This parameter controls the logic applied to the TRESET signal on the target. Selecting OPENC uses an open collector approach in which the active driver is released by tri-stating the line and allowing conditioning resistors on the target to return the signal to the non-active state. Selecting ACTIVE in this option causes the emulator to drive the TRESET signal to both active and inactive states. This is sometimes required on targets in which the conditioning resistors cause excessive rise or fall time on the signal when returning to an inactive state. This excessive time can cause the processor to come out of reset in an incorrect state.

### **Emulator HALT Command Control (CMDRST)**

### CF CMDRST[IN,RST,BOTH]

This configuration option is used for multicore debugging, and is used to define when the HRESET line is asserted during a reset. If the option is set to BOTH, any time an IN or a RST command is issued, all of the processors that are running are reset. If the option is set to IN, then all of the processors reset only when an IN command is issued. If a RST command is issued, only the processor that is being used is reset and the other ones are left running. If the option is set to RST, then all of the processors will reset if a RST command is issued. However, if an IN command is issued, only the processor that you are using will reset.

### **Except Handlers Available (HANDLERS)**

### CF HANDLERS [YES, NO]

This option indicates whether or not Exception Handler code is available to run if an exception occurs. The default is **YES**.

If this option is set to NO, and an exception occurs, an error message will appear.

### External Trigger In (TRGIN)

(Wind River ICE SX only)

### CF TRGIN[OFF, LEVELHI, LEVELLO, EDGEHI, EDGELO]

This option sets the trigger input signal sense detection. When activated, **Trigger In** stops the target upon detection. **Trigger In** does not work with any events.

The following table describes the available settings for this option.

Table 3-1 Trigger In Settings

| Setting | Description                                                       |

|---------|-------------------------------------------------------------------|

| OFF     | Trigger signal detection is off.                                  |

| LEVELHI | The trigger input level is set to a value of 1.8 volts or higher. |

| LEVELLO | The trigger input level is set below 1.8 volts.                   |

| EDGEHI  | Configures the system to trigger on the rising edge of a pulse.   |

| EDGELO  | Configures the system to trigger on the falling edge of a pulse.  |

### External Trigger In Mode (TRGINMODE)

(Wind River ICE SX only)

### CF TRGINMODE[AUTO, BOTH]

This option allows users to determine where the trigger input signal sense detection come from when Wind River Trace is being used. When set to AUTO, the system automatically detects whether the source of the TRGIN is from the

Wind River ICE SX or the Wind River Trace. When set to **BOTH**, the system will accept **TRGIN**s from both Wind River ICE SX and Wind River Trace. By default, this option is set to **AUTO**.

### **External Trigger Out (TRGOUT)**

(Wind River ICE SX only)

### CF TRGOUT[LEVELHI, LEVELLO, PULSEHI, PULSELO]

This option allows you to set the trigger output signal type and level. The following table describes the available settings for this option.