### **WIND RIVER**

Wind River®

**BOARD BRING-UP GUIDE**

1.0

Copyright © 2006 Wind River Systems, Inc.

All rights reserved. No part of this publication may be reproduced or transmitted in any form or by any means without the prior written permission of Wind River Systems, Inc.

Wind River, the Wind River logo, Tornado, and VxWorks are registered trademarks of Wind River Systems, Inc. Any third-party trademarks referenced are the property of their respective owners. For further information regarding Wind River trademarks, please see:

### http://www.windriver.com/company/terms/trademark.html

This product may include software licensed to Wind River by third parties. Relevant notices (if any) are provided in your product installation at the following location: <code>installDirlproduct\_name/3rd\_party\_licensor\_notice.pdf</code>.

Wind River may refer to third-party documentation by listing publications or providing links to third-party Web sites for informational purposes. Wind River accepts no responsibility for the information provided in such third-party documentation.

### **Corporate Headquarters**

Wind River Systems, Inc. 500 Wind River Way Alameda, CA 94501-1153 U.S.A.

toll free (U.S.): (800) 545-WIND telephone: (510) 748-4100 facsimile: (510) 749-2010

For additional contact information, please visit the Wind River URL:

http://www.windriver.com

For information on how to contact Customer Support, please visit the following URL:

http://www.windriver.com/support

Wind River Board Bring-Up Guide, 1.0

4 May 06

Part #: DOC-17526-ZD-00

## Contents

| 1 | Intro | oductio | on                                                                                                                    | 1              |

|---|-------|---------|-----------------------------------------------------------------------------------------------------------------------|----------------|

| 2 | On-   | -Chip E | Debugging                                                                                                             | 3              |

| 3 | Boa   | rd Brin | ıg-Up                                                                                                                 | 7              |

|   | 3.1   | Goals   | and Objectives                                                                                                        | 7              |

|   | 3.2   | Seque   | ence of Events                                                                                                        | 7              |

| 4 | Boa   | rd Des  | criptor Files                                                                                                         | 9              |

|   | 4.1   | Introd  | luction                                                                                                               | 9              |

|   | 4.2   | Creati  | ng a New Board Descriptor File                                                                                        | 10             |

|   |       |         | Using the Predefined Layouts in JTAG Editor Using the Custom Option in the JTAG Editor View Editing Your Board Layout | 12<br>17<br>19 |

|   | 4.3   | XML 1   | Board Files                                                                                                           | 20             |

|   |       | 4.3.1   | XML Board File Fields                                                                                                 | 22             |

|   |       |         | <device_table> Fields</device_table>                                                                                  | 22<br>22       |

|   | 4.4   | Manu    | ally Creating XML Board Files                                                                                         | 23             |

|   | 4.5 | Layou     | t, Routing and Design Considerations       | 25         |

|---|-----|-----------|--------------------------------------------|------------|

|   | 4.6 | JTAG      | Timing Parameters for Wind River Emulators | <b>2</b> 6 |

| 5 | OCI | O Conn    | ections                                    | 27         |

|   | 5.1 | Debug     | g Connections                              | 27         |

|   | 5.2 | Creati    | ng a Target Connection                     | 28         |

| 6 | Тоо | l Confi   | guration                                   | 33         |

|   | 6.1 | Introd    | uction                                     | 33         |

|   | 6.2 | Tool C    | Configuration                              | 34         |

|   |     | 6.2.1     | Clock Rate                                 | 34         |

|   |     | 6.2.2     | Drive TRESET Line                          | 35         |

|   |     | 6.2.3     | Monitor Target Reset                       | 35         |

|   |     | 6.2.4     | Emulator HRESET Control                    | 36         |

|   |     | 6.2.5     | CPU Reset Type                             | 36         |

|   |     | 6.2.6     | Saving Changes                             | 37         |

| 7 | Boa | rd Initia | alization                                  | 39         |

|   | 7.1 | Introd    | uction                                     | 39         |

|   | 7.2 | Backg     | round Mode                                 | 40         |

|   |     | 7.2.1     | The IN Command                             | 40         |

|   |     | 7.2.2     | Set Verbose On                             | 40         |

|   | 7.3 | The IN    | NN Command                                 | 43         |

|   | 7.4 | Regist    | ers                                        | 43         |

|   |     | 7.4.1     | Downloading a Register File                | 44         |

|   |     | 7.4.2     | Enabling and Disabling Register Groups     | 45         |

|   |     | 7.4.3     | Modifying Registers Manually               | 46         |

| 8  | Veri | Verifying Hardware |                              |          |  |  |

|----|------|--------------------|------------------------------|----------|--|--|

|    | 8.1  | Introd             | luction                      | 49       |  |  |

|    | 8.2  | Settin             | g a Workspace                | 49       |  |  |

|    | 8.3  | Diagn              | ostic Functions              | 50       |  |  |

|    |      | 8.3.1              | Simple RAM Test              | 50       |  |  |

|    |      | 8.3.2              | Full RAM Tests               | 52       |  |  |

|    |      | 8.3.3              | CRC Calculation              | 53       |  |  |

|    |      | 8.3.4              | Scope Tests                  | 53       |  |  |

|    |      |                    | Read From Location           | 53       |  |  |

|    |      |                    | Write To Location            | 53       |  |  |

|    |      |                    | Write and Complement         | 54<br>54 |  |  |

|    |      |                    | Write Then Read              | 54       |  |  |

|    |      | 8.3.5              | Bus Tests                    | 54       |  |  |

|    |      |                    | Address Bus Test             | 54       |  |  |

|    |      |                    | Data Bus Test                | 54       |  |  |

| 9  | Test | ing Me             | emory                        | 55       |  |  |

|    | 9.1  | Introd             | luction                      | 55       |  |  |

|    | 9.2  | Testin             | g Memory                     | 55       |  |  |

|    |      | 9.2.1              | Stepping an Instruction      | 56       |  |  |

|    |      | 9.2.2              | Running Code                 | 58       |  |  |

|    |      | 9.2.3              | Setting Software Breakpoints | 59       |  |  |

|    |      | 9.2.4              | Setting Hardware Breakpoints | 61       |  |  |

| 10 | Deb  | ugging             | g in RAM                     | 65       |  |  |

|    | 10.1 | Overview           |                              |          |  |  |

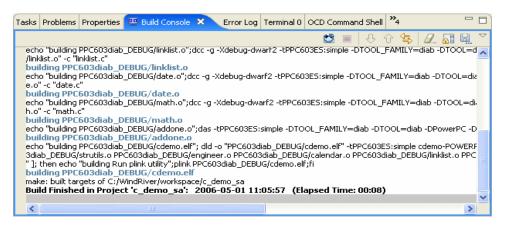

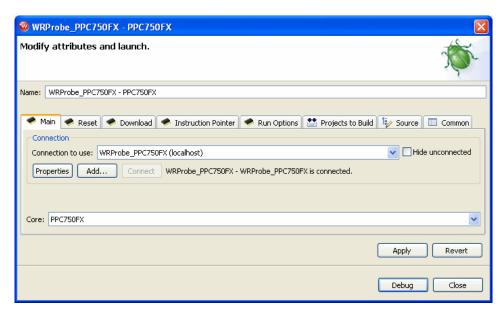

|    | 10.2 | Creati             | ng a Target Connection       | 65       |  |  |

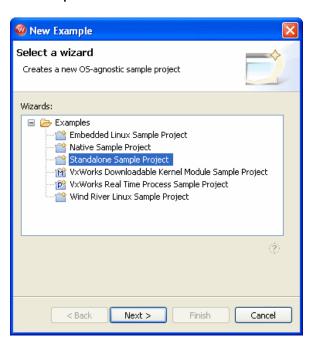

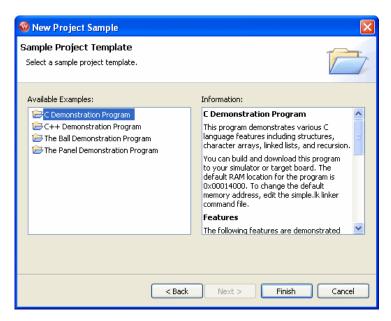

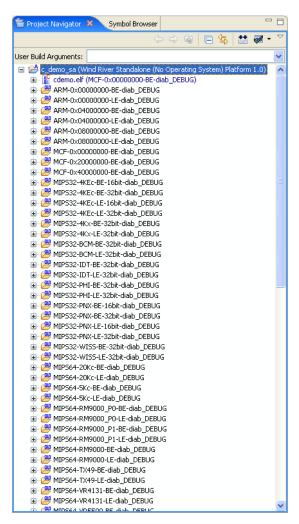

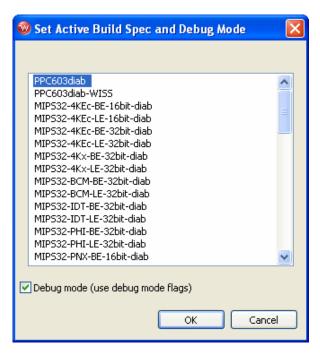

|    | 10.3 | Creatin | ng a Project                            | 66         |

|----|------|---------|-----------------------------------------|------------|

|    | 10.4 | Downl   | loading Code and Symbol Information     | <b>71</b>  |

|    | 10.5 | Debug   | ging Code in RAM                        | 74         |

|    |      | 10.5.1  | Monitoring Processes                    | <b>7</b> 5 |

|    |      | 10.5.2  | Stepping Through Code                   | <b>7</b> 5 |

|    |      | 10.5.3  | Setting a Software Breakpoint           | 76         |

|    |      | 10.5.4  | Running a Program                       | 77         |

|    |      | 10.5.5  | Stepping Through a Program              | 78         |

|    |      | 10.5.6  | Setting a Hardware Breakpoint           | <b>7</b> 9 |

|    |      | 10.5.7  | Disconnecting and Terminating Processes | 83         |

| 11 | Prog | grammi  | ng Flash Memory                         | 85         |

|    | 11.1 | Introd  | uction                                  | 85         |

|    | 11.2 | Testing | g Flash Workspace                       | 86         |

|    |      |         | Reading and Writing Memory              | 86         |

|    | 11.3 | Getting | g Started                               | 87         |

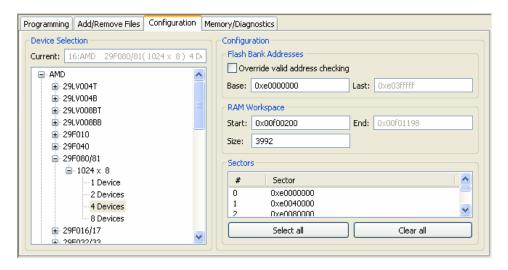

|    | 11.4 | Flash ( | Configuration Tab                       | 88         |

|    |      | 11.4.1  | Selecting a Flash Driver                | 89         |

|    |      | 11.4.2  | Configuring Flash Memory Bounds         | 89         |

|    |      | 11.4.3  | Configuring RAM Workspace               | 90         |

|    |      | 11.4.4  | Selecting Flash Sectors for Erasure     | 90         |

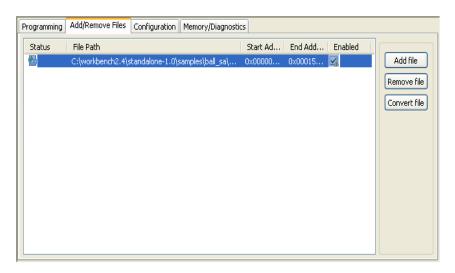

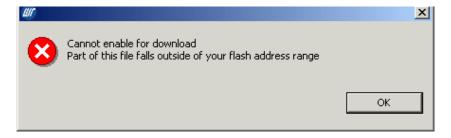

|    | 11.5 | Flash A | Add/Remove Files Tab                    | 91         |

|    |      | 11.5.1  | Adding Files                            | 91         |

|    |      | 11.5.2  | Removing Files                          | 91         |

|    |      | 11.5.3  | Converting .hex Files To .bin Format    | 91         |

|    |      | 11.5.4  | Setting The Download Offset Of A File   | 92         |

|    |      | 11.5.5  | Enabling A File For Download            | 92         |

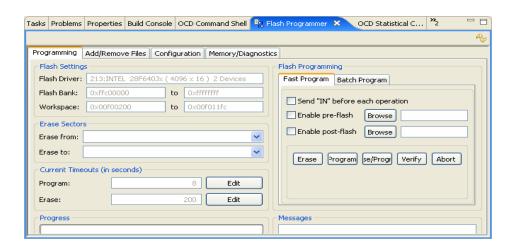

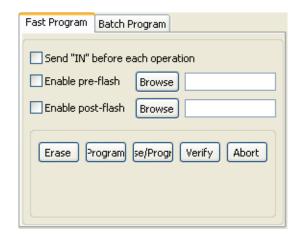

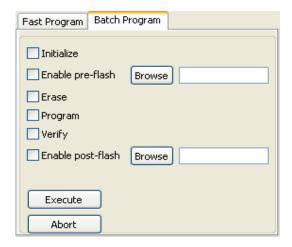

|    | 11.6       | Flash Programming Tab              |

|----|------------|------------------------------------|

|    |            | 1.6.1 Fast And Batch Program Tabs  |

|    |            | 1.6.2 Erasing Flash                |

|    |            | 1.6.3 Programming Flash 99         |

|    |            | 1.6.4 Verifying Flash Contents     |

|    |            | 1.6.5 Setting Timeouts             |

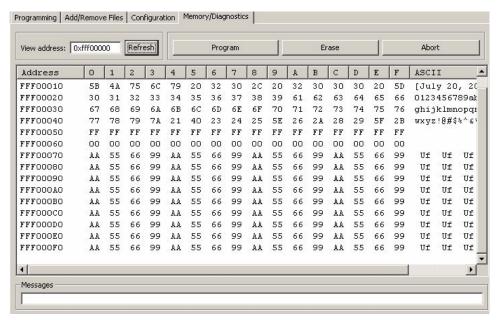

|    | 11.7       | Flash Memory/Diagnostics Tab       |

|    |            | 1.7.1 Viewing Memory               |

|    |            | 1.7.2 Running Diagnostic Tests     |

| 12 | Deb        | ging in ROM 99                     |

|    | 12.1       | Overview                           |

|    | 12.2       | Getting Started                    |

|    | 12.3       | Debugging in ROM 100               |

|    |            | 2.3.1 Stepping Through Boot Code   |

|    |            | 2.3.2 Setting Hardware Breakpoints |

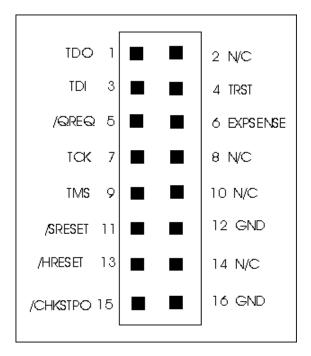

| A  | Pins       | Mapped to Common Signals 107       |

|    | <b>A.1</b> | ntroduction                        |

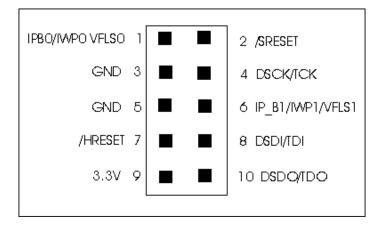

|    | <b>A.2</b> | PowerPC Processors JTAG 108        |

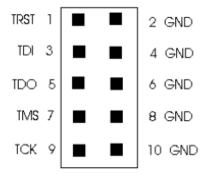

|    | <b>A.3</b> | MIPS Processors JTAG 109           |

|    | <b>A.4</b> | ARM Processors JTAG 110            |

|    | <b>A.5</b> | ColdFire Processors JTAG           |

|    | A.6        | BDM Processors 112                 |

| В | Inte       | ernal Bi | reakpoint Capabilities                     | 113   |

|---|------------|----------|--------------------------------------------|-------|

|   |            |          | Line Breakpoints                           | . 114 |

|   |            |          | Expression Breakpoints                     |       |

|   |            |          | Hardware Breakpoints                       |       |

|   |            |          | Importing Breakpoints                      |       |

|   |            |          | Exporting Breakpoints                      |       |

|   |            |          | Disabling Breakpoints                      |       |

|   |            |          | Removing Breakpoints                       |       |

| С | Pin        | Termin   | ations                                     | 119   |

|   | <b>C.1</b> | JTAG     | Pin Terminations                           | . 119 |

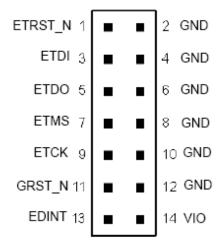

|   |            | C.1.1    | 16-Pin JTAG Connector                      | . 119 |

|   |            | C.1.2    | ARM 14-Pin JTAG Connector                  | . 121 |

|   |            | C.1.3    | ARM 20-Pin JTAG Connector                  | . 123 |

|   |            | C.1.4    | ARMX (XScale) 20-Pin JTAG Connector        | . 124 |

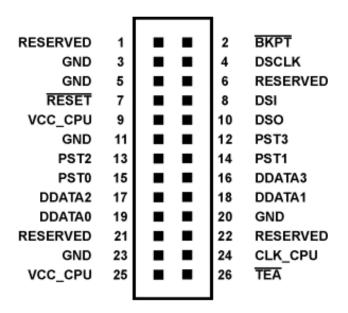

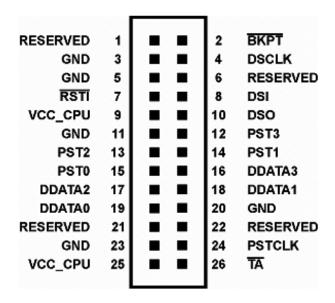

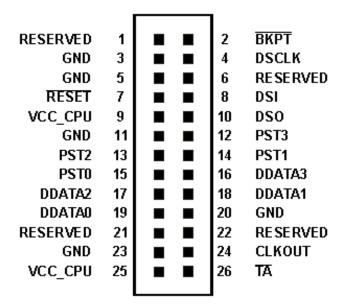

|   | <b>C.2</b> | EJTAC    | G Pin Terminations                         | 125   |

|   |            | C.2.1    | MIPS 14-Pin EJTAG Connector                | . 125 |

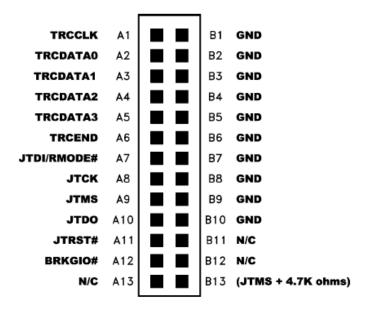

|   |            | C.2.2    | MIPS Philips 20-Pin EJTAG Connector        | . 126 |

|   |            | C.2.3    | MIPS IDT 24-Pin EJTAG Connector            | . 128 |

|   |            | C.2.4    | MIPS Broadcom 10-Pin EJTAG Connector       | . 130 |

|   |            | C.2.5    | MIPS NEC 26-Pin EJTAG Connector            | . 131 |

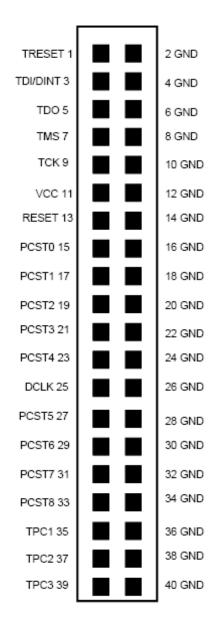

|   |            | C.2.6    | MIPS Toshiba 40-Pin EJTAG Connector        | . 133 |

|   | <b>C.3</b> | BDM 1    | Pin Terminations                           | 136   |

|   |            | C.3.1    | PowerPC 5xx/8xx 10-pin BDM Connector       | . 136 |

|   |            | C.3.2    | Freescale ColdFire 26-Pin BDM Connector    | . 137 |

|   |            |          | ColdFire 26-Pin BDM Connector, Option One  |       |

|   |            |          | ColdFire 26-Pin BDM Connector, Option Two  |       |

|   |            |          | ColdFire 26-Pin BDM Connector, Option Four |       |

|   | <b>C.4</b> | Mictor   | r Pin Terminations                         | . 141 |

### Contents

| Index |       |                                          | 145 |

|-------|-------|------------------------------------------|-----|

|       | C.4.2 | AMCC 44x 38-pin Mictor Connector Pin-out | 142 |

|       | C.4.1 | AMCC 40x 38-pin Mictor Connector Pin-out | 141 |

Wind River Board Bring-Up Guide, 1.0

### 1 Introduction

This document describes procedures for using Wind River Workbench with the Wind River Probe and Wind River ICE emulators to bring up a target board, from the first power-up through running and debugging application code.

This document includes the following chapters:

- 1. Introduction -- Introduces the document.

- 2. On-Chip Debugging -- Describes of the theory of on-chip debugging.

- 3. Board Bring-Up -- Provides an overview of board bring-up procedure.

- 4. Board Descriptor Files -- Describes how to create, edit, and use board descriptor files.

- 5. *OCD Connections* -- Describes making an OCD connection to a target using a JTAG or BDM port.

- 6. Tool Configuration -- Describes hardware-specific configuration options for Wind River emulators.

- 7. *Board Initialization --* Describes how to use Wind River emulators to initialize the target hardware.

- 8. Verifying Hardware -- Describes how to use Wind River Workbench to run hardware diagnostics on your target.

- 9. *Testing Memory* -- Describes how to use Wind River emulators to suspend CPU operations and force the target into background mode.

- 10. *Debugging in RAM* -- Describes how to create a project, download code and symbol information, set software breakpoints, and step through code.

- 11. *Programming Flash Memory* -- Describes working with flash memory on your target.

- 12. Debugging in ROM -- Describes using hardware breakpoints to debug in ROM.

- *A. Pins Mapped to Common Signals --* Provides a mapping reference for Wind River-supported processor families.

- *B. Internal Breakpoint Capabilities --* Provides a detailed reference for line, expression, and hardware breakpoints in Workbench.

- *C. Pin Terminations* -- provides a detailed reference of pinouts for Wind River-supported processor families.

# 2 On-Chip Debugging

Almost all embedded systems have hardware and software elements, which are separate but interdependent. Since embedded systems generally do not have keyboards, or any kind of user interface, debugging of their software elements must be done externally.

An older solution to this problem was the in-circuit emulator, which substituted its own internal processor for the central processing unit (CPU) of the embedded system.

However, in-circuit emulators are expensive; and since they are made by third-party vendors, there is often a long delay between a new target and a new in-circuit emulator that can attach to it. A cheaper, and more easily implemented, solution is *on-chip debugging* (OCD).

Many semiconductor manufacturers now integrate dedicated debug microcircuitry into their chips. This approach adds hardware and software debug capability to the existing JTAG or BDM ports. Since the debug operations occur on a dedicated area of the chip itself, this solution is known as on-chip debugging.

OCD combines many features of software debug monitors and in-circuit emulators. Like an in-circuit emulator, OCD provides low-level hardware access. It does not need to use target memory; it does not need a target communication channel; and it can edit memory and registers without halting the processor. Like a software monitor, OCD lets you set breakpoints, stop and start the CPU, step through code, examine memory, and run diagnostic tests; but unlike a software monitor, OCD does not need good hardware to run.

Software defects that cause the operating system to crash will typically cause an agent-based debug environment to fail. However, since an OCD connection is implemented in the hardware, it is not as sensitive.

An OCD connection remains active even on bad hardware. Using an OCD connection, you can download low-level software even when the target board is not functioning correctly, and the boot loader cannot run.

On-chip debugging capability varies from one processor family to another, but the provided functionality is generally similar. As an illustration, Freescale ColdFire processors use the following primitives for Background Debug Mode (BDM):

Table 2-1 Freescale ColdFire OCD Primitives

| Command        | Mnemonic | Description                                                     |  |

|----------------|----------|-----------------------------------------------------------------|--|

| Read Register  | RDREG    | Read a data register and return the value.                      |  |

| Write Register | WDREG    | Write a value to a data register.                               |  |

| Read Memory    | READ     | Read from a memory location.                                    |  |

| Write Memory   | WRITE    | Write to a memory location.                                     |  |

| Stop Processor | BGND     | Assume control of the bus and put processor in background mode. |  |

| Single Step    | STEP     | Step one instruction.                                           |  |

| Resume         | GO       | Resume execution at the program counter's current location.     |  |

Wind River tools use these low-level OCD primitives as building blocks to create a higher level of primitives, thus allowing hardware and software verification.

OCD commands invoked while the processor is running "steal" bus cycles from the CPU in the same way a Direct Memory Access (DMA) controller does.

As the debugger reads and writes to memory and registers, it halts the CPU and restarts it. The CPU is not involved in OCD operations. The **BGND** instruction from the OCD hardware will cause the CPU to halt, and the OCD hardware will assume control of chip operations. A **GO** (Resume) command will flush OCD operations and restart the CPU.

The Wind River Probe and Wind River ICE SX tools use the on-chip debug capabilities embedded in the target processor. These tools are not true in-circuit emulators, because they do not replace the target CPU with their own internal processor. However, the functions they perform are similar, and this document will refer to them as "emulators".

OCD has many advantages over in-circuit emulation. It is cheaper; the debug hardware is included by the silicon manufacturer, not by a third party; and unlike an in-circuit emulator, the OCD hardware does not lag behind chip releases.

When you access the OCD services on the chip, all interaction between the Wind River Probe or Wind River ICE SX and the target runs exclusively through the OCD connection. This means that your system is effective for the entire development process, even before board-level peripherals are stable.

ColdFire processors, and some older PowerPC processors (5xx and 8xx) use a dedicated BDM port for OCD operations. A more recent approach is to attach the OCD functions to the Joint Test Action Group (JTAG) interface to communicate to the target CPU, and share this interface with boundary-scan board-circuit testing. The JTAG interface follows the IEEE 1149.1 boundary-scan (JTAG/Test Interface) specification.

The JTAG interface consists of a set of five signals, three JTAG registers, and a test access port (TAP) controller. The TAP controller is typically embedded in the target microprocessor or device. The information related signals are **TDI** (Test Data In) and **TDO** (Test Data Out). The boundary-scan register chain (data) includes registers controlling the direction of the input/output drivers, as well as registers reflecting the signal value received or driven. The expectation and details of particular CPU chains are encoded directly into the emulator firmware.

Each device sharing the JTAG interface employs a serial stream of relative data. The data streams for all devices can be chained together. An associated process can scan the combined chain to extract any particular device's information.

For further information about JTAG operations, refer to the IEEE 1149.1 specification at <a href="http://standards.ieee.org">http://standards.ieee.org</a>.

Wind River emulators are non-intrusive; that is, they do not use target resources. An emulator will not affect target memory, stack space, or the flash workspace.

On-chip debug agents reside inside cache and memory management units they share the chip with, so the OCD hardware sees address and data values just like the CPU sees them. Some processor families have dedicated output signals (other than the JTAG pins) that can deliver information on the state of the processor. Combined with external hardware (such as the Wind River ICE SX, in conjunction with the Wind River Trace tool) these signals can log the real-time code execution history to a trace buffer. This data is helpful when you need to debug problems that only occur when the processor is running at full speed.

There is an industry standard, not yet widely adopted, created by the Global Embedded Processor Debug Interface Forum, formally called IEEE-ISTO 5001. For

Wind River Board Bring-Up Guide, 1.0

the standard, and a good deal of further information, see <a href="http://www.nexus5001.org/standard.html">http://www.nexus5001.org/standard.html</a>.

## 3 Board Bring-Up

- 3.1 Goals and Objectives 7

- 3.2 Sequence of Events 7

### 3.1 Goals and Objectives

The goal of a board bring-up procedure is to verify the operation of a target board, all the way from power-on to successfully running and debugging code.

This chapter provides a general overview of board bring-up procedure. Later chapters go over the matter in detail.

### 3.2 Sequence of Events

In general, the procedure of bringing up a board uses the following general outline:

- Attempt a "smoke test"-- that is, can you apply power to the board without damaging it?

- Perform a "lamp check" -- turn the LEDs on and off

- Establish a JTAG or BDM connection to the emulator.

- Configure the emulator-target interface; set voltage, clock rate, signal logic.

- Enter background mode.

- Read and write core registers.

- Configure the target workspace.

- Run simple RAM tests.

- Run bus tests on the address and data buses.

- Test low-level stepping and breakpoints.

- Execute low-level code.

- Test source-level stepping and breakpoints.

- Execute application.

- Debug application code in RAM.

- Test the target's ability to erase and program flash memory.

- Debug application code in ROM.

# **4**Board Descriptor Files

- 4.1 Introduction 9

- Creating a New Board Descriptor File 10

- 4.3 XML Board Files 20

- Manually Creating XML Board Files 23

- Layout, Routing and Design Considerations 25

- JTAG Timing Parameters for Wind River Emulators 26

### 4.1 Introduction

In most cases you do not need to concern yourself with the JTAG board file. However, if you are debugging multiple cores or if your JTAG scan chain has other devices besides the core on it, your emulator requires a board descriptor file to correctly set up the JTAG scan chain for your target.

The board file provides a description of each of the devices that are included in the scan chain, and provides information about each device.

All Wind River target boards are shipped with a board descriptor file that works for that target board. If you are using a Wind River target board, you can specify the default board descriptor file for that target in the **New Connection** Wizard in Wind River Workbench, as described in the Establishing Communications chapter of your emulator's Hardware Reference.

**NOTE:** If you choose to modify a board descriptor file that was shipped with Wind River Workbench, save your modified file with a different name to prevent overwriting the default file.

Board descriptor files are written in extensible markup language (XML). However, it is easiest to create or modify board files using Workbench. The software allows you to create and catalog scan chain devices such as processors, complex programmable logic devices (CPLDs), field-programmable gate arrays (FPGAs), and application-specific integrated circuits (ASICs), and from that catalog create a board file that properly describes the scan chain on your target.

**CAUTION:** Your board file must list the devices included on your scan chain in the same order as they are physically laid out on the target. If the board file and the physical scan chain do not match, the board file for your target will not work.

### 4.2 Creating a New Board Descriptor File

Workbench uses JTAG Editor to create and modify board files. To use the JTAG Editor view, you must first have an active project running. For information on creating projects, see the *Wind River Workbench User's Guide*.

To create a new board file:

- 1. Open your project in Workbench.

- 2. Select File > New > JTAG Board Layout.

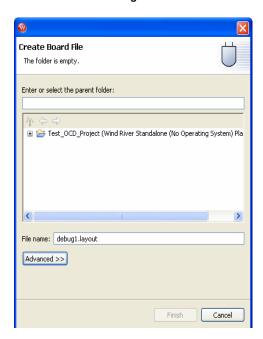

The **Create Board File** dialog appears, as shown in Figure 4-1.

### Figure 4-1 Create Board File Dialog

Wind River Workbench automatically populates the **Parent Folder** field with your active project. In the **File Name** field, type a name for your board file. This creates a **.layout** file, which JTAG Editor will use to create a **.brd** file in the next step.

The example shown in Figure 4-1 creates a file called **debug1.layout** for the project **debug1**.

3. Click **Finish**.

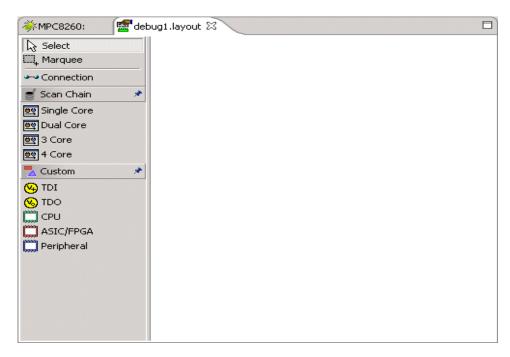

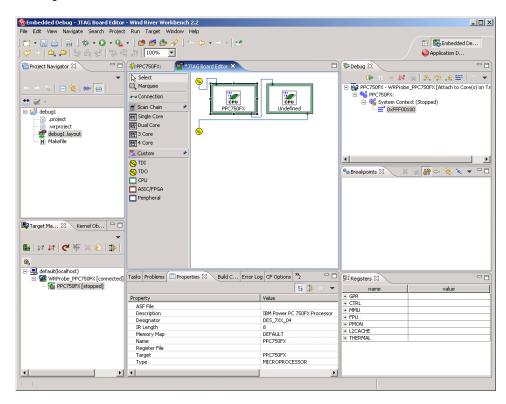

This opens the JTAG Editor view, as shown in Figure 4-2.

**>**

**NOTE:** JTAG Editor edits a **.layout** file, which is a graphic representation of the board layout. A **.brd** file cannot be created until you have created a JTAG layout, such as the one shown in Figure 4-4.

Figure 4-2 JTAG Editor

### Using the Predefined Layouts in JTAG Editor

JTAG Editor includes predefined graphic layouts for one, two, three, and four cores, which are displayed in the Editor toolbar to the left of the editing field, as shown in Figure 4-3.

In the rare case where you need to debug more than four cores at the same time, the JTAG Editor also includes a **Custom** option. See *Using the Custom Option in the JTAG Editor View*, p. 17, for more information.

- 4. In the JTAG toolbar, click **Select**.

- 5. Under Scan Chain, pick the number of cores you need to debug.

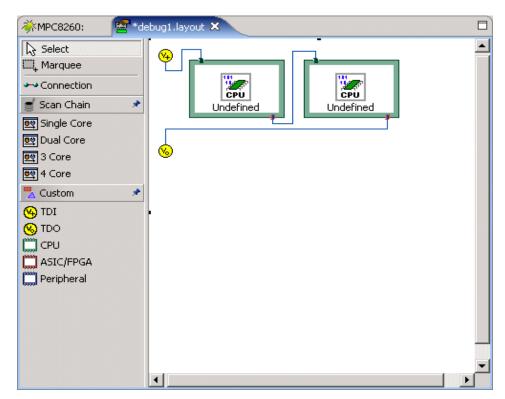

For example, if the **debug1** project has two cores, click on **Dual Core** under the **Scan Chain** heading and drag it into the editing field, as shown in Figure 4-4.

NOTE: The core icon must be clicked and dragged into the editing field. Just clicking on it will not do anything.

Figure 4-4 **Dual Core Layout**

**NOTE:** You can only drag one predefined layout into the editing field at a time. If you drag in a second layout, it will overlay the first, causing confusion.

The editing field now shows a graphic representation of the scan chain. Notice that the two cores are labelled **Undefined**. They have no properties until you assign them in the next step.

Double-click on the first core.

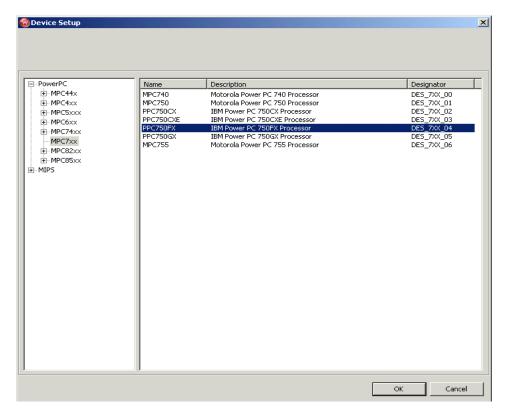

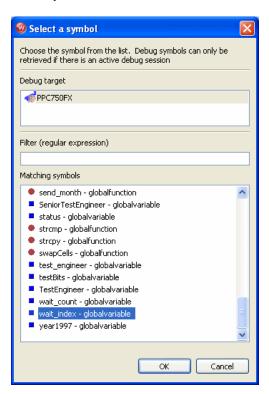

The **Device Setup** dialog appears, as shown in Figure 4-5.

Figure 4-5 **Device Setup**

Use the dialog to select your processor type. The example in Figure 4-5 shows a PPC750FX processor.

### 7. Click **OK**.

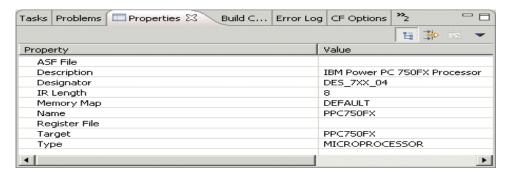

You are returned to the **Device Debug** Perspective. The first core is now defined as a PPC750FX, and the **Properties** view is displayed.

Figure 4-6 **Defining the Core**

You can use the **Properties** view to finish defining the first core.

Figure 4-7 Properties View

8. Click on any property to modify it.

Clicking on the **Register File** property will open a browser window; use the browser to navigate to the **.reg** file you want to use.

Your first core is now defined. To define your second core, double-click on it and repeat Steps 6 through 8.

If both cores use the same processor type, make sure you edit the **Designator** value in the **Properties** view. Workbench does not allow two cores to have the same unique designator. For example, in Figure 4-7 the first core's designator is **DES\_7XX\_04**. If your second core is the same processor type as the first, the same designator will appear in the **Properties** window. Click on the **Designator** value to change it to (for instance) **DES\_7XX\_05**.

Once you have defined all your cores, you can create your board file.

9. Right-click on the editing area. In the dialog that appears, choose **Export Board File**.

A browser window appears. Choose the folder you want to save your board file in.

- In the File Name field, type the name you wish to assign to your board file.

In the example, the board file name is debug1.brd.

- 11. Click **Save**.

### Using the Custom Option in the JTAG Editor View

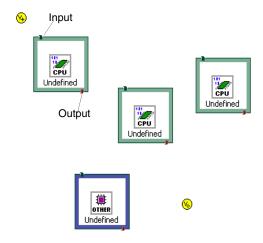

In the rare case where you need to debug more than four cores at the same time, JTAG Editor uses a **Custom** option to create a new board file piece by piece.

- 1. In the JTAG toolbar (Figure 4-3), click **Custom**.

- 2. Construct your layout using the elements under the **Custom** heading.

The elements available are an input node (TDI) and a termination node (TDO), as well as CPUs, ASICs, FPGAs, and peripherals. To add an element, click on its icon and drag it into the editing field.

Figure 4-8 shows a partially completed layout with an input, a terminator, three CPUs, and a peripheral device.

Figure 4-8 Partial Custom Layout

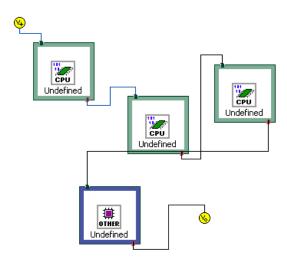

Once you have your terminating nodes and devices laid out, you need to connect them.

- 3. In the JTAG toolbar, click **Connections**.

- When you move the cursor back into the editing field, it now looks like a power cord.

- 4. Click on the input node.

- 5. Move the cursor to your first processor and click again.

- A connection line joins the input node and the processor.

- 6. Click on the first processor, move the cursor to the second processor, and click on it.

- A connection line joins the two processors.

- 7. Continue this process until you complete the circuit by clicking on the terminator node.

8. When you have connected all devices and nodes, click **Connections** again. The cursor returns to normal.

Your custom board is now laid out. Define its properties and generate your .brd file by following Steps 6-11 in *Using the Predefined Layouts in JTAG Editor*, p.12.

### **Editing Your Board Layout**

To remove a device, node, or connection from your layout, use the **Select** button or the **Marquee** button in the JTAG toolbar.

To use the **Select** button, click **Select** in the toolbar. Then click on any device, node, or connection to highlight it and press **Delete**.

To use the **Marquee** button, click **Marquee** in the toolbar. You will see that the cursor now appears as a crosshair in the editing field. Hold the mouse button down and drag the cursor to create a box around the device you wish to highlight, then press **Delete**.

**NOTE:** The **Marquee** button can only highlight devices, not nodes or connections.

You can also edit your layout using the **Outline** view in Workbench. In the Workbench toolbar, click on **Window**. Select **Show View > Outline**.

The **Outline** view appears as shown in Figure 4-10.

Figure 4-10 Outline View

The **Outline** view displays the elements of your layout in the order they were added. Click on any element to highlight it and press **Delete**.

Using the **Outline** view in this way is handy if you have accidentally overlaid one layout on top of another, or if you want to back up and start again. Use the list in the **Outline** window to delete any or all of the contents of the JTAG editing field.

### 4.3 XML Board Files

Board descriptor files are created in extensible markup language (XML). You can view the XML version of your board file by opening your .brd file in a text editor, or by selecting File > Open in Workbench and navigating to the .brd file in the

browser window that appears. The XML text will appear in the Workbench Editor. An example board descriptor file is shown below.

Figure 4-11 Board File XML version

```

*JTAG Board Editor

PPC750FX:

📄 boardfiles_debug1.brd 🗶

<DEVICE_TABLE>

<TABLE MODE>SLOW</TABLE MODE>

<TABLE CLOCK>16Mhz</TABLE CLOCK>

<TABLE_MULTI>ENABLE</TABLE_MULTI>

<TABLE TIED RESET>OFF</TABLE TIED RESET>

<DEVICE>

<NAME>PPC750FX</NAME>

<DESCRIPTION>IBM Power PC 750FX Processor</DESCRIPTION>

<TYPE>MICROPROCESSOR</TYPE>

<TARGET>PPC750FX</TARGET>

<SELREG FILE></SELREG FILE>

<DESIGNATOR>DES_7XX_04

<IR LEN>8</IR LEN>

<ASF FILE></ASF FILE>

<REG FILES>

</REG FILES>

<MEMORY MAP>

<MEMORY MODE>DEFAULT/MEMORY MODE>

</memory map>

</DEVICE>

<DEVICE>

<NAME>PPC750FX</NAME>

<DESCRIPTION>IBM Power PC 750FX Processor</DESCRIPTION>

<TYPE>MICROPROCESSOR</TYPE>

<TARGET>PPC750FX</TARGET>

<SELREG FILE></SELREG FILE>

<DESIGNATOR>DES 7XX 05</DESIGNATOR>

<IR LEN>8</IR LEN>

<ASF_FILE></ASF_FILE>

<REG FILES>

</REG FILES>

<MEMORY MAP>

<MEMORY MODE>DEFAULT</MEMORY MODE>

</memory_map>

</DEVICE>

</DEVICE_TABLE>

```

This is the **debug1.brd** board file created in *Using the Predefined Layouts in JTAG Editor*, p. 12. The first block of code contains comments that describe what the target reference design is set for; the next blocks of code define the devices included in the file.

For information on board file fields, see 4.3.1 XML Board File Fields, p.22.

**>**

**NOTE:** If you choose to modify a board descriptor file shipped with your system, it is best to save your modified file with a different name to prevent overwriting the default file.

### 4.3.1 XML Board File Fields

The board descriptor file contains comments, <DEVICE\_TABLE > fields, and one or more <DEVICE> field-sets. A <DEVICE\_TABLE> specifies common and rudimentary scan-chain (signal) operational functions and provides a list of <DEVICE> descriptions for each device sharing the JTAG interface.

### <DEVICE\_TABLE> Fields

### <TABLE\_MODE>

This field designates the scan-chain characteristics applicable to the devices on the chain. It can be set to FAST or SLOW. This also relates to the optimization implementation on the emulator. When in doubt, set it to SLOW.

### <TABLE\_CLOCK>

This field specifies the JTAG strobe rate, in MHz, for the information signals Test Data In (TDI) and Test Data Out (TDO). This is analogous to the emulator configuration option CF CLK *clock\_rate*. They are not always automatically synchronized, so check your emulator to make sure you have the CF CLK option set to the same clock rate specified in the board file. The fastest JTAG clock rate is 16 MHz.

### <TABLE\_MULTI>

Set this field to ENABLE if you are debugging multiple targets on the same JTAG interface. Otherwise set it to DISABLE.

### <TABLE\_TIED\_RESET>

Set this field to ON only if your target board's **RESET** and **TRST** signals on the JTAG interface are physically connected (tied together.)

### <DEVICE> Fields

### <NAME>

A reference name for the target device.

### <DESCRIPTION>

A reference description of the target device.

### <TYPE>

The valid types are MICROPROCESSOR, CPLD, FPGA, INTERFACE, and OTHER.

### <TARGET>

The CPU type. The run-time processes on Wind River emulators require this information in order to match the exact JTAG scan chain and JTAG-specific characteristics.

### <DESIGNATOR>

A mandatory field that Workbench uses to distinguish between devices. Typically this is set to U0, U1, U2....

Make sure you use a unique <DESIGNATOR> tag for each target device. Workbench does not allow two devices to use the same designator.

### <IR\_LENGTH>

Use this field to specify the length, in bits, of the target device's JTAG Instruction Register. To find this information, consult the manufacturer's specification for the target device.

### 4.4 Manually Creating XML Board Files

If you need a custom board file, it is usually easiest to take one of the generic board files from <code>installDir/workbench-version/dfw/build/host/boardfiles</code> and modify it to suit your needs. Remember to save it with a different name if you want to preserve the original file.

To create a board file that properly describes the scan chain on your target:

- 1. Open a text editor.

- 2. Begin the board file with the tag <DEVICE\_TABLE>.

- 3. Lay out the header block.

The first block of XML defines mode, clock speed, and status of multi-core debugging. An example would look like:

```

<TABLE_MODE>SLOW</TABLE_MODE>

<TABLE_CLOCK>16Mhz</TABLE_CLOCK>

<TABLE_MULTI>ENABLE</TABLE_MULTI>

<TABLE_TIED_RESET>ON</TABLE_TIED_RESET>

```

This example is set for slow mode, with a clock speed of 16 MHz; it is enabled for multi-core debugging, and it is set to issue RST reset commands (which affect all cores) rather than IN reset commands (which affect only one core.)

The next blocks of XML define the devices included in the file. Workbench needs this information so that it can position the devices in the correct location in the 25-bit data stream. The physical location of each device can also be determined by its position in the board descriptor file.

4. Lay out the block for the first device.

A device block begins with the tag <DEVICE>. An example would look like:

<DEVICE>

```

<NAME>MPC8260</NAME>

```

<DESCRIPTION>Motorola Power PC 8260 Processor

<TYPE>MICROPROCESSOR</TYPE>

<TARGET>MPC8260</TARGET>

<DESIGNATOR>U0</DESIGNATOR>

<IR\_LEN>8</IR\_LEN>

</DEVICE>

This example describes a PowerPC 8260 target.

5. Repeat Step 4 for every device on the JTAG scan chain.

Your board file must list the devices included on your scan chain in the same order as they are physically laid out on the target. If the board file and the physical scan chain do not match, the board file for your target will not work.

When you are finished, your board file should look something like this:

```

<DEVICE_TABLE>

```

```

<TABLE_MODE>SLOW</TABLE_MODE>

```

<TABLE\_CLOCK>16Mhz</TABLE\_CLOCK>

```

<TABLE MULTI>ENABLE</TABLE MULTI>

<TABLE TIED RESET>OFF</TABLE TIED RESET>

<DEVICE>

<NAME>MPC8260</NAME>

<DESCRIPTION>Motorola Power PC 8260 Processor

<TYPE>MICROPROCESSOR</TYPE>

<TARGET>MPC8260</TARGET>

<DESIGNATOR>U0</DESIGNATOR>

<IR_LEN>8</IR_LEN>

</DEVICE>

<DEVICE>

<NAME>PPC750FX</NAME>

<DESCRIPTION>IBM Power PC 750FX Processor

<TYPE>MICROPROCESSOR</TYPE>

<TARGET>PPC750FX</TARGET>

<DESIGNATOR>U1</DESIGNATOR>

<IR LEN>8</IR LEN>

</DEVICE>

</DEVICE TABLE>

```

This example describes two targets, but you can add as many <DEVICE> blocks as you need to describe your JTAG scan chain.

6. When you are finished, save the file with the extension **.brd**.

### 4.5 Layout, Routing and Design Considerations

Wind River recommends the following routing requirements to minimize the possibility of JTAG communication failures.

- Position the first device in the JTAG scan chain between one half and two

thirds of the total routing length of the chain. This will minimize the reflections

back to the first device in the scan chain.

- Route the TCK and TMS signals to approximately the same length from device to device.

- Provide a series dampening resistor as close as possible to the JTAG header for the TCK, TMS and TDI signals. A series resistor should also be positioned on the TDO output from device to device, and positioned as close as possible to the source. The last device in the JTAG scan chain should minimize reflections. These resistor values can be adjusted to match the impedance of the circuit board trace.

- Position the last device in the scan chain as close as possible to the JTAG connector to minimize the trace length of the TDO signal back to the emulator.

- Provide the ability to bypass any and all devices except the processor in the scan chain with zero-ohm resistors or jumpers.

### 4.6 JTAG Timing Parameters for Wind River Emulators

The following table describes JTAG timing parameters for the Wind River probe and Wind River ICE.

Table 4-1 JTAG Timing Parameters

| TCK           | TDO               | TDO               | TMS               | TMS               | TDI          | TDI      |

|---------------|-------------------|-------------------|-------------------|-------------------|--------------|----------|

|               | Min Prop<br>Delay | Max Prop<br>Delay | Min Prop<br>Delay | Max Prop<br>Delay | Min<br>Setup | Min Hold |

| Negative Edge | -3 ns             | +3 ns             | -3 ns             | +3 ns             |              |          |

| Positive Edge |                   |                   |                   |                   | 23 ns        | 3 ns     |

# **5**OCD Connections

- 5.1 Debug Connections 27

- 5.2 Creating a Target Connection 28

### 5.1 **Debug Connections**

To create a target connection, create projects, and download code, you need a Wind River Probe or a Wind River ICE SX.

For software-only tests, you can create a simulated connection using the Wind River Instruction Set Simulator (ISS), which is available to all users of Wind River Workbench OCD Edition. For instructions on using the Instruction Set Simulator, see the *Wind River Workbench On-Chip Debugging Guide*.

The instructions in this document use a Wind River Probe connecting to a PowerPC750FX target. The process for connecting with the ICE is similar; for instructions on connecting with a Wind River ICE SX, see the *Wind River ICE SX for Wind River Workbench Hardware Reference*.

### 5.2 Creating a Target Connection

To create a target connection using a Wind River Probe, use the following steps:

- 1. Open Wind River Workbench.

- Right-click in the Target Manager view and select New Connection.

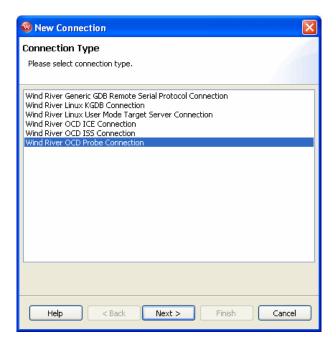

The Connection Type dialog appears, as shown in Figure 5-1.

Figure 5-1 Choose Connection Type

Select Wind River OCD Probe Connection and click Next.

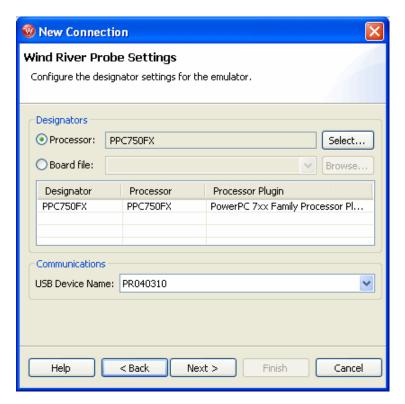

The Processor Selection dialog appears, as shown in Figure 5-2.

Figure 5-2 Processor Selection

- 4. Click **Select**. From the list that appears, expand MPC7xx and select MPC750FX.

- Click **OK**.

You are returned to the **Processor Selection** dialog.

6. Click Next.

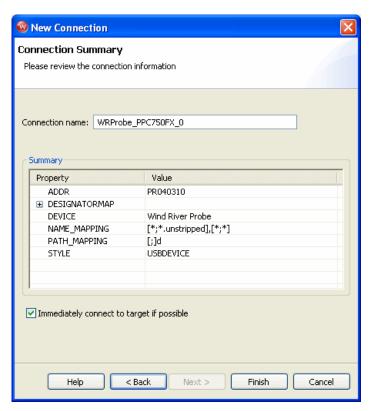

The connection wizard passes through four screens: Target Operating System Settings, Memory Mapping, Object Path Mappings, and Target State Refresh. For the purposes of this chapter you do not need to use these screens. Click Next until you come to the Connection Summary, as shown in Figure 5-3.

Figure 5-3 Connection Summary

Make sure that the Immediately connect to target if possible checkbox is selected and click Finish.

Workbench creates a target connection called **WRProbe\_PPC750FX** in the **Target Manager** view.

8. In the **Target Manager** view, click on the "+" sign next to the WRProbe\_PPC750FX target connection name to expand it.

Before Workbench can actually talk to the processor on the target system, Workbench must attach to the core.

9. Right-click on PPC750FX [connected - stopped] and select Attach to Core.

Workbench is now attached to the core, and able to talk to the processor. Workbench switches to displaying the **Device Debug** perspective.

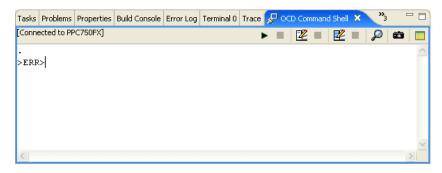

In the Workbench toolbar, select **Window > Show View > OCD Command Shell**. The **OCD Command Shell** opens, as shown in Figure 5-4.

Figure 5-4 OCD Command Shell

The prompt in the **OCD Command Shell** will read either **>BKM>** (background mode) or **>ERR>** (error.)

There are several reasons an **>ERR>** prompt might appear; these will be addressed further on.

The next step is to configure the emulator by setting certain configuration options, as described in *6. Tool Configuration*.

Wind River Board Bring-Up Guide, 1.0

### Tool Configuration

- 6.1 Introduction 33

- 6.2 Tool Configuration 34

### 6.1 Introduction

Wind River emulators can be configured in several different ways to specify various settings such as electrical properties, connection logic, and clock rate. To configure these settings Workbench uses configuration options, or CF options, which can be set in the OCD Command Shell.

This document only describes the most important CF options, ones that are common to all Wind River-supported processor families. For a full description of all Wind River CF options sorted by processor family, see the Wind River Workbench On-Chip Debugging Configuration Options Reference.

### 6.2 **Tool Configuration**

At the prompt in the **OCD Command Shell** (either **>BKM>** or **>ERR>**) enter the command **CF** with no arguments.

This displays a list of all CF options available for your target processor, along with their current settings.

```

>ERR>cf

Set BreakPoint

SB[SB, IHBC] = SB

Vector Table Location

VECTOR[HIGH,LOW,IGNORE] = LOW

Monitor Target reset

RST[YES, NO, HALT, RUN] = YES

Target CPU

TAR[AUTO, 603E, EC603E, 603P, 603R, 740, 745,

750,750CX,750CXE,750FX,750GX,755,7400,7410] = 750FX

SLAVE[NONE, 8260] = NONE

Target CPU( SLAVE )

Slave IMMR reset value

SLIMMRVAL[AUTO, VALUE] = AUTO

JTAG clock rate (MHz)

CLK[0.025...100, AUTO] = 16

AIMMRER[OFF,START and END] = OFF

Application IMMR Exclusion Range

Application IMMR Value

AIMMRVAL[VALUE] = 0e000000

Real time Preservation

RTP[YES,NO] = NO

Little Endian Mode

LENDIAN[YES, NO] = NO

Processor Mode

MODE[32,64] = 64

Download Mode

DLD[NORMAL, 8] = NORMAL

Emulator HRESET Control

HRESET[ENABLE, DISABLE] = ENABLE

Data Parity Checking

PAR[YES,NO] = NO

Set Work Space

WSPACE[BASE and SIZE] = 00000000 77c

Set Stack Range

STACK[OFF / LOWER and UPPER] = OFF

Target Console Redirection

TGTCONS[BDM,COM1,COM2] = BDM

Drive TReset line

TRESET[OPENC, ACTIVE] = ACTIVE

Reset Pulse Length N*1ms

RPL[1..600] = 1

Sense Power via HRESET

SPOWER[YES, NO] = YES

Power On Reset Length N*1ms

PONR[0..500] = 0

RESET[HRESET, SRESET, HRESET_UNFILTER,

CPU Reset Type

SRESET_UNFILTER] = HRESET

TRPEXP[YES, NO, SOI, BREAKPOINTONLY] = YES

Trap exception

Issue an IN on coldstart

INCOLD[YES,NO] = YES

Display L2 Data Cache Warning

L2WARNING[YES,NO] = NO

MMU[ENABLE, DISABLE] = DISABLE

Memory Management Unit Mode

Load Boot Table On IN

BL[ENABLE, DISABLE] = DISABLE

Trigger In Report Mode

BRKREP[REPONLY, BRKREP] = BRKREP

TMD Mode

TMD[ENABLE, DISABLE] = DISABLE

Run Counter Length

RCL[1000..FFFF] = 1000

Delay after Reset Nms

DRST[0..10000] = 25

```

### 6.2.1 Clock Rate

The CLK option controls the rate at which the JTAG clock (or BDM clock) clocks debug commands to the target.

Available clock rates, and default settings, vary between processor families. Enter CF at the prompt and look for CLK in the list of CF options to see the available clock rates for your target.

For a PowerPC 750FX target, the available rates (shown above) range from 0.025 to 100. The default is 16. To change the clock rate, say from 16 to 32, use the following command:

>ERR>cf clk 32

### 6.2.2 Drive TRESET Line

The TRESET option controls the logic applied to the target reset (TRESET) signal on the target.

The option can be set to **OPENC** or **ACTIVE**. It is set to **ACTIVE** by default.

When set to **ACTIVE**, the emulator uses transistor-transistor logic (TTL.) The emulator drives the TRESET signal to both active and inactive states. On some targets, the conditioning resistors cause excessive rise or fall time on the signal when returning to an inactive state. This excessive time can cause the processor to come out of reset in an incorrect state.

When set to **OPENC**, the emulator uses open-collector logic. The active driver is released by tri-stating the line and allowing conditioning resistors on the target to return the signal to the non-active state.

If you are driving the TRESET signal with an external line, you should set the emulator to use open-collector logic. Otherwise you could have an external line driving the TRESET signal LOW while the emulator is driving it HIGH, thus causing bus contention and possible damage to the target or the emulator.

To set the TRESET option to **OPENC**, use the following command:

>ERR>cf treset openc

To change it back, use the following command:

>ERR>cf treset active

### 6.2.3 Monitor Target Reset

The emulator continuously monitors the TRESET signal. If a target reset occurs, one of the following actions may be taken:

- YES If a target reset occurs it is reported to the user, and the target is forced out of background mode.

- NO If a target reset occurs it is ignored. This is normally used if the code contains a reset instruction, which causes a reset to the external hardware, but does not reset the core.

- HALT If a reset occurs, the target is trapped at the restart vector.

- RUN If a reset occurs, the target is restarted and remains in background mode.

By default, this option is set to YES. When set to YES, the target will start running code after each reset. If you are doing low-level work -- for example, if you are examining register settings -- you may want the target to halt after a reset so you can get a target snapshot. To set this option to halt the target on a reset, use the following command:

>ERR>cf rst halt

To change it back, use the following command:

>ERR>cf rst yes

### 6.2.4 Emulator HRESET Control

By default, the emulator asserts the hardware reset (HRESET) signal when initializing the hardware.

To configure the emulator not to assert the HRESET signal when it initializes the board, use the following command:

>ERR>cf hreset disable

To change it back, use the following command:

>ERR>cf hreset enable

### 6.2.5 CPU Reset Type

As stated above, the emulator asserts the hardware reset (HRESET) signal when initializing the hardware. You can configure the emulator to assert the software reset (SRESET) signal on an initialization instead.

To configure the emulator to assert the SREST signal instead of the HRESET signal when it initializes the board, use the following command:

>ERR>cf reset sreset

To change it back, use the following command:

>ERR>cf reset hreset

You can also set this option to **HRESET\_UNFILTER** or **SRESET\_UNFILTER**. With the **\_UNFILTER** argument added, The emulator will not sample the reset signal when it initializes the board.

### 6.2.6 Saving Changes

Most changes to configuration options do not take effect until you initialize the board, as described in 7. *Board Initialization*.

Wind River Board Bring-Up Guide, 1.0

### **7**Board Initialization

- 7.1 Introduction 39

- 7.2 Background Mode 40

- The INN Command 43

- 7.4 Registers 43

### 7.1 Introduction

In order to establish communications with your target, you must first initialize it. Also, if the code you are running on your target causes the connection to be lost, you must initialize the target to restore that connection. Initialization is also required if you change the register settings in the emulator and want them to be reflected in the target.

The target is initialized whenever you first establish a connection using your emulator. If you need to initialize the target when you are debugging, you can do it using the IN or INN initialization commands, as described in this chapter.

### 7.2 Background Mode

In order for the emulator to work with the target, it must stop the target CPU and put the target in background mode. When the target is in background mode, a >BKM> prompt appears in the OCD Command Shell.

If an >ERR> prompt appears in the OCD Command Shell, the target is not in background mode.

### 7.2.1 The IN Command

The IN command does two different things. First, it places the target board into background mode. Second, it copies all of the register information that is stored in the emulator's NVRAM down to the target.

To initialize the board and enter background mode, enter the following command:

```

>ERR> in

```

The IN command may fail for several reasons. For example, if you have not connected power to the target board, the output will resemble the following:

For a list of the tests the emulator runs during an **IN** sequence, see 7.2.2 Set Verbose *On*, p.40.

### 7.2.2 Set Verbose On

To see the tests the emulator is running while attempting to enter background mode, put the emulator in verbose mode using the following command:

### >ERR>set verbose on

Then enter the IN command again.

Here is a brief description of the tests with some possible reasons why each test would fail.

### **Testing Communications to Hardware Interface**

This tests the hardware connectivity, and examines the communications path between the host and the emulator. If the test fails, ensure that you have the power properly connected and turned on, that the emulator is correctly connected to the host computer, and that your emulator hardware is properly connected to the target.

### **Driving HRESET to be High**

This function tests the RESET signal to verify that it is HIGH. The emulator is not driving the RESET signal during this test, so the target must drive the RESET signal via a pull-up resistor. If this test fails, check to see if the target board has a pull-up resistor on the RESET signal to the HRESET pin of the connector. Also, check the target board reset logic and verify that it is not continually driving RESET LOW.

### **Driving HRESET to be Low**

The RESET signal is a bi-directional signal for your unit. The emulator drives the RESET signal LOW and clocks it back in to verify that it is LOW. If this test fails, you may have contention on your RESET signal. Check to see if a device on your target board is continually driving RESET HIGH. Verify that the device on your target board that is driving the RESET signal is an open-collector device with a pull-up resistor.

### Attempting JTAG communication

During this test, the emulator stops the processor and attempts to establish JTAG communications. If this fails, check to see that your hardware is connected properly, and that the tests preceding this one passed accordingly. It is also possible that there is contention on your board.

### Waiting for HRESET to be Released

The emulator only drives RESET low for a specified period of time. After RESET is driven LOW for the allotted time, it tri-states the RESET driver and clocks the RESET signal back in to see if the RESET signal went high. It continues to check for RESET to go high until is sees it go high or until you type **Ctrl+X**. If this test fails,

check to see if your target board reset logic is still driving the RESET signal LOW. Also check that your target board has a pull-up resistor to drive RESET HIGH.

### **Testing for target STOP State**

This test verifies that the processor stopped during the preceding JTAG Communications test by polling the processor status. If the target is still running, this test fails.

### **Comparing Target CPU With CF Setting**

This test verifies that you are properly configured for the appropriate target processor by comparing the processor type on your target with the processor type specified in your board file. If the test fails, use the CF TAR command to properly configure your target. For example, if you are using a PPC750FX target, and this test fails, enter the following commands:

```

>ERR>cf tar 750fx

>ERR>in

```

### Attempting to Locate IMMR register

This test only completes for PowerPC 82xx targets. It attempts to verify the location of the IMMR register, which serves as a pointer to all of the other registers. If it fails, none of the internal registers are accessible. If the test fails, check the reset configuration word, located in Flash, and ensure that it is set to the correct value. To find the correct value for the reset configuration word for your target, see your target's target.ref file, located in <code>installDir/vxworks-6.x/target/config/yourTarget</code>.

### **Loading Internal Registers**

Once background communications are established, the emulator downloads register values from the debugger NV-RAM to the target. It will only download register values for those register groups that are enabled. If this test fails, see the information in 7.3 *The INN Command*, p.43.

### **Testing JTAG Communication**

This test examines the JTAG communication between the emulator and the target using the internal clock rate for which the emulator is configured. If this test fails, set the internal clock to a lower rate using the following command:

```

>ERR>cf clk value

```

### Attempting to restore CPU context

This test restores the processor scan chains.

### 7.3 The INN Command

In order to get a processor into background mode, the emulator asserts the RESET line of the processor and then releases it. The processor and its peripherals on the target board are forced into their reset state, and all of the internal registers are forced to their manufacturer's reset value.

The INN command places the target in background mode without overwriting the target's registers, leaving them in their default reset state for the processor.

If the **IN** command fails to put the target in background mode, enter the following command:

Generally, if an IN command fails but an INN succeeds, it is usually caused by incorrect register values in the emulator's NVRAM.

To configure register values, see 7.4 Registers, p.43.

### 7.4 Registers

Your emulator includes an area of non-volatile memory (NVRAM) where you may store register settings for a target.

Once the register values are present in NVRAM, they are automatically loaded to the target after each cold start, warm start, or **IN** initialization command. You can select which register values are written to the target by enabling and disabling the appropriate register groups.

Wind River uses low-level **SCGA** commands to configure registers. Since configuring registers manually would require entering a large number of **SCGA** commands, Wind River provides *register files* for many targets. A register file is a Workbench-specific script that you can execute in the **OCD Command Shell**.

Register files are ASCII files using the extension .reg. For example, the register file for the Wind River PPC750FX target is ppmc750fx.reg, located in <code>installDir/workbench-2.x/dfw/build/host/registers/PowerPC/7xx/WindRiver\_PPMC</code>.

### 7.4.1 Downloading a Register File

To download a register file to the emulator, use the following steps:

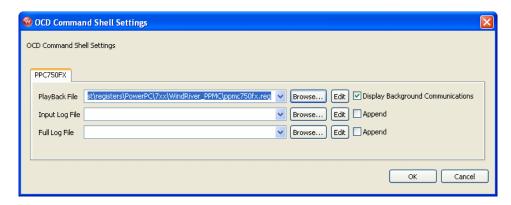

In the OCD Command Shell, click the Settings button.

The OCD Command Shell Settings dialog appears, as shown in Figure 7-1.

Figure 7-1 OCD Command Shell Settings

- 2. Next to the **PlayBack File** field, click **Browse**.

- 3. Navigate to the register file you wish to use and click **Open**.

- 4. Click **OK**.

- 5. In the OCD Command Shell, click the Playback File button.

The register file you selected is downloaded to your target. The commands from the file appear in the **OCD Command Shell**.

This procedure only sets the register values in the emulator's NVRAM, not on the target. To copy the register values from the emulator to the target, you must initialize the target with the **IN** command:

```

>BKM>in

```

Only enabled register groups are copied to the target.

### 7.4.2 Enabling and Disabling Register Groups

If you look at the **ppmc750fx.reg** register file, you will see that it ends with several lines that begin **CF GRP ENABLED**. Registers are stored in logical register groups. When you issue an **IN** command, the emulator only copies down register settings for register groups that are enabled. Register groups that are disabled on your target do not have register data transferred.

Disabling a register group enables you to view the target register value, but prevents it from being overwritten during target initialization.

**NOTE:** If you change a register value directly on the target of a register group that is disabled, that register does not get overwritten by the emulator during an initialization. Note, however, that the processor may still reset that register value to the processor default during a target initialization.

To enable or disable a register group on your target, use the following steps:

1. At the **>BKM>** prompt, type the command **CF GRP**.

The first register group appears, as shown below:

```

>BKM>cf grp

Group (CF GRP (M/S) Name = ENABLED/DISABLED

CUSTOM (0=Disable 1=Enable) Enabled >

```

The name of the register group is displayed, along with its current status (either **ENABLED** or **DISABLED**).

- 2. Type **1** to enable the group or **0** to disable it.

- 3. To leave the setting as it is and advance to the next register group, press the ENTER key without typing 0 or 1.

- 4. Continue through the list of register groups enabling and disabling them as required.

5. When the register groups are enabled or disabled, type **CF UPLOAD GROUP** at the **>BKM>** prompt.

This displays a list of all of the register groups on your target with their current settings as shown below:

```

>BKM>cf upload group

CF GRP GT64260_CPU ENABLED ; GROUP

CF GRP GT64260_SDRAM ENABLED ; GROUP

CF GRP GT64260_DEVICE ENABLED ; GROUP

CF GRP GT64260_GPP ENABLED ; GROUP

CF GRP GT64260_MPP ENABLED ; GROUP

>BKM>

```

### 7.4.3 Modifying Registers Manually

Wind River supplies register files for Wind River evaluation boards, as well as for many third-party target boards.

If you are using a target for which Wind River does not supply a register file, you may have to create one. For instructions on creating register files, see the *Wind River Workbench On-Chip Debugging Guide: Configuring Registers*.

Remember that the register file sets the register values in the emulator NVRAM, not on the target. The emulator copies the values you set in its NVRAM down to the target when you initialize the target with an IN command. Without a register file, the NVRAM contains default register values, typically made for a Wind River evaluation board, which most likely are not suitable for your target. So the IN command will not set the target registers properly.

Some target processors, for instance most PowerPC targets, come with default register settings. If your target has default register settings, you can modify the registers directly on your on your target manually, at least to the point where you can download your boot ROM application code.

Remember that if you modify your registers manually, any initialization command or target reset will overwrite your changes.

To modify registers manually, use the **Registers** view in Workbench. The **Registers** view lets you view the bit-level detail for each register. The following sections describe the **Registers** view and the bit-level detail provided.

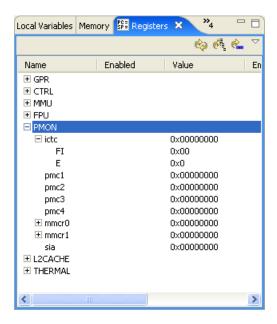

### The Registers View

When the **Registers** view is open in Workbench, all of the register groups for your target are displayed with + signs beside them. Clicking on a + sign expands the

register group, showing all of the registers that are included in that register group along with the value that they are currently set to. An example of an expanded register group is shown in Figure 7-2.

Figure 7-2 Expanded Register Group

NOTE: Figure 7-2 is only an example of an expanded register group. The groups and the register values vary widely depending on your target architecture.

### **Bit-Level Detail**

You can view the bit-level detail for any register by clicking on the + sign beside the register in the register group.

NOTE: Before you can make any changes to your register settings, you need to enable the register group that contains the register you want to modify, so that the values download to the target when you initialize your system. If you do not enable the register group, you can still modify the settings in the emulator but not on the target. For more information, see 7.4.2 Enabling and Disabling Register Groups, p.45.

You can make changes to any of the register settings by modifying each of the bit-level settings for any register.

To modify bit-level values for your target, complete the following steps:

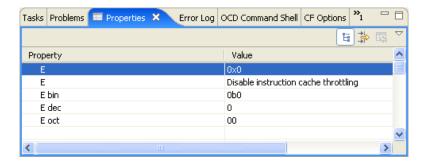

1. In the **Registers** view, double-click on the name of the register you wish to edit. This opens the **Properties** view, which shows the name of the register you have selected under the **Property** heading and its current setting under the **Value** heading, as shown in Figure 7-3.

Figure 7-3 Properties View

- 2. Select the value under the **Value** heading and edit it as necessary.

- 3. In the **Registers** view, click the **Refresh Values** icon. The register information reappears with your changes.

For more information on registers, including creating custom registers and register groups, see the *Wind River Workbench On-Chip Debugging Guide: Configuring Registers*.

When you have initialized your target and entered background mode, with a >BKM> prompt showing in the OCD Command Shell, you can proceed to test your hardware, as described in 8. Verifying Hardware.

### **V**erifying Hardware

- 8.1 Introduction 49

- 8.2 Setting a Workspace 49

- 8.3 Diagnostic Functions 50

### 8.1 Introduction

This chapter describes several tests and diagnostics you can use to verify that your hardware is working correctly.

### 8.2 Setting a Workspace

The workspace is an area of RAM on the target that the emulator uses to download the hardware diagnostic routines and flash programming algorithms.

You must tell your emulator where writable RAM is located on your target for this purpose.

Depending on the device family and type, this space is limited to under 2 KB. Note that more memory improves the speed of programming.

To configure the workspace, enter the parameters using the syntax

### **CF WSPACE** base size

where *base* is the start address, and *size* is the minimum number of bytes of target RAM required.

To find the base and size values for your target, consult your target's target.ref file, located in <code>installDir/vxworks-6.x/target/config/yourTarget</code>.

For a Wind River PPC750FX target, the base of the workspace is 00000000 and the size is 6000. To set the workspace, enter the command

```

>BKM>cf wspace 0 60000

```

This sets the workspace at address 0 with a size of 0x00006000 bytes.

### 8.3 Diagnostic Functions

Wind River Workbench provides a set of RAM and bus diagnostics and utilities that can be controlled by the emulator or run on the target.

Some of the following tests can run code directly on the target instead of through the emulator by selecting the **Run on Target** checkbox. This allows the test to run at the execution speed of the target processor.

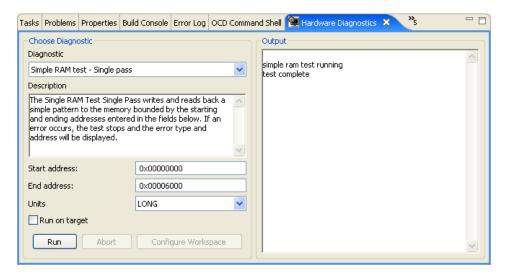

### 8.3.1 Simple RAM Test

This test writes and reads back a simple pattern to the memory bounded by the starting and ending addresses entered in the **Start Address** and **End Address** fields. If an error occurs, the test stops and the error type and address are displayed in the **Output** field.

The first diagnostic to be run is a Simple Ram Test on the area of memory used by the workspace.

1. In the Workbench toolbar, select **Window > Show View > Hardware Diagnostics**.

- 2. In the **Diagnostic** field, select **Simple RAM Test Single Pass**.

- 3. The workspace cannot be used to test itself, so make sure the **Run on target** checkbox is unchecked.

- 4. In the **Start Address** field, enter **0**.

- 5. In the **End Address** field, enter **6000**.

- 6. In the **Units** field, select **LONG**.

- Click Run.

Workbench displays the test result in the **Output** field. The output of a successful test will resemble that in Figure 8-1.

Figure 8-1 Successful Simple RAM Test

If the test fails, the **Address Bus Test** diagnostic and the **Data Bus Test** diagnostic may determine the cause of the failure; see *8.3.5 Bus Tests*, p.54.

If the RAM test of the memory used by the workspace passed, the rest of the memory in the target system can now be tested at full bus speed.

- 1. In the Diagnostic field, select Simple RAM Test Single Pass.

- 2. Select the Run on Target checkbox.

- 3. In the Start Address field, enter 14000.

- 4. In the **End Address** field, enter **20000000**.

- 5. In the **Units** field, select **LONG**.

- 6. Click **Run**.

Workbench displays the test result in the **Output** field.

If the message **Test Complete** appears, then the diagnostic passed.

If the test fails, try re-seating the SDRAM module and repeat the test. If the test still fails, then run the **Address Bus Test** diagnostic and the **Data Bus Test** diagnostic to determine the cause of the failure. See *8.3.5 Bus Tests*, p.54.

### 8.3.2 Full RAM Tests

A Full RAM test writes a "walking" 1 on each bit of RAM and reads it back. This is a very lengthy test and can detect bus configuration errors, typically on a new printed circuit board.

This test sets and then clears each bit to try to locate memory defects bounded by the starting and ending addresses entered in the **Start Address** and **End Address** fields. If an error occurs, the test stops and the error type and address will be displayed in the **Output** field.

**NOTE:** A complete Full RAM test would take several years to finish, so make sure you specify a very small region of memory to be tested.

Full RAM tests are designed to check for cell disturbance and addressing problems. These tests perform the following actions:

A **Single Pass** test will run the test only once. A **Continuous** test will repeat the test over the same address until you click **Stop**.

- In the Diagnostic field, select Simple RAM Test Single Pass.

- Select the Run on Target checkbox.

- 3. In the **Start Address** field, enter **0**.

- 4. In the **End Address** field, enter **0000100**.

- In the Units field, select LONG.

- Click Run.

Workbench displays the test result in the **Output** field.

If the message **Test Complete** appears, then the diagnostics passed.

If the test fails, try re-seating the SDRAM module and repeat the test. If the test still fails, then run the **Address Bus Test** diagnostic and the **Data Bus Test** diagnostic to determine the cause of the failure. See *8.3.5 Bus Tests*, p.54.

### 8.3.3 CRC Calculation

Workbench and the emulator support the calculation of a Cyclic Redundancy Check (CRC) on all addresses in the range specified. The CRC test will checksum a block of data in the target for the address range you specify in the **CRC Calculation** dialog. The CRC algorithm is based on the following polynomial:

$$x^{16} + x^{15} + x^{2} + 1$$

Workbench uses this polynomial as follows:

Workbench reads a location and uses the value read, *x*, to calculate the CRC. Then Workbench adds the result to the value calculated for the previous address. This process continues until Workbench has checked the entire specified memory range.

The CRC sum will be returned if the communications with the emulator and target are working. To interrupt the test, click **Stop**.

### 8.3.4 Scope Tests

### **Read From Location**

The Read From Location Scope Test performs a memory read of designated length from the address entered in the **From Address** field.

### **Write To Location**

The Write To Location Scope Test performs a memory write of designated length of the value entered in the **Data Value** field to the address in the **To Address** field.

### Write and Complement

The Write and Complement Scope Test performs a memory write of designated length of the value entered in the **Data Value** field to the address in the **To Address** field; the value is then complemented.

### Write Rotating Value

The Write Rotating Value Scope Test performs a memory write of the value entered in the **Data Value** field to the address in the **To Address** field. The value is then rotated through all of the bit positions with respect to the designated length of the memory address.

### Write Then Read

The Write and Read Scope Test performs a memory write of designated length of the value entered in the **Data Value** field to the address in the **To Address** field; the value is then read back.

### 8.3.5 Bus Tests

### **Address Bus Test**

This test detects faults in the address bus over the range bounded by the starting and ending addresses entered in the **Start Address** and **End Address** fields. This test can be interrupted by clicking the **Stop** button.

### **Data Bus Test**

This test detects faults in the data bus over the range bounded by the starting and ending addresses entered in the **Start Address** and **End Address** fields. This test can be interrupted by clicking the **Stop** button.

When you have tested your hardware successfully, you must test your ability to read and write memory, as described in 9. *Testing Memory*.

## 9 Testing Memory

- 9.1 Introduction 55

- 9.2 Testing Memory 55

### 9.1 Introduction

Before handling more complex application code, the target system must be able to handle low-level assembly instructions.

Wind River Workbench includes a simple diagnostic to test the target's ability to write to memory, set breakpoints, and run and step code. This diagnostic writes a loop of NOP instructions at a specified memory address.

### 9.2 **Testing Memory**

To run the memory diagnostic, use the following steps.

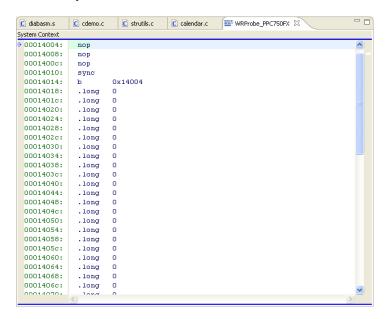

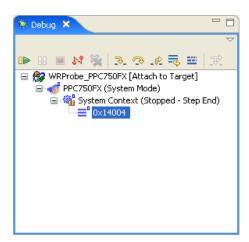

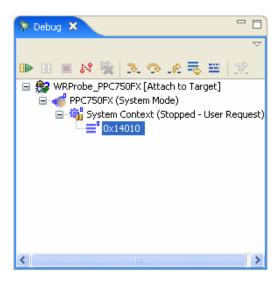

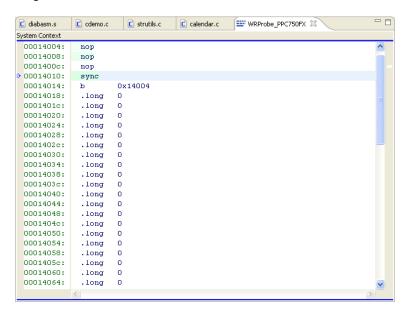

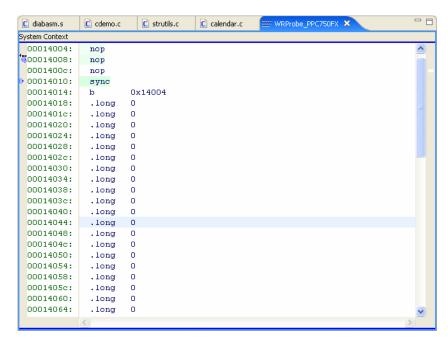

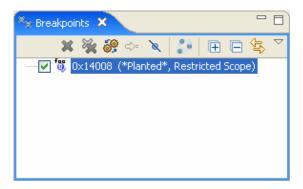

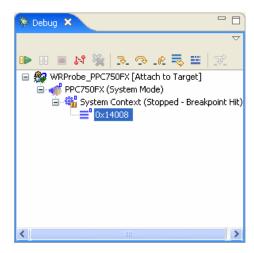

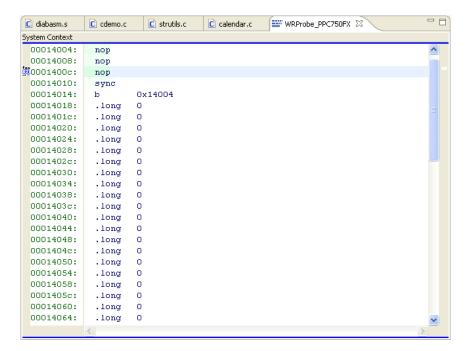

1. At the **>BKM>** prompt in the **OCD Command Shell**, enter **DF E 14000**. This writes a NOP loop at address 0x14000.

### 2. Enter the command DI 14000.

This command disassembles the instructions at 0x14000.

### 3. Enter the command SR PC 14000.

This command sets the Program Counter to address 0x14000.

The output should resemble that shown below.

```

>BKM>df e 14000

>BKM>di 14000

$00014000 : 0x60000000 :ppc nop

$00014004 : 0x60000000 :ppc nop

$00014008 : 0x60000000 :ppc nop

$0001400C : 0x60000000 :ppc nop

$00014010 : 0x7C0004AC :ppc sync

$00014014 : 0x4BFFFFF0 :ppc b

0x14004

$00014018 : 0x00000000 :ppc dc.1

0x0

$0001401C : 0x00000000 :ppc dc.1

$00014020 : 0x00000000 :ppc dc.1

0x0

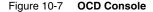

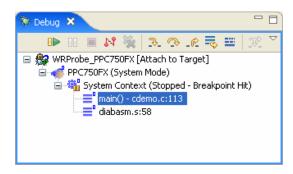

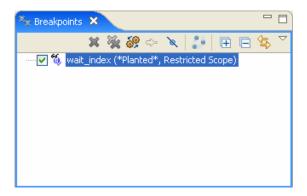

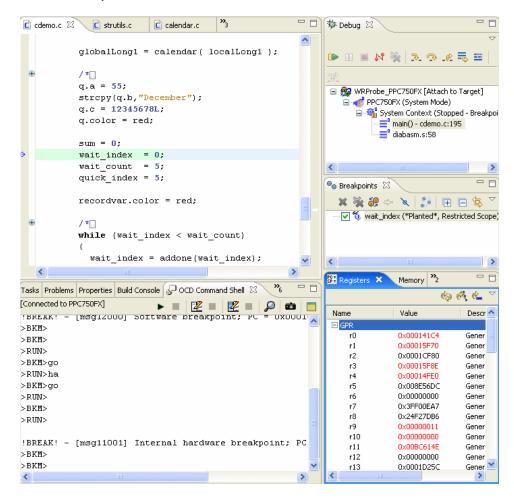

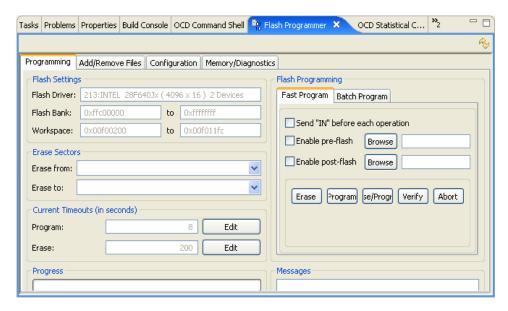

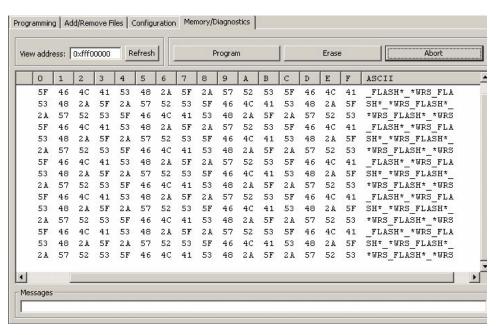

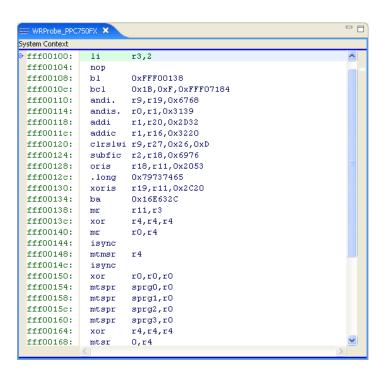

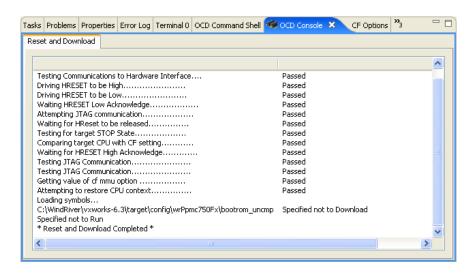

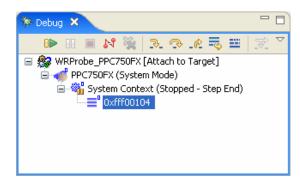

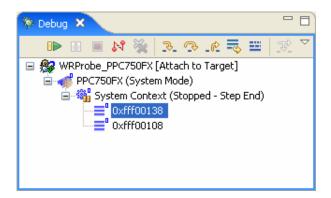

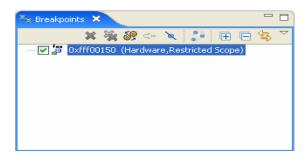

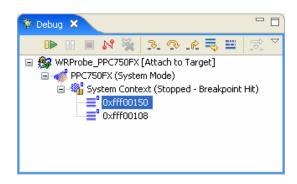

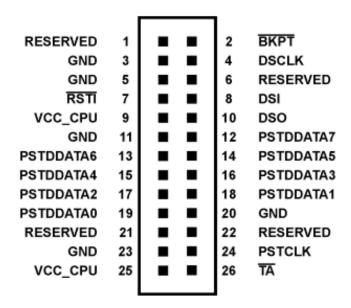

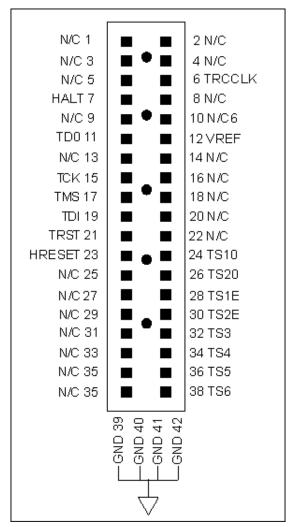

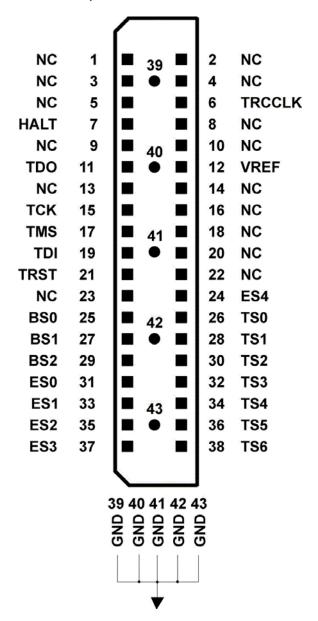

0x0