### SECTION 8 - INPUT/OUTPUT SECTION

### 8.1. GENERAL DESCRIPTION

### 8.1-1. OBJECTIVES

To present the general description of the I/O Section.

#### 8.1-2. INTRODUCTION

The I/O section is responsible for all communication in the form of control signals and word transfers with peripheral equipment.

### 8.1-3. REFERENCES

<u>UNIVAC 1219 Technical Manual</u>, Volume I, Paragraphs  $1-5\underline{d}$ ,  $3-6\underline{c}(2)$ , and  $4-3\underline{a}$  through  $4-3\underline{e}$ .

### 8.1-4. INFORMATION

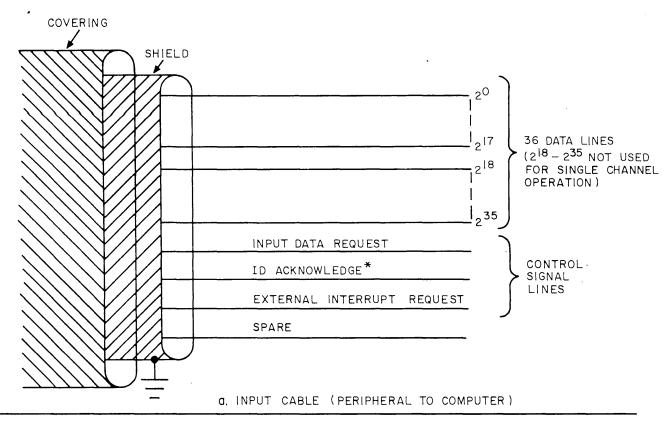

a. Channels, I/O Cable, and Chassis Assignment. The 1219 Computer is able to communicate with a maximum of 16 peripheral devices. Each communication path is referred to as a channel. The channels are numbered 0-178. Each data word transfer involves a maximum of 18 bits or 36 bits in parallel for single or duel channel operation, respectively. Each channel has an associated input cable and output cable. The shielded cables consist of twisted pairs of data or signal lines and their individual ground return lines. Refer to figure 8.1-1 and UNIVAC 1219 Technical Manual, Volume I, Section 2, table 2-2 for the cable description. The I/O control signals are discussed later in this sheet.

The logic for the 16 channels is distributed among the four I/O chassis, with each chassis controlling four channels. Depending upon the number of channels required, all four I/O chassis may not be present. The number of channels may be any multiple of four up to sixteen. Refer to table 8.1-1 for the channel/chassis assignment.

| CHASSIS | CHANNELS       |

|---------|----------------|

| 2       | 0, 2, 4, 6     |

| 1       | 1, 3, 5, 7     |

| 10      | 10, 12, 14, 16 |

| 9       | 11, 13, 15, 17 |

TABLE 8.1-1. I/O CHANNEL/CHASSIS ASSIGNMENT

NOTES: EACH LINE IS TWISTED WITH A GROUND RETURN LINE (NOT SHOWN).

\*ACKNOWLEDGE SIGNALS ARE SENT FROM COMPUTER TO PERIPHERAL, ALL OTHER SIGNALS

ARE SENT TO COMPUTER FROM PERIPHERAL.

Figure 8.1-1. I/O Cables

b. Interface. This term refers to the characteristics involved in the mating together of two pieces of equipment so as to enable data or signal exchange between them. All I/O factors such as voltage levels, signal duration, signal rate, and line impedance can be considered under the topic of interface. There are two types of interface employed in this computer. Refer to table 8.1-2 for the basic interface characteristics.

|                | ,                       |                             |                                |

|----------------|-------------------------|-----------------------------|--------------------------------|

| Interface Type | Line Voltage Levels     | ID<br>Acknowledge<br>Signal | OD/EF<br>Acknowledge<br>Signal |

| Slow           | H = Ov (grd.); L = -15v | 14.725 ms                   | 14.375 ms                      |

| Fast           | H = Ov (grd.); L = -3v  | 2.725 ms                    | 2.375 ms                       |

TABLE 8.1-2. I/O INTERFACE CHARACTERISTICS

The acknowledges are signals sent from the computer to the peripheral device indicating the completion of a data word exchange. The signals are discussed later in this sheet.

The type of interface is selected by plug-in jumper cards. All four channels on a common chassis have the same type of interface. Of these four channels, the interface for data input to the computer need not be the same type as for output data operations. The type of interface used is primarily determined by the requirements of the peripheral equipment and cable length.

c. Data Exchange Rate. The time necessary to complete one data word exchange operation for single channel is four microseconds. The maximum I/O rate is one word exchange every two microseconds because of a two microsecond overlap of consecutive word exchange operations.

The type of interface affects the I/O rate because of the acknowledge timing. For example, the ID Acknowledge signal timing is common to the four channels of a chassis and prevents any input data operation on these channels while the signal is being generated. Likewise, the OD/EF Acknowledge signal timing will disable any output data operation on the four channels of a chassis. If dual channel operation (36-bit word transfer) is employed, the acknowledge timing will prevent another data exchange operation of the same type on any channel of the entire drawer (2 chassis). Dual channel operation is discussed in more detail later in this sheet. Refer to table 8.1-3 for the I/O rates.

## d. I/O Signals.

# 1. Data Request Signals.

a) <u>Definition</u>. Request signals are those which are sent from a peripheral device to the computer and cause the transfer of one data word. The request honoring operation requires the use of memory to output or input a word. Therefore, it disables the instruction sequences to stop the program during its 2 microsecond use of memory. The request operations use the I/01 and I/02-sequences.

| OTHER CONDITIONS                                            | MODE (WORD SIZE)               | FAST           | INTERFA        | CE              | SLO            | W INTERF       | ACE             |

|-------------------------------------------------------------|--------------------------------|----------------|----------------|-----------------|----------------|----------------|-----------------|

|                                                             |                                | ONE<br>CHASSIS | TWO<br>CHASSIS | FOUR<br>CHASSIS | ONE<br>CHASSIS | TWO<br>CHASSIS | FOUR<br>CHASSIS |

|                                                             | Single Channel<br>Dual Channel | 500<br>NA      | 500<br>250     | 500<br>250      | 83.3<br>NA     | 167<br>76.9    | 334<br>154      |

| Inputs Only or Outputs Only on Alternate Channels           |                                | 250<br>NA      | 500<br>167     | 500<br>250      | 41.6<br>NA     | 83.3<br>38.4   | 167<br>76.9     |

| Inputs Only or Out-<br>puts Only on Indi-<br>vidual Channel |                                | 167<br>NA      | NA<br>125      | NA<br>NA        | 41.6<br>NA     | NA<br>38.4     | NA<br>NA        |

| Alternate Inputs<br>and Outputs on In-<br>dividual Channel  | Single Channel<br>Dual Channel | 334<br>NA      | NA<br>250      | NA<br>NA        | 83.3<br>NA     | NA<br>76.9     | NA<br>NA        |

TABLE 8.1-3. DATA TRANSFER RATES (MAXIMUM)\*

## b) <u>Types</u>.

- 1) <u>Input Data Request (IDR)</u>. This signal is sent to the computer with a data word. The IDR requests the computer to accept the word.

- 2) Output Data Request (ODR). This signal requests the computer to output a data word to the peripheral device.

- 3) External Function Request (EFR). This signal requests the computer to output an external function word to the peripheral device. Usually, the external function word is used to control the peripheral device according to its bit configuration.

The EFR operation could also be used as a technique of outputting data to the peripheral device.

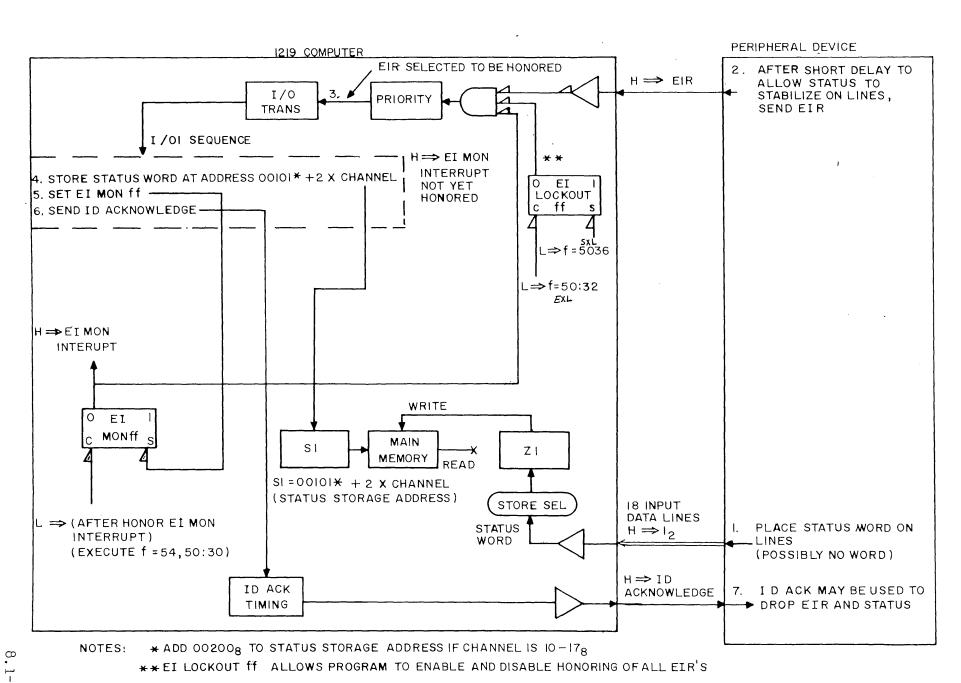

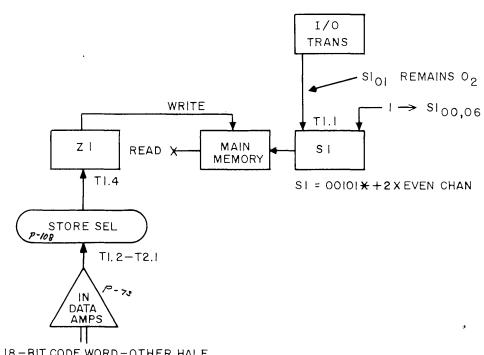

4) External Interrupt Request (EIR). This signal is sent to the computer possibly with a status word. Usually, the status word is used to inform the computer of the condition of the peripheral device as indicated by its bit configuration. For example, it may indicate timing errors, data word content errors, data word content errors, data word content errors, data ready condition, etc. The EIR requests the computer to accept the status word and inform the program of its occurrence by means of a program jump using the EIM interrupt signal. The EIM interrupt is discussed later in this sheet. The status word is stored in memory at the address  $00101_8 + 2x$  channel if the channel is 0-7 or address  $00301_8 + 2x$  channel if the channel is  $10-17_8$ .

<sup>\*</sup>All rates are in thousands of words per second.

Some equipments do not send status words but generate the EIR merely as means of interrupting the program. The EIR status word transfer operation could also be used as a technique of inputting data to the computer.

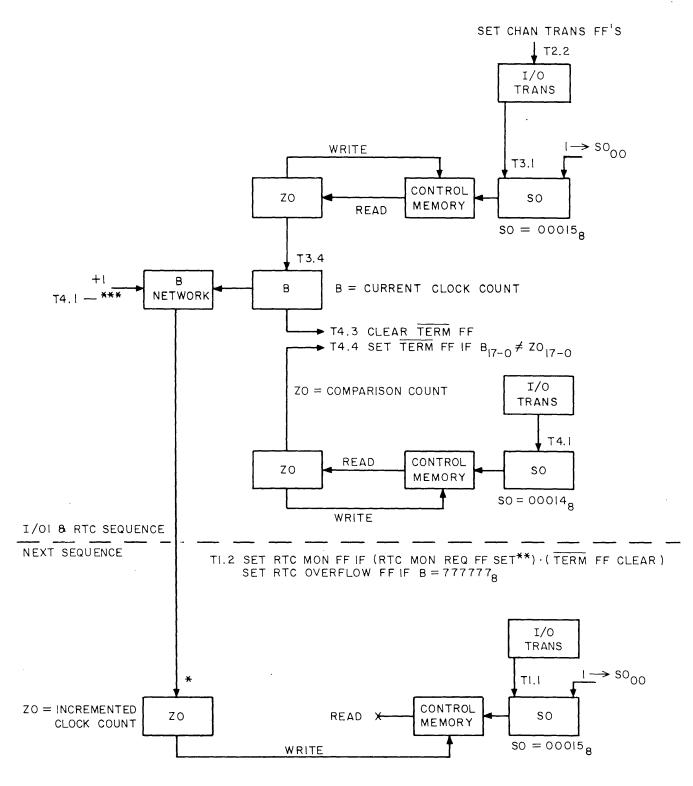

2. Real Time Clock Request (RTC Request). The RTC Request is generated by an internal, accurate oscillator operating at a frequency of 1024 pps. This oscillator is used to maintain a constantly updated 18-bit clock count in the control memory address 000158. The RTC request causes the computer to increment by +1 the content of this address. The addition is performed in an open-ended adder manner such that the incrementing of the 7777778 count results in the 0000008 count. This clock count can be preset to any value by the program and periodically referenced so as to time certain program events. The honoring of the RTC request can be prevented only by the RTC DISCONNECT switch.

Like the data request signals, the RTC request uses the I/Ol-sequence to perform the updating operation.

# 3. Interrupt Signals.

a) <u>Definition</u>. Interrupt signals are those which cause an interruption to the program in the form of a jump. Each type of interrupt has a special jump address assigned to it. The jump address is also referred to as the interrupt entrance register. The jump is made without disturbing P, such that a return jump instruction could be used at the jump address to retain P for later return to the program at the point of interruption as well as execute a second jump to an interrupt routine.

With the exception of the external sync interrupt, all interrupts are internally generated.

## b) Types.

## 1) Monitor Interrupts.

a. Input Data Monitor Interrupt (ID Mon). This signal can occur on any of the I/O channels. It indicates that the ID buffer set up by the program on its channel has been completed and that the program had desired the interrupt at the ID buffer termination. The ID buffer refers to the specified number of data words to be inputted on the particular channel.

This ID Mon interrupt causes a program jump to address  $00160_8 + 2x$  channel if the channel is 0-7 or address  $00360_8 + 2x$  channel if the channel is  $10-17_8$ .

The EF/OD Mon interrupt causes a program jump to address  $00140_8+2x$  channel if the channel is 0-7 or address  $00340_8+2x$  channel if the channel is  $10-17_8$ .

The EI Mon interrupt causes a program jump to address  $00100_8 + 2x$  channel if the channel is 0-7 or address  $00300_8 + 2x$  channel if the channel is  $10-17_8$ .

## 2) Special Interrupts.

a. RTC Overflow Interrupt. This signal is generated when the RTC request is honored and increments the clock count from 7777778 to 0000008. With the RTC oscillator operating at a frequency of 1024 pps, this interrupt occurs every 256 seconds. It can be prevented by the RTC DISCONNECT switch.

The RTC overflow interrupt causes a program jump to the control memory address  $00013_{\mbox{\scriptsize G}}.$

b. RTC Monitor Interrupt. This signal is generated during the honoring of the RTC request if the clock count in address  $00015_8$  (before incrementation) equals the content of the control memory address  $00014_8$ , and the interrupt was desired by the program. The comparison count in address  $00014_8$  must be set up by the program. The program must also execute the RTC instruction (f = 50:14) to enable the interrupt when the clock reaches this count. This instruction must be executed after each interrupt if another RTC monitor interrupt is desired.

The RTC monitor interrupt causes a program jump to the control memory address  $00012_{\mbox{\scriptsize R}}.$

which is directly generated externally. It is a non-channel type and is carried by a separate I/O cable. It can be used as a timing input from an external device or allow external control over the program.

The external sync interrupt causes a program jump to the control memory address  $\mathsf{00016}_8.$

The instruction-fault interrupt causes a program jump to the control memory address  $00000_8$  if the AUTO RECOVERY switch is in the down position or address  $00500_8$  (bootstrap) if the switch is in the up position. The interrupt also activates the PROGRAM FAULT indicator which can only be extinguished by master clear.

<u>e. Resume Fault Interrupt (Inter-Computer Time-Out Fault).</u> This signal occurs only during output data transfers to another computer. It indicates that the receiving computer did not accept a data word within a specified period of time. It is timed by the RTC operations; therefore, the RTC request must not be disconnected. The amount of time allowed for the acceptance of each data word is determined by the wiring configuration to examine a particular bit position of the RTC clock count. The time period allowed involves two changes of the bit tested.

When the interrupt occurs, it is necessary for the program to execute the SRSM instruction (f = 50:20). Otherwise, all EF and OD operations on the particular chassis involved will be disabled.

The resume-fault interrupt causes a program jump to the control memory address  $00011_{\Omega}$ .

e. Buffers and Address Control Words. Buffer refers to the number of words set up by the program to be transferred. ID, OD, and EF buffers are established by the instructions IN (f=50:11), OUT (f=50:12), and EXF (f=50:13), respectively. The two addresses immediately following these instructions in the program are reserved as the buffer limits. Buffer limits are the initial and final addresses for the data to be transferred.

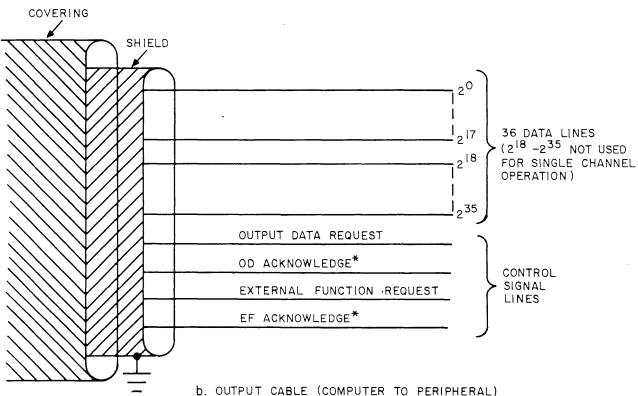

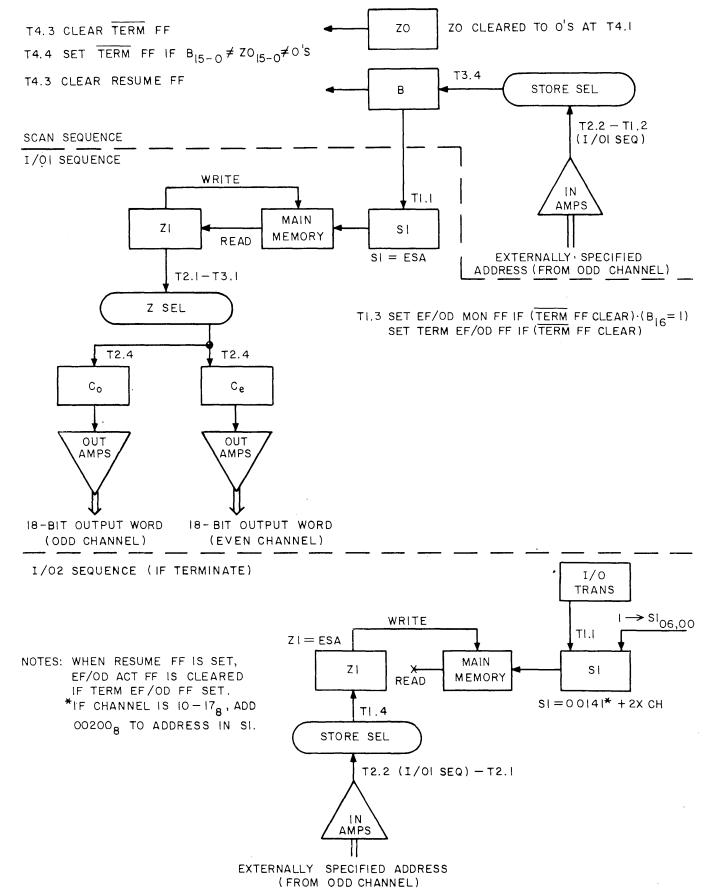

The terminal address control word (TACW) immediately follows the buffer instruction in the program. Among other things, it contains the 16-bit final data address. For example, if an OD buffer is being established the TACW specifies the address from where the last data word of the buffer is to be obtained and outputted. The TACW also may request the continuous data mode (CDM) at buffer termination. CDM is discussed later in this sheet. Refer to figure 8.1-2 for the TACW format.

Figure 8.1-2. Terminal Address Control Word Format

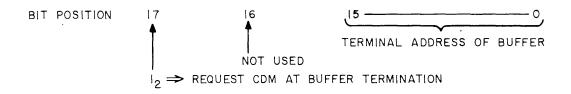

The initial address control word (IACW) immediately follows the TACW in the program. Among other things, it contains the 16-bit initial data address. For example, if an ID buffer is being established the IACW specifies the address where the first input data word of the buffer is to be stored. The IACW also may request the monitor interrupt to be generated at buffer termination. That is, after the last word of the buffer is transferred, the ID Mon, OD Mon, or EF Mon interrupt, depending upon the buffer type, is generated on the particular channel.

The IACW also specifies the direction of the buffer. A forward buffer is one which provides sequentially increasing addresses for the data. A backward buffer provides sequentially decreasing data addresses. In both cases, the TACW and IACW specify the terminal and initial buffer addresses, respectively. Refer to figure 8.1-3 for the IACW format.

Once the buffer is established (made active), the IACW is more appropriately referred to as the current address control word (CACW). The TACW and IACW are transferred into special control memory addresses. See Table 8.1-4. In control memory, the IACW is updated by  $\pm 1$ , depending upon the buffer direction, after each word transfer. It, therefore, always specifies the address for the next word transfer. Thus, the IACW becomes the CACW.

Figure 8.1-3. Initial Address Control Word Format

TABLE 8.1-4. ASSIGNED ADDRESSES FOR ADDRESS CONTROL WORDS

| ADDRESS CONTROL WORD   | SPECIAL ADDRESSES            |                              |  |  |

|------------------------|------------------------------|------------------------------|--|--|

| ADDITEOS CONTINOE WOND | ID                           | EF/OD                        |  |  |

| TACW                   | 00060 <sub>8</sub> + 2x chan | 00040 <sub>8</sub> + 2x chan |  |  |

| IACW (CACW)            | 00061 <sub>8</sub> + 2x chan | 00041 <sub>8</sub> + 2x chan |  |  |

All of the I/O instructions are format 2 type. The k designator (6 least significant bits) specifies the channel number. Refer to figure 8.1-4 for programing examples of buffer initiation.

# f. Special I/O Logic.

1. Active Flip-Flops. Each channel has an active flip-flop for ID and EF/OD. This flip-flop in the set state is the only requirement for the computer to detect and honor the associated request signal from a peripheral device. The active flip-flop is set by the buffer instruction (f = 50:11-50:13). There is an EF Mode flip-flop which allows the computer to distinguish between an EFR and ODR. This is necessary because the EF/OD Active flip-flop is shared by both functions.

At buffer termination, the active flip-flop is cleared to prevent the honoring of more requests than had been determined by the address control words.

- 2. Priority. Since it is possible to have more than one I/O signal requesting I/O services at the same time, a priority system exists to select one of these signals to be honored. Priority is set up on a channel number and function basis. The channel priority can be altered by plug-in cards. The priority scheme is discussed in a later sheet.

- 3.  $\underline{\text{I/O Translator}}$ . After a signal is selected by the priority logic, the information is placed in the I/O translator. This logic translates the signal type (function) and its channel number and assists in developing the control signals necessary to execute the proper I/O service.

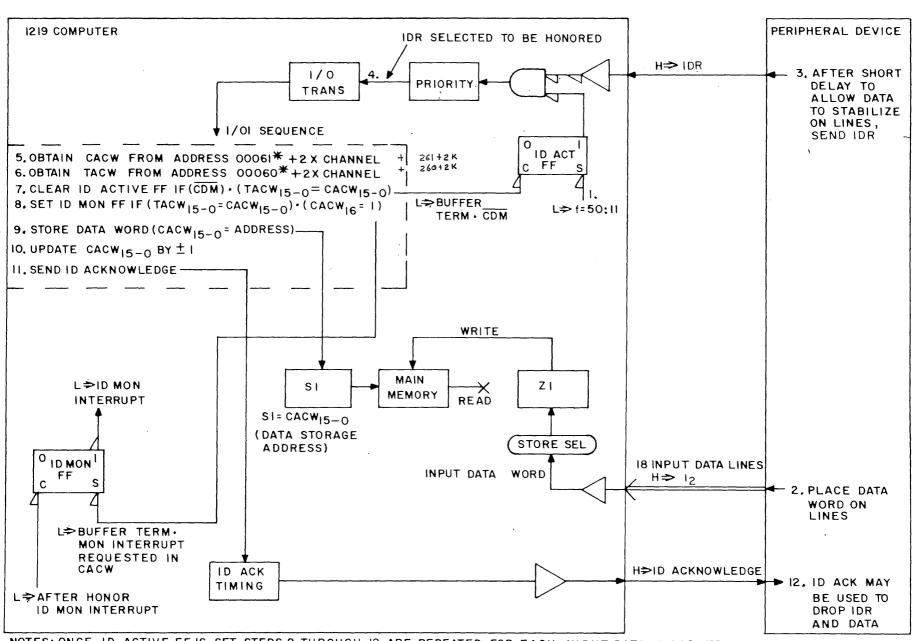

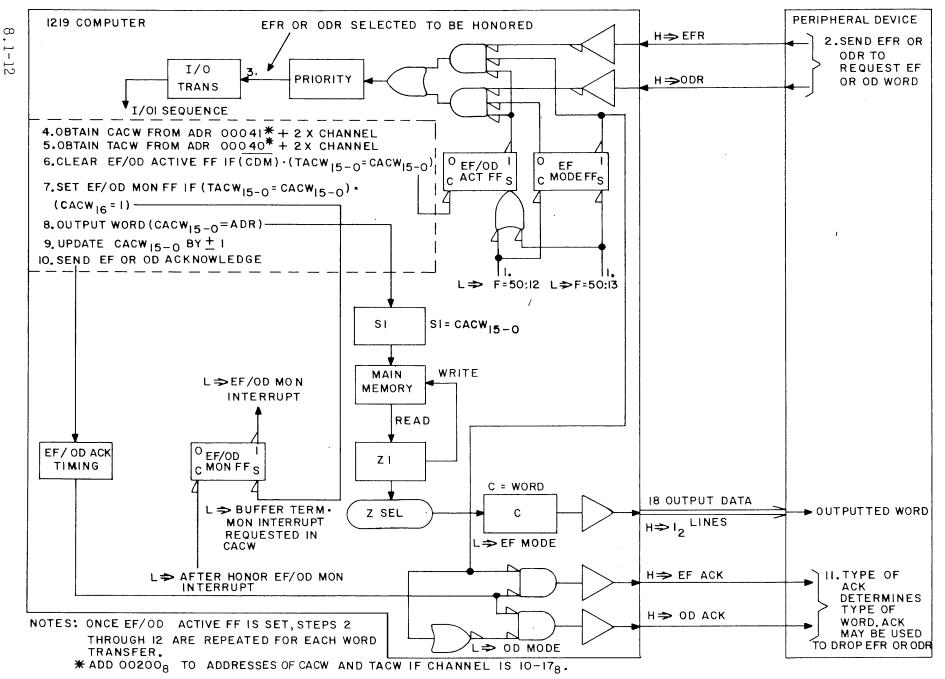

- g. Block Diagram Description of Data Request Operations. The I/Ol-sequence is used to honor an IDR, ODR, EFR, or EIR. Each of these signals requires a word transfer between the computer and the requesting peripheral device. They may also generate a monitor interrupt which is a separate signal to be considered

## PROGRAM ADDRESS

01000 501202 OUT INSTRUCTION, CHANNEL 2 01001 003000 TACW 01002 20200 IACW

### NOTES: 1. IACW SPECIFIES:

- a, FIRST OUTPUT DATA WORD WILL BE OBTAINED FROM ADDRESS 020008.

- b. OD MON INTERRUPT ON CHANNEL 2 AT BUFFER TERMINATION.

- c. FORWARD BUFFER.

### 2. TACW SPECIFIES:

- a. LAST OUTPUT DATA WORD WILL BE OBTAINED FROM ADDRESS 030008.

- b. NO CDM AT BUFFER TERMINATION.

- 3. IACW AND TACW TOGETHER ESTABLISH A 010018 WORD BUFFER.

### a. OD BUFFER EXAMPLE

### PROGRAM ADDRESS

04000 501104 IN INSTRUCTION, CHANNEL 4 04001 006000 TACW 04002 407500 IACW

### NOTES: I. IACW SPECIFIES:

- g. FIRST INPUT DATA WORD WILL BE STORED AT ADDRESS 07500 $_{

m B}$  .

- b. NO ID MON INTERRUPT AT BUFFER TERMINATION.

- c. BACKWARD BUFFER.

### 2. TACW SPECIFIES:

- a. LAST INPUT DATA WORD WILL BE STORED AT ADDRESS 060008.

- b. NO CDM AT BUFFER TERMINATION.

- 3. IACW AND TACW TOGETHER ESTABLISH A  $01501_{\mbox{\scriptsize R}}$  -WORD BUFFER.

### b. ID BUFFER EXAMPLE

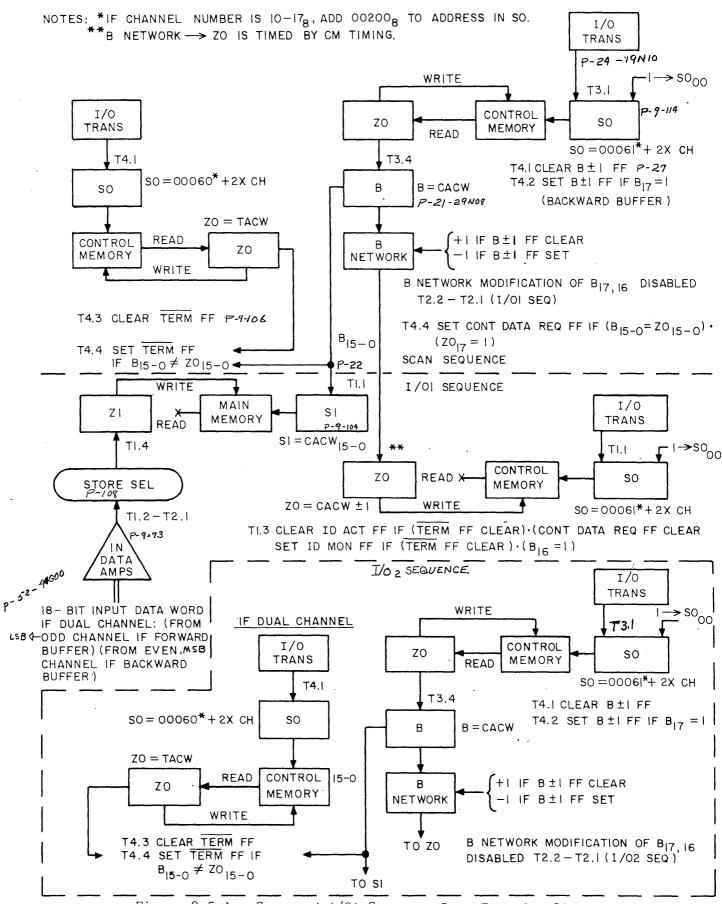

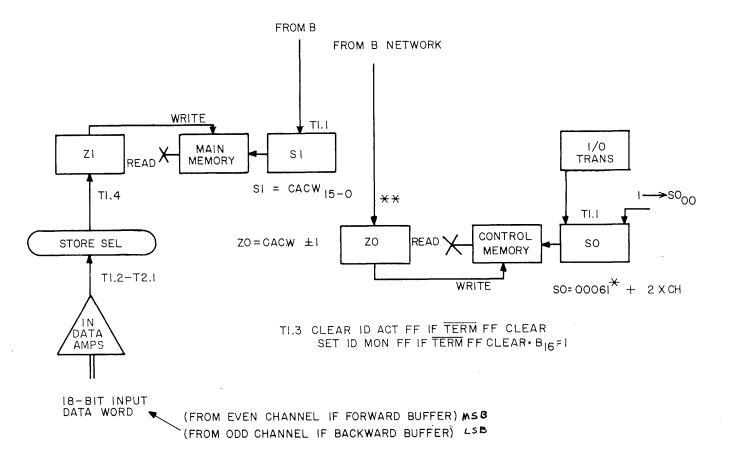

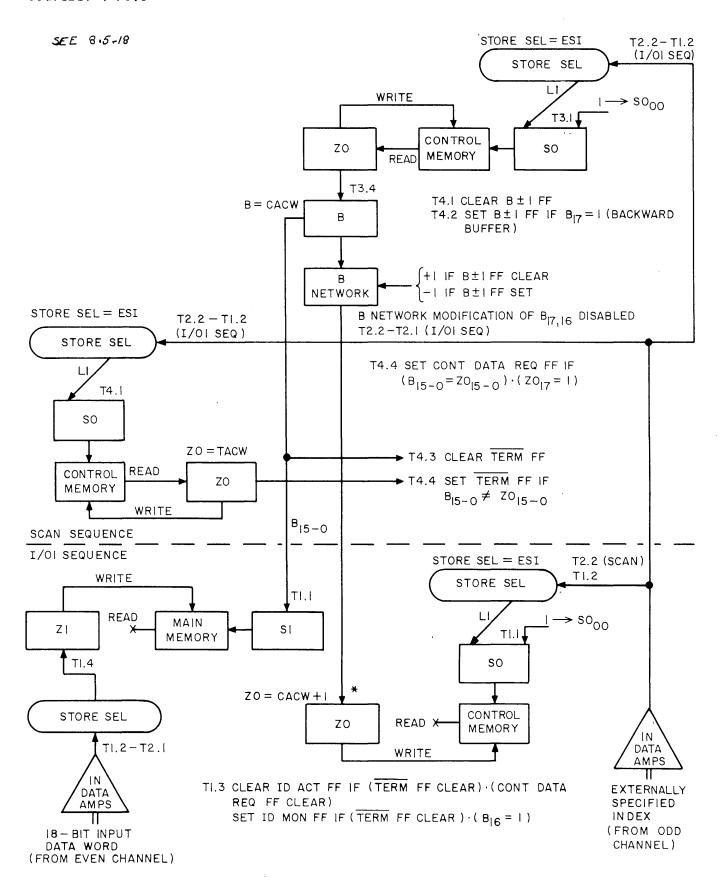

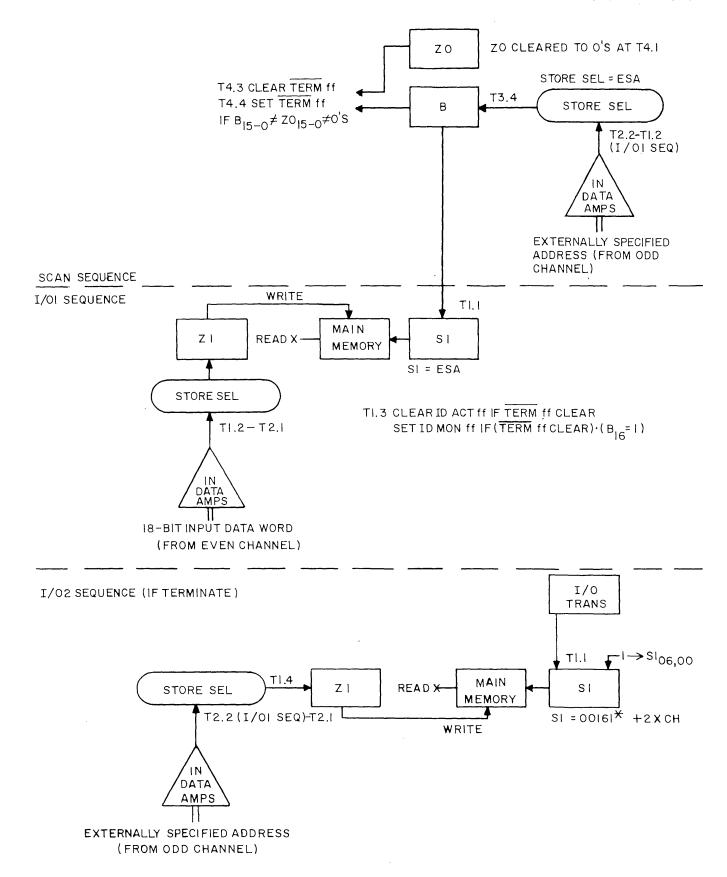

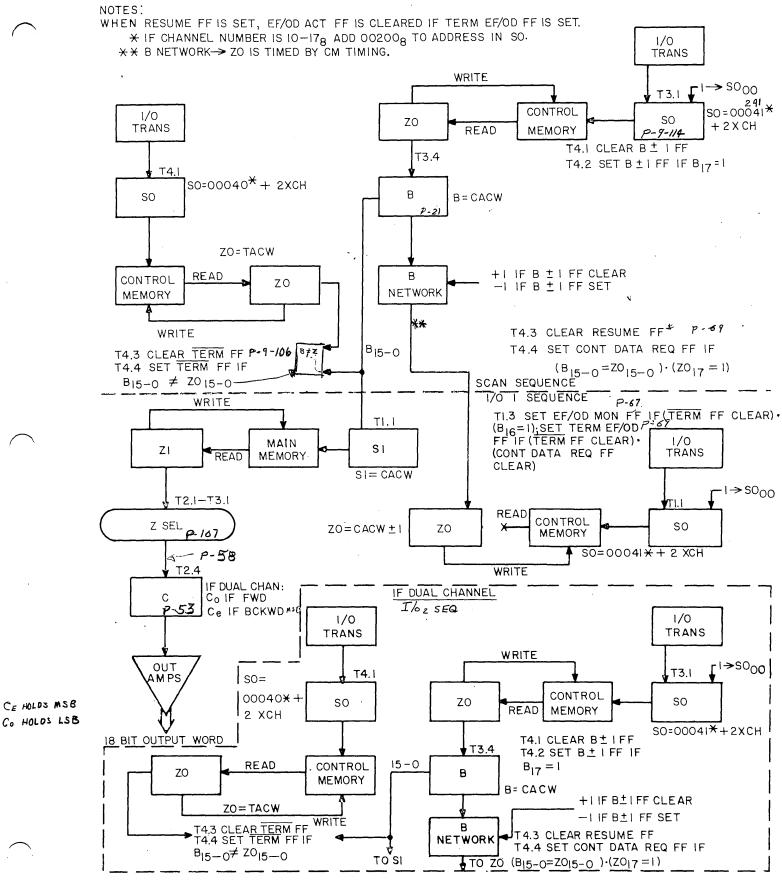

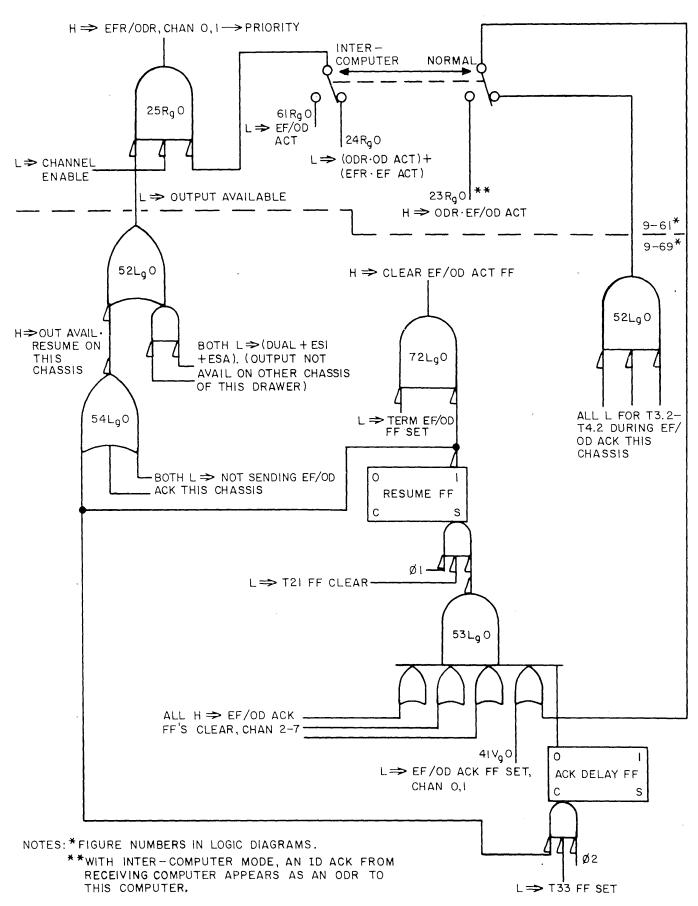

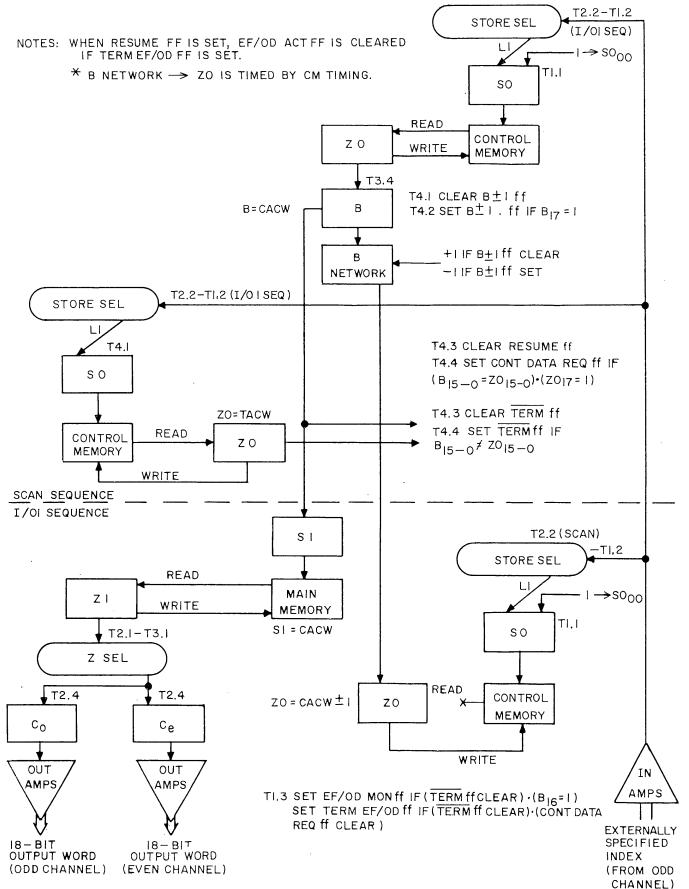

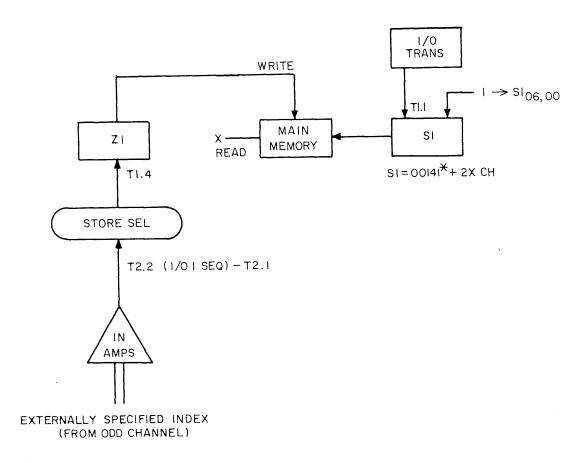

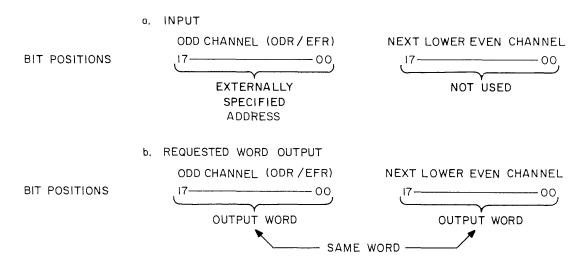

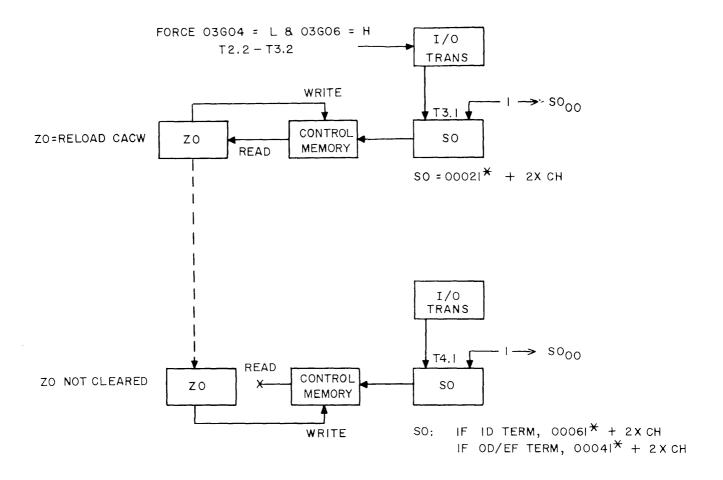

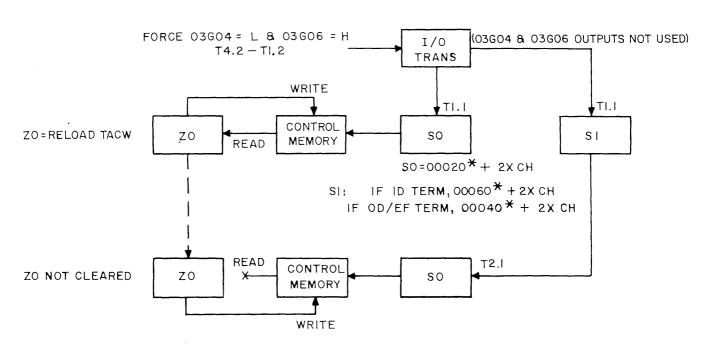

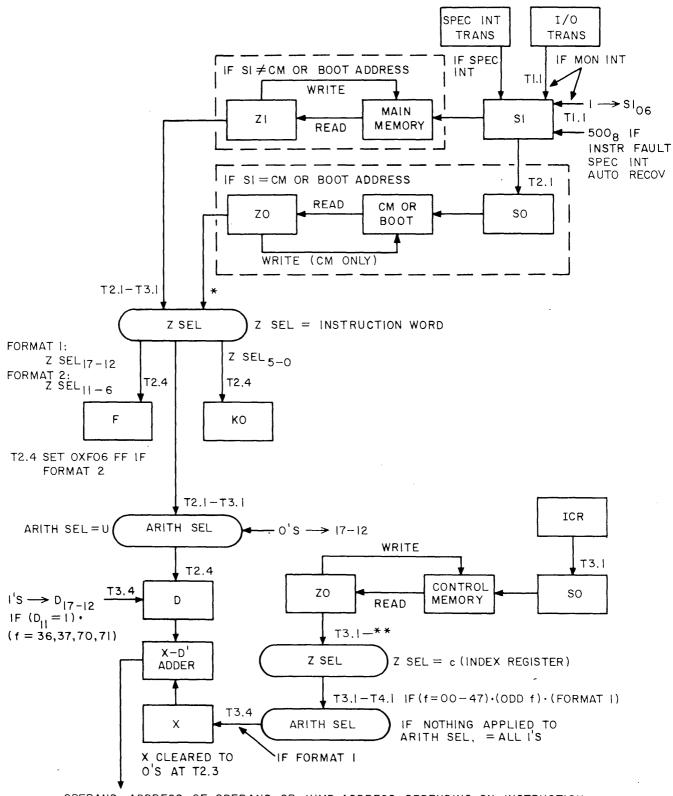

by priority before it can be honored to cause the program jump. Refer to figures 8.1-5, 8.1-6, and 8.1-7 for block diagram descriptions.

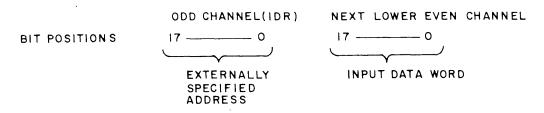

h. <u>Dual Channel Operations</u>. Dual channel operation involves the use of an odd numbered channel with the next lower channel which is even numbered to effect a 36-bit word transfer. The request signal must occur on the odd channel and the CHANNEL FUNCTION switch (one for each odd channel) must be in the dual position. If the request occurs on the even channel, single channel mode is in effect regardless of the switch.

The 18-bit word for each channel is treated normally as single channel. The only difference is that the acknowledge signal is not sent until after both halves of the 36-bit word have been transferred.

i. Continuous Data Mode (CDM). CDM is initiated at buffer termination if requested by the TACW (TACW $_{17}=1$ ). It keeps the channel active by preventing the normal clearing of the associated active flip-flop, and it establishes a new set of address control words. It obtains the new TACW from the control memory address 000208 + 2x channel if the channel is 0-7 or address 002208 + 2x channel if the channel is 10-178. These words are transferred to the normal special control memory addresses which hold the words during the buffer operation.

Prior to buffer termination, the program must have stored the "reload" TACW and CACW in preparation for CDM. If requested by the CACW (CACW $_{16}=1$ ), the normal monitor interrupt can occur at the termination of the old buffer after the new buffer has automatically been established. Each new set of address control words can determine its buffer direction, requirement for monitor interrupt, and requirement for CDM again.

Usually the monitor interrupt technique is used with CDM. The interrupt is the indication to the program that the address control words have been reloaded and, if CDM reload is to be performed again, the program must prepare the next TACW and CACW. Realize that for a particular channel, all three functions (ID, OD, and EF) use the same addresses to obtain the reload TACW and CACW. Therefore, if both an ID buffer and EF or OD buffer are active at the same time on the same channel, probably the program would not request CDM for both.

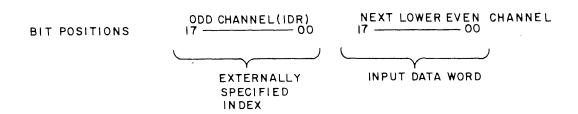

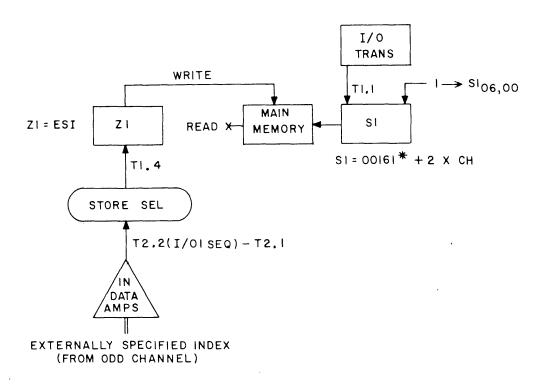

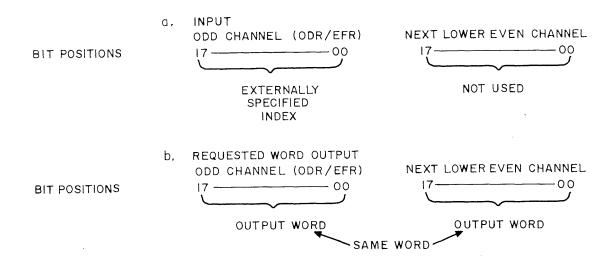

j. Externally Specified Index (ESI). Es, operation involves the use of an odd numbered channel with the next lower channel which is even numbered. The normal special addresses used to obtain the address control words are not used. The odd channel carries the control memory address to obtain the TACW. The CACW is extracted from the next consecutively high address. ESI allows the peripheral device to select its own address control words for each word transferred. These address control words must be set up by the program. The word transfer is effected over the even channel.

To enable ESI operation, the request signal must occur on the odd channel and the CHANNEL FUNCTION switch must be in the ESI position. If the request occurs on the even channel, single channel mode is in effect regardless of the switch.

ESI mode with an EIR forces dual channel operation (36-bit status word).

NOTES: ONCE ID ACTIVE FF IS SET, STEPS 2 THROUGH 12 ARE REPEATED FOR EACH INPUT DATA WORD TRANSFER. # ADD 002008 TO ADDRESSES OF CACW AND TACW IF CHANNEL IS 10-178.

Figure 8.1-5. Input Data Operations, Single Channel Without ESI and ESA

Figure 8.1-6. External Function/Output Data Operations, Single Channel Without ESI and ESA

Figure 8.1-7. External Interrupt Operations, Single Channel

#### S.G.1219 (M)8.1

k. Externally Specified Address (ESA). ESA operation involves the use of an odd numbered channel with the next lower channel which is even numbered. With this operation in effect, there are no address control words. The peripheral device directly specifies over the odd channel, the address for the word transfer requested. The word transfer is effected over the even channel.

To enable ESA operation, the request signal must occur on the odd channel and the CHANNEL FUNCTION switch must be in the ESA position. If the request occurs on the even channel, single channel mode is in effect regardless of the switch.

ESA mode with an EIR forces dual channel operation (36-bit status word).

### 8.1-5. SUMMARY

Read the <u>UNIVAC 1219 Technical Manual</u>, Volume I, Paragraph  $3-6\underline{c}(2)$  for a description of the I/O instructions. More detailed descriptions of these are presented in later sheets. Review the general description of the I/O section by reading <u>UNIVAC 1219 Technical Manual</u>, Volume I, Paragraphs 1-5d and 4-3a through 4-3e.

# SECTION 8 - INPUT/OUTPUT SECTION

8.2. INSTRUCTION EXECUTION OF SIN, SOUT, SEXF, INSTP, OUTSTP, EXFSTP

#### 8.2-1. OBJECTIVES

To present the detailed theory of operation involved in the execution of instructions with f = 50:01 - 50:03, 50:15 - 50:17.

### 8.2-2. INTRODUCTION

These instructions set one of the active flip-flops or terminate ID, OD, or EF operations on a selected channel.

#### 8.2-3. REFERENCES

- a. <u>UNIVAC 1219 Technical Manual</u>, Volume I, Paragraphs 4-3<u>d</u> and 4-7, table 4-11.

- b. UNIVAC 1219 Technical Manual, Volume II, Section 9 (logic diagrams).

## 8.2-4. INFORMATION

- a. General Description.

- 1. Instruction Interpretation.

- a) SIN, f=50:01. This instruction sets the ID Active flip-flop for the channel specified by the four least significant bits (k) of the instruction word. Input data operations are enabled on this channel.

- b) SOUT, f=50:02. This instruction sets the EF/OD Active flip-flop and clears the EF Mode flip-flop for channel k. Output data operations are enabled on this channel.

- c) SEXF, f=50:03. This instruction sets the EF/OD Active flip-flop and sets the EF Mode flip-flop for channel k. External function operations are enabled on this channel.

- d) INSTP, f = 50:15. This instruction terminates input data operations on channel k by clearing its ID Active flip-flop. Its ID Monitor flip-flop is also cleared to prevent the occurrence of an ID monitor interrupt.

- e) OUTSTP, f = 50:16 and EXFSTP, f = 50:17. Since the OD and EF buffer operations for the same channel share common logic, these instructions are actually the same. They terminate output operations (OD and EF) on channel k by clearing the associated EF/OD Active flip-flop. The EF/OD Monitor flip-flop for the channel is also cleared to prevent the occurrence of an EF/OD monitor interrupt.

Both instructions are included in the repertoire simply to provide compatibility with the UNIVAC 1218 Computer programs.

2. Execution Sequence (I). All operations are performed within the I-sequence. Only the one memory reference to obtain the instruction is necessary.

## b. Detailed Analysis.

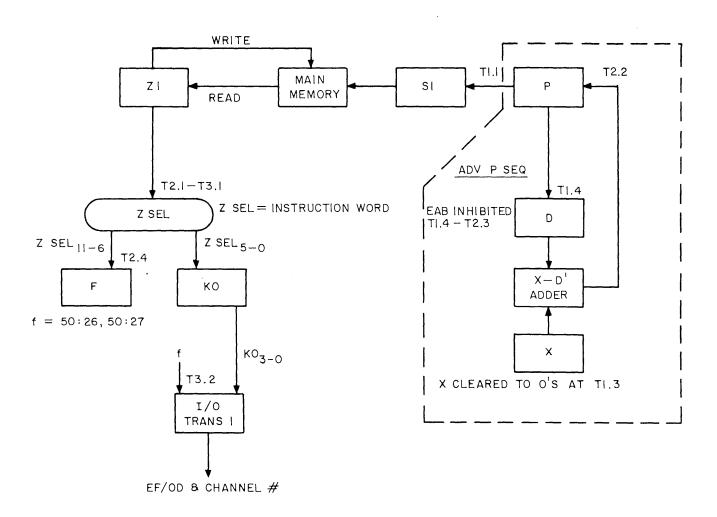

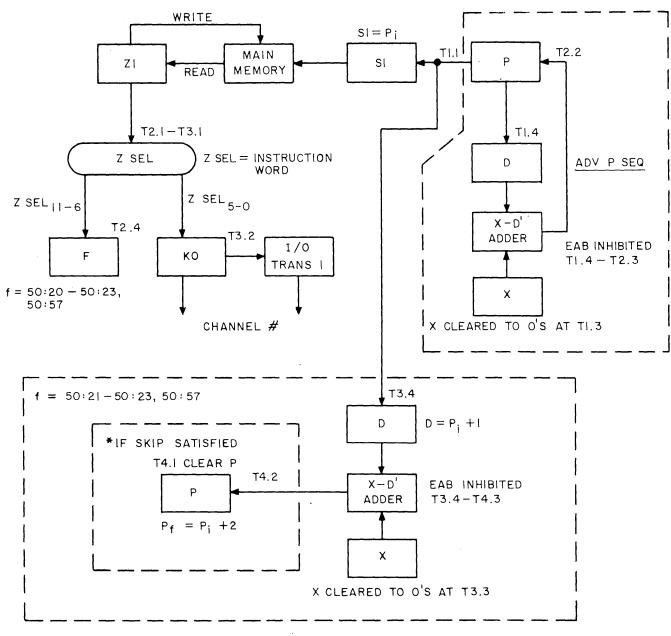

l. Data Flow Block Diagram. Refer to figure 8.2-1 for a block diagram description of the execution of f = 50:01 - 50:03, 50:15 - 50:17.

Most of the I-sequence operations are as previously described. If necessary, refer to study guide sheet number 5.4 for a detailed description.

KO is set to the six least significant bit positions of the instruction word from Z-select. Only the four lower bits of this value are used. At T3.2 time, the I/O translator register is set to  ${\rm KO_{3-O}}$  which is the channel number. This register is also affected by the function code which indicates the type of buffer (ID, OD, or EF).

As discussed in a prior sheet, the instruction could be obtained from bootstrap or control memory.

2. Essential Commands. Refer to table 8.2-1 for a sequential list of essential I-sequence events. Develop these commands by referring to the proper enable pages in the logic diagrams.

### 8.2-5. SUMMARY

The f = 50:01 - 50:03, 50:15 - 50:17 instructions are format 2 and use the value k. The k value is available in KO after T2.4 time. Only the I-sequence is required to complete the execution of these instructions.

9-49 I/O TRANSLATOR & SCAN TIMING

9-53 JO COMMANDS

9-57 " " CONTROL II

9-58 " " CONTROL III

9-59 TRANSLATOR I

9-60 TRANSLATOR II

```

T4.3 IF f = 50:01; SET ID ACT FF P-6/\rightarrow 64

IF f = 50:02; SET EF/OD ACT FF & CLEAR EF MODE FF

IF f = 50:03; SET EF/OD ACT FF & SET EF MODE FF

IF f = 50:15; CLEAR ID ACT FF & CLEAR ID MON FF

IF f = 50:16; 50:17; CLEAR EF/OD ACT FF & CLEAR EF/OD MON FF

```

Figure 8.2-1. I-Sequence Data Flow for f = 50:01 - 50:03, 50:15 - 50:17

TABLE 8.2-1. I SEQUENCE ESSENTIAL COMMANDS FOR f = 50:01 - 50:03, 50:15 - 50:17

| TIME NOTATION | COMMANDS                                                                                          |

|---------------|---------------------------------------------------------------------------------------------------|

| T4.4          | Clear Sl                                                                                          |

| T1.1          | P →S1, Init Memory, *set Incr P ff                                                                |

| T1.3          | *Clear D, *clear X, clear Zl, clear F, *set OXL11 ff                                              |

| T1.4          | $*P_L \longrightarrow D_L$ , $*P_U \longrightarrow D_U$ , clear KO, *set Inhib EAB ff             |

| T2.1          | *Clear P, Zl -> Z Sel, *clear Incr P ff                                                           |

| T2.2          | *Adder -> P                                                                                       |

| T2.3          | *Clear OXL11 ff, *clear Inhib EAB ff                                                              |

| T2.4          | $Z \text{ Sel}_{11-6} \longrightarrow F$ , set OXF06 ff, $Z \text{ Sel}_{5-0} \longrightarrow K0$ |

| ТЗ.1          | Clear I/O Trans 1, drop Zl —> Z Sel                                                               |

| Т3.2          | f & KO → I/O Trans 1                                                                              |

| T4.3          | **Set Act ff, **clear Act & Mon ff's                                                              |

|               |                                                                                                   |

<sup>\*</sup>These events are concerned with or are controlled by the advance-P subsequence.

<sup>\*\*</sup> if f = 50:01; set ID Act ff

if f = 50:02; set EF/OD Act ff & clear EF Mode ff

if f = 50:03; set EF/OD Act ff & set EF Mode ff

if f = 50:15; clear ID Act ff & clear ID Mon ff

if f = 50:16, 50:17; clear EF/OD Act ff & clear EF/OD Mon ff

I/O Translator 1 selects the channel number.

## SECTION 8 - INPUT/OUTPUT SECTION

# 8.3. INSTRUCTION EXECUTION OF IN, OUT, EXF

### 8.3-1. OBJECTIVES

To present the detailed theory of operation involved in the execution of instructions with f = 50:11 - 50:13.

## 8.3-2. INTRODUCTION

These instructions set-up  ${\tt ID}$ ,  ${\tt OD}$ , or  ${\tt EF}$  buffer operations on a particular channel with specified buffer limits.

### 8.3-3. REFERENCES

- a. <u>UNIVAC 1219 Technical Manual</u>, Volume I, Paragraphs 4-3<u>d</u> and 4-7, tables 4-11, 4-15, and 4-16.

- b. UNIVAC 1219 Technical Manual, Volume II, Section 9 (logic diagrams).

#### 8.3-4. INFORMATION

### a. General Description.

### 1. Instruction Interpretation.

- a)  $\overline{\text{IN, f}}=50:11$ . This instruction enables input data operations on channel k by setting its  $\overline{\text{ID}}$  Active flip-flop. The terminal address control word (TACW) is taken from the next consecutive address after this instruction. The initial address control word (IACW) is taken from the next consecutive address after the TACW. These control words specify the area of memory involved in the data exchange operation.

- b) OUT, f=50:12. This instruction enables output data operations on channel k by setting its EF/OD Active flip-flop and clearing its EF Mode flip-flop. The origins of TACW and IACW are the same for f=50:11.

- c) EXF, f=50:13. This instruction enables external function operations on channel k by setting its EF/OD Active flip-flop and setting its EF Mode flip-flop. The origins of TACW and IACW are the same as for f=50:11.

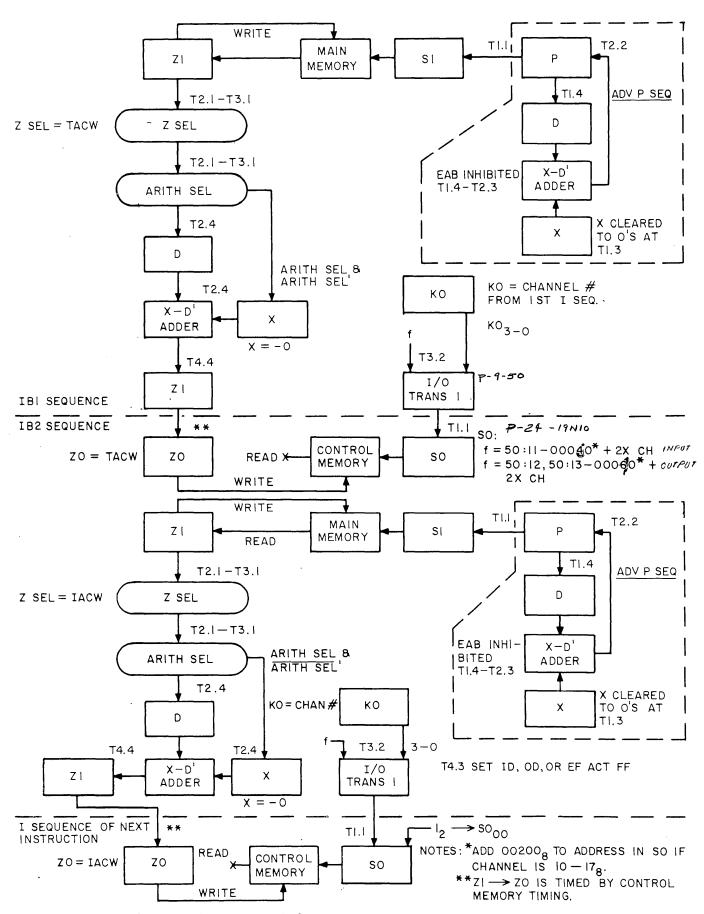

## 2. Execution Sequences.

- a) <u>I-Sequence</u>. During the I-sequence which obtains the instruction from memory, the channel number is placed in KO.

- b)  $\underline{\text{IB1-Sequence}}$ . The Bl and I-sequences run in parallel to obtain the TACW from memory.

- c)  $\overline{\text{IB2-Sequence}}$ . The B2 and I-sequences run in parallel to store the TACW in control memory, obtain the IACW from memory, and set the proper active flip-flop.

- d) Next I-Sequence. The initial portion of the I-sequence for the next instruction is used to store the IACW in control memory.

### b. Detailed Analysis.

- 1. <u>I-Sequence</u>. The I-sequence operations are as previously described. If necessary, refer to study guide sheet number 5.4 for a detailed description. At the end of the I-sequence, KO contains the channel number. Only the four least significant bits of KO are interpreted.

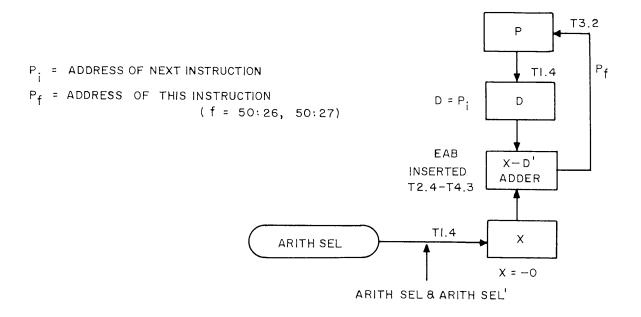

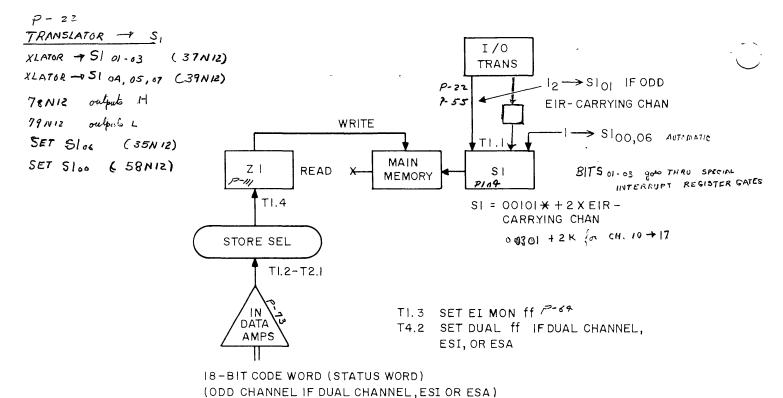

- 2. Data Flow Block Diagram. Refer to figure 8.3-1 for a block diagram description of the execution of f = 50:11 50:13.

The IB1-sequence uses a memory reference to obtain the TACW from the address contained in P. P was advanced to the next consecutive address after this instruction by the advance-P subsequence during the I-sequence which obtained this instruction. The advance-P subsequence is used during this IB1-sequence to increment P to address of the IACW.

The TACW is applied to one side of the adder from D. X is set to all 1's and applies this -O value to the other side. The adder, therefore, outputs the TACW unmodified which is placed in Zl. The I/O translator register is set according to the channel number from KO and the type of active flip-flop to be set from the function code translator.

The IB2-sequence uses a control memory reference to store the TACW. The storage address is dependent upon the function code and channel number as supplied by the I/O translator register. The gating of control memory to ZO is disabled during the read portion of the memory cycle which destroys the original memory content.

Another memory cycle is used to obtain the IACW from the address contained in P. The IACW passes through the X-D' adder unmodified just as did the TACW and is placed in Zl. The advance-P subsequence is used to increment P to the address of the next instruction in the program.

The initial portion of the I-sequence for the next instruction initiates a control memory reference to store the IACW. The storage address for the IACW is one greater than that for the TACW. The IACW storage address is formulated by setting SO from the I/O translator register and also setting  $SO_{OO}$  to  $l_2$ .

3. Essential Command. Refer to table 8.3-1 for a sequential list of essential IB1, IB2, and next I-sequence events. Develop these commands by referring to the proper enable pages in the logic diagrams.

### 8.3-5. SUMMARY

The f = 50:11 - 50:13 instructions are format 2 and use the value k. The k value is available in KO after T2.4 time of the I-sequence. The IB1 and IB2-sequences are required to complete the executions of these instructions.

Figure 8.3-1. IB1 and IB2-Sequence Data Flow for f = 50:11 - 50:13

TABLE 8.3-1. IB1, IB2, AND NEXT I SEQUENCE ESSENTIAL COMMANDS FOR  $f = 50 \colon\! 11$  -  $50 \colon\! 13$

| TIME NOTATION | COMMANDS                                                                                              |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------|--|--|--|

|               | IB1 SEQUENCE                                                                                          |  |  |  |

| T4.4          | Clear S1                                                                                              |  |  |  |

| T1.1          | P→S1, Init Memory, *set Incr P ff                                                                     |  |  |  |

| T1.3          | *Clear D, *clear X, clear Z1, *set 0XL11 ff                                                           |  |  |  |

| T1.4          | * $P_L \rightarrow D_L$ , * $P_U \rightarrow D_U$ , *set Inhib EAB ff                                 |  |  |  |

| T2.1          | *Clear P, Z1→Z Sel, Z Sel→Arith Sel, *clear Incr P ff                                                 |  |  |  |

| T2.2          | *Adder→P                                                                                              |  |  |  |

| T2.3          | *Clear 0XL11 ff, *clear Inhib EAB ff, clear D, clear X                                                |  |  |  |

| T2.4          | Arith Sel $\rightarrow$ D, Arith Sel $\rightarrow$ X & Arith Sel' $\rightarrow$ X (set X = 1's)       |  |  |  |

| Т3.1          | Clear I/O Trans 1, drop Z1→Z Sel, drop Z Sel→Arith Sel                                                |  |  |  |

| Т3.2          | f & K0→I/O Trans 1                                                                                    |  |  |  |

| Т4.3          | Clear Z1                                                                                              |  |  |  |

| T4.4          | Adder→Z1, **disable CM→ZO, clear S1                                                                   |  |  |  |

|               | IB2 SEQUENCE                                                                                          |  |  |  |

| T1.1          | I/O Trans 1-SO, Init CM, P-S1, Init Memory, * set Incr P                                              |  |  |  |

| T1.3          | *Clear D, *clear X, clear Z1, *set 0XL11 ff                                                           |  |  |  |

| T1.4          | * $P_L \rightarrow D_L$ , * $P_U \rightarrow D_U$ *set Inhib EAB ff, drop disable CM $\rightarrow$ ZO |  |  |  |

| T2.1          | *Clear P, Z1-> Z Sel, Z Sel-> Arith Sel, *clear Incr P ff                                             |  |  |  |

| T2.2          | *Adder→P                                                                                              |  |  |  |

| Т2.3          | *Clear 0XL11 ff, *clear Inhib EAB ff, clear D, clear X                                                |  |  |  |

| T2.4          | Arith Sel $\rightarrow$ D, Arith Sel $\rightarrow$ X & Arith Sel' $\rightarrow$ X (set X = 1's)       |  |  |  |

| Т3.1          | Clear I/O Trans 1, drop Z1→Z Sel, drop Z Sel→Arith Sel                                                |  |  |  |

| Т3.2          | f & K0→I/O Trans 1                                                                                    |  |  |  |

| Т4.3          | Clear Z1, ***set ID, OD, or EF Act ff                                                                 |  |  |  |

| T4.4          | Adder→Z1, **disable CM→ZO                                                                             |  |  |  |

|               | I SEQUENCE OF NEXT INSTRUCTION                                                                        |  |  |  |

| T1.1          | I/O Trans $1 \rightarrow SO$ , $1_2 \rightarrow SO_{00}$ , Init CM                                    |  |  |  |

| T1.4          | Drop disable CM→ZO                                                                                    |  |  |  |

<sup>\*</sup>These events are concerned with or are controlled by the advance P subsequence.

<sup>\*\*</sup>Z1->ZO is timed by control memory timing.

<sup>\*\*\*</sup>if f = 50:11, set ID Act ff

if f = 50:12, set EF/OD Act ff & clear EF Mode ff

if f = 50:13, set EF/OD Act ff & set EF Mode ff

I/O Translator 1 selects the channel number.

# SECTION 8 - INPUT/OUTPUT SECTION

### 8.4. SIGNAL DETECTION AND SELECTION

### 8.4-1. OBJECTIVES

To present the detailed theory of operation involved in input/output signal selection.

#### 8.4-2. INTRODUCTION

The signal selection logic determines which one of the present input/output signals will be honored first.

### 8.4-3. REFERENCES

- a. UNIVAC 1219 Technical Manual, Volume I, Paragraph 4-3.

- b. UNIVAC 1219 Technical Manual, Volume II, Section 9 (logic diagrams).

### 8.4-4. INFORMATION

### a. General Description.

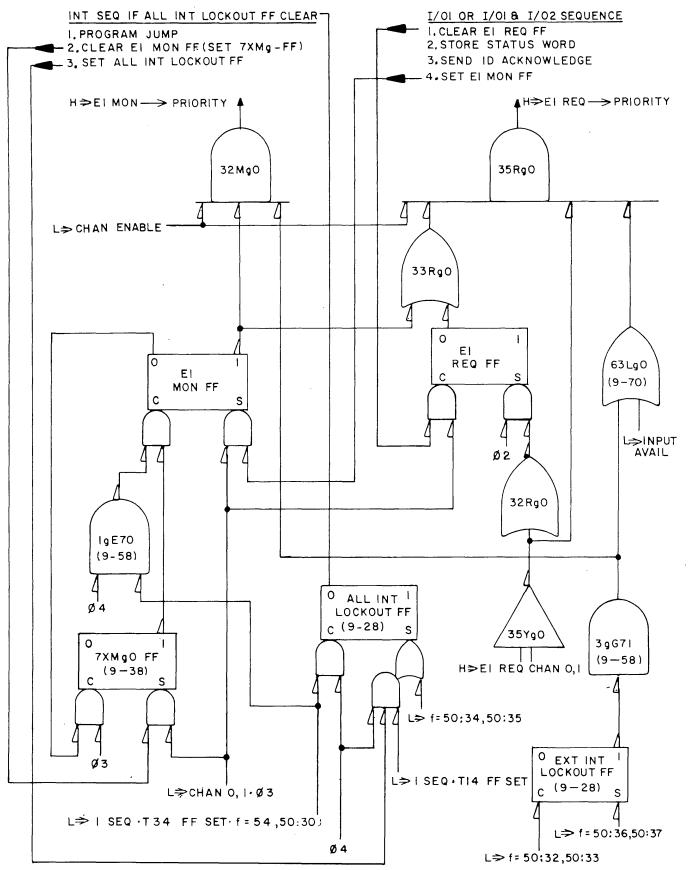

l. Signal Types. The input/output section of the computer handles signals generated externally to the computer as well as some originating internally. The types of external signals are external interrupt request (EIR), external function request (EFR), output data request (ODR), input data request (IDR), and external sync. The first four of these listed are channel type. That is, each of the 16 channels can generate these requests. All other signals are generated from within the computer. Among these are the monitor interrupts (EI Mon, EF/OD Mon, and ID Mon). These interrupt signals are also channel type.

The computer can handle only one signal at a time and others present must wait. A priority scheme is established by the logic to service the signals in a specific sequence. The priority set-up actually has two levels. One is for channel priority, as required by the channel type signals; and the other is for function priority to select the type of signal to be honored (serviced). Refer to table 8.4-1 for the signal types listed in their order of function priority.

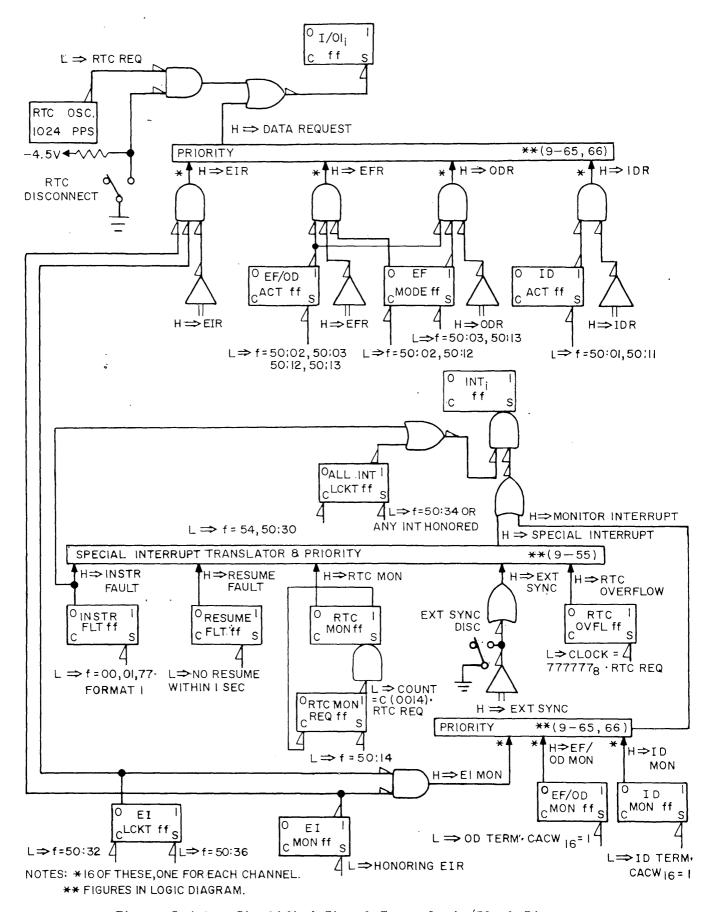

If a data request or monitor interrupt type is to be honored, channel priority is considered first. Then, the type of signal is selected from those of the function group which are present on the selected channel. The priority scheme is discussed in more detail later in this sheet. Refer to figure 8.4--1 for a block diagram showing all of the signals handled by the input/output logic.

The priority logic for the data requests and monitor interrupts is discussed later in this sheet. The priority logic for the special interrupts is analyzed in a later sheet.

| (non-channel)                        | RTC Request                                                  |                                                      |

|--------------------------------------|--------------------------------------------------------------|------------------------------------------------------|

| Data Requests<br>(channel type)      | - EIR ← EFR or ODR* IDR*                                     | disabled by External Interrupt Lockout flip-flop set |

| Special Interrupts<br>(non-channel)  | Instruction Fault Resume Fault RTC Mon Ext Sync RTC Overflow | disabled by All Interrupt<br>Lockout flip-flop set   |

| Monitor Interrupts<br>(channel type) | EI Mon <del>&lt;</del> EF/OD Mon* ID Mon*                    |                                                      |

TABLE 8.4-1. SIGNALS PRESENTED TO INPUT/OUTPUT LOGIC

EFR and ODR are listed together because only one of these buffer types can be active at one time on one channel. Signals are listed in their order of function priority.

\* Priority of these signals can reverse.

2. Data Request and Monitor Interrupt Priority. Priority logic is used to perform the actual selection of one of the signals presented to it during one of the two scan periods. The scan periods are described later in this sheet.

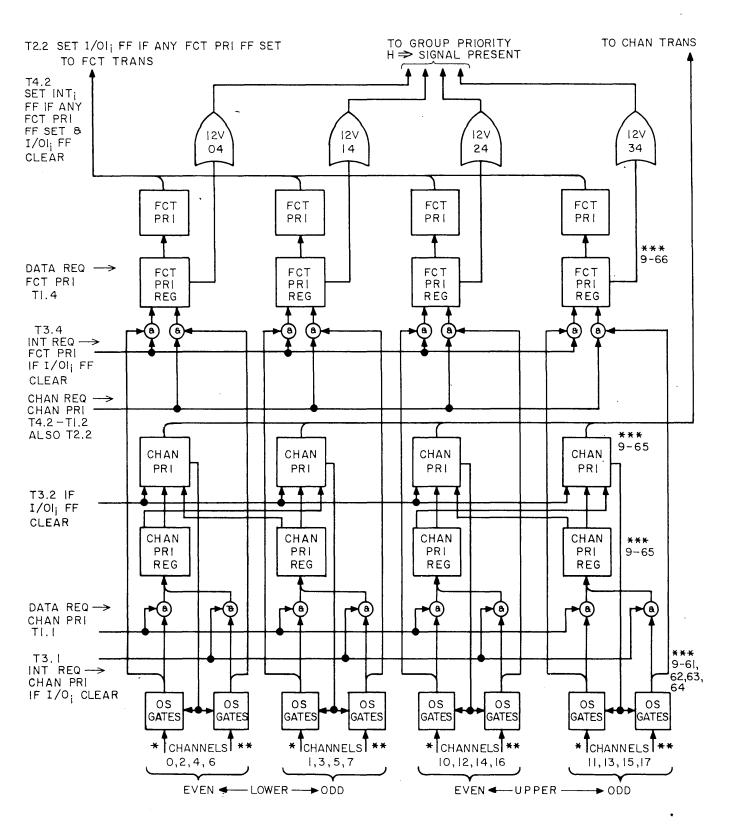

Channel logic is distributed among four chassis. Each chassis is connected to four channels. The channels are divided into two groups. Channels 0-7 are considered the lower group. Channels 10-17 are considered the upper group. Of each group, channel priority selects the highest numbered channel which has a signal present. The signals of the selected channel enter function priority which determines the type of signal of the selected channel to be honored.

Group priority then determines that a signal selected from the upper group (channels 10-17) will be honored before a signal from the lower group (channels 0-7). The overall priority setup is such that the highest numbered channel which carries a signal is selected and one signal type on that channel is selected.

3. <u>Data Request Scan</u>. A certain period of the main timing cycle is used to scan the computer input signals for data requests. Data requests include external interrupt, external function, input data, and output data requests. These are all signals from external devices which require some computer service.

Figure 8.4-1. Simplified Signal Input Logic/Block Diagram

The described priority scheme is altered if an IDR or EIR occurs immediately after an ODR or EFR is honored. In this case, the IDR has higher priority than an ODR. The priority of ODR's and IDR's is therefore alternated if they continuously occur.

Real time clock (RTC) operations are discussed in a later sheet.

4. Interrupt Request Scan. If no data request was detected during the scan period described above, another scan occurs for monitor interrupts. The same priority logic is used to select a particular signal to be honored. Refer to table 8.4-1 for the monitor interrupt types. If either an ODR or EFR was previously honored and an IDR or EIR was not since honored, an ID Mon has higher priority than an OD Mon.

Special interrupt operations are discussed in a later sheet.

# b. Detailed Analysis.

l. Request Signal Entrance Logic. The logic which detects the input/output signals is constructed in a one-shot manner. This arrangement prevents the signal from being honored more than once. Any signal which is selected and honored must drop and reappear before it can again be detected. Refer to logic diagrams, figure 9-61 for the channel 0, 1 signals input logic.

This logic is either for channel 0,  $10_8$ , 1, or  $11_8$  depending upon the particular chassis. Each type of signal has an associated flip-flop. The IDR signal detection is analyzed as an example.

The ID Request flip-flop OXRgO provides the one-shot function for the IDR. A low logic level from O5YgO represents an IDR being applied to the computer. If the IDR is absent, the ID Request flip-flop is set during  $\emptyset 2$ . A resulting low level enable is applied to gate O5RgO on pin 8. The low level enable on pin 7 is present only if the ID Active flip-flop is set. This flip-flop must have been set by a previously executed f = 50:01, 50:11 instruction.

The low level enable on pin 6 of 05RgO is present if the input circuitry is available. Actually this line is at a low level if the input acknowledge signal is not currently being generated.

The low level enable on pin 5 of 05 RgO is present during the signal scan period. 05 RgO is fully enabled if the IDR is present which applies a low level on its pin 9. The resulting high level output of 05 RgO applies this IDR to the priority logic on this particular chassis. The 80 RgO output is to channel priority. The 16 RgA output is to function priority.

If this IDR is selected by the priority logic and honored, the ID Request flip-flop OXRgO is cleared to provide the signal one-shot function. Pin 10 of OXRgO becomes a low level during the honoring operation. Pin 9 is a low level indicating that this channel is being serviced. The clearing of this flip-flop presents a high level disable to gate O5RgO, pin 8. Therefore, the recognition of the IDR signal on this channel is prevented until flip-flop OXRgO is set. The setting of OXRgO can only occur if the external equipment drops the IDR signal. The clearing is timed by  $\emptyset 2$ .

EIR, EFR, and ODR signals pass through similar entrance logic. EF and OD buffers cannot be active at the same time on the same channel. They have a common active

flip-flop which, when set, enables the recognition of either the EFR or ODR. The status of the EF Mode flip-flop determines which type of buffer is active. If set, it allows the EFR to be sent to priority. If cleared, it enables the ODR.

## 2. Data Flow Block Diagram.

a) <u>Data Request Scan</u>. Refer to figure 8.4-2 for a block diagram description of the input/output signal selection.

All signals are presented to the one-shot entrance gates. The Chan Req  $\longrightarrow$  Chan Pri (T4.2-T1.2) command forces channel priority on each chassis to enable all channels. The resulting enables to the one-shot gates allow all input signals to be detected. However, only the outputs of the gates for EIR, EFR, ODR, and IDR signals are allowed to enter channel priority at Tl.l time. These data request signals are enabled by the Data Req  $\longrightarrow$  Chan Pri command. The monitor interrupt signals do not enter channel priority at this time because of the absence of the Int Req  $\longrightarrow$  Chan Pri command.

As soon as the channel priority on each chassis receives the request signals, channel selection is made. The channel priority register for channels 0, 2, 4, 6 is connected to the channel priority logic for channels 1, 3, 5, 7 and vice versa. This interconnection causes the channel priority logic for these two chassis to act as one priority system. This system then selects the highest numbered channel of 0-7 which carries an input signal. The channel priority logic for channels 10-17 is likewise interconnected. It then selects one channel of 10-17.

The Chan Req -> Chan Pri command drops at T1.2 time. By this time, channel priority has performed the selection. Since channel priority is no longer forced to indicate all channels, only the selected channel one-shot gates are enabled (one gate of channels 0-7 if there is an input signal present and one gate of channels 10-17 if there is an input signal present).

The Data Req $\rightarrow$ Fct Pri command enters the function priority register with the signals from the enabled one-shot gates. Only the signals on the selected channels are affected.

Function priority presents a high logic level to group priority if it contains a signal. Group priority selects the upper group (channels 10-17) if there is an associated input signal; otherwise, the lower group (channels 0-7) is selected. One particular channel is chosen after group priority and function priority selects the type of signal on this channel.

If a signal was processed during the above events, the I/O  $l_i$  Sequence flip-flop is set at T2.2 time. At this time, the selected signal information is passed to the function, channel, and I/O translators. The translators outputs are used to control the computer operations to effect the honoring of the selected signal.

### b) Interrupt Request Scan. Refer to figure 8.4-2.

If the  $I/Ol_i$  flip-flop was not set during the data request scan, no EIR, EFR, ODR nor IDR signal was detected. A scan is then made for monitor interrupts. The Chan-Req—> Chan Pri command occurs again at T2.2-T3.2 time to allow channel priority to enable all one-shot entrance gates. During this scan period, however, only the entrance gates for the monitor interrupts are allowed to pass their signals to channel priority because of the presence of the Int Req—> Chan Pri command.

NOTES: \*ODR, IDR, EFR, & EIR SIGNALS.

Figure 8.4-2. Input/Output Signal Selection Flow

<sup>\*\*</sup>OD MON, ID MON, EF MON, & EI MON SIGNALS (INTERNALLY GENERATED).

<sup>\*\*\*</sup>FIGURES IN LOGIC DIAGRAMS.

Figure 8.4-2. Input/Output Signal Selection Flow (Cont.)

Channel priority functions as described for the data requests. During the Int  $\text{Req} \longrightarrow \text{Fct}$  Pri command, the signals of the selected channels enter function priority which selects one type of signal. Group priority selects one particular channel. At the next T2.2 time, the signal information is passed to the translators.

If a monitor interrupt signal was detected during the above events, the Inti Sequence flip-flop is set at T4.2 time. The setting of this flip-flop is prevented by the  $I/Ol_i$  Sequence flip-flop if a data request signal was detected during the first scan.

- 3. Essential Commands. Refer to table 8.4-2 for a sequential list of essential events concerning signal selection. After the commands shown, events follow to honor the selected signal. These events and RTC operations are discussed in later sheets. Develop the commands shown by referring to the proper enable pages in the logic diagrams.

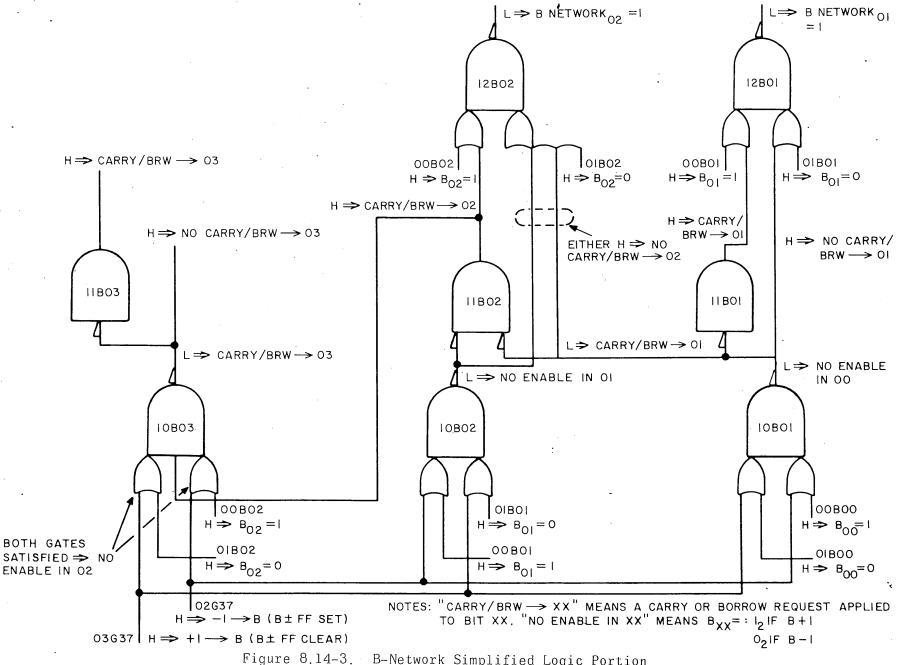

- 4. Channel Priority. Refer to logic diagrams, figure 9-65.

Each I/O chassis has channel priority logic. Request signals enter channel priority by way of the 80Rg- gates during the data request scan period. If no request is detected, the monitor interrupt signals enter by way of the 80Mg- gates during the interrupt request scan period.

The channel flip-flops are set if any signal is present on their channels, regardless of signal type. The llVg- gates provide the channel enable which "opens" all of the signal entrance gates to allow all data requests or monitor interrupts to enter channel priority. The llVg- gates have a common "Chan Req  $\longrightarrow$  Chan Pri" input which forces these gates to enable all channels. When this signal drops, all signals have been inputted to channel priority and one channel has been selected. The loVg- inputs to the llVg- gates enable one channel. Thus, when the signals enter function priority, only the data requests or monitor interrupts of the selected channel are involved.

The channel priority logic on the two chassis of the same drawer are interconnected. These are the dotted-line inputs and outputs shown. These lines are connecting a chassis with odd channels to the chassis with even channels and vice-versa. It is this interconnection which causes the highest channel number with a signal present to be selected among the eight channels of the particular drawer. Thus, only one channel priority of each drawer can indicate a selected channel.

The 10Vg- gates perform the actual channel selection. Refer to table 8.4-3 for the conditions to enable these gates. Realize that these gates are fed by the channel priority flip-flops on this chassis as well as on the other chassis of the same drawer.

5. Function Priority. Refer to logic diagrams, figure 9-66.

Each I/O chassis has function priority logic. Only those signals which are present on the channel selected by channel priority are enabled to enter function priority. There is a separate flip-flop for each function type. Request signals enter this logic by way of the 16Rg- gates during the data request scan period. If no request is detected, the monitor interrupt signals enter by way of the 16Mg- gates during the interrupt request scan period.

TABLE 8.4-2. SCAN SEQUENCE ESSENTIAL COMMANDS

| TIME NOTATION | COMMANDS                                                                                                            |

|---------------|---------------------------------------------------------------------------------------------------------------------|

| T4.2          | Chan Req→Chan Pri <i>P-65</i>                                                                                       |

| T4.4          | Clear Chan & Fct Pri                                                                                                |

| T1.1          | Data Req→Chan Pri                                                                                                   |

| T1.2          | Drop Chan Req -> Chan Pri                                                                                           |

| T1.4          | Data Req─→Fct Pri                                                                                                   |

| T2.1          | Clear Fct, Chan, & I/O Trans 1 P-50 £51                                                                             |

| T2.2          | Set I/Ol <sub>i</sub> ff if any Fct Pri ff set                                                                      |

|               | Pri → Fct, Chan, & I/O Trans 1 if any Fct Pri ff set                                                                |

|               | Chan Req → Chan Pri if I/Ol, ff clear                                                                               |

| T2.4          | Clear Chan & Fct Pri if I/Ol, ff clear                                                                              |

| T3.1          | Int Req→Chan Pri if I/Ol; ff clear                                                                                  |

| Т3.2          | Drop Chan Req─>Chan Pri√                                                                                            |

| T3.4          | Int Req $\longrightarrow$ Fct Pri if I/Ol <sub>i</sub> ff clear, clear Chan & Fct Pri if I/Ol <sub>i</sub> ff clear |

| T4.1          | Clear I/O Trans 2, clear Fct, Chan, & I/O Trans 1 if $I/Ol_i$ ff clear                                              |

| T4.2          | Set $I/Ol_f$ ff if $I/Ol_i$ ff set $\sqrt{}$                                                                        |

|               | Set Int; ff if (any Fct Pri ff set) · (I/Ol; ff clear)                                                              |

|               | I/O Trans 1 $\longrightarrow$ I/O Trans 2 if I/Ol <sub>i</sub> ff set $\checkmark$                                  |

|               | Pri -> Fct, Chan, & I/O Trans 1 if I/Ol <sub>i</sub> ff clear                                                       |

TABLE 8.4-3. CHANNEL PRIORITY GATES, CHASSIS 1 AND 2

|           | Gates  | Conditions to Output High Level                                                                                                                                                                                                                    |

|-----------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 10V13~ | Chan 7                                                                                                                                                                                                                                             |

|           | 10V12  | Chan 5 · chan 7 · chan 6                                                                                                                                                                                                                           |

| Chassis l | 10V11  | Chan 3 · chan 7 · chan 6 · chan 5 · chan 4                                                                                                                                                                                                         |

| Chassis I | 10V10  | $\frac{\text{Chan } 1 \cdot \overline{\text{chan } 7} \cdot \overline{\text{chan } 6} \cdot \overline{\text{chan } 5} \cdot \overline{\text{chan } 4} \cdot \overline{\text{chan } 3}}{\overline{\text{chan } 3} \cdot \overline{\text{chan } 2}}$ |

|           | 12V11  | Chan 5 or 7 selected                                                                                                                                                                                                                               |

|           | 12V10  | Chan 3 or 7 selected                                                                                                                                                                                                                               |

|           | 10V03  | Chan 6 · chan 7                                                                                                                                                                                                                                    |

|           | 10V02  | Chan 4 · chan 7 · chan 6 · chan 5                                                                                                                                                                                                                  |

| Chassis 2 | 10V01  | Chan 2 · chan 7 · chan 6 · chan 5 · chan 4 · chan 3                                                                                                                                                                                                |

| Shaddid 2 | 10000  | $\frac{\text{Chan } 0 \cdot \text{chan } 7 \cdot \text{chan } 6 \cdot \text{chan } 5 \cdot \text{chan } 4}{\text{chan } 3 \cdot \text{chan } 2 \cdot \text{chan } 1}$                                                                              |

|           | 12V01  | Chan 4 or 6 selected                                                                                                                                                                                                                               |

|           | 12V00  | Chan 2 or 6 selected                                                                                                                                                                                                                               |

Even though each I/O chassis has function priority logic like that shown, only one function priority on each drawer will be presented with signals. This is because the two channel priorities on each drawer are inter-connected such that only one channel is selected between them. Then, only the function priority on the chassis of the selected channel will receive signals.

11Vg4 outputting a low level indicates that at least one of the function priority flip-flops is set or that a signal has been selected on its chassis. The two outputs of this logic to figure 9-51 will specify the type of selected signal. If OlVq7 (EI flip-flop) outputs a high level, the selected type is either EF/OD or ID; since there is no EI type, and it has the highest function priority.

The high level output of 12Vg6 is prevented by its input from the EI flip-flop if an EI type is present. If the EI flip-flop is clear, 12Vg6 can output a high level if an ID type is selected. This selection is determined by 11Vg6. 11Vg6 outputs a low level if no EF/OD type is present or if an ID type is present and output was last. The output last indication from 51Vg4 actually means the Priority Alternator

flip-flop is set. This flip-flop is set whenever an OD or EF Acknowledge signal is sent and is cleared whenever an ID Acknowledge signal is sent. Both of these acknowledges are on this same chassis. This flip-flop then allows the function priority of EF/OD and ID type signals to be reversed depending upon the type of I/O operation performed last.

The outputs of the EI flip-flop, 12Vg6, and 12Vg4 then indicate the presence of a signal on this chassis and the type of the selected signal. Refer to table 8.4-4 for the signal type translation indication from this logic.

| ſ |                      | PRIORITY OUT  | PUTS  |

|---|----------------------|---------------|-------|

|   | SELECTED SIGNAL TYPE | OlVg7 (EI ff) | 12Vg6 |

| ſ | EI                   | L             | L     |

|   | EF/OD                | Н             | L     |

| . | ID                   | Н             | Н     |

|   | ID                   | Н             | Н     |

TABLE 8.4-4. FUNCTION PRIORITY SELECTION INDICATIONS

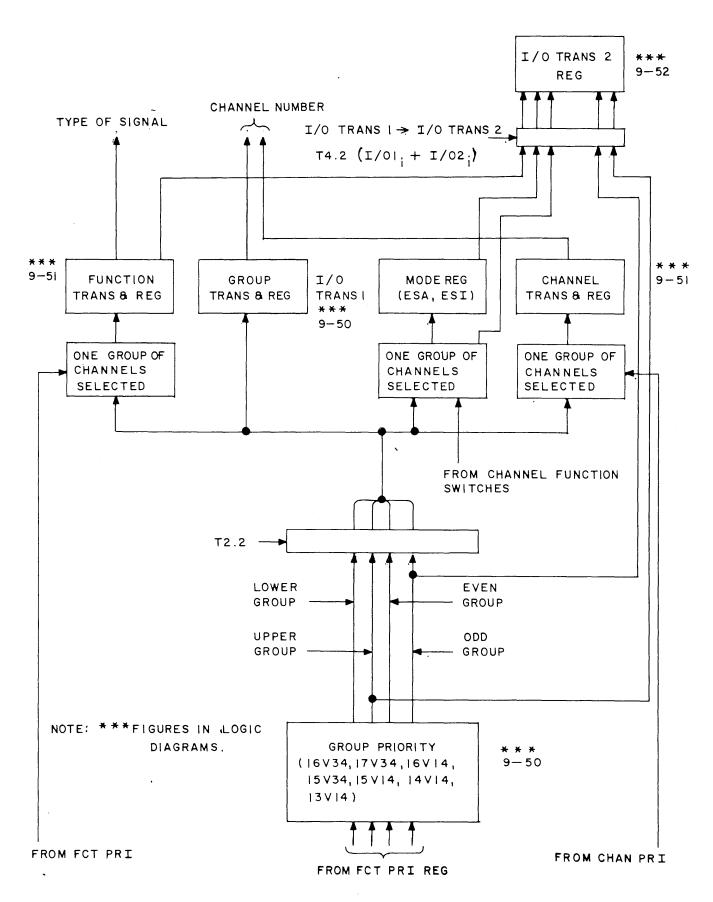

## 6. Group Priority. Refer to logic diagrams, figure 9-50.

Group priority logic is comprised of gates 16V34, 17V34, 16V14, 15V34, 15V14, 14V14, and 13V14. This logic receives indications from each of the four function priorities, by way of the 12V94 inputs, as to whether or not these priorities contain a signal. A high level from a 12V94 gate indicates that a signal has been selected on its chassis. From this information, group priority simply selects the signal of higher channel number; which means it selects the I/O chassis that has the selected signal. The effect of chassis selection is to allow the outputs of the channel priority and function priority on the selected chassis to enter the function and channel translators. Refer to table 8.4-5 for the group priority selection indications.

The group priority outputs are combined by the I/O translator 1 to select one chassis.

7. Group Translator (I/O Translator 1). Refer to logic diagrams, figure 9-50.

The group translator logic is comprised of flip-flops OXGO7, OXGO8, and OXGOO and their output gates. These flip-flops are set according to the selection made by group priority. Flip-flop OXGOO is set by the odd channel gate signal. Refer to logic diagrams, figure 9-49 to see that this signal is dependent upon timing and the fact that group priority has selected an odd channel chassis.

Thus, 0X600 being set indicates an odd chassis signal has been selected. Its clear state indicates an even chassis signal.

TABLE 8.4-5. GROUP PRIORITY SELECTION INDICATIONS

|                          | Function Priority Gate Outputs upper-group lower group |                   |     |                 |                  |                                                                                                                                                      |

|--------------------------|--------------------------------------------------------|-------------------|-----|-----------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Group Priority<br>Gates  | chass 9<br>12V34                                       | chass 10<br>12V24 |     | hass l<br>12V14 | chass 2<br>12V04 | Meaning of<br>Group Priority Gate Outputs                                                                                                            |

| 13V14 = L                |                                                        |                   |     | Н               |                  | Chassis l signal                                                                                                                                     |

| 14V14 = H                |                                                        | (L ;              | and | Н)              |                  | (Chass l signal) · (no chass<br>10 signal)                                                                                                           |

| 15V14 = L                | (Н) о                                                  | r (L ;            | and | H)              |                  | (Chass 9 signal) + (chass l<br>signal · no chass 10 sig-<br>nal) - same as "odd group"                                                               |

| 16V14 = L                | (L) a                                                  | <br>nd (H (       | or  | L)              |                  | (Chass 10 signal · no chass 9 signal) + (no chass 9 signal · no chass 1 signal) same as (chass 10 signal) + (chass 2 signal)* - same as "even group" |

| 15V34 = L<br>& 17V34 = L | (Н о                                                   | l<br>r H)         |     |                 |                  | (Chass 9 signal) + (chass 10 signal) - same as "upper group"                                                                                         |

| 16V34 = L                | (L o                                                   | r L)              |     | ·               |                  | (No chass 9 signal) · (no chass 10 signal) + (chass 2 signal)* - same as "lower group"                                                               |

<sup>\*</sup>This chart assumes a signal to be present on at least one chassis. Therefore, if a gate is conditioned by the absence of signals on a chassis, it indicates the presence of a signal on another chassis.

The setting of flip-flop OXGO7 is dependent upon timing from the request gate signal and also the fact that group priority has selected an upper chassis (chassis 9 or 10). Thus, OXGO7 being set indicates an upper chassis signal has been selected. Its clear state indicates a lower chassis signal.

Flip-flop OXGO8 is set simply to indicate that a signal has been selected by priority and is present in the translator. The setting of this flip-flop is enabled by the same timing input as is OXGO7. The other enable to set OXGO8 is from 13VO4. Notice that 13VO4 is fed by the 12Vg4 gates of function priority. If any signal is present in any function priority, 13VO4 outputs a low level. Thus, OXGO8 being set indicates a signal is present and enables the group translator gates (20G10, 20G11, 20G12, and 20G13). Refer to table 8.4-6 for the group translator indications.

| TRANSLATOR FLIP-FLOPS |       |                                                   |

|-----------------------|-------|---------------------------------------------------|

| OXG07                 | OXG00 | INDICATIONS                                       |

| Clear                 | Clear | 20Gl0 = H; chassis 2 selected (lower-given group) |

| Clear                 | Set   | 20Gll = H, chassis l selected (lower-odd group)   |

| Set                   | Clear | 20G12 = H, chassis 10 selected (upper-even group) |

| Set                   | Set   | 20G13 = H, chassis 9 selected (upper-odd group)   |

TABLE 8.4-6. GROUP TRANSLATOR INDICATIONS

A signal is assumed to be present (flip-flop OXGO8 set).

8. Mode Translator (I/O Translator 1). Refer to logic diagrams, figure 9-50.

If the selected channel is odd, the position of the CHANNEL FUNCTION switch for that chassis is sensed. If the switch position is either dual, ESI, or ESA, the associated flip-flop is set. The Dual flip-flop is actually part of I/O Translator 2 and its setting is performed at a later time if the output of llGO9 is a low level. If the selected channel is even, single channel mode is enforced.

9. Channel Translator. Refer to logic diagrams, figure 9-51.

The channel translator is comprised of flip-flops OXGO2 and OXGO1 and their output gates. These flip-flops are set according to the selection made by channel priority on the chassis selected by group priority. The channel priority inputs are from the 12Vg- gates. Two of these inputs enter the channel translator as selected by the 16V34, 17V34, 13E00, and 14E00 inputs from group priority. Refer back to table 8.4-3 for the translation of the 12Vg- inputs.

The Channel Translator flip-flops actually indicate the selected channel of the selected chassis. When channel translation is combined with the Group Translator outputs, the complete channel number is described. Channel translation is performed by gates 20G00, 20G01, 20G02, and 20G03. Refer to table 8.4-7 for the channel translation indications.

10. Function Translation. Refer to logic diagrams, figure 9-51.

The function translator is comprised of flip-flops OXGO5 and OXGO4 and their output gates. These flip-flops are according to the selection made by function priority on the chassis selected by group priority. The function priority inputs are from the  $12\,\text{Vg}6$  gates and the EI function flip-flops (O1Vg7 inputs). Two of these inputs enter the function translator as selected by the  $16\,\text{V34}$ ,  $17\,\text{V34}$ ,  $13\,\text{EOO}$ , and  $14\,\text{EOO}$  inputs from group priority. Refer back to table 8.4-4 for the translation of the inputs from function priority.

Function translation is performed by gates 20G04, 20G06, and 20G07. Refer to table 8.4-8 for the function translation indications.

| TRANSLATOR FLIP-FLOPS OXGO2 OXGO1 |       | INDICATIONS                                 |

|-----------------------------------|-------|---------------------------------------------|

|                                   |       |                                             |

| Clear                             | Clear | 20G00 = H; channel 0, 1, 10, or 11 selected |

| Clear                             | Set   | 20G01 = H; channel 2, 3, 12, or 13 selected |

| Set                               | Clear | 20G02 = H; channel 4, 5, 14, or 15 selected |

| Set                               | Set   | 20G03 = H; channel 6, 7, 16, or 17 selected |

TABLE 8.4-7. CHANNEL TRANSLATOR INDICATIONS

TABLE 8.4-8. FUNCTION TRANSLATOR INDICATIONS

| TRANSLATOR<br>OXGO5 | FLIP-FLOPS<br>OXGO4 | INDICATIONS                        |

|---------------------|---------------------|------------------------------------|

| Clear               | Clear               | 20G07 = H, EI function selected    |

| Set                 | Clear               | 20G06 = H, EF/OD function selected |

| Set                 | Set                 | 20G04 = H, ID function selected    |

The condition of OXGO5 clear and OXGO4 set is not used.

The function translator outputs are used to dictate the basic operation to be performed by the  $\rm I/O$  logic in honoring the selected signal.

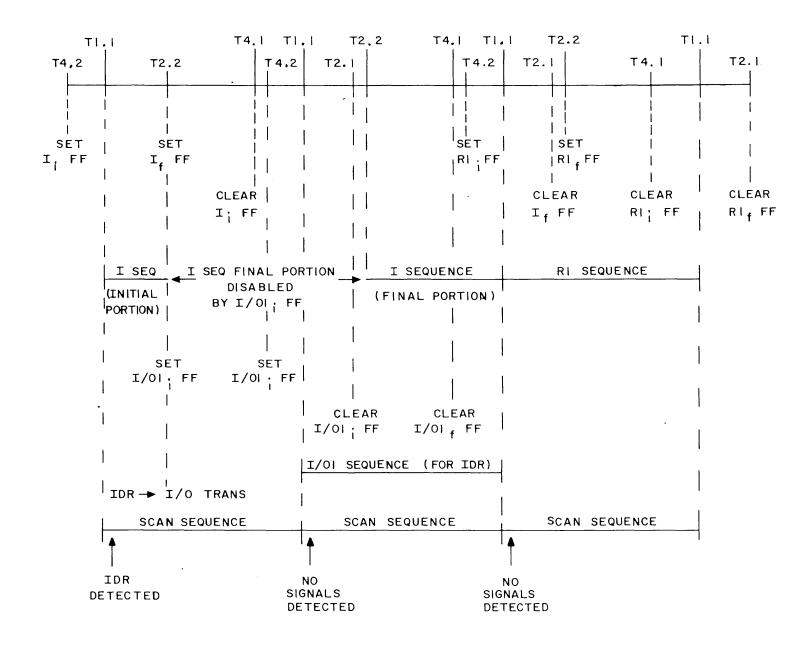

11. Data Request Sequence Timing. The honoring of a data request involves the use of memory under control of the I/O sequences. Single channel operation uses only the I/Ol-sequence, one main memory cycle. In this case, the program sequences are disabled for 2 microseconds. Dual channel operation requires two main memory cycles to complete the transfers of both halves of a 36-bit word. The I/Ol and I/O2 sequences are used, and the program sequences are disabled for four microseconds.

The scan sequence is always running to detect and select I/O signals to be honored. If a signal is detected, it is gated into the priority logic and then into the I/O translator. If the scan sequence selects a data request signal to be honored, as the signal information is placed in the I/O translator the I/Ol $_{\rm i}$  flip-flop is set. The next 2 microsecond period beginning with Tl.l time is then considered to be the I/Ol-sequence, and the requested I/O service is performed.

There is no scan flip-flop; rather, every main timing cycle is considered to be a scan sequence which is testing all signal entrance logic for I/O requests. Therefore during each sequence of each instruction, the possibility of I/O operation is being tested by the priority logic. The detection of a data request activates the I/Ol-sequence during which the program is effectively halted. The amount of delay to the program is determined by whether the I/O service involves single or dual

channel operation. This delay period will be extended by consecutive I/O-sequences if data requests are continually selected by consecutive scan sequences. Since the scan sequence also runs during the I/Ol-sequence, it is conceivable that each main timing cycle could be under control of an I/O sequence and the program would not progress. In a practical situation, however, there would not be such an extended period of continual I/O activity because of the limited speed of peripheral devices and the high speed of the computer in handling an I/O request.

The scan sequence can be effectively disabled under certain conditions by preventing the setting of the  $\rm I/Ol_i$  flip-flop. A direct disable to this flip-flop is present if f = 57 and the Rl-sequence is in control or if f = 20-23 and the first Rl-sequence is in control (without the R2-sequence). These conditions also prevent the setting of the  $\rm I/O2_i$  flip-flop. Refer to logic diagrams, figure 9-13 for this disable.

An indirect disable to the setting of the  $I/Ol_i$  flip-flop is the prevention of the Data Req Function Priority command. This disable can exist if the  $I/Ol_f$  flip-flop is set and the I/O service being performed involves dual channel operation or ESI/ESA which has a terminate condition. Both of these conditions require the I/O2-sequence to follow the I/O1-sequence. This indirect disable to the I/O1-sequence also exists if the CDM-sequence is to be run. Refer to logic diagrams, figure 9-49 for this disable.

The disable to the program sequences by the I/O-sequences occurs between the initial and final portions, beginning at T2.2 time. During the set time of either the I/Oli or I/O2i flip-flop, the outputs of the If, Rlf, R2f, and Wf flip-flops are disabled; and the setting of the Ii, Rli, R2i, Wi, Bli, and B2i flip-flops is inhibited. During the set time of either the I/Olf or I/O2f flip-flops, the advancing of the sequence final flip-flops is prevented. That is, the setting and clearing of the If, Rlf, R2f, Wf, Blf, and B2f flip-flops is inhibited.

These disable conditions are such that any sequence of any instruction may effectively be halted after the operations controlled by the sequence initial flip-flop are executed and those operations caused by the sequence final flip-flop will not be performed until after the interrupting I/O service is performed. The halting point can be considered to be at T2.2 time, the setting time for the program sequence final flip-flop as well as the setting time for the I/Ol and I/O2 flip-flops.

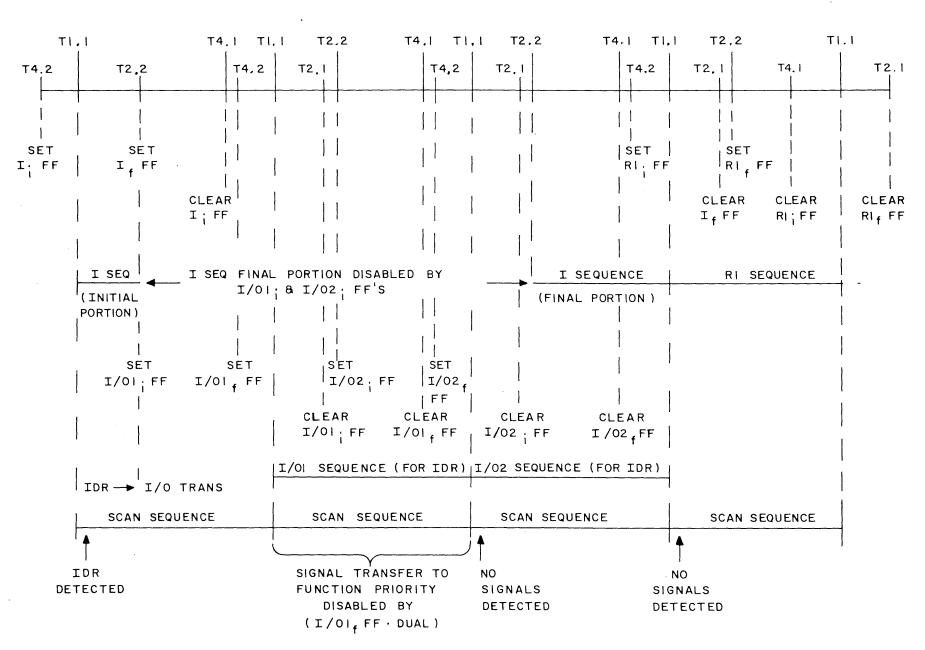

Refer to figures 8.4-3, 8.4-4, and 8.4-5 for timing diagrams illustrating possible relationships of the program and I/0-sequences. These diagrams show the I/0 operations interrupting the I-sequence. Realize that any sequence can be disturbed in the same manner.

#### 8.4-5. SUMMARY

Channel, function, and group priorities select the highest channel number which has a signal present and then one type of signal on that channel to be honored. The translators have flip-flops to hold that selected signal information and translation gates to inform the rest of the  $\rm I/O$  logic as to the type of operation to be performed and the channel involved.

Operations concerning the real time clock and special interrupts are discussed in later sheets.

Figure 8.4-3. Single Data Request, Single Channel, Timing Example

Figure 8.4-4. Single Data Request, Dual Channel, Timing Example

1219 (M)8.4

Figure 8.4-5. Multiple Data Request, Single Channel, Timing Example

|             |          |                                     |             |             | NAME:       |                                               |

|-------------|----------|-------------------------------------|-------------|-------------|-------------|-----------------------------------------------|

| 8.4-6. STUI | DY QUEST | IONS                                |             |             |             |                                               |

| a.          | Refer t  | o logic diag                        | rams, figur | es 9-50 and | 9-51.       |                                               |

|             |          | $0 \times 602$ , and $0 \times 600$ |             |             |             | , OXGO5, OXGO4,<br>on channel 13 <sub>8</sub> |

| OXG08       | OXGO7    | · 0XGO2                             | OXGO1       | OXG00       | OXG05       | OXGO4                                         |

|             |          | ·                                   |             |             |             |                                               |

| b.          | Refer t  | o logic diag                        | rams, figur | e 9-50.     |             |                                               |

|             |          | g that the fi                       |             |             |             | priority gates<br>and 2 contain               |