# ST412 INTERFACE AND STEPPER MOTOR DRIVE MICROCODE CLASS

By Litko Chan 12/02/87

#### **DUTLINE**

- Overview.

- ST412 Interface.

- Power-up sequence (ST251).

- Seek modes.

- Drive recalibration (Auto-truncation).

- Recovery Mode.

- Seek settling (Ring Detection).

- Auto-tuning.

- Access time.

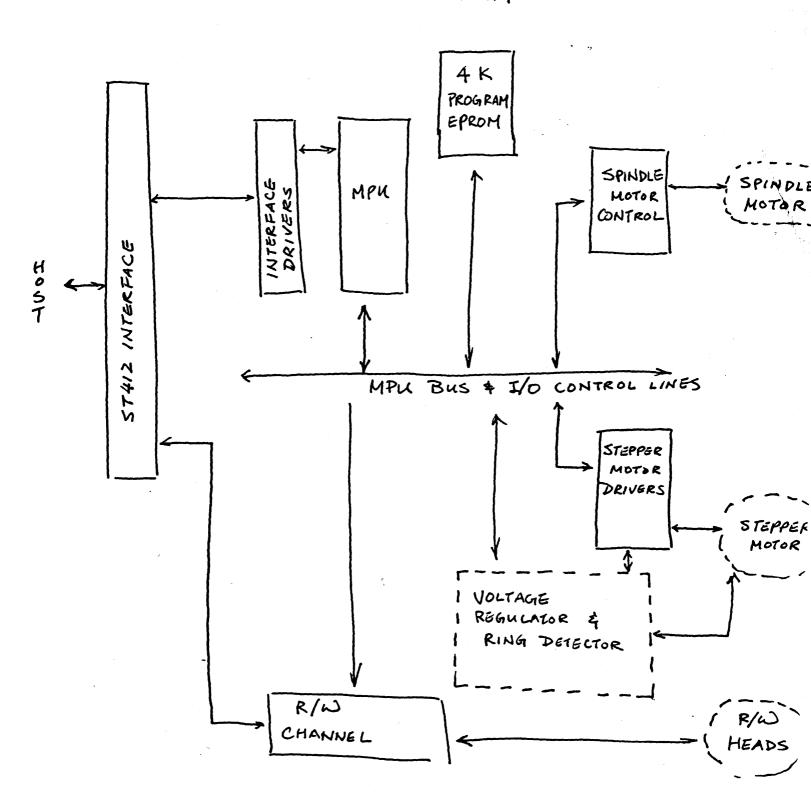

ST412 STEPPER DRIVE BLOCK DIAGRAM

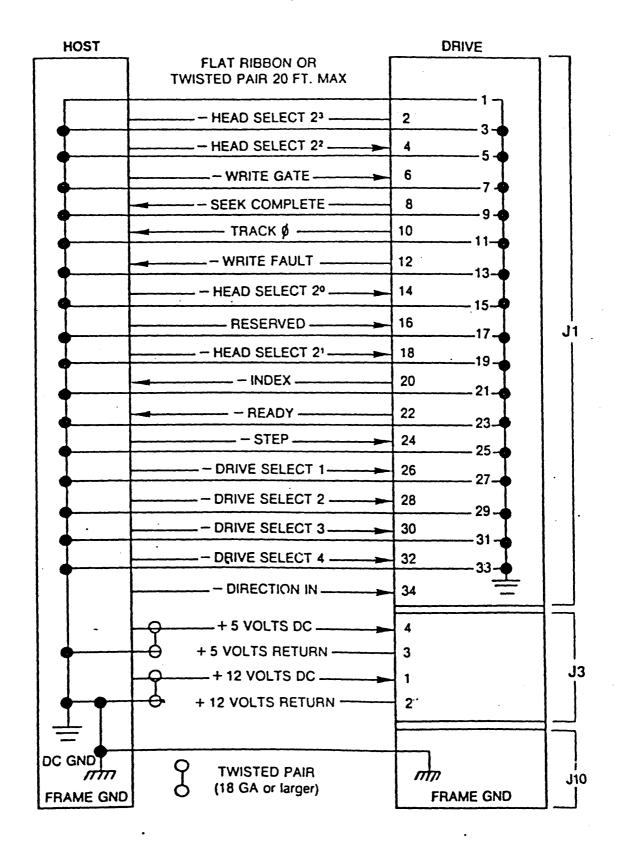

# Control/Status Signals

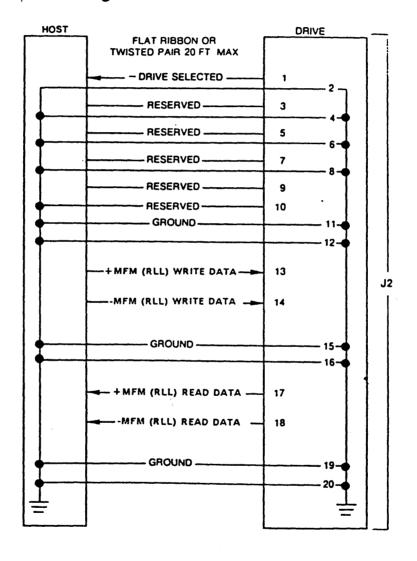

## Data Signals

1-6

Seagate ST412 Interface Manual

### ST412 INTERFACE SIGNALS

#### CONTROL INPUT SIGNALS:

- DRIVE SELECT LINES

- HEAD SELECT LINES

- WRITE GATE

- STEP

- DIRECTION IN

- RECOVERY MODE

#### CONTROL OUTPUT SIGNALS:

- DRIVE SELECTED

- INDEX

- TRACK O

- READY

- SEEK COMPLETE

- WRITE FAULT

#### CONTROL INPUT SIGNALS

#### DRIVE SELECT LINES

The Drive Select line is activated by the controller to select and address the drive.

#### **HEAD SELECT LINES**

Head Select lines 2<sup>0</sup>, 2<sup>1</sup>, 2<sup>2</sup> and 2<sup>3</sup> allow the selection of each Read/Write head in a binary code sequence. Head Select line 2<sup>0</sup> is the least significant line. When all Head Select lines are high on the interface, Head 0 is selected.

Note: Depending on the product, one or more Head \*Select lines may not be required, and therefore terminated. These lines are present on the interface, but the drive will not respond to input signals on any terminated line(s).

#### WRITE GATE

The active state of this signal, or low level, enables the data to be written to the disc. When inactive, or high, this signal enables data to be transferred from the drive and enables Step pulses to move the heads. Heads may not be moved while Write Gate is active.

#### **STEP**

The Step signal is a 2 microsec. minimum width pulse that initiates Read/Write head motion. The Step pulse period determines the access method. The pulse number of pulses determines seek length.

Step pulse periods for specific products may be found in the Product Manuals.

The Direction In line must be stable 100 nsec. before the leading edge of the first pulse and remain stable for a 100 nsec. after the last pulse in a string of Step pulses.

If excessive Step pulses are issued which would cause a seek inward beyond the maximum data cylinder, or outward beyond Track Ø the drive will enter the Auto Truncation mode. Refer to "2.3.3 Auto-Truncation".

### DIRECTION IN

The Direction line defines the direction the Read/Write heads will move when the Step line is pulsed. With Direction In true, each pulse causes the heads to move one cylinder inward toward the spindle. When Direction In is false, each pulse causes the heads to move one cylinder outward toward Track Ø.

#### **CONTROL OUTPUT SIGNALS**

#### DRIVE SELECTED

Drive Selected is a status signal transmitted over J2, which informs the host system of the selection status of the drive. The signal is driven by a TTL open collector. The signal goes true on the interface only when the drive is configured correctly, and the appropriate Drive Select line is activated by the host system.

#### INDEX

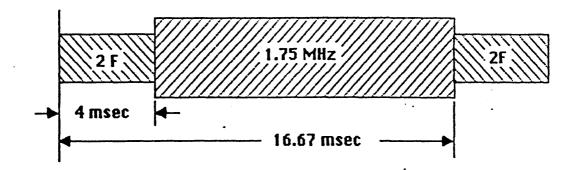

This signal is provided by the drive once each revolution (16.67 msec. nominal) to indicate the beginning of a track. Normally this signal makes the transition to low to indicate Index. Only the transition from high to low, or the leading edge, is valid.

#### \_. 3.3 TRACK Ø

This signal indicates a low level (true) when the Read/Write heads are positioned at Cylinder Zero.

Track Ø is the only cylinder that provides interface recognition. The drive is designed to recalibrate to Track Ø during power-on and Auto-Truncation operations.

Track  $\emptyset$  may also be accessed via conventional buffered and single-track seek modes. After Track  $\emptyset$  is true, no actions may be taken by the controller until Seek Complete is also true.

#### **READY**

This signal, when true together with Seek Complete, indicates that the drive is ready to Read, Write or Step and that all control input signals are valid. When the line is high, all reading, writing, and stepping is inhibited.

During the power-up sequence, Ready remains false until:

- 1. The recalibration to Track Ø is complete

- 2. Spindle speed is stable within:

- a.  $\pm 0.5\%$  of nominal for the ST4000 series drives

- b. +0.5% of nominal for the ST251

- c.  $\pm 1\%$  of nominal for the ST213, ST225, ST238

- 3. Drive initialization routines are complete

- 4. DC voltage are within tolerances

Refer to the Product Manual for maximum power-up time.

#### SEEK COMPLETE

This signal goes to the low level on the interface when the Read/ Write heads have settled on the target track at the end of a seek. Seeking, reading or writing should not be attempted when Seek Complete is false. Seek Complete goes false in the following cases:

- 1. When a recalibration sequence is initiated (by drive logic) at power-on

- 2. 100 nsec. typical after the leading edge of a Step pulse

- 3. If either +5 or +12 Volts are detected as unsafe

- 4. If the drive attempts a Seek-Retry after settling on a track (Drive-specific feature)

#### → S WRITE FAULT

This signal notifies the host system that a condition exists which, if not corrected, may cause an incorrect Write operation.

#### ST251 POWER UP SEQUENCE

- 01) Microprocessor gets reset.

- 02) Initialize all circuitries to default conditions.

- 03) Stiction jump.

- 04) Check spindle speed.

- 05) Loop in step 5 until spindle speed is within +/- .5% of the specified rotational speed (3600 RPM).

- 06) Recalibrate drive to cylinder 0.

- 07) Perform two shoe-shine seeks to shretch the band.

- 08) Perform Auto-tuning to find optimum seeking voltage.

- 09) Check Life-test Jumper. Jump to step 11 if jumper is open.

- 10) Perform shoe-shine seeks. Loop if step 10 while the Life-test Jumper remains close.

- 11) Set TRACK O, READY, and SEEK COMPLETE.

- 12) Stay in IDLE loop until a STEP is received.

#### SEEK MODES

#### - BUFFERED SEEK:

Buffered seeks are performed when the incoming pulses are issued by the host a rate of 3 us to 200 us. The host must not vary the pulse rate during a single seek command. In general, buffered seeks can be separated into two modes:

- NON-OVERLAPPED SEEK MODE (41 US - 200 US)

In non-overlapped seek mode, incoming step pulses are issued at a fixed rate between 41 to 200 microsecond. At this rate, initiation of a seek starts shortly after the LAST pulse is received.

- OVERLAPPED SEEK MODE (3 US - 40 US)

In overlapped seek mode, incoming step pulses are issued at a fixed rate between 3 to 40 microsecond. At this rate, the drive is capable of maintaining the step count while a seek is being performed. Therefore, initiation of a seek may be started shortly after the FIRST pulse is received. The advantage of this seek mode is to optimize access timing.

#### - SLOW-STEP MODE ( 3 MS OR GREATER)

In Slow-Step, the read/write heads move at the rate of the incoming step pulses. The minimum period between pulses is 3 msec. SEEK COMPLETE is issued after the drive received the last pulse and applies sufficient settling delay after seeking to the final target track. This seek mode is used typically by some PRE-HISTORIC controllers for recalibrating the read/write heads back to cylinder 0.

## 2.3.3 AUTO-TRUNCATION

The drive will enter the Auto-Truncation mode if the controller issues an excessive number of Step pulses, which would place the Read/Write heads outward beyond Track  $\varnothing$  or inward beyond the maximum data cylinder.

With Auto-Truncation active, the drive will ignore additional pulses, take control of the actuator, and recalibrate the heads to Track Ø.

Caution: If the controller is still issuing Slow-Step pulses after the drive issues Seek Complete from Auto-Truncation mode, the drive will either reenter Auto-Truncation mode with Direction In false, or step the remaining cylinders with Direction In true.

| 57251      |              |         |     | 5 PHASE STEP TABE 7-29-85 UNK |     |    |     |            |          |     |     |                        |               |                 |

|------------|--------------|---------|-----|-------------------------------|-----|----|-----|------------|----------|-----|-----|------------------------|---------------|-----------------|

| <b>~</b> · | STEP         | A       | Ā   | B                             | B   | c  | ار  | <b>D</b> - | <u>D</u> | E   | ĺω  | 2¢                     | STEP<br>SIZE  | STEP            |

| =          | ø.           | 1 0     | 0 0 | 0 0 .                         | 1   | 1  | 0 0 | 0 0        | 1        | 1   | 0 0 | CĎ                     | · 1/2<br>Full | AB CDE<br>BCDE  |

|            | . 1.         | 00      | 7.  | 0.0                           | ~ 0 | 1  | 00  | 0 0        | 1.       | 1.  | 0 0 | DE                     | 1/2<br>FULL   | ABCDE<br>A CDE  |

|            | 2            | 0 0     | 1   | 1                             | 0 0 | 10 | 00  | 00         | 1        | 1   | 00  | ĀĘ                     |               | ABCDE<br>AB DE  |

|            | 3            | 0 0     | 1   | 1.                            | 00  | 00 | 1   | 00         | 10       | 1   | 00  |                        | 1 1           | ABC E           |

|            | 4            | 00      | 1   | 1                             | 0 0 | 00 | 1   | 1. /       | 0.0      | 10  | 0.0 | BC                     | 1/2<br>FULL   | ABCDE<br>ABCD   |

|            | 5            | 00      | 1.0 | 1                             | 00  | 00 | 1   | 1          | 00       | 00  | 1   | C D                    | 1/2<br>FULL   | ABCDE<br>BCDE   |

|            | 6            | 1       | 00  | 10                            | 00  | 90 | . ( | 1          | 00       | 0 0 | 1   | DE                     | 1/2<br>Fore   | ABCDE<br>A CDE  |

|            | 7            | 1       | 0   | 00                            | /   | 00 | 10. | 1          | .00.     | 0 0 | 1 7 | ĄĒ                     | .1/2<br>FULL  | ABCDE.<br>AB DE |

|            | 8            | /.<br>/ | 0.  | 00                            | 1   | 1  | 00  | 10         | 00       | 0 0 | 11  | AB                     | 1/2<br>Foce   | ABCDE<br>ABC E  |

|            | 9            | 1       | 00  | 00                            | /   | 1  | 00  | 00         | 1        | 00  | 10  | BC                     |               | ABCDE<br>ABCD   |

|            | 10<br>REVEAT | 10      | 00  | 00                            | 1   | 1  | 00  | 0          | 1        | 1   | 0.0 | $\subset \overline{D}$ | 1/2<br>FOLL   | ABCDE<br>BCDE   |

|            |              |         | •   |                               |     |    |     |            |          |     |     |                        |               |                 |

|            |              |         | ·   | ·                             |     |    |     |            | •        |     | ·   |                        |               | 12              |

| Track  | -4   | INDEX/TRACK LAYOUT R //////////////////////////////////// |                                                                                                                |                |  |  |  |  |  |  |

|--------|------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------|--|--|--|--|--|--|

|        | -3   | D.C. Erased                                               | Mtr Phase 7                                                                                                    | D.C.<br>Erased |  |  |  |  |  |  |

|        | -2   | Index                                                     |                                                                                                                | to<br>Crash    |  |  |  |  |  |  |

| _      | -1   | D.C. Erased                                               | Mtr Phase 9                                                                                                    | Stop           |  |  |  |  |  |  |

| _      | 8    | Outer Most Data Tr                                        | rk                                                                                                             |                |  |  |  |  |  |  |

| •      | +1   |                                                           |                                                                                                                |                |  |  |  |  |  |  |

| Track  | 819  | Inner Most Data Track                                     |                                                                                                                |                |  |  |  |  |  |  |

| • -    | 820  | D.C. Erased                                               | Mtr Phase Ø                                                                                                    |                |  |  |  |  |  |  |

| -<br>- | 821  | D.C. Erased                                               |                                                                                                                |                |  |  |  |  |  |  |

| -      | 822  | D.C. Erased                                               | Mtr Phase 2                                                                                                    |                |  |  |  |  |  |  |

|        | 823  | 1.75 MHz                                                  | Mtr Phase 3                                                                                                    |                |  |  |  |  |  |  |

| . ·    | 824  | B.C. Erased                                               | Mtr Phase 4                                                                                                    |                |  |  |  |  |  |  |

| _      | 825  | D.C. Erased                                               | Mtr Phase 5                                                                                                    |                |  |  |  |  |  |  |

| _      | 826  | 1.75 MHz                                                  | Mtr Phase 6                                                                                                    |                |  |  |  |  |  |  |

| - د.   | 827  |                                                           | D.C. Erased on Odd Tracks to Inner Crash Stop.                                                                 | _              |  |  |  |  |  |  |

| -      | 828  |                                                           | 1.75 MHz on all Tracks with Motor<br>Phases Ø and 6 to Inner Crash Stop.<br>All Other Even Tracks D.C. Erased. | <b>*</b>       |  |  |  |  |  |  |

|        | NOTE | All area outside of t<br>be D.C. Erased on 1.             |                                                                                                                |                |  |  |  |  |  |  |

before Index and 1.75 MHz are written.

## Index Track Data Pattern

2-11-86 K. Johnson

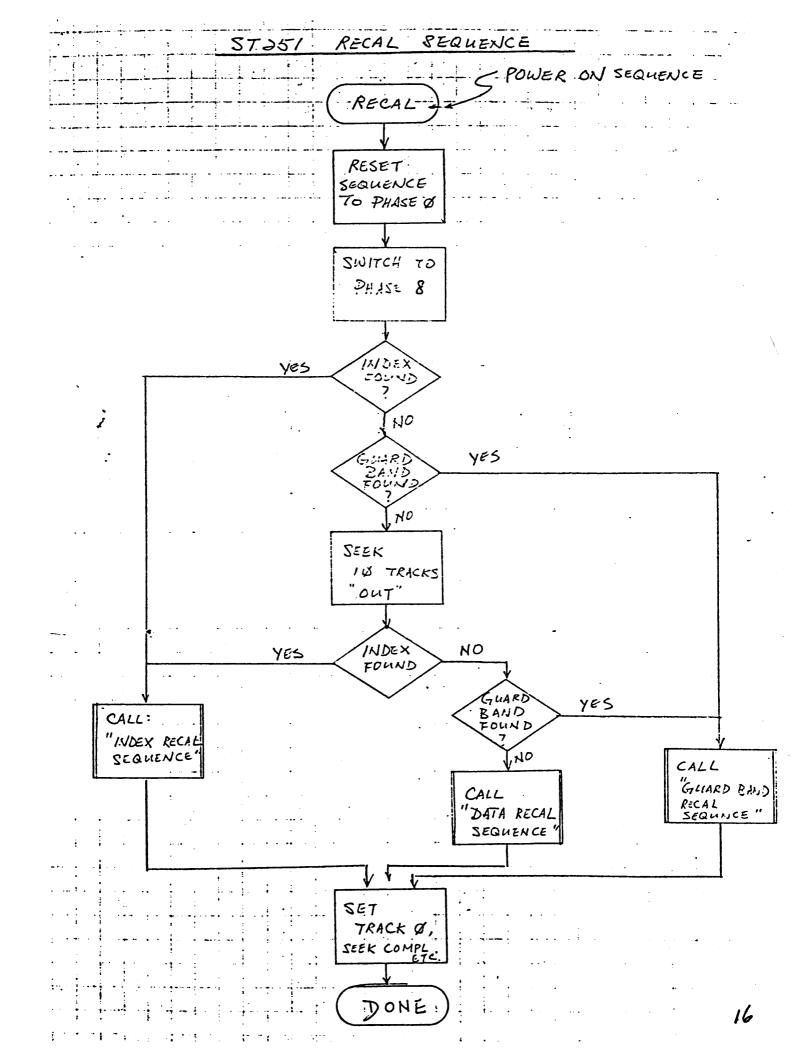

- 1. RESET SEQUENCER TO PHASE O.

- 2. SWITCH TO PHASE & (SAME PHASE AS -2).

- 3. VERIFY INDEX PATTERN.

- 4. GO TO STEP 14 IF INDEX PATTERN FOUND.

- 5. VERIFY GUARD BAND. ( PHASE & AND PHASE 6)

- 6. GO TO STEP 16 IF GUARD BAND DETECTED.

- ; 7. SEEK 10 TRACK QUI.

- 8. VERIFY INDEX PATTERN.

- 9. GO TO STEP 14 IF INDEX PATTERN FOUND.

- 10. VERIGY GUARD BAND.

- 11. GO TO STEP 16" IF GUARD BAND DETECTED.

- 12. APPLY "DATA RECAL SEQUENCE".

- 13. GO TO STEP 17.

- 14. APPLY "INDEX RECAL SEQUENCE".

- 15. GO TO STEP 17.

- 16. APPLY "GUARD BAND RECAL SEQUENCE".

- 17. LOCK INDEX.

- 18. SET TRACK O.

- 19. SET SEEK COMPLETE.

L.RC

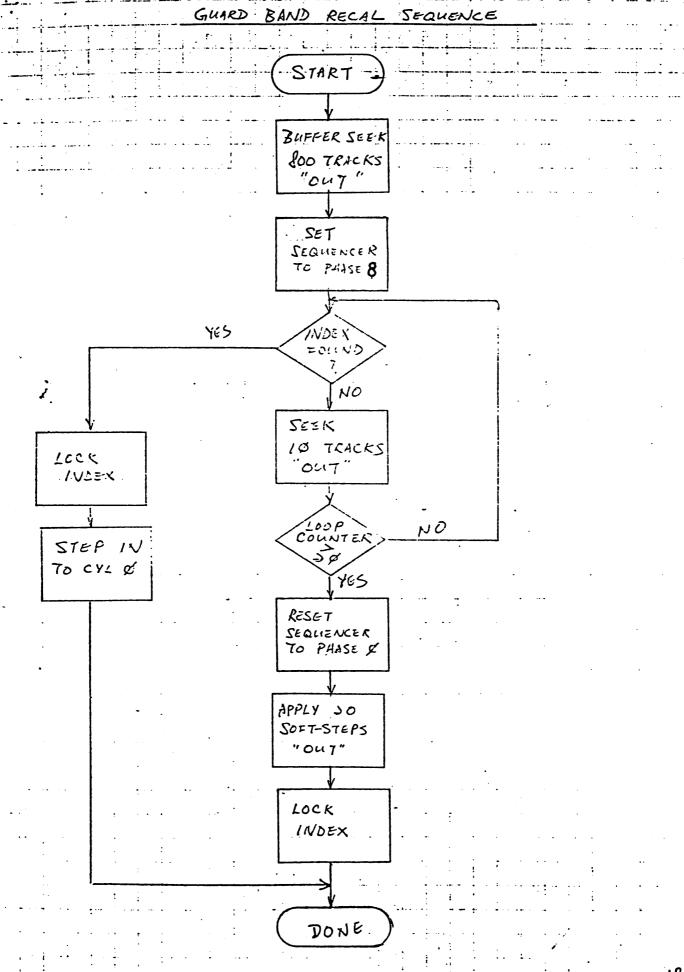

- 1. BUFFER SEEK 800 TRACKS OUT.

- 2. SET SEQUENCER TO PHASE 8.

- 3. VERIFY INDEX PATTERN.

- 4. GO TO STEP 12 IF INDEX PATTERN DETECTED.

- 5. SEEK 10 TRACKS DUT.

- 6. REPEAT STEP 3 STEP 5 UP TO 13 TIMES.

- 7. RESET SEQUENCER TO PHASE O

- 8. APPLY 20 SOFT-STEPS TOWARD THE O.D.

- 9. LOCK INDEX.

- 10. GO TO STEP 13.

- 11. LOCK INDEX.

- 12. STEP "IN" TO CYLINDER O.

- 13. DONE.

LRC

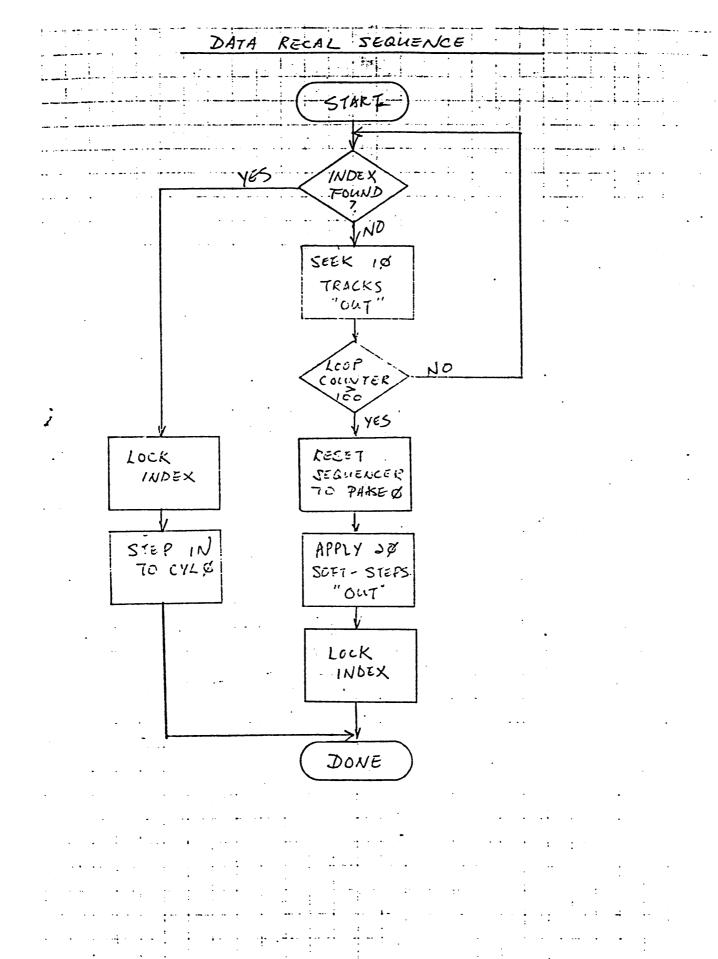

- 1. VERIFY INDEX PATTERN.

- 2. GO TO STEP 9 IF INDEX PATTERN DETECTED.

- 3. SEEK 10 TRACKS OUT.

- 4. REPEAT STEP 1 STEP 3 UP TO 93 TIMES.

- 5. RESET SEQUENCER TO PHASE O.

- 6. APPLY 20 SOFT-STEPS TOWARD THE O.D.

- 7. LOCK INDEX.

- 8. GO TO STEP 11.

- 9. STEP "IN" TO CYLINDER O.

- 10. LOCK INDEX.

- 11. DONE.

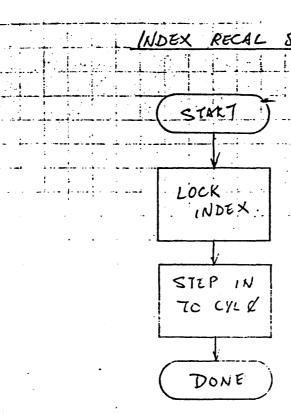

### INDEX BECAL SEQUENCE

12/4/85

- 1. STEP "IN" TO CYLINDER O.

- 2. LOCK INDEX.

- 3. DONE.

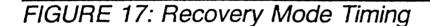

## **RECOVERY MODE**

RECOVERY MODE provides a read/write head micro-positioning option. It may be used after the controller has completed its retry options on a read error.

RECOVERY MODE is initiated by the controller asserting the RECOVERY MODE line low (true) at the interface. This changes the STEP line to a micro-step function after 100nsec. A step at this time will cause SEEK COMPLETE to go false 100nsec after the drive receives the step pulse. The drive then micro-steps off track using the optimum algorithm, allowing 20msec for the heads to settle, and then takes the SEEK COMPLETE line true. The controller may then attempt to read data. Refer to Figure 17 below. If data is not read correctly, the controller may issue an additional step pulse. Up to eight separate micro-step algorithms may be accessed before the sequence is repeated.

When data is read correctly, the controller exits RECOVERY MODE by taking the RECOVERY MODE line false on the interface. The drive then returns the heads to the nominal position by taking SEEK COMPLETE false, waiting 20msec for the heads to settle and reasserting SEEK COMPLETE.

10-28-87 JNK ()