APRIL 29-MAY 3, 1996 SAN JOSE, CALIFORNIA

# CONFERENCE PROCEEDINGS S P O N S O R E D B Y

PC<sup>2</sup> Consulting

0-929392-34-5

# PC SPRING

**DEVELOPERS' CONFERENCE AND EXPO**

APRIL 29-MAY 3, 1996 SAN JOSE, CALIFORNIA

# CONFERENCE PROCEEDINGS

S P O N S O R E D B Y

PC<sup>2</sup> Consulting

0-929392-34-5

You are welcome to send us comments or questions concerning this or other Annabooks products, or to request a catalog of our other products and seminars.

Annabooks 11838 Bernardo Plaza Court San Diego, CA 92128-2414

800-462-1042 619-673-0870 619-673-1432 FAX 73204.3405 @ compuserve.com

ISBN 0-929392-34-5

### Proceedings of PCI SPRING '96 Developers' Conference and Expo

April 29-May 3, 1996 • San Jose, California

| Preface                                                                                                                                       | ix |

|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

| Ed Solari, PC <sup>2</sup> Consulting LLC                                                                                                     |    |

| Session F1 Docking for Mobile Computing                                                                                                       | 1  |

| Harish Nayak, Cirrus Logic The New Digital Media Tony Shaharman, Intel Cornoration                                                            | 7  |

| Tony Sheberman, Intel Corporation  How to Implement a CardBus Solution  Gary Gildersleeve, Cirrus Logic                                       | 8  |

| Session F2                                                                                                                                    |    |

| PCI Technology for Industrial Control Systems—Benefits and Issues Clyde Thomas, Allen-Bradley Company, Inc., Rockwell Automation              | 12 |

| Using the PCI Bus for Packet Switching Applications Raymond Kolment, Teknor Industrial Computers                                              | 13 |

| Impact of PCI Technology on Control Solutions  Edwin Lee, Pro-Log Corporation                                                                 | 17 |

| Leveraging PCI in Data Acquisition Applications Richard J. Burk, Data Translation, Inc.                                                       | 22 |

| Session F3 Efficient Use of PCI Frank Hady, Intel Corporation                                                                                 | 26 |

| Session F4                                                                                                                                    |    |

| The Role of CardBus in a PCI Bus Hierarchy Claude A. Cruz, National Semiconductor Corporation                                                 | 44 |

| Session F7                                                                                                                                    |    |

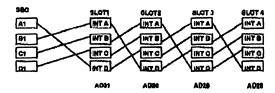

| Where Do I Plug the Cable? Solving the Logical-Physical Slot<br>Numbering Problem<br>Jeff Autor and Alan Goodrum, Compaq Computer Corporation | 51 |

| Session F8                                                                                                                                    |    |

| PowerPC <sup>TM</sup> Platform  Mike Becker, Motorola                                                                                         | 61 |

| Session F9                                                                                                                                    |    |

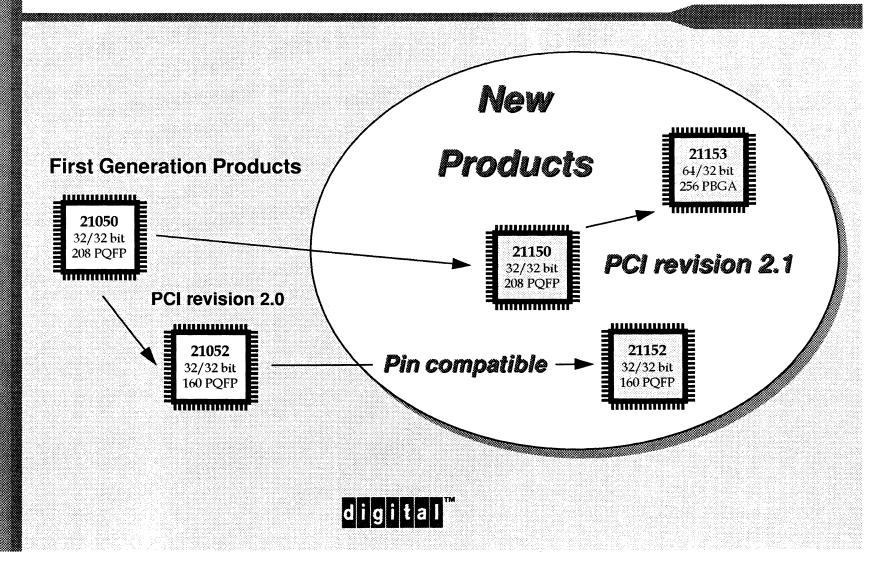

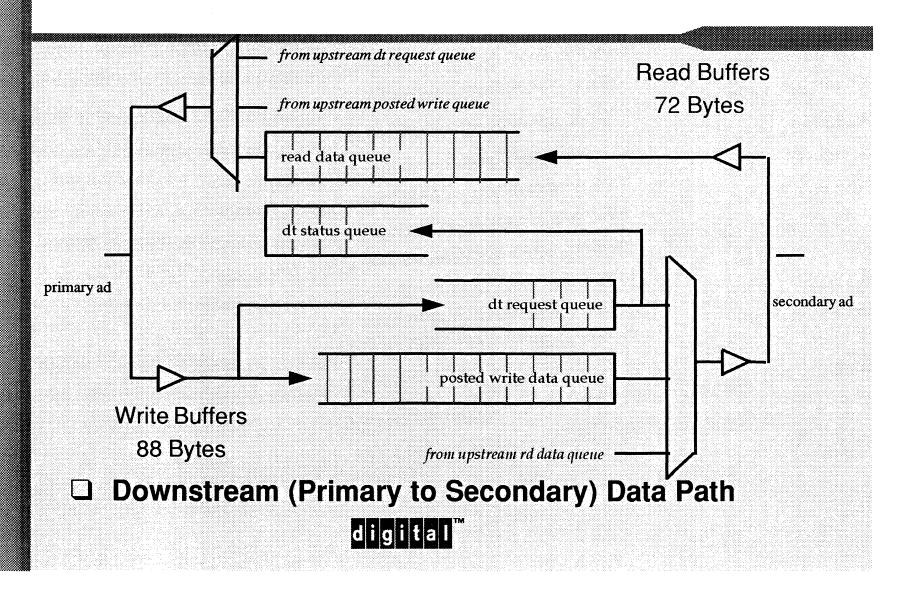

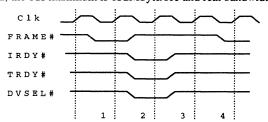

| The Standard in PCI to PCI Bridges  Tracy Richardson, Digital Semiconductor                                                                   | 71 |

| Design Issues for PCI-to-PCI Bridges  Thomas L. Anderson and Mark W. Knecht, Virtual Chips, Inc.;  Jacques Wong, Advanced Micro Devices       | 86 |

| PCI Interrupt Controller for Industry Standard PCI-ISA Bus Architecture                                   |      |

|-----------------------------------------------------------------------------------------------------------|------|

| Using PCI-to-PCI Bridge Technology                                                                        | 93   |

| Ross L. Armstrong, Digital Equipment Corporation                                                          | 101  |

| DCM's PCI-to-PCI Bridge Solution  Kamal Mansharamani, DCM DataSystems                                     | 101  |

| Session F12                                                                                               |      |

| PC-DMA and PCI: New Open Standard Blends Both                                                             | 109  |

| Dwight D. Riley, Compaq Computer Corporation                                                              |      |

| Session F13                                                                                               |      |

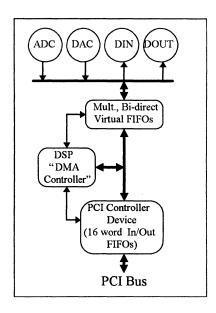

| A PCI Accelerator Architecture for the ADI SHARC DSP                                                      | 119  |

| Joseph A. Sgro, Alacron, Inc.                                                                             |      |

| PMC: The PCI Mezzanine Card                                                                               | 154  |

| Rodger H. Hosking, Pentek, Inc.                                                                           | 1.00 |

| DSP and I/O System Integration for PCI                                                                    | 160  |

| Jack Carter and Manish Kasliwal, Sonitech International Inc.                                              |      |

| Session F14                                                                                               | 1/1  |

| RACEway Interlink as a PCI Switching Fabric  Barry Isenstein and Bob Blau, Mercury Computer Systems, Inc. | 161  |

| PCI Bus Switching with the PSX                                                                            | 171  |

| Kent Dahlgren, I-Cube Incorporated                                                                        |      |

| Session 1A                                                                                                |      |

| The Future of PCI                                                                                         | 178  |

| Edwin Lee, Ed Lee Executive Workshop                                                                      |      |

| The Future of PCI                                                                                         | 186  |

| Bert Forbes, Ziatech Corporation                                                                          |      |

| Session 1B                                                                                                |      |

| PCI and Data Acquisition                                                                                  | 187  |

| Jim Fitzgerald, Keithley MetraByte                                                                        |      |

| Design Considerations for Data Acquisition Hardware on the PCI Bus                                        | 191  |

| Richard J. Burk, Data Translation, Inc. The Impact of BCI on the Test and Measurement Industry.           | 195  |

| The Impact of PCI on the Test and Measurement Industry  Arthur Ryan, National Instruments                 | 193  |

| Session 1C                                                                                                |      |

| Programmable Logic Implementations of PCI                                                                 | 199  |

| David Ridgeway, Xilinx                                                                                    | 1//  |

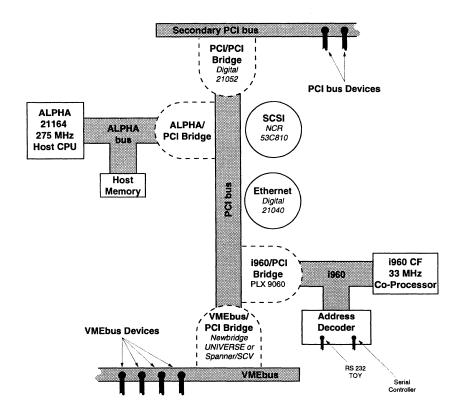

| PCI Is Not Just for PCs: Embedded Systems Migrate to PCI Architecture                                     | 200  |

| Mike Salameh, PLX Technology, Inc.                                                                        |      |

| Session 1D                                                                                                |      |

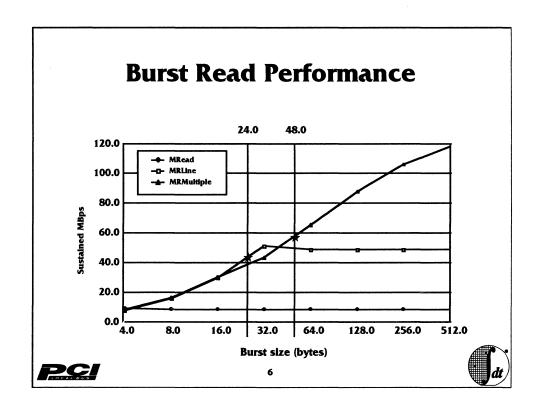

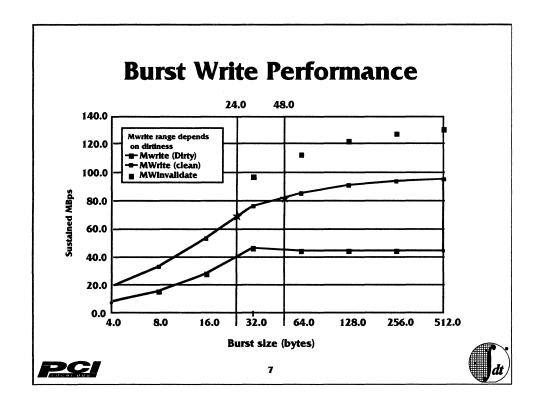

| PCI Performance Analysis for High-Speed Networking                                                        | 201  |

| Peter N. Glaskowsky, Integrated Device Technology, Inc.                                                   |      |

| The PCI Multi-Function Device: Benefits and Design Considerations                                         | 211  |

| Margit E. Stearns, Symbios Logic, Inc.                                                                    |      |

| Session 2A                                                                                                |      |

| XVideo Family for PCI                                                                                     | 214  |

| Bob Goodwin. Parallax Graphics                                                                            |      |

| New Generation Silicon for 3D Graphics on PCI                                                    | 215 |  |  |

|--------------------------------------------------------------------------------------------------|-----|--|--|

| Neil Trevett, 3Dlabs Inc.                                                                        | 225 |  |  |

| High-Speed DRAMs for PCI Systems                                                                 |     |  |  |

| Billy Garrett, Rambus Inc.                                                                       |     |  |  |

| Session 2B                                                                                       |     |  |  |

| Using PCI Interface in Routers                                                                   | 233 |  |  |

| Aamer Mahmood, Cisco Systems                                                                     |     |  |  |

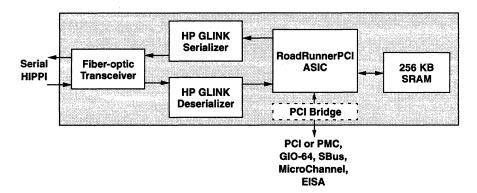

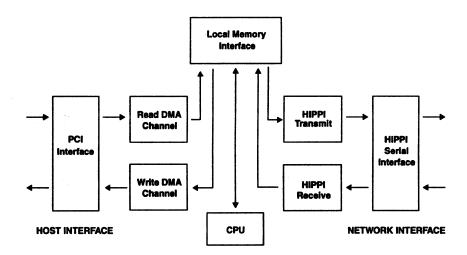

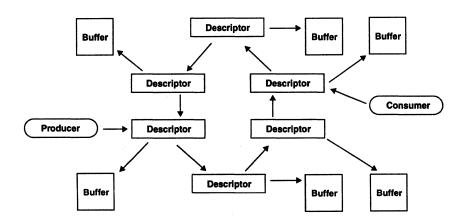

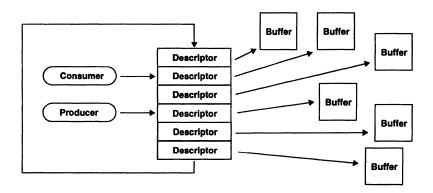

| Serial-HIPPI Network Interfaces Using the RoadRunnerPCI ASIC                                     | 234 |  |  |

| Michael McGowen, Essential Communications                                                        |     |  |  |

| Session 2C                                                                                       |     |  |  |

| Computer Makers Roundtable                                                                       | 243 |  |  |

| Donald F. McCook, Dolch Computer Systems                                                         |     |  |  |

| Session 2D                                                                                       |     |  |  |

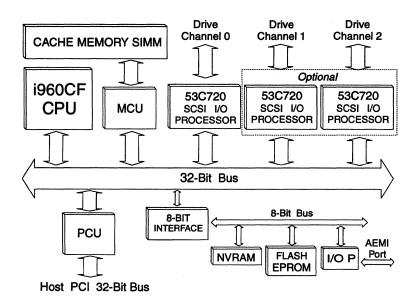

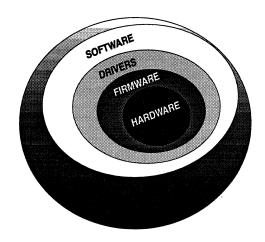

| PCI RAID Controllers                                                                             | 255 |  |  |

| K. K. Rao, Mylex Corporation                                                                     |     |  |  |

| Embedded RAID Presentation                                                                       | 261 |  |  |

| Scott Jensen, Adaptec                                                                            |     |  |  |

| Fast-40 SCSI, Pushing PCI to the Limit                                                           | 262 |  |  |

| Richard Mourn, Symbios Logic Inc.                                                                |     |  |  |

| Session 3A                                                                                       |     |  |  |

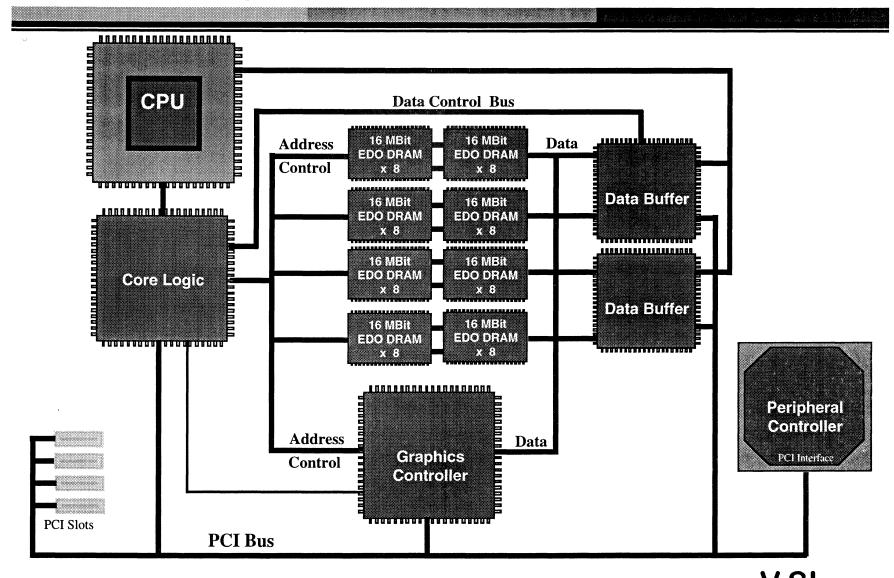

| What's Good & What's Bad About Unified Memory Architectures (UMA)                                | 268 |  |  |

| Desi Rhoden, VLSI Technology, Inc.                                                               | 200 |  |  |

|                                                                                                  |     |  |  |

| Session 3B                                                                                       |     |  |  |

| Leveraging PCI Bus Bandwidth and High Performance CPUs in                                        | 274 |  |  |

| Designing MPEG-1 and H.261 Video CODECs  Frank Schools Digital Equipment Comparation             | 2/4 |  |  |

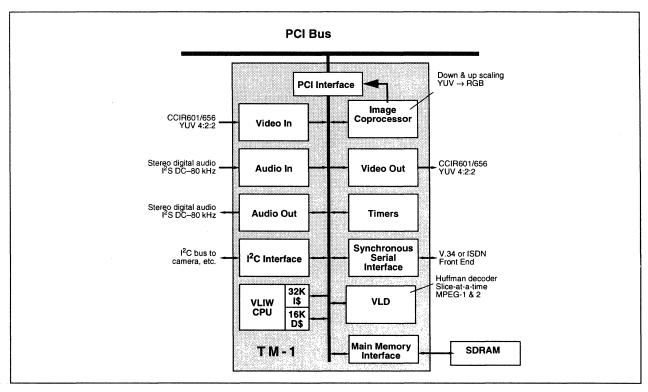

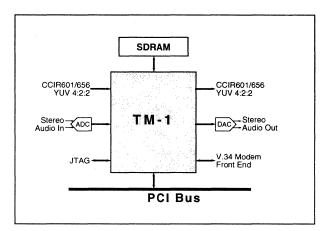

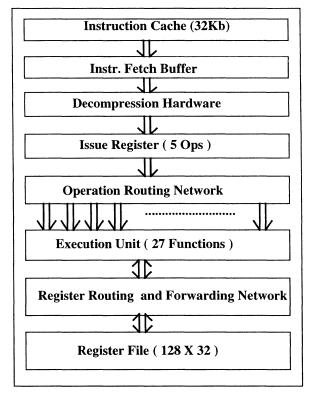

| Frank Schapfel, Digital Equipment Corporation Trimedia—The Processor for PC-Consumer Multimedia  | 275 |  |  |

|                                                                                                  | 275 |  |  |

| Selliah Rathnam and Gert Slavenburg, Philips Semiconductors Multimedia Bandwidth Issues Over PCI | 202 |  |  |

|                                                                                                  | 283 |  |  |

| Giri Venkat, Yamaha Systems Technology, Inc.                                                     |     |  |  |

| Session 3C                                                                                       |     |  |  |

| Board Maker's Roundtable                                                                         | 284 |  |  |

| Steve Cooper, I-Bus                                                                              |     |  |  |

| Session 3D                                                                                       |     |  |  |

| Bus-to-Bus Connections                                                                           | 285 |  |  |

| Stephan Ohr, Computer Design                                                                     |     |  |  |

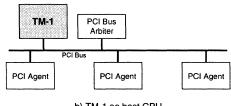

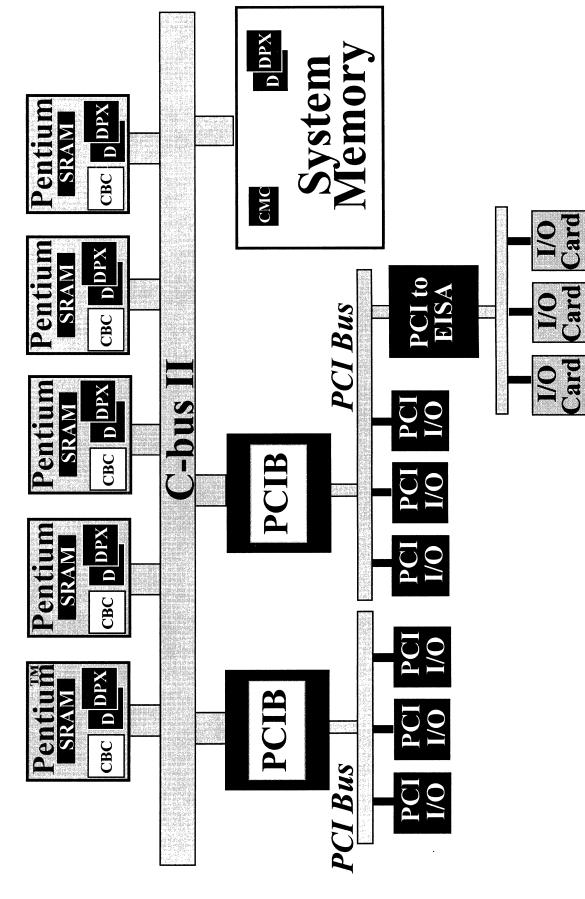

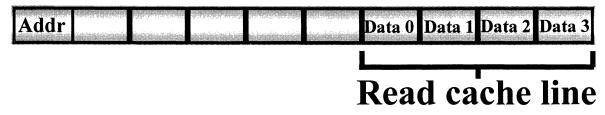

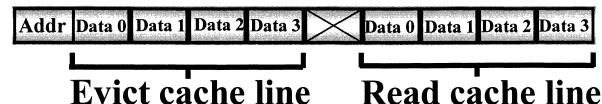

| PCI and Multiprocessing                                                                          | 286 |  |  |

| George P. White, Corollary, Inc.                                                                 |     |  |  |

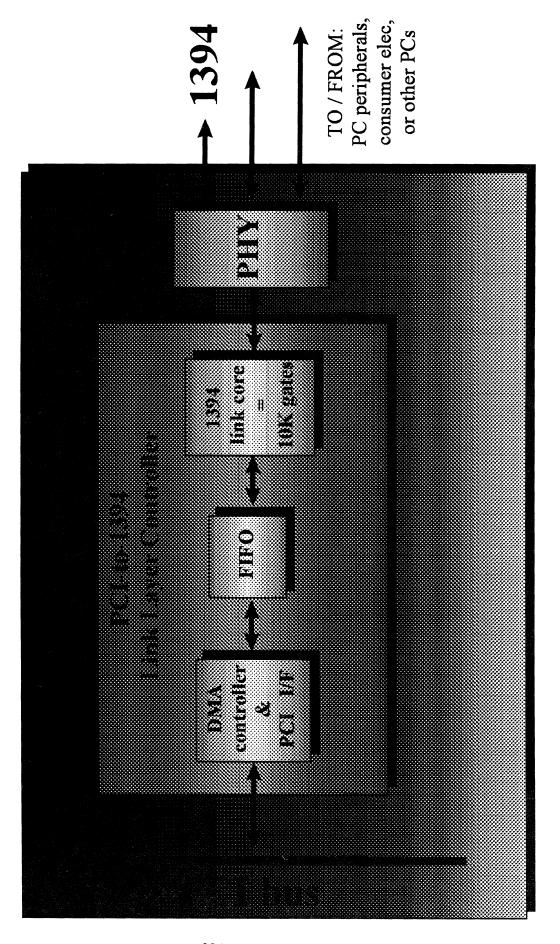

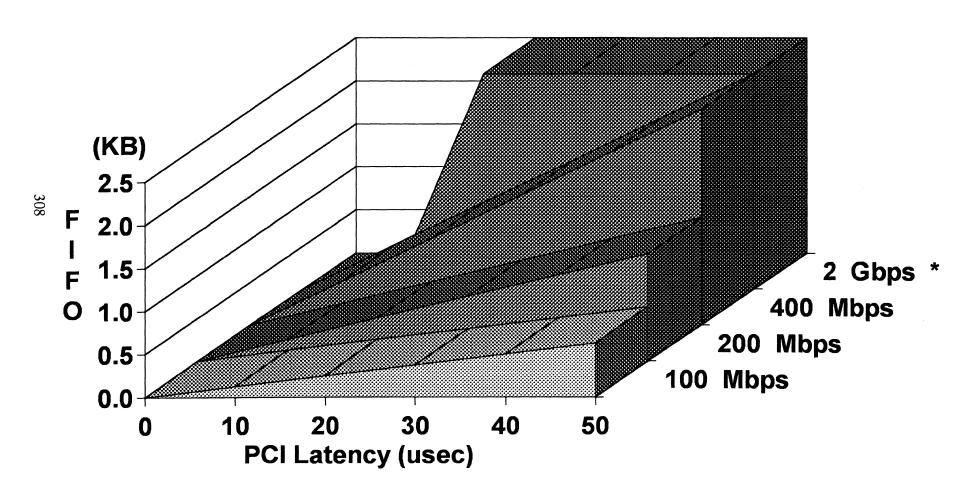

| 1394 and PCI                                                                                     | 302 |  |  |

| Larry Blackledge, Texas Instruments                                                              |     |  |  |

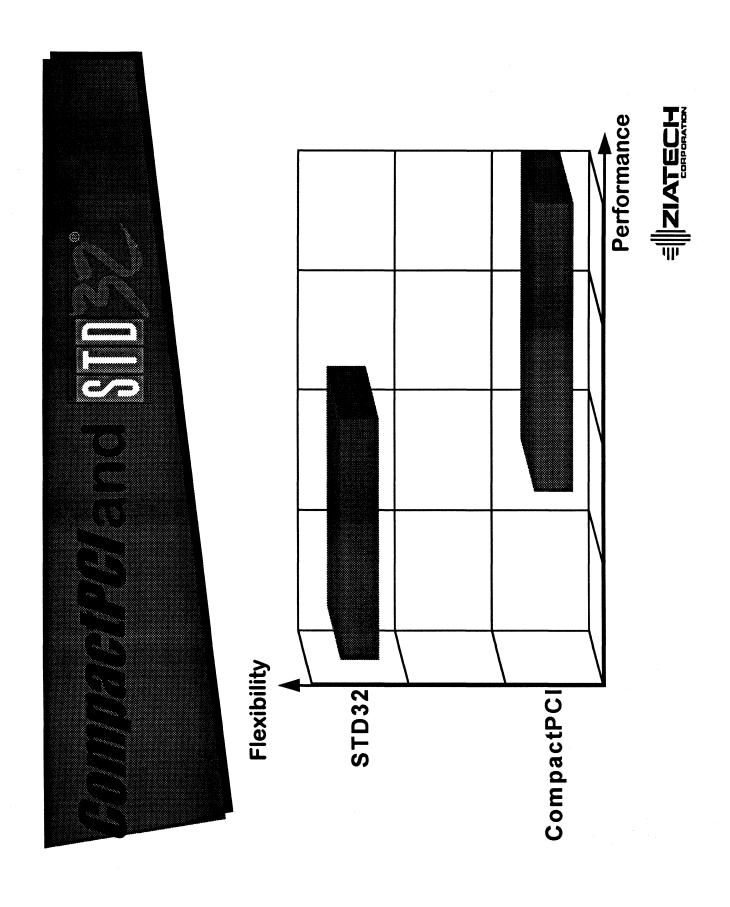

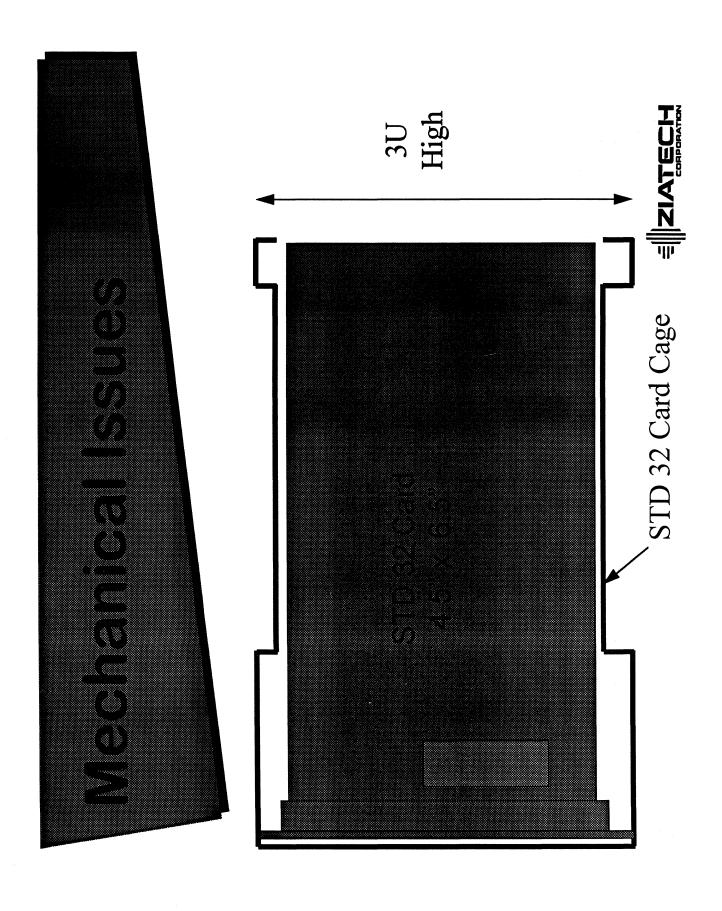

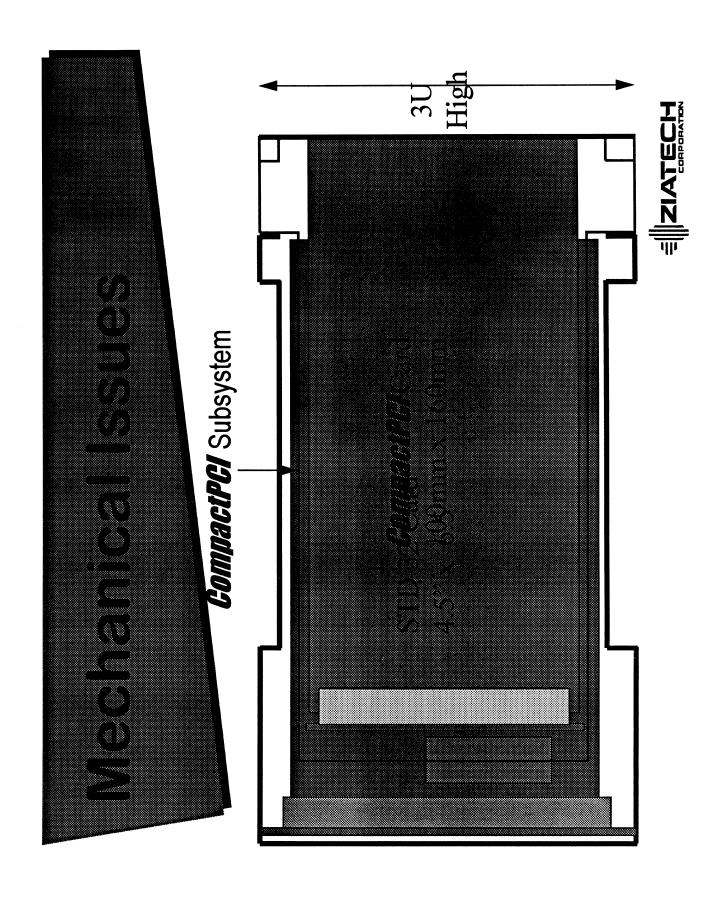

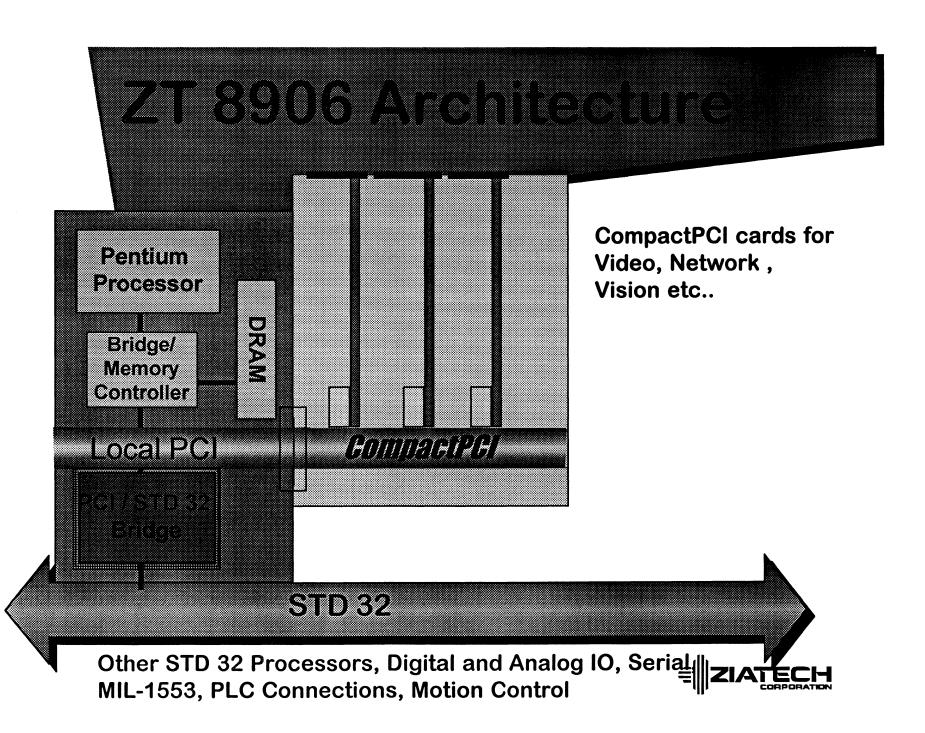

| CompactPCI™ to STD32                                                                             | 312 |  |  |

| Jim Medeiros, Ziatech Corporation                                                                |     |  |  |

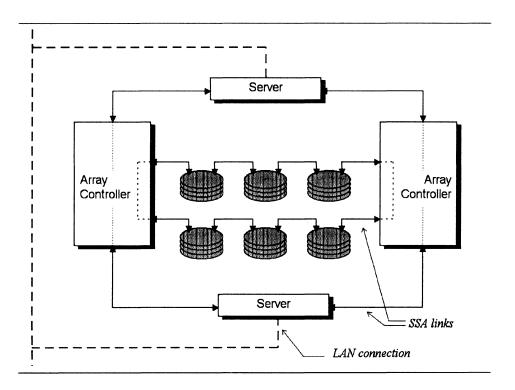

| Serial Storage Architecture: A Low-Cost, High-Speed Serial Connection                            |     |  |  |

| for Disk Subsystems                                                                              | 328 |  |  |

| Adge Hawes, IBM Havant                                                                           |     |  |  |

| Session 4A                                                                                                 |     |

|------------------------------------------------------------------------------------------------------------|-----|

| Using a Design Foundation for Flexible and Rapid PCI Interface Development Leo K. Wong, Altera Corporation | 334 |

| A New FPGA Family for PCI Interface Designs                                                                | 343 |

| Brian Small, QuickLogic Corporation                                                                        | 010 |

| PCI Implementation Kits for ORCA FPGAs: Features and                                                       |     |

| Design Considerations                                                                                      | 347 |

| James F. Hoff, Lucent Technologies                                                                         | 547 |

| ,,                                                                                                         |     |

| Session 4B                                                                                                 |     |

| MPEG Bridges Using T1 Lines                                                                                | 353 |

| Tom Thorsteinson, Linear Systems Ltd.                                                                      |     |

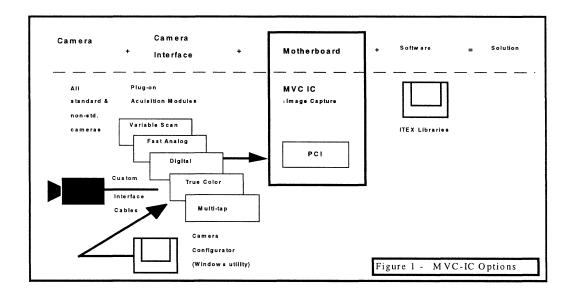

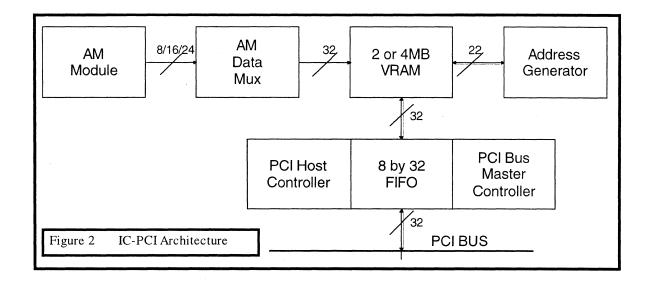

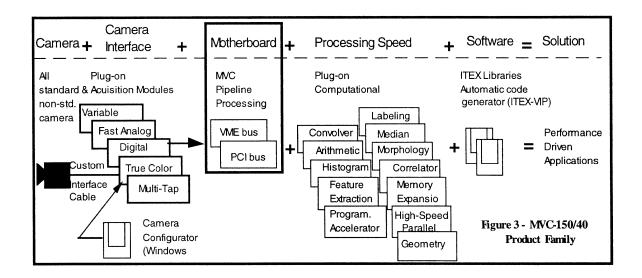

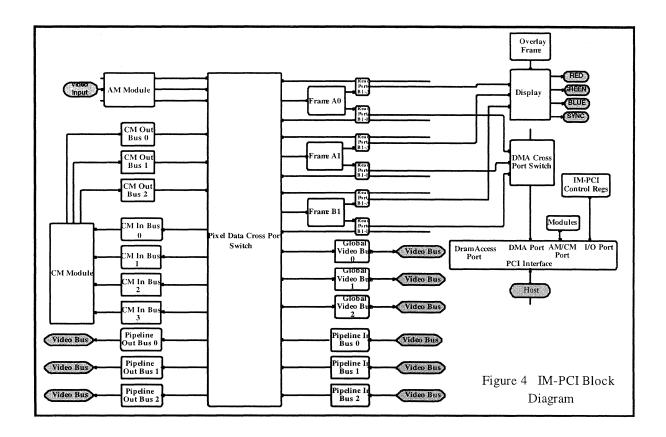

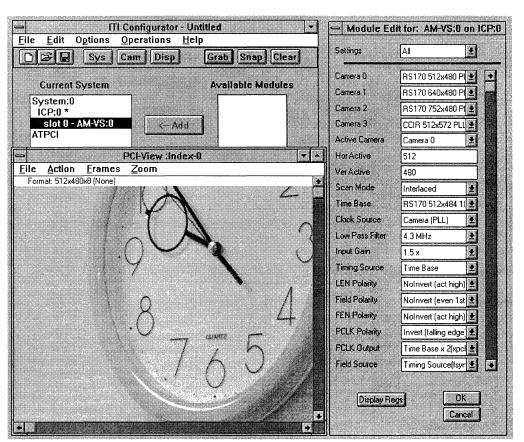

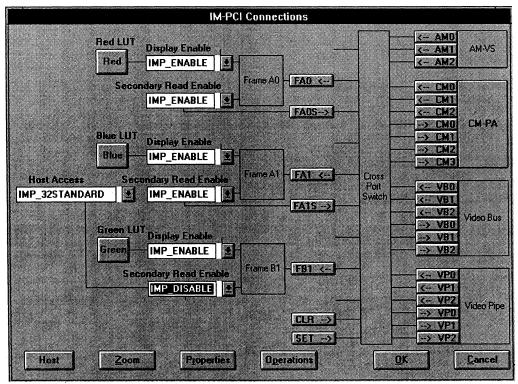

| High Performance Vision Processing for the PCI Bus                                                         | 358 |

| Fernando Serra, Imaging Technology, Inc.                                                                   | -   |

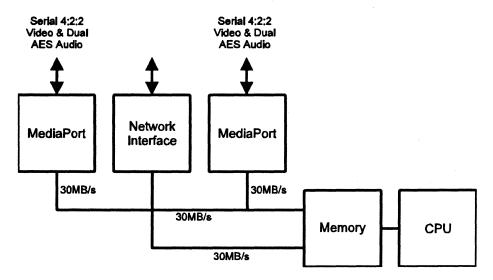

| The PCI Bus and Broadcast Quality Video and Audio                                                          | 366 |

| Richard A. Kupnicki, Leitch Technology                                                                     |     |

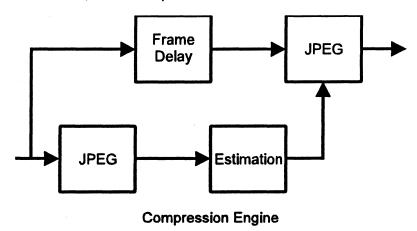

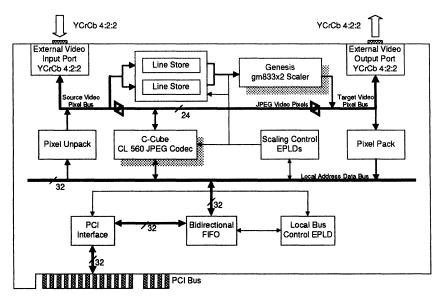

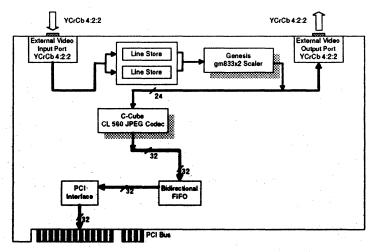

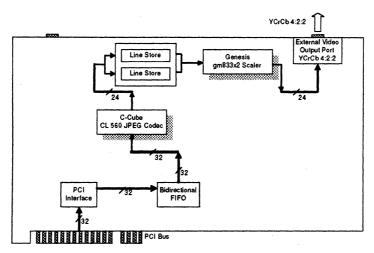

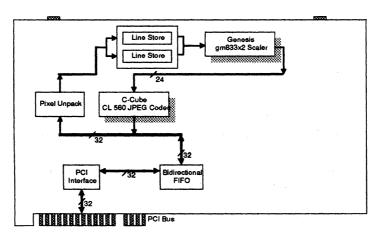

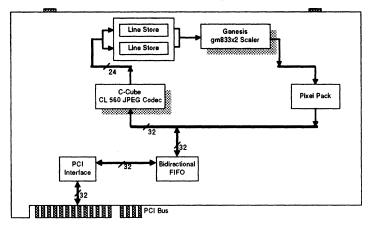

| Board Improves JPEG Compression Using Pre- and Post-Compression                                            |     |

| Image Scaling                                                                                              | 381 |

| Harold Schiefer, Ernest Yeung, Steven Hanna, and Lance Greggain,                                           |     |

| Genesis Microchip Inc.                                                                                     |     |

| Session 4D                                                                                                 |     |

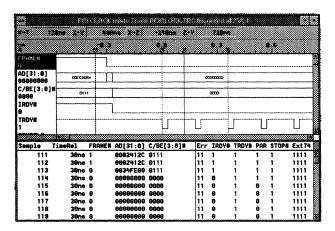

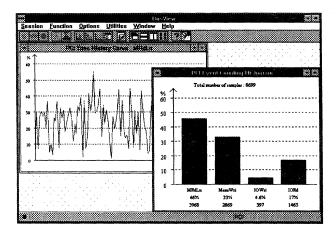

| PCI Bus Analyzer Simplifies Systems Test & Debugging                                                       | 390 |

| Thomas Nygaard, VMETRO, Inc.                                                                               | 570 |

| PCI: The Bus That Glues?                                                                                   | 394 |

|                                                                                                            | 374 |

| Mark Bronson, Aeon Systems, Inc.                                                                           | 200 |

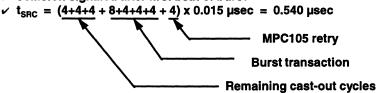

| Latency Issues in PowerPC Reference Platform Architectures                                                 | 399 |

| Don Dingee, Motorola Computer Group                                                                        | 400 |

| PCI Passive Backplane Technologies                                                                         | 409 |

| Joe Pavlat, Pro-Log Corporation                                                                            | 440 |

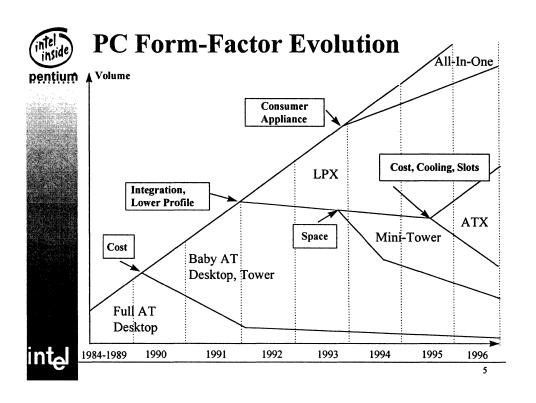

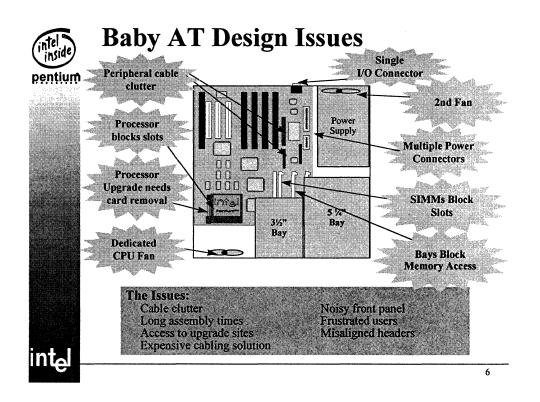

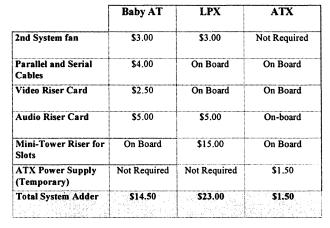

| PCI Shifts in the PC Landscape                                                                             | 440 |

| Yong Yao, MicroDesign Resources                                                                            |     |

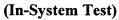

| The ATX Form-Factor                                                                                        | 443 |

| Tim Craven, Intel                                                                                          |     |

| Session 5A                                                                                                 |     |

| BIOS Boot Selection                                                                                        | 452 |

| Frances Cohen, Phoenix Technologies Ltd.                                                                   |     |

| Notebook Docking: Techniques and Considerations                                                            | 454 |

| Jim Kelsey, SystemSoft Corporation                                                                         |     |

| Session 5C                                                                                                 |     |

|                                                                                                            | 460 |

| Multimedia Roundtable                                                                                      | 462 |

| Bridging the PCI to a Secondary Multimedia Bus:                                                            | 460 |

| Can We Plug and Play?                                                                                      | 463 |

| Larry Chisvin, S3 Incorporated                                                                             |     |

| Session 5D                                                                                                 |     |

| CAD Tools                                                                                                  | 464 |

| Iim Lipman, EDN                                                                                            |     |

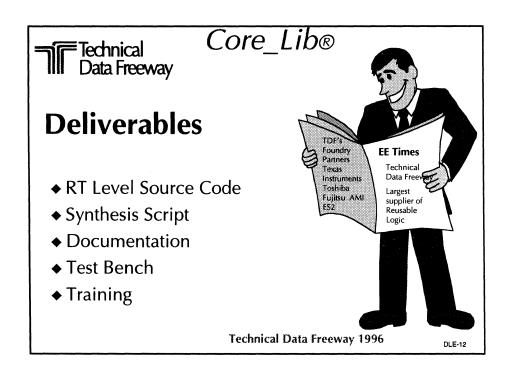

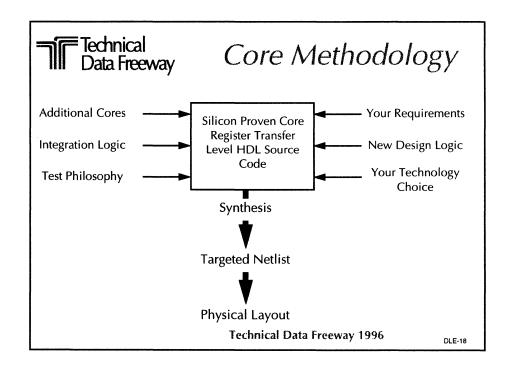

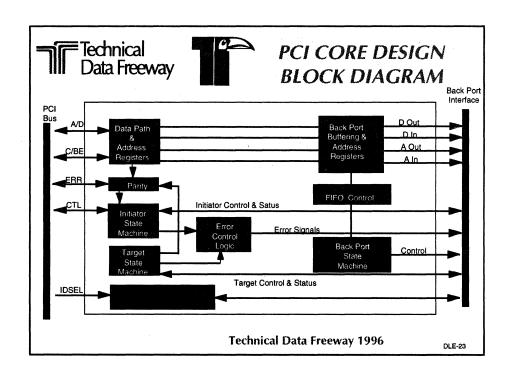

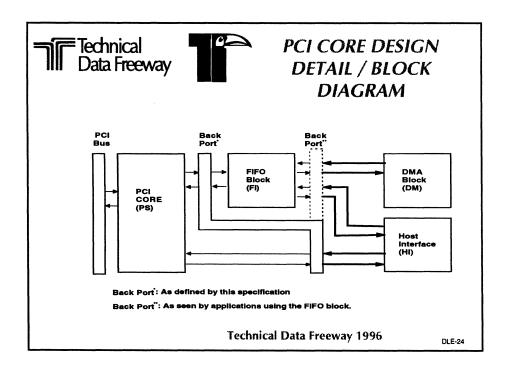

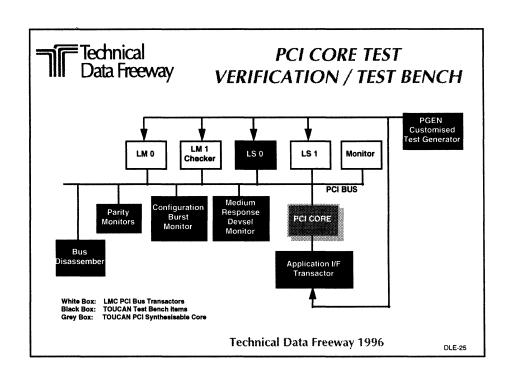

| Getting Quality Products to Market Faster with a Synthesizable PCI Core | 465 |

|-------------------------------------------------------------------------|-----|

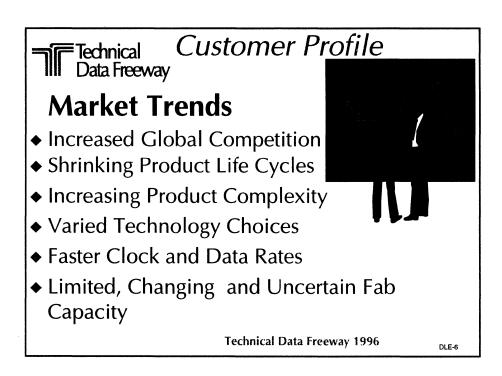

| David L. Evans, Technical Data Freeway                                  |     |

| The Problem of Model Availability for Simulation of Devices and Systems | 479 |

| Dave Apte, Omniview, Inc.                                               |     |

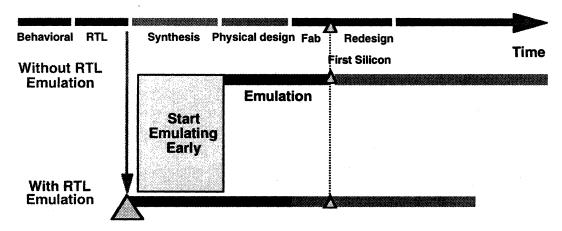

| Verifying PCI Bus System at Megahertz Speed                             | 485 |

| Sanjay Sawant, Quickturn Design Systems                                 |     |

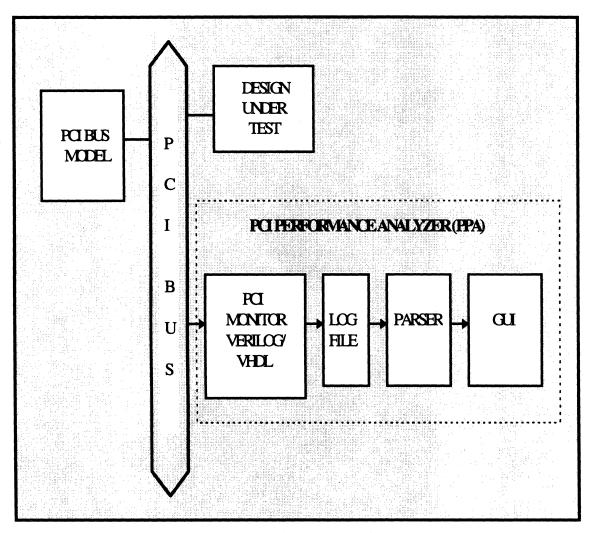

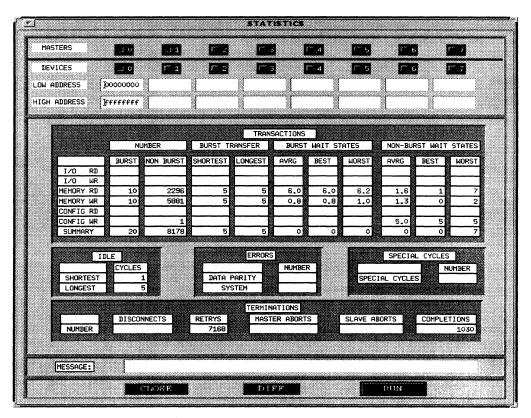

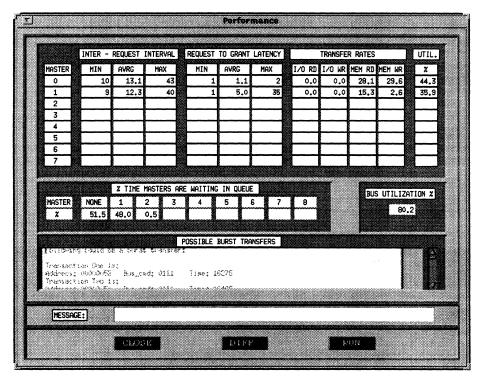

| Measuring and Optimizing Performance of PCI Based Designs               | 488 |

| Venkatesh Arunarthi, Sand Microelectronics, Inc.                        |     |

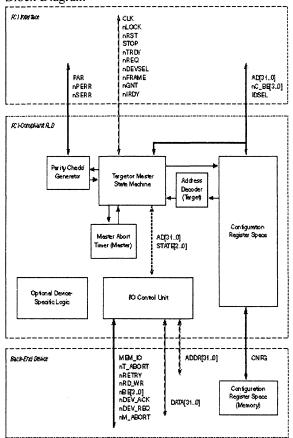

| A VHDL Design Approach to a Master/Target PCI Interface                 | 494 |

| Leo K. Wong and Martin Won, Altera Corporation;                         |     |

| Subbu Ganesan, ZeitNet, Inc.                                            |     |

| Late Papers                                                             |     |

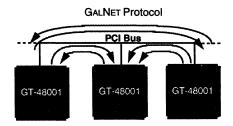

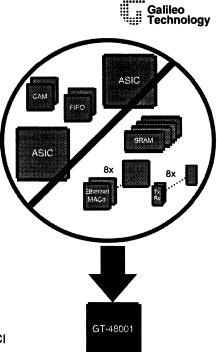

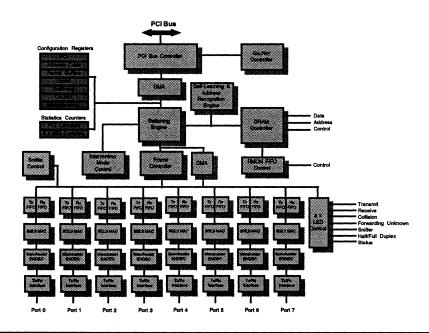

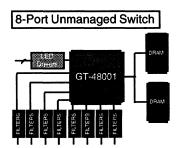

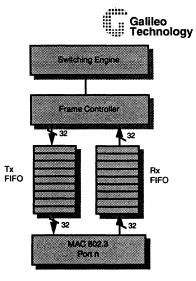

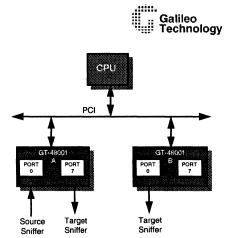

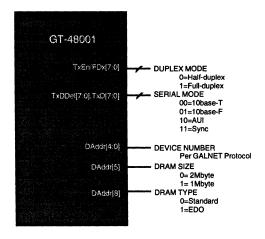

| The GALNET Architecture: A PCI-Based Solution for High Performance      |     |

| Internetworking                                                         | 500 |

| Manuel Alba, Galileo Technology                                         |     |

| Using FPGAs for High-Performance PCI                                    | 520 |

| James D. Joseph, Actel Corporation                                      |     |

| Author Index                                                            | 525 |

| Keyword Index                                                           | 527 |

| Participant Index                                                       | 529 |

#### **Preface to PCI Spring 96 Proceedings**

Prior to the development of PCI engineers developing products for the non-PC (Personal Computer) industry could only select between high performance proprietary buses or standard buses like VME and Multibus I&II. PC buses like ISA and EISA were simply insufficient for the non-PC industry. Proprietary buses by definition required development of all key hardware and software components. Components for VME buses were not always compatible. Multibus I components were compatible, but became overshadowed by Multibus II which required extensive software development.

The size of the PC industry insured a diverse set of low cost components and an unparalleled selection of software. However, the lack of easy configuration and low performance of ISA bus; and the complexity, limitations, and cost of EISA bus did not provide a long term bus to replace proprietary or other standard buses.

The existence of extensive PC compatible software, appreciation for easy system configuration, and the ever increasing ASIC functionally set the stage for a new bus standard. PCI began as a bus definition to provide an easy to configure, low cost, and high performance interconnection between PC software compatible ASICs. As it was fine turned into a PC industry standard it was expanded to include definitions for slots and add-in cards. As PCI became integral to mainstream PCs the PCI hardware costs decreased and the functional diversity of PCI ASICs and add-in cards increased. What evolved was a new bus standard that brought together performance, building block diversity, low cost, easy configuration, and compatibility with "limitless" PC compatible software.

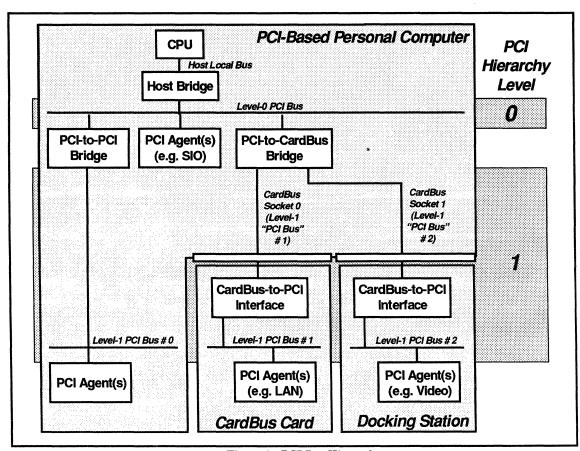

In the mobile environment the traditional PCMCIA standard (recently renamed PC-Card 16) is essentially an extension of low performance ISA bus with configuration enhancements and power-on installation. The recent enhancement of this standard with CardBus, brings all of the advantages of PCI to PCMCIA. CardBus is a small form factor version of PCI with the power-on installation.

Most recently, the embedded systems world has also discovered the cost and software advantages, and building block diversity of PCI.

It has become impossible for proprietary buses and standard buses like VME or Multibus I&II to compete with PCI due to the size of dynamics of the PC industry. The ever growing availability of PCI cards and slots will eventually replace all of the ISA and EISA cards and slots. Similarly, the eventual availability of combination PC-Card 16 / CardBus slots in the mobile and desktop environments will facilitate the eventual extinction of PC-Card 16. Consequently, these proceedings contain information about PCI and CardBus which are the future bus standards with the unique ability to address both the PC and non-PC industries.

Ed Solari PC<sup>2</sup> Consulting LLC

#### **Docking for Mobile Computing**

Harish Nayak, Cirrus Logic, Inc. Systems Technology Products (STP)

The gap in speed, capacity and functionality that has separated desktop systems from portable computers has rapidly narrowed. Today, more and more mobile computer users are relying on their portable systems to serve their needs while on the road and at the office. In this way, they avoid the problems of file transfers and version tracking that annoy their dual-computer-using colleagues.

On the road, one can get by with the small display screens, but in the office, users want larger screens, and to be able to attach networks, laser printers, scanners and other peripherals to their portable systems.

At first, they did so using ad-hoc solutions—display screen cables connected to monitor ports, network cables to network ports, and port replicators, where the computer's I/O ports are replicated and consolidated into a single port-replication box. Having to unplug several cables each time one left on a business trip, then reconnect them each time one returned, proved to be discouraging. It also created an opportunity to solve the problem with "docking."

In essence, a docking set up consists of the portable system plus a docking station to which are attached whatever peripherals the user requires. Docking's primary feature is its ability to quickly connect or disconnect the portable system from the docking station and its peripherals. But docking is far more than simply a mechanism for rapidly plugging or unplugging multiple interfaces. It must also ensure that in the process users cannot inadvertently lose or damage any data files. As such, docking approaches are both related to, and limited by, the operating system's features and functions, and the I/O buses involved.

Docking is an evolving technology. With the advances of new I/O bus technologies and operating systems, docking is also advancing toward a fully automatic, any time, capability.

#### **Docking Stations Today**

There are a range of docking solutions in place, today. They differ in terms of their physical docking attributes, and their electrical docking requirements.

#### **Physical**

A surprise-style docking/ejection mechanism is one of the simplest but requires that the user make sure the system is "ready" for docking or undocking. There is no fail-safe mechanism, here, that permits either the operating system or basic I/O system (BIOS) to override the operation. Hence, there is a risk of losing files.

The VCR-style and locking-style docking/ejection mechanisms provide a fail-safe system for docking or undocking. For undocking, an eject button or icon is pressed or selected which initiates a series of interactions between the BIOS and various hardware and software components. The result of these interactions is putting the computer into a safe undocking state. Only after the undocking is approved by all involved is the portable computer actually ejected.

#### Electrical

In addition to the various physical manifestations of docking, there are differences in docking electrical conditions.

"Cold" docking, for example, refers to a docking scheme whereby both the computer and docking station must both be powered down before docking or undocking can take place. Afterward, the computer and docking station are powered up, and the computer must go through a boot up sequence.

A so-called "warm" docking technique permits the systems to be powered up when docking, but requires that the computer be in a suspended operational state before docking or undocking. After docking or undocking, the computer must still go through a wake-up process to restore it to an operation-ready state, or it may require a full reboot, depending upon the operating system.

In moving toward the ideal—a fully automatic, any time, docking capability—docking technology must first progress to the "hot" docking stage. Here, the computer and docking station are both powered up, and the computer is operational. The industry is on the brink of hot docking but there will be varying degrees of less-than-fully-automatic operation for a while.

#### **Operating Systems and Docking**

There are definite relationships between operating systems and docking capabilities. For example, portable computers running DOS and Windows 3.1 are limited to cold and warm docking. These operating systems simply lack the functional support needed for hot docking.

Windows 95, however, has provided a foundation for all three types of docking, including hot docking. Its penchant for hot docking is primarily due to its dynamic loadable drivers, device enumeration, and operating system-to-BIOS links for automatically adding and removing resources.

#### System Buses and Docking

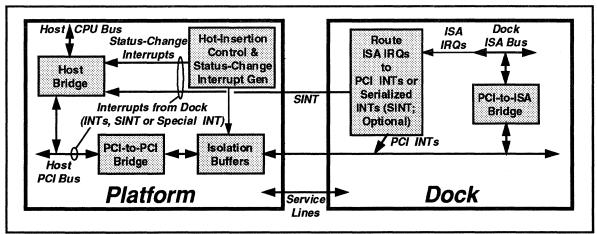

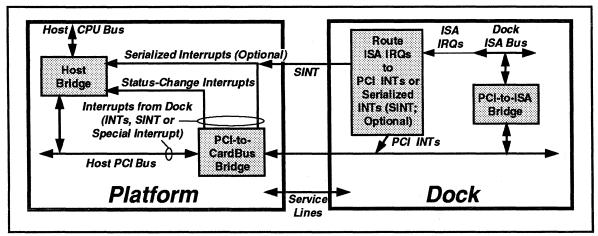

Designers have some choices. They can "dock" across an ISA-bus infrastructure, or do it across a PCI-bus infrastructure. There are obvious advantages to choosing PCI. It is broadband and fast with very short latency. ISA, on the other hand, is a 1980s technology, lacking in both bandwidth and speed.

However, ISA does enjoy an important advantage. It is the I/O standard for a large number of available and economical peripherals. That's why, for now, portable computers are being built with both ISA and PCI, and it's a good reason to equip a docking station with a secondary ISA interface, too.

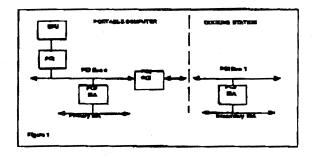

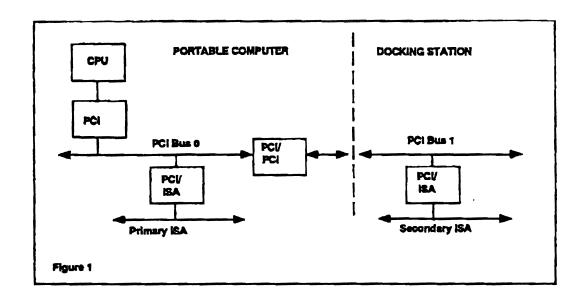

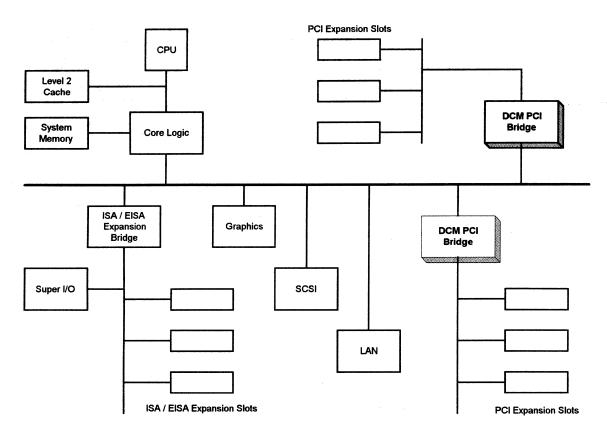

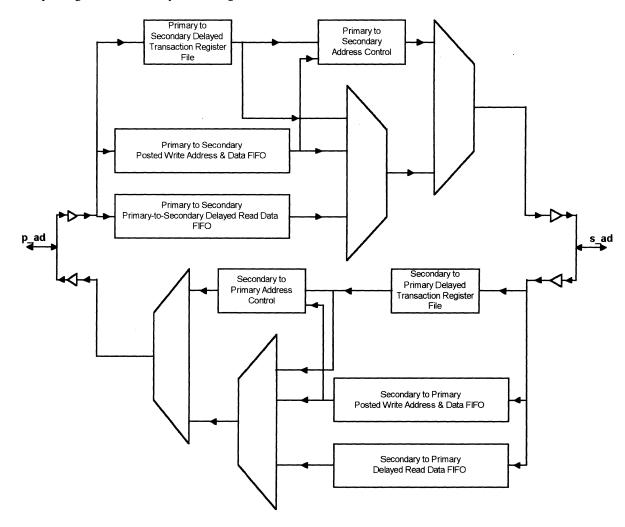

When an ISA bus is present both in the computer and the PCI-based docking station, it is referred to as a "dual ISA" design. Both systems—portable computer and docking station—will take advantage of PCI-to-ISA bridging to connect ISA peripherals on both sides of the docking demarcation line via a PCI bus interface (see figure 1).

In effect, the computer's ISA bus (primary) is connected to the docking station's ISA bus (secondary) through the PCI bus.

With the approach shown in figure 1, though, a DMA controller (DMAC) and Programmable Interrupt Controller (PIC) are implemented on both sides of the docking line, and they use the same I/O address space. That poses a problem.

There are two other concerns that must be addressed in implementing a dual ISA design, too. The "legacy" peripherals that use the ISA bus comply with ISA's Interrupt Request (IRQ) specifications. And these peripherals are also designed, in most cases, to use ISA Direct Memory Access (DMA). However, neither ISA, IRQ nor ISA DMA is part of the PCI standard.

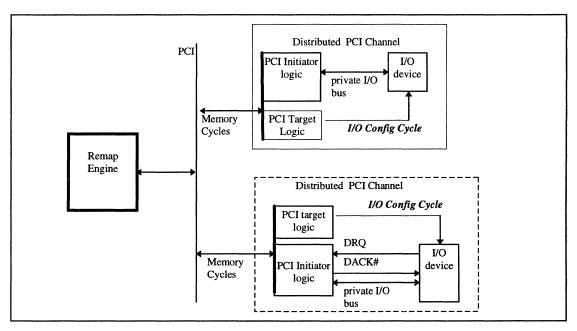

There are two open-standard mechanisms that can solve this dilemma. Serialized IRQ, or IRQSER, is a mechanism for communicating IRQ status between PCI-to-ISA bridges, and between legacy components and PCI-to-ISA bridges. Distributed DMA, or DDMA, is a mechanism for legacy DMA support on a PCI bus.

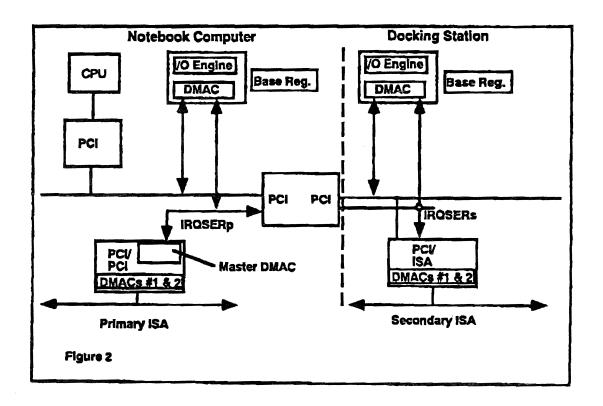

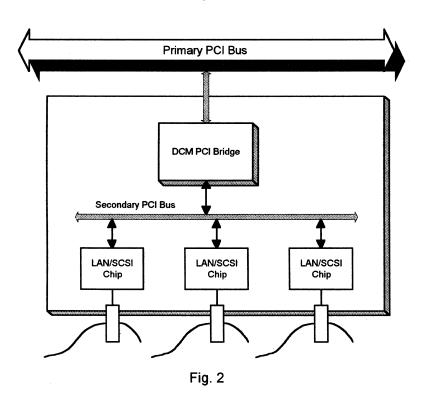

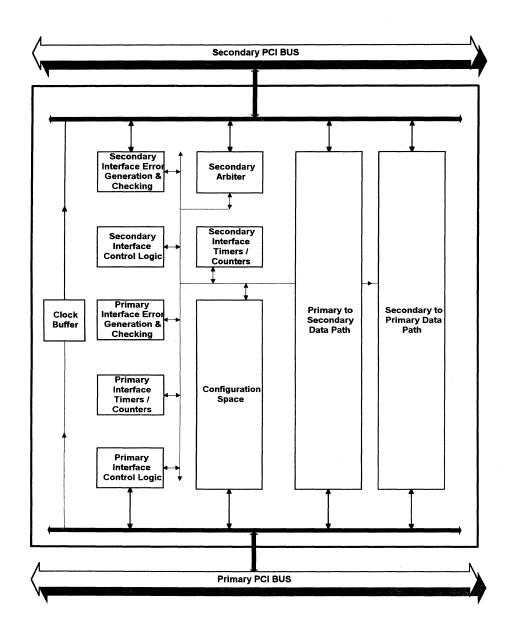

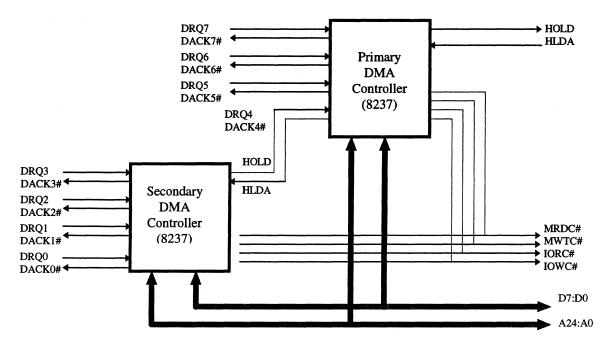

The implementation in figure 2 solves both the ISA IRQ and DMA legacy support across the PCI bus through IRQSERp and IRQSERs and the DDMA mechanism.

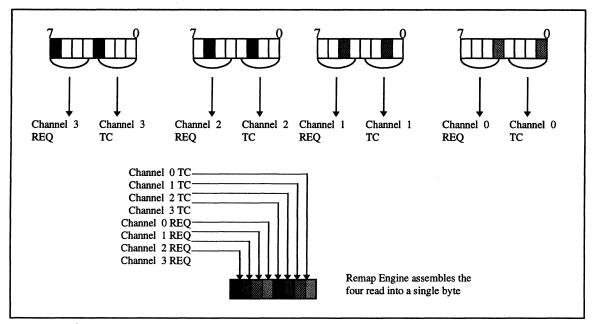

Here, only the PCI/ISA bridge in the computer has a master DMA controller, and all others are slaves, each having a base register and DRQ/IRQ definition.

All slave devices positively decode their DMA I/O registers. The PCI-to-PCI bridge and secondary PCI-to-ISA bridges subtractively decode the unclaimed DMA I/O registers.

Multichannel- or channel-specific "write" (e.g., not on the primary ISA bus) is broadcast by the master DMAC. Multichannel- or channel-specific "read" is also broadcast by the master DMAC. Where it is a multichannel read, the master DMAC will properly assemble the bit information, then it will return the 8-bit word during the retry cycle.

Instead of edge-triggered IRQ signals, creating a risk of glitches during docking, or a need for Q-switch isolation, the serialized IRQs are passed from PCI-to-ISA bridge via the PCI-to-PCI bridge. With this implementation, the PCICLK is stopped during docking and undocking and the IRQSER signal is ignored during those times (patent pending).

### Issues and Limitations in Docking Today

To reiterate, there have been step-wise enhancements to docking technologies as direct consequences of step-wise improvements in operating systems and I/O bus infrastructures. For example, PCI allows us a simple docking interface with high performance.

The availability and low cost of ISA-compatible peripherals, and the reality that, for now, Sound Blaster compatibility requires the ISA interface, necessitates designing the support for ISA and legacy peripherals in any serious docking solution.

Today's operating systems, particularly Windows 95, have set the stage for hot docking by creating a foundation for it. Many of the plug-and-play supporting features of Windows 95 play significant roles in hot docking (e.g., device enumeration). However, a foundation is meant to be built upon, and the next generation of the Windows '95 family promises to offer an even-more-comprehensive set of features in support of hot docking among other functions.

Power management is a critical feature in battery-powered portable systems. As such, power management support must be part of any full-featured docking solution.

### Solving Some Problems Addressing Design, Architecture, and Application Solutions

Given the ultimate, fully-automatic, any-time docking objective, we are now far down the road, but not quite at our destination.

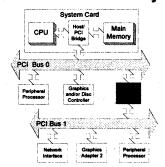

As mentioned earlier, Windows '95 has set the stage for a step-wise leap in docking progress. It supports a dynamic loading of drivers, device enumeration, and plug-and-play. But Windows '95 will only enumerate the devices connected to PCI bus 0, not those connected to bus 1. For that to occur, the docking station would need a plug-and-play BIOS to enumerate its devices and interact with Windows '95 in order to load the drivers dynamically.

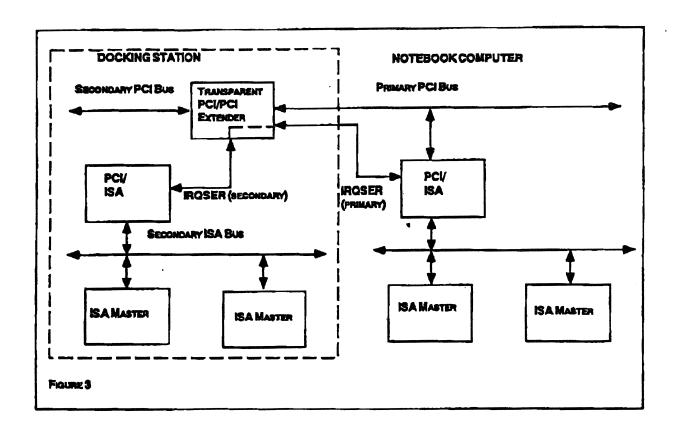

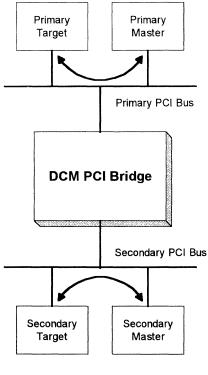

The next generation of Windows '95 will take care of the Bus 1 enumeration situation, but in the meantime, a transparent bus extender (patent pending) can be used to make two physical PCI buses look like a single, logical bus 0. There is no bus 0-to-bus 1 configuration cycle conversion, and no PCI configuration space involved (see figure 3).

#### On-Board or Off-Board?

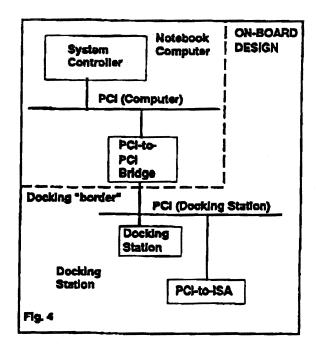

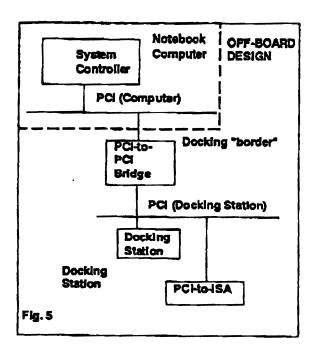

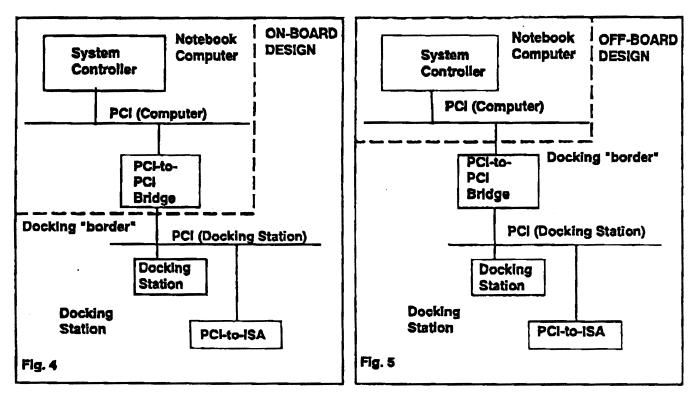

Hot docking hardware implementations can be done in two fundamental ways—putting the PCI-to-PCI bridge on the computer, or putting it onto the docking station. There are some advantages to taking the off-board approach.

By adding the bridge to the computer, a designer has to allow more space, increase the cost, as well as the power consumption. In addition, the on-board approach may require Q-switches to isolate the IRQ signals during docking and undocking (unless a IRQSER approach is used). This, too, adds cost. For those users who do not intend to dock their systems, it is unutilized cost (see figure 4).

By putting the PCI-to-PCI bridge on the docking station (e.g., off-board), docking and undocking glitches can be isolated from on-board PCI devices without need of Q-switches (see figure 5). What's more, there is no pressure on computer board space, weight, power consumption, or cost.

#### Ensuring network compliance

Since many docked computers will be part of some networking scheme, there is a need to ensure that the docked system can be compliant with network requirements.

For example, a computer in sleep mode must be able to rouse to full operation within a certain time (e.g., 100 milliseconds) to meet network polling requirements. This is a significant challenge to be met by forthcoming docking implementation approaches.

#### Easy docking with Windows '95

In sum, the advent of the next generation of Windows '95 and the proliferation of PCI peripherals will take us a long way toward the ideal docking infrastructure. Meanwhile, the current version of Windows '95 has already propelled us very far forward.

Despite some of its evolutionary limitations, Windows '95 is a good basis not only for hot docking, but for a hot docking scheme that is reasonably automatic.

Windows '95 is capable of supporting cold, warm and hot docking techniques, and matched by hardware that is equally capable of supporting all three modes, docking station and notebook designers will have the design flexibility and versatility they require.

#### The New Digital Media

Tony Sheberman

Intel Technical Marketing Engineer

Intel Corporation FM3-77

1900 Prairie City Road

Folsom, CA 95661

(916)356-7399/2703 (fax)

The Presentation will cover the similarities and differences of the Miniature Card to the PC Card and some typical applications for Miniature Card. The Miniature Card (Minicard) is about one fourth the size of a PCMCIA card. Typical uses include the storage and exchange of image, text, and voice data for digital cameras, audio recorders, cellular phones, handheld computers (PDAs), and other portable consumer devices. The Minicard is also the smallest standard form factor for removable memory-expansion cards. It can accommodate up to 64 MB of flash, DRAM, or ROM. The card features a 60-connection memory-only bus interface, with a 16-bit-wide, non-multiplexed data bus. Since the Minicard interface is a subset of the PC Card standard, data can be moved easily into the PC using a PC card adapter.

#### How to implement a CardBus solution

Gary Gildersleeve Cirrus Logic, Inc 3100 West Warren Ave. Fremont, CA 95438 (510) 252- 6095/6080 (fax)

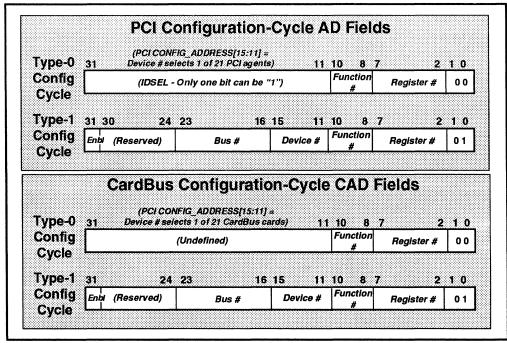

This article describes how to implement a CardBus bridge host controller solution and some of the design choices the architect faces. Several terms are used in this article which need a basic definition. For example, CardBus bridge controller refers to a PCI to PC Card bridge host controller. PC Card 16 refers to the revision 2.1 compatible PC Cards or R2 Cards which have an ISA type 16 bit data path. PC Card 32 refers to CardBus Cards that have a PCI type interface with a 32 bit data path.

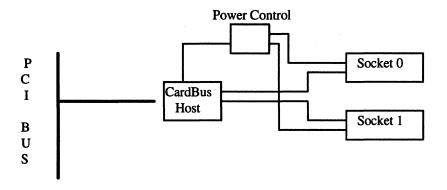

In a basic CardBus subsystem, there are three independent interfaces, which are stated below:

- 1) Host bus bridge interface ( PCI ).

- 2) Socket interface

- 3) Socket Power control interface

For most CardBus designs, the host bridge interface signals are directly connected to the corresponding PCI bus signals. These signals are the multiplexed address/data, control and arbitration signals and interrupts. Most of the PCI bus signals are direct connections to the CardBus bridge host controller. Therefore, this article will focus on other areas of the CardBus design. There will be some discussion brought up in regard to specific signals in the component and layout section. Main areas of discussion will be the Interrupts, Power control and the optional feature of Zoomed Video (ZV). The last topic discussed is the testing and verification of the CardBus design. This article is not intended to sway the reader in anyway upon how to design their notebook system, but rather to help conger up ideas and possible problems that may occur in a CardBus design.

#### Component and layout issues

Component placement is another design issue that should be considered in a CardBus host controller implementation. Remembering that CardBus is similar in many aspects to the PCI bus. The timing on the control signals are critical and have stringent requirements (11 ns max.). The CardBus host controller chip should be placed as closely as possible to the PC Card Connector. It is recommended that the trace length from the host bridge control to the PC Card socket does not exceed 5". Loading condition of these lines should also not exceed the loading specified in the PC Card specification. The CardBus

clock signal (CCLK/A16) should be give special attention since this is the 33 Mhz clock supplied to the PC Card socket from the CardBus host controller. To ensure a clean clock signal to the CardBus socket, a double wide trace should be used and additional guard-banding with a ground maybe preferable. To prevent Cross Talk on neighboring signals extra spacing can be added between the CCLK signal and other board signals. In the routing of the board good layout practice should be used by avoiding sharp 90 degree corners. Always use 45 degree corners instead. Since there is a lot of simultaneous switching of signals at the PCI and CardBus interfaces, adequate bypassing of the power supply is essential. This can be achieved by placing quality capacitors close to the host controller. In a PC Card 16 host controller design, placement and routing were not as critical to ensure host functionality. The PC Card 16 bus was a slow bus with few critical timing requirements. As opposed to that in CardBus host design, component placement and layout considerations are major factors that govern successful operation. Most of the of issues stated involve basic design and board layout principles which need to be taken into account in a CardBus subsystem design.

#### Interrupts

CardBus host adapters typically support both ISA and PCI interrupts. ISA style interrupts are active high interrupts. These interrupts are used by PC Card 16 cards and typically are not shared between devices. Each device that requires an interrupt is assigned its own interrupt signal. PCI interrupts are active low and are designed to be shared in the system. If a CardBus card is installed in the socket which is defined as function 0, it is assigned the interrupt INTA#.

There three different mechanisms in which the ISA interrupts can be generated. These methods are listed below along with a brief description

External Hardware to generate the individual Interrupts PCI/Way interrupts PC/PCI interrupts Individual Interrupt pin from the host

External Hardware method uses two output pins from the host (ISDAT and ISLD) and the PCI system clock. When a card interrupt in generated, the host then sends out the serial interrupt to the external hardware via the ISDAT line. Once the serial data is correctly aligned, the ISLD signal is sent to latch in the data and initiate the ISA interrupt. This is a unidirectional protocol from the host to the external hardware with no acknowledgment.

**PCI/Way** interrupt method only requires one pin (IRQSER) from the host controller and the PCI clock. This bi-directional data stream is use to communicate the state of the interrupt between the host controller and the core logic. When an interrupt is generated by the controller, a start pulse is generated to begin the transaction. Within the start and stop time period, each interrupt is assigned three clocks which are used to show the state of the interrupt and each interrupt has its own time slot within the start and stop period.

**PC/PCI** mode supports the Mobile computing model for serial interrupts. This method requires two pins (SOUT and SIN) and the PCI clock to interface the SIC (serial interrupt controller). The number of interrupts supported is dependent upon the configuration of the SIC. For more information refer to the mobile computing specification.

Individual Interrupts means that CardBus bridge has dedicated pins for each ISA interrupt.

The choice of interrupt method used is dependent upon the host bridge and core logic that will be used in the system design.

#### Voltage Control & Power issues

Earlier host controller designs that only supported PC Card 16 cards could sometimes exclude mixed voltage support to the PC Card socket without being severely penalized due to the limited number of low voltage cards in the marketplace. It is no longer feasible for designers to avoid mixed voltage designs with the trend shifting towards low voltage systems and power saving. Mixed voltage support is no longer an option for the CardBus controllers. The PC Card Standard specifies that the CardBus interface can only operate at 3.3V. PC Card socket power control switches are available from many different manufactures in the marketplace and provide integrated solution for power control. These switches are used to control the Vcc and Vpp voltage levels of the PC Card socket. These switches come in either parallel or serial interface. Most of the CardBus host controllers today use the serial power control switch to free up pins.

Power requirements for the CardBus system is another area the designer needs to be aware of to determine the total system power requirements. Typically, the designer needs to know the worst case power requirements for each subsystem. For the CardBus subsystem this can be easily calculated using the following formulas.

Socket Power = (number sockets) \* (max. voltage of the socket) \* (Amp)

The 1 Amp value is derived from the PC Card Specification that states the maximum rating for pin of the PC Card socket is 500 ma per pin. 2 \* 500 mA = 1 A

Host Power = (Highest Voltage applied to Host) \* (1A)

Using the formulas above, the worst case power requirements for the CardBus host subsystem would be 15 Watt of power dissipation using 5V as the maximum voltage to be used in the system.

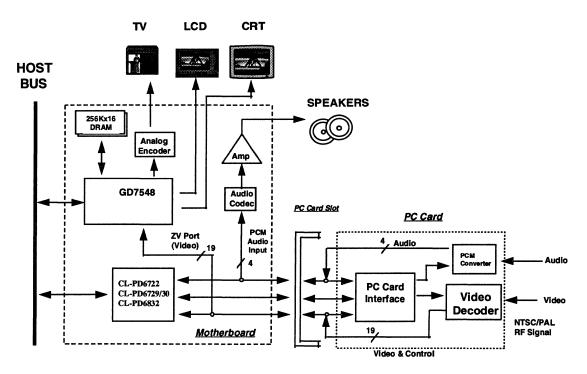

#### ZV (zoomed Video)

The Zoomed Video (ZV) Port is a direct connection between a PC Card and a VGA controller / Audio DAC. It allows the PC Card to write video data directly to an input port of a graphics controller and audio data directly to a digital-to-analog converter.

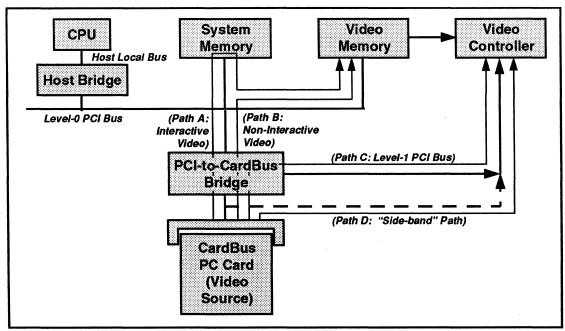

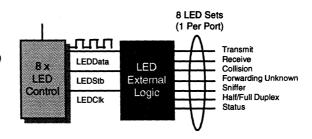

A few of PC Card host adapters are being introduced in to market that are capable of supporting the proposed ZV Port standard. There are two methods of supporting ZV Port capability. The first method is termed pass through in which all the ZV Port signals pass directly through the host controller. The second method is termed "bypass" mode. Bypass mode is where the signals are re-routed from the PC Card bus directly to the video port. The video port of the graphic controller is termed the "V Port". This re-routing is accomplished by tri-stating specific PC Card Bus signals from the PC Card host adapter. Once these signals are tri-stated by the host controller during ZV Port operation, the ZV Port compliant PC Card drives video and audio data on the same signals. Video signals from the PC Card are routed to the ZV Port capable Video controller. Audio signals from the PC Card are routed to the ZV Port compliant audio DAC in the host system. This mechanism allows for an inexpensive means to add video/audio capability to a notebook or desktop system without burdening the host bus. Figure 1 shows block diagram for a typical implementation.

A ZV Port compliant PC Card, when inserted into a PC Card slot, is initialized the same way as a PC Card 16. This is specified in the PC Card standard. The ZV Port PC Card is thereafter recognized as a ZV Port card and is programmed accordingly by Card Services. In this example, the Host controller

enters into ZV Port mode by tri-stating address pins A[25..4] of the PC Card bus when the Multimedia or ZV Port enable bit is set.

The address pins are outputs from the host controller during normal PC Card operation. Tri-stating of the address pins by the adapter, allows the A[25..4] signals to carry video data and video capture timing control signals directly to a video controller and the audio signals to the audio DAC.

It should be noted that ZV Port implementations are likely to vary amongst platforms and that Socket Services software has to be customized to address these variability's. Controlling output enable inputs of the external buffers depends upon specific hardware design and Socket Services has to be aware of these specifics such as the I/O Port addresses.

#### Validation and Test

Once the design is done a very important aspect is validation and testing of the system. In most cases, the CardBus host bridge is typically the last subsystem tested and usually given the minimum time compared to other subsystems like Video controller. The CardBus interface may prove to be an even more difficult interface to validate. One reason is due to the enormous number of PC Cards in the marketplace. How can you test to ensure compatibility with every card? Also many of the PC Card 16 cards come with point enablers that bypass Socket and Card Services that can be a source of a problem. If a certain PC Card fails, how is one to determine the cause? Is the problem the CardBus bridge, the card manufacture, software, etc.. One suggestion during system validation is to start the validation of the CardBus bridge earlier. Plan on carrying out comprehensive tests to verify the bridge interface. Probe and measure the timing generated by the controller, look for timing violation, noise, Vcc and Ground bounce. Any of these problem many cause the system layout to change, and cause the design schedule to slip.

Figure 1

Typical Example of the ZV Port Implementation

### PCI Technology for Industrial Control Application Benefits and Issues

### Clyde Thomas Allen-Bradley Company, Inc., Rockwell Automation

Historically, the large industrial automation vendors have used proprietary bus technologies in their control solutions. A number of market and technology drivers has created interest in using standard and commercially available technologies such as PCI. This paper presents how one major control vendor, Allen-Bradley (A-B), has adopted PCI to help introduce a new line of PC-based controllers using existing A-B form factors and I/O products. The presentation will discuss the benefits of using existing PCI standards and technologies, and how the use of PCI allowed for shorter development time as well as access to additional technologies to broaden the application capability of A-B's industrial control solutions. In addition, several issues of adopting PCI technology from the commercial PC-based form factors as well as the emerging CompactPCI definitions will be addressed.

- I. Introduction to Industrial Automation Control Systems and Traditional Approaches

- II. Drivers for Change in the Industry Automation Market

- III. The Role of PCI and Its Suitability for Industrial Control

- IV. Benefits of Using PCI

- V. Unique Design Constraints

- VI. Issues Associated with Industrial Application

- VII. Close—A Trend Not a Fad

## **Using the PCI Bus for Packet Switching Applications**

Raymond Kolment, PCI Group Leader Teknor Industrial Computers Inc

#### ■ Abstract:

Present packet switching applications are normally based on the use of custom designs. The use of off the shelf PC products is generally out of the question. This paper proposes a method of designing a medium rate communication switch, using standard industrial quality products. The use and application of the PCI bus and available industrial PC products is demonstrated.

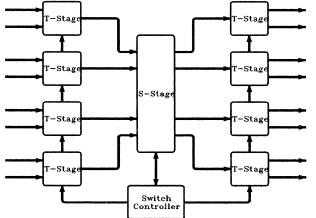

#### ■ Background:

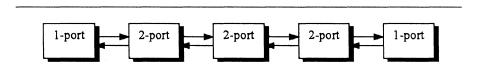

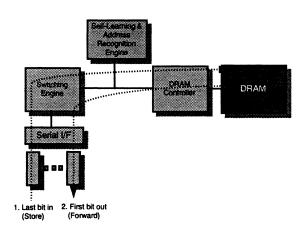

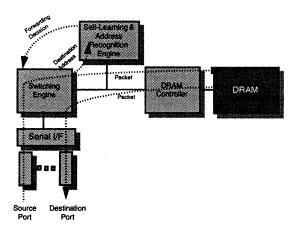

The basic architecture for most digital data communication circuits is the *T-S-T*, or Time-Space-Time data switch. This switching architecture allows messages to be handled in both the time and space domain. Most circuit switching systems and all packet switching systems use one form or another of the basic *T-S-T* architecture.

T-Stage: A time switch has a finite amount of memory to store

incoming data packets. These data packets are subsequently routed to their intended destinations. The *T-stage* will delay the data, if necessary, to assure that there are no clashes between concurrent data packets. A packet that cannot be immediately routed will be delayed a short time before being sent to its destination. This process arbitrates the packet access to the finite output resources by scheduling the access to these resources. This process can be

<u>S-Stage:</u> A space switch provides independent concurrent cross-connections between inputs and

applied to both packet and circuit

switched data systems.

outputs. The classical operator switchboard, used in the earlier half of this century, is an example of an *S-stage*. Cross point switches are another example of the *S-stage*.

A T-stage that includes multiple inputs and outputs can perform the operation of an S-stage, but there are physical size limitations on this switch architecture. The number of inputs/outputs can cause an electrical implementation of the circuit to

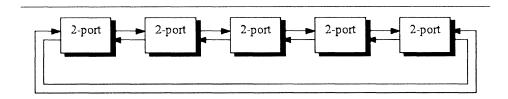

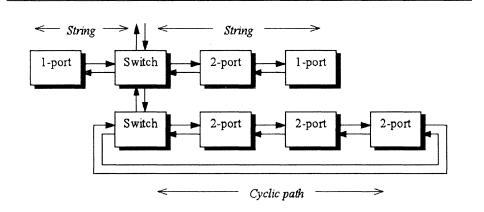

Figure 1 Typical Communication Switch Architecture.

become I/O bound, whereas the physical size of the temporary storage memory will limit the number of channels that can be handled by one circuit assembly.

This is the reason why the T-S-T architecture is so popular in switch designs. A simple T-S-T architecture allows a modular implementation for switching circuits. This modular implementation allows a single switch to be expandable in both the number of individual input/outputs that can be

serviced and the amount of data that can be handled by one central switch.

Figure 1 shows the basic architecture for a typical *T-S-T* switch. The circuit includes a *Switch Controller* that is used to monitor and control the operation of the switch. Typical functions implemented by the *Switch Controller* include:

- Switch Configuration;

- Circuit Synchronization;

- Status & Health Monitoring

- Billing & Customer Use Control:

- Circuit Switching Connection Control;

- Packet/Circuit Switch Priority Control;

#### **■** Circuit Implementation:

Present implementations of this system use proprietary hardware to implement most of the switch. This can be costly to design and manufacture. In many cases, the design and manufacture of the Switch Controller is based on current CPU and chipset technologies. Given the constant state of flux of the CPU market, especially the chipset market, the reliable supply of CPU's as Switch Controllers becomes a concern.

The use of generic hardware can reduce the overall cost of such a circuit and remedy the CPU source supply problem. For

instance if a standard backplane, cardcage and CPU is used, the cost of designing the Switch Controller is eliminated. A switch manufacturer could concentrate all of their efforts on designing switch hardware instead of spending their time redesigning Switch Controllers. Since the Controller is a standard product, it can be easily updated by just simply swapping boards.

#### ■ PCI Bus:

By designing the *T-stage* components

of the switch as PCI compatible assemblies, the interface between Tstages can be greatly simplified. The actual implementation of the S-stage can be done with the PCI bus architecture. The PCI bus completely replaces the S-stage.

The PCI bus supports burst transfer rates up to 33 Mcycles/sec, with data bus widths up to 64 bits. The bus therefor yields a peak data rate of i:

> R<sub>peak</sub> = 33Mhz × 64bits/cycle R<sub>peak</sub> = 2.112Gbits/Sec

Given that the bus can be used at up to 85% of its bandwidth, which is not unusual for synchronous access schemes such as time-divisionmultiple-access (TDMAii iii), the net transfer rate of the PCI bus is:

> $\Re_{net} = 2.112 Gbit/Sec \times 0.85$ Rnet = 1.795Gbit/Sec

As a figure of merit, one can compare this net rate to the number of telephone channels it can support. uncompressed voice channel requires a channel rate of 64kbit/sec1. The PCI bus in this recommended application could support 33,000 simultaneous phone conversations!

Reset

Since the probability of using all phone lines at the same time is quite remote, a multiplication factor is used to determine the total number of lines that such a switch could handle. If the probability of a line being used is 0.2, the total number of lines that can be serviced by such a system would be over 165,000.

The use of such a circuit would find itself applicable to medium rate services. This would include such applications as PBX systems which are commonly installed in medium to large sized corporations. Since the system can support expansion by simply installing more T-stage elements, a common system would service many different clients.

Other medium rate services include central phone office services. As stated above, each system could handle up to 33,000 simultaneous calls.

#### **■** Software Development:

In the past, the software developed for data switching circuits was based on real time operating systems. The recommended solution discussed in this paper would maintain the use of this software database, however, the development platforms used to write the application software would be based on common PC technology. Because of the close relation between existing PC platforms and the recommended solution, the cost of

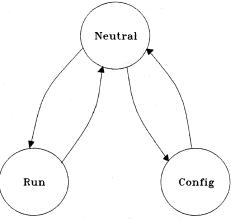

Figure 2 State Diagram of Communication Circuit.

true for hardware and software development tools.

Given the state of the art of today's PC technology and the reliable supply of industrial quality CPU's, the future development of data switches will be readily supported for years to come.

#### ■ System Architecture:

To implement the proposed system, the PCI bus must perform the same functions performed by the S-stage and provide interconnections between the T-stages & Switch Controller.

The circuit will assume one of three mutually exclusive states (see Figure 2).

Neutral: The Neutral state is initially forces

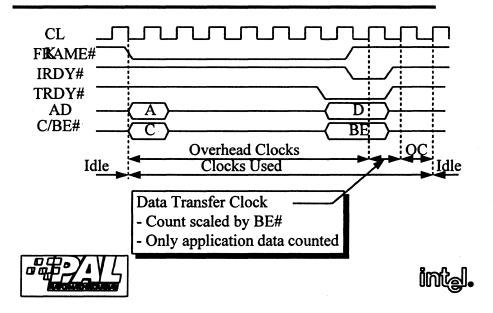

Figure 3 Transition Diagram of PCI Bus Events.

<sup>1</sup> A standard telephone service uses a sampling rate of 8kHz at 8 bits/sample.

This is especially evident in development and coding of common drivers used in such a system. It is also

assume a failsafe operation mode. This mode affects all of the modules of the switch.

<u>Configuration</u>: The <u>Configuration</u> state is used to configure the switch. This mode is executed sequentially and is not bound by real-time operating requirements. This state may be used to perform software downloads from the <u>Switch Controller</u> to the <u>T-stage</u> modules. It may also be used to perform offline diagnostics and major switch reconfigurations.

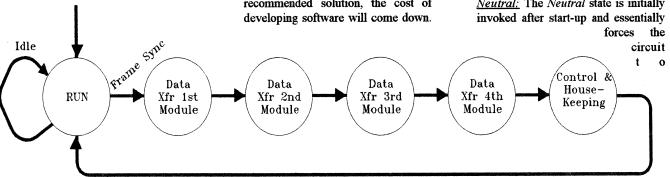

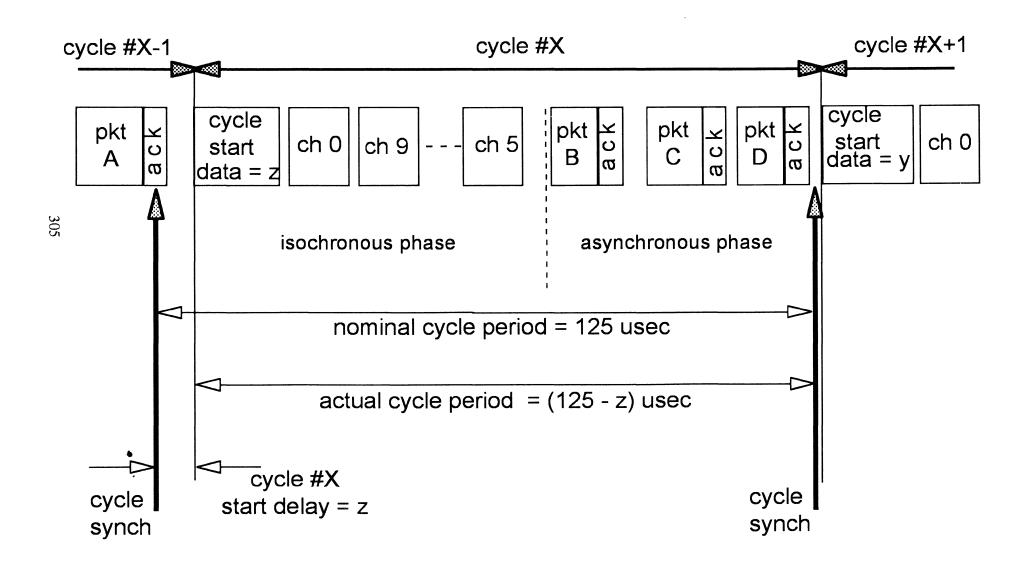

Run: The Run state requires the system to operate in a synchronous mode. Figure 3 illustrates the activity during this state. The PCI must perform all of the functions of the S-stage, and must also support the communications between the system modules. This process is synchronous, and must not be interrupted by other processes within the system.

The run process is invoked from the neutral state, and is triggered by the Frame Sync interrupt. The typical period of this event is 125µS. During this period of time, the Switch Controller will command each T-stage module to send data packets to their appropriate destination T-stage. The dwell time for each module is the same. Upon completing the four transfer processes, the Switch Controller will query each T-stage for status information and send commands for the next Frame Sync cycle.

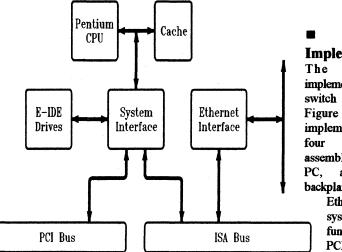

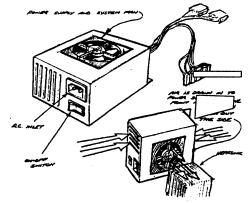

standard PICMG backplane using a 64 bit PCI extension. The T-stage modules are custom, in that they are specific to the switch implementation, however, the PC and backplane are based on standard products. An industrial PC such as Teknor's PCI-933 can easily implement the circuit described in this note. Assembly Because of the low bandwidth requirements of the Switch Controller. PCI a standard 32 bit PCI interface is sufficient. Assembl The major advantage of using a PCI-933, is that the operation of the PCI T-Stage bus, E-IDE disk drives and the ISA bus are concurrent. This allows the system designer to base their design on the multi-master PCI bus. Figure 5 Assembly illustrates the three Industrial (Switch Controller) ISA Ethernet Controller E-IDE Drive(s)

Figure 4 Physical Implementation of a *T-S-T* Communication Switch, Implemented with an Industrial PC and PCI bus.

Figure 5 Block Diagram of Major Components of the Teknor PCI-933.

### Physical Implementation:

recommended implementation of the T-S-Tswitch is illustrated in 4. This implementation includes PCI T-stage assemblies, an industrial a PCI/ISA backplane (PICMG) and an Ethernet controller for system management function interface. The PCI/ISA bus backplane is implemented with a

independent paths of the PCI and ISA busses, as well as the system disks.

To maximize the switch traffic over the PCI bus, parallel processing paths must be used to assure that the PCI communication process is not interrupted.

While the system is operating in the Run state, the Switch Controller must operate independent and in parallel with the S-stage process. Asynchronous communications between the Switch Controller and the Ethernet bus must not affect the operation the PCI bus. A T-S-T communication switch based on the PCI-933 will fulfill all of these requirements.

3

#### PCI Spring: Industrial Applications

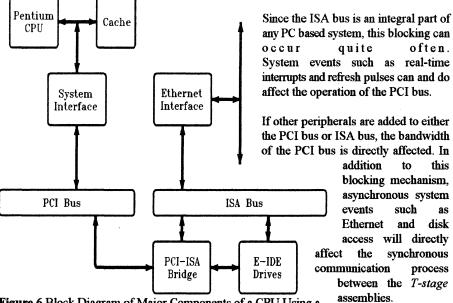

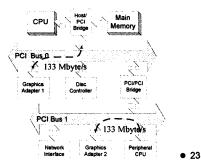

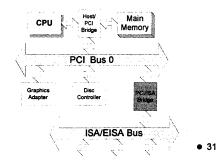

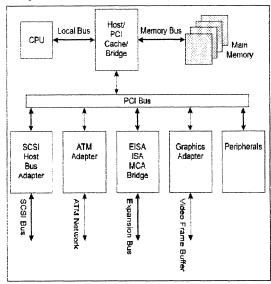

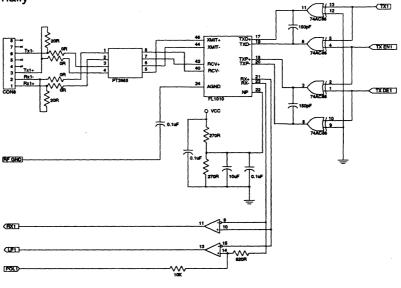

Figure 6 Block Diagram of Major Components of a CPU Using a PCI-ISA Bridge Interface.

Alternate products base their industrial PC designs on PCI to ISA bridge implementations (see Figure 6). These implementations have the disadvantage of locking up the PCI bus anytime the ISA bus or disk drives are accessed.

**Conclusion:**

The architecture developed in this paper demonstrates the versatility of the PCI bus architecture. Furthermore, this architecture will allow communication switch designers the flexibility and choice of using standard Industrial PC

products in their new switch designs. The overall performance of the bus is quite substantial, and is capable of taking on bigger and more complicated tasks.

The use of the Teknor PCI-933 is compatible with the needs of advanced communication circuits and is capable of handling the multi-task environment of standard switch architectures.

#### **■**Biography:

Ray Kolment is the PCI Group Leader for Teknor Industrial Computers Inc. in Montreal Quebec. He holds a Masters Degree in Electrical Engineering from New Jersey Institute of Technology, and his major studies include topics in communications systems. He had completed his Master's Thesis in switching theory. Mr Kolment is presently involved in the definition and design of advanced computer and communication products at Teknor Industrial Computers Inc. 616 Curé Boivin, Boisbriand, Quebec J7G 2A7 (514)-437-5682.

#### **■** References:

- i. PCI Local Bus Specification; Rev. 2.1, Oct. 21, 1994

©PCI Special Interest Group; 1994

- Local Networks; Franta, W.R & Chlamtac, Imrich 3rd ed. D.C. Heath & Co.; Lexington Mass. 1981

- iii. A Study in Data Communication Networks; Kolment, Raymond Department of Electrical Engineering; New Jersey Institute of Technology July 1988

#### Impact of PCI Technology on Control Solutions

by Edwin Lee (Pro-Log Corporation)

#### **Abstract:**

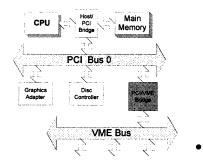

PCI Technology will accelerate the decade long process of replacing systems specifically designed for industrial applications, including Allen Bradley programmable controllers and VME bus products, with systems that meet the Intel/Microsoft standards. PCI Technology will help to make the Intel/Microsoft standards as dominant in control systems as they are in desktop PCS.

PCI Technology bus speeds, I/O expand-ability, and multi-processing support are ample to concurrently handle real-time control, graphics intensive data processing, and high speed networking. The driving forces behind the move to Intel/Microsoft compatible solutions in Control Systems are: economics, the *Mind Bus*, and immediate access to the latest improvements in hardware, software, and design tools.

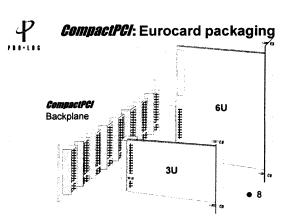

PCI Technology is now available for Control Solutions in three packaging formats: desktop, Passive backplane, and **CompactPCI**<sup>TM1</sup> The desktop format provides the most economic and convenient solutions at the expense of ruggedness and mean-time-to-repair. The Passive backplane format improves ruggedness and slightly reduces the mean-time-to-repair. **CompactPCI** combines the IBM PC electrical and software standards with the Eurocard packaging standards to produce cost effective systems with the ruggedness and mean-times-to-repair required by the most demanding applications.

Passive backplane PCI and **CompactPCI** are emerging, open standards supported by PICMG, the PCI Industrial Manufacturers Group. This two year old association already has over 90 member companies, and includes IBM, DEC, HP, and Force on its Board of Directors. Any company is free to make or buy products to the standards it supports.

#### The Industrial Versions of PCI Technology

PCI technology is available in three packages: desktop, Passive Backplane, and CompactPCI (Eurocard).

Desktop computers have been used in control systems for the last decade. Although I don't have specific survey data, my estimate from experience and anecdotal data is that ~ 40% of control systems already use desktop computers because of their convenience and low costs. The trend started a decade ago. For example, in 1985, one user had already rigged a desktop IBM PC to control part of his process in a cement mixing plant. He protected the system from dust with a protective plastic covering. His backup system? His secretary's computer!

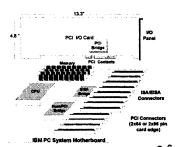

Passive Backplane systems have approximately the same form factor as desktop systems. However, the

<sup>&</sup>lt;sup>1</sup>CompactPCI is a registered Trademark of PICMG

motherboard is replaced with a plug-in system card and a passive backplane that includes both the PCI bus and the ISA bus. In addition, the systems have beefed up cooling, beefed up power supplies and far more rugged packaging. This family of products is already available from dozens of manufacturers, including Pro-Log.

**CompactPCI** packages the desktop PC, including the PCI bus, in the Eurocard format. **CompactPCI** has a passive backplane and a system card. However, high density pin and sleeve connectors replace the card edge connectors of the desktop packages. The cards sizes are standardized in 3U and/or 6U Eurocard formats. The cards are locked in place and are supported on all four edges. The Eurocard packaging, required in Europe for industrial systems and popularized in this country by VME bus, vastly improves shock and vibration tolerances and thermal characteristics. The pin and sleeve connectors used by **CompactPCI** enhance grounding and shielding which improve performance margins and PCI bus fanout (A system card can drive 7 peripheral cards for each set of bridge chips) and reduce EMI radiation and susceptibility.

Users of **CompactPCI** can buy or make products that bring I/O out the front panel (as is now typical for Industrial Control systems) or out through a connector to the backplane (as required by Telecommunications systems to minimize down time during card replacement).

#### The Economics of PCI Technology

PCI Technology is driven by the >\$150 billion desktop PC market. This juggernaut is driving chip development, chip production, applications development and software development. Products used in this market have such an overwhelming volume that their costs to produce are the lowest possible. Furthermore, they are supplied by low margin, aggressively competitive suppliers.

By contrast the Controls market is somewhere around \$4 billion (Including telecommunications, industrial control, instrumentation, and medical electronics). The income stream from the Controls market is not adequate to sustain leading edge product development (hardware or software) or to produce products at competitive prices. Furthermore, the traditional suppliers require high margins to support expensive technical support, sales and service infrastructures, and to earn reasonable profits. The result is product costs to users that are two to five times that of comparable desktop products.

Apple computer, with its 7% share of the desktop PC market, has a far bigger market than the entire controls market. However, it hasn't been able to thrive by competing with the Intel/Microsoft standards. Motorola has given up on its CPU race with Intel. The income stream for the 680x0 CPUs produced by Apple, VME bus, and a captive market was not enough to sustain innovation. The Power PC is Motorola's *fig leaf*, not a viable alternative.

Just to clarify the economic perspective: \$1.5 billion is the entire market for VME bus hardware, software and systems this year (fewer than 250 thousand VME bus systems). It is also Intel's market share of the PCI system logic chip sets (40 million)! Intel is only one of several suppliers.

#### The Mind Bus and PCI Technology

The *Mind Bus* is a term I use to describe a standard set of skills, expectations, and beliefs about computers held by the hundreds of millions of people who buy and use them. The Mind Bus has been created by the desktop PC market over the last 15 years. It is shared by engineers, executives, students and housewives (just to name a few). It's responsible for Apple's shrinking market share and with Allen

Bradley's difficulties over the last decade.

The Mind Bus provides common expectations and value references. These expectations and value references didn't exist fifteen years ago. They already impact customer preferences in Control Solutions, and explain the wide use of desktop PC's in control systems. Because the PCI Technology removes performance restrictions, the Mind Bus will dominate how designers implement Control Solutions within five years.

PCI Technology is part of the desktop PC standards and it is part and parcel of the Mind Bus. I don't have to sell it or explain it in any detail to engineers or to executives. However, I would have to spend considerable time and money to sell an alternative to Mind Bus skills, expectations, and beliefs. Just ask Apple. They are clinging to less than 8% of the market with products that may be easier to use, but don't fit mind bus standards. Within a few years we should see the same situation in Control solutions.

#### Relevant Beliefs of the Mind Bus

Computers are commodities, not esoteric products that require careful selection, special training, and annual service contracts. Significant elements of this core belief include:

I expect industry standard computers to be cheap and reliable The best buys and latest innovations are always found in open-architecture, dominant standards supplied by many competing suppliers. Closed systems dominated computers until 1982. But, since then Wang, Apple, and IBM simply couldn't keep up with the rate of innovation and cost reductions provided by a host of suppliers vigorously competing to supply the IBM PC standards.

I can configure my own system to meet my specific needs by using standard "plug-in" hardware and software. I expect plug and play capabilities. Users routinely buy and successfully install third party modems, printers, and scanners. They no longer need to buy all products from a single supplier, or have suppliers install products or configure systems to specific applications. The customer thereby assigns little or no value to system configuration and system installation. Since customers can also update operating systems and applications software, they assign little value to these traditional, supplier furnished services.

I can successfully use them without studying user manuals or paying for special training by the manufacturer. User friendly software, built-in tutorials, third party books, or third party courses and workshops educate customers instead of User Manuals and manufacturer training.

I can buy computers, peripherals, and software through distribution (retail) and get the lowest prices and most convenience. Buying direct from the manufacturer is more expensive and produces less effective support.

I can usually service my own computer with the "as needed" backup support of the manufacturer, distributor, or third party service organization when and if the need arises. A one-year warranty supported by a telephone hotline is customary and expected. Beyond that, the failure rate is expected to be low enough that additional service is seldom needed, and annual service contracts are not cost effective.

Other core beliefs that affect the Control markets are:

Mass produced software is relatively cheap, reliable, and user friendly. It is worthwhile to solve my

problem using standard software rather than paying for special purpose software.

The desktop PC has created a value reference for software: price, performance, and user friendliness. That value reference is improving with time. Special purpose software is orders of magnitude more expensive, doesn't work as well, and is seldom as user friendly as the leading software for the PC standards. The customer asks himself: How can I use a standard word processor, accounting package, data base, customer contact package, etc. to fit my application? In the past customers would specify their needs and have software designed to meet them. That software was expensive, had bugs, and was horrible to maintain or update.

I expect dramatic improvements in performance/dollar each and every year, therefore I want a system I can update or replace frequently.

When a customer buys a desktop computer, she expects it to be competitively obsolete within 3 years. However, its architecture and its low costs give her the viable options to update it or replace it. The old belief was that the solution should be "competitive" for more than five years.

#### How the Mind Bus and PCI technology will alter the Controls Solutions

Designers will make commercial chips, operating systems, development systems, and applications software serve Control Applications. They will accept tradeoffs from the ideal solutions because of the overwhelming economic and performance benefits of making these tradeoffs. Two examples come to mind: multi-mastering as implemented on VME bus, and Hot Swap.

PCI technology does not support true multi-mastering as does VME bus. On the VME bus, any CPU can take over the bus. PCI technology provides a more limited multi-mastering through a single Host that supports bus mastering for a limited number of peripheral processors. However, PCI technology has enough capability to solve any control problem. Designers will make PCI Technology fit their needs, rather than require it to add true peer-peer multi-processing.

Hot Swap, changing a plug-in card without turning power off or rebooting the system, is a Holy Grail of many control system designers. Its benefit might be to reduce mean time to repair to a matter of seconds. (I seriously doubt that anyone would actually realize this benefit.) However, unless Intel makes it a standard feature of PCI chip technology, and unless someone modifies how Plug and Play software operates, the overwhelming majority (>99%) of control systems will continue to live without it. Plug and Play software, as it works today, analyzes the peripheral cards modifies their bioses during boot-up. If a peripheral card is hot swapped there would be not assurance that it would be compatible with the system unless that system were rebooted.). Of course there is no feasible way to "hot swap" a Host CPU card.

In my opinion, we will live without Hot Swap for the foreseeable future. Let me put it another way: should VME bus, for example, successfully implement hot swap, it will not help them sustain market share in any significant way!

Major accounts for Control Solutions will buy direct, smaller accounts will buy through Distribution. Major suppliers will trim their overhead by focusing on shipping large quantities of fewer, standard products to key accounts. Large Distributors will be some of their key accounts. OEMs, Distributors, and third party organizations (including VARs) will provide depot level and on-site service.

#### **PCI Technology and Legacy busses**

In the near-term, PCI Technology has to work with legacy buses, especially the ISA bus. These buses

have an established base of peripheral cards and operating software. PCI Technology can theoretically support as much I/O as anyone would need through PCI/PCI bridge chips. However, this solution is not yet fully implemented in the desktop world.

In the long run, PCI technology should greatly reduce, or eliminate, ISA usage in the desktop environment. It should more swiftly eliminate the use of ISA and other legacy buses, including VME, in the controls environment for a few simple reasons: reduced costs, improved performance, and greater software compatibility.

PCI Technology is supported, and will continue to be supported, by the latest in hardware and software tools. VME, for example, has different and far less up-to-date software tools to support it. It is far easier, far cheaper, and much more productive for suppliers to move their peripheral designs to the PCI bus, than to bridge the PCI bus to a legacy bus. A bridge is expensive and slows down one or both busses as it interprets one set of protocols to another. A PCI/VME bridge, for example, is like an English to Chinese interpreter passing information from one language to the other. Also, in a hybrid system of PCI and VME you can kiss *plug and play* goodbye.

What about legacy I/O busses like Allen Bradley's data highway? They'll hang on for years because old-timers will insist on sticking with what they know and will be able to hoodwink their management into paying enormous premiums to support their preferences. But new applications should move quickly to open-architecture I/O busses (like SCSI-2 or PCMCIA) supported by desktop software. There's a need for, and probably an opportunity for someone to develop an Industrial I/O bus that takes advantage of PCI technology.

#### **Conclusions**