RC 9225 (#40521) 1/22/82 Computer Science 40 pages

THE IBM SELECTIVE SEQUENCE ELECTRONIC CALCULATOR

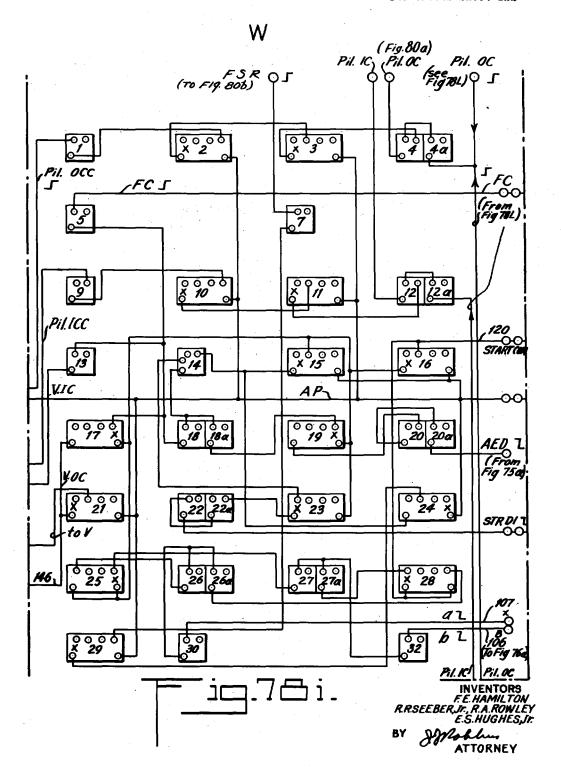

Arup K. Bhattacharya

Columbia University New York, N.Y.

Typed by: C.C. Coppola

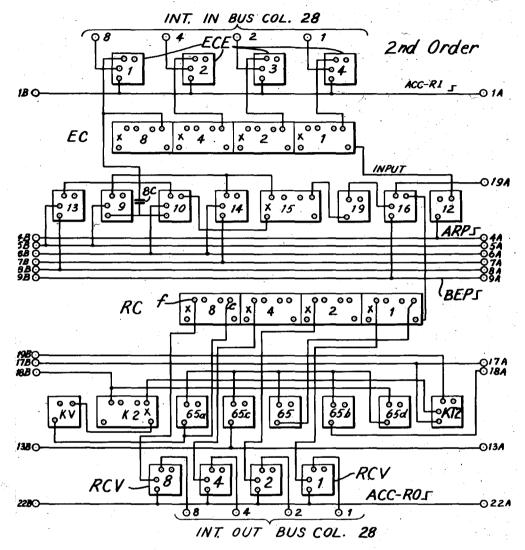

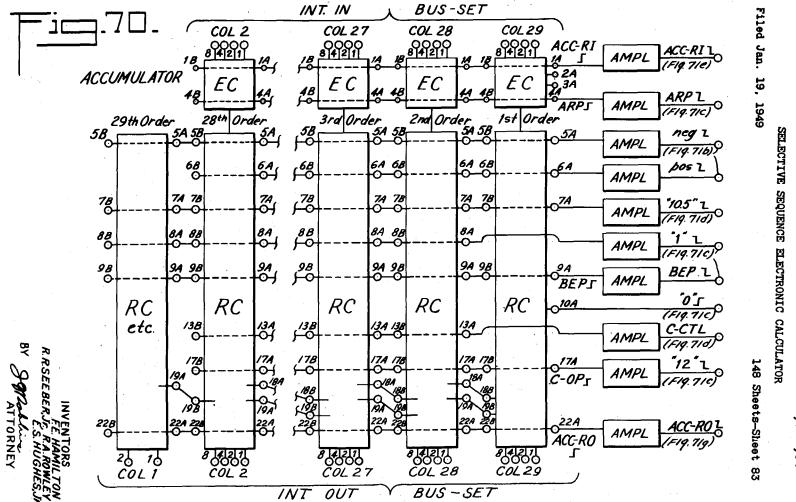

Abstract: The IBM Selective Sequence Electronic Calculator (SSEC) was placed in operation in January, 1948. It was partly electronic and partly electromechanical. It is of historical interest, in part because of its capability of operating dynamically on its own stored instructions as data. This report includes a summary of its major functional units, its program and value formats, and the manner in which it operated. This description is based primarily upon information contained in U.S. Patent No. 2,636,672, "Selective Sequence Electronic Calculator," issued on April 28, 1953, to F.E. Hamilton, R.R. Seeber, Jr., R.A. Rowley, and E.S. Hughes, Jr.

#### Introduction

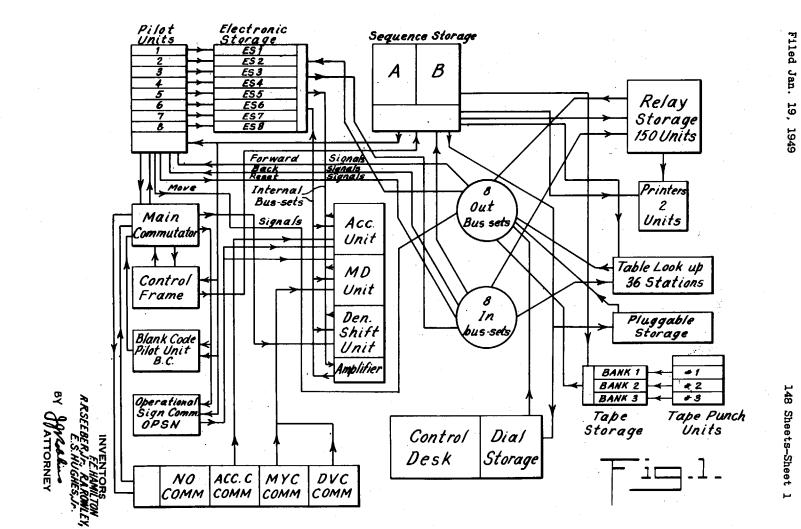

The IBM Selective Sequence Electronic Calculator (SSEC) was a large-scale electronic and electromechanical machine with all the system components of a modern general-purpose computer. It was developed and built in the IBM laboratory in Endicott, N.Y., in the period from 1945 to 1947, moved to IBM corporate headquarters in mid-1947, and placed in service with a formal dedication on January 27, 1948.

The SSEC performed its computations electronically, according to "lines of sequence" (instructions) stored in the same memory and in the same word form as ordinary data. Its memory consisted of three levels in three technologies, in order of increasing capacity and decreasing speed: electronic storage units (registers), relays, and punched paper tape. It was capable of modifying any part of an instruction in memory, including the part that specified the next instruction to be executed.

The SSEC contained 12,500 vacuum tubes, 21,400 electromechanical relays, and 66 paper tape readers, and occupied the periphery of a room about 60 feet long and 30 feet wide. It is of historical interest, in part because of its ability to modify its own program. It was not described in great detail in its own day (it was dismantled in mid-1952), and in order to produce the equivalent of a programmers's description of the machine, a study was made of U.S. Patent No. 2,636,672, "Selective Sequence Electronic Calculator," issued on April 28, 1953, naming as inventors F.E. Hamilton, R.R. Seeber, Jr., R.A. Rowley, and E.S. Hughes, Jr., of IBM. That patent is the primary source of information that has been used in this description.

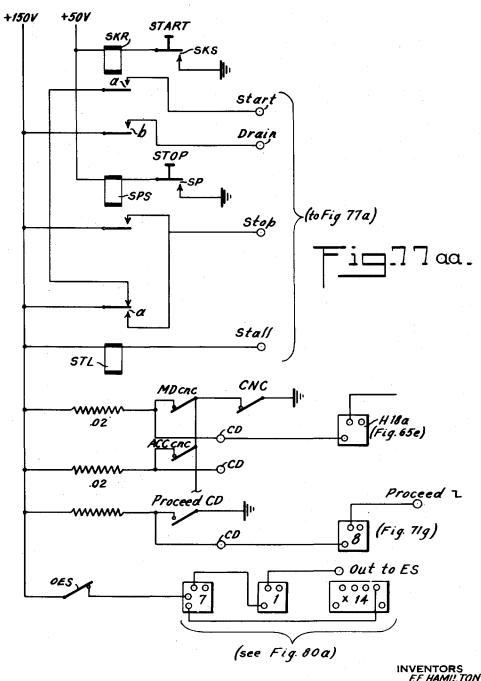

### **CONTROL DESK**

The Control desk is a manual switching center at which a duplicate of practically every control circuit in the machine may be set up by manipulating switches and keys. The control desk holds control keys such as start and stop keys; also sets of dial storage and the switches and keys for use in setting up an artificial line of sequence. A keyboard and connection are also provided at the control desk for applying desired numbers to relay storage. Cancel circuits (clearing circuits) for the MD calculating unit, the accumulator unit, the denominational shift unit, the electronic storage, the main commutator, the pilot units and every other unit desired may be operated individually or together from the control desk as well as automatically.

# ARTIFICIAL LINE OF SEQUENCE

The machine is started by an artificial line of sequence, which is manually set. This consists of S1 or S2 data or both and is inserted in sequence storage under manual control, as the starting instruction for sequencing of operations of a problem. In other words, the artificial line of sequence data provides direction as to where the first real set or line of sequence data is to be obtained. By a real set of sequence data is meant such data as is called out automatically from tape storage or relay storage or other source for sequencing operations leading to the solution of some problem.

### **RECORD TAPES**

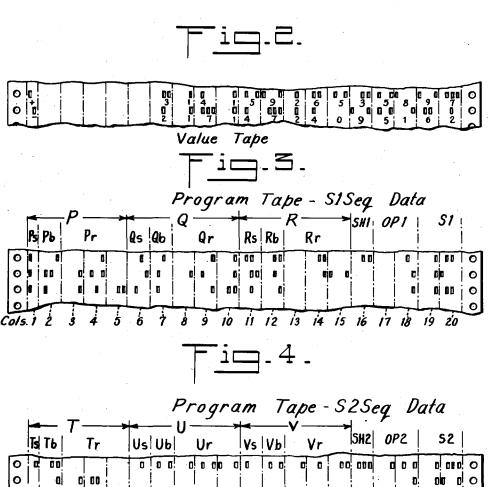

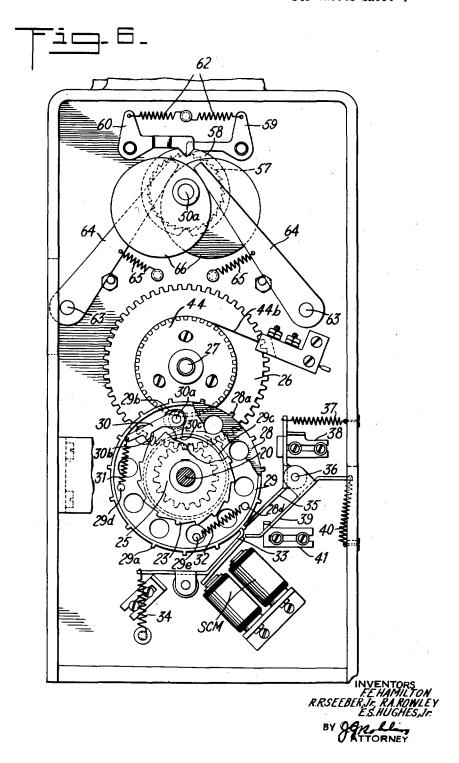

The record tapes may be used to store values either for computational purposes or for program or sequence control purposes. Sequence data is made up of numbers which can be handled the same as the numbers involved in calculation. Tapes which store numbers for computation are called "value tapes." Tapes which bear programming or sequence data are called "program tapes." For both program and value tapes, the numbers are punched according to the same code, binary coded decimal, in which a complete binary zone which is called a column, is made up of four successive binary positions 8, 4, 2 and 1.

The record tape has the width of a standard 80 index position card, but owing to the space occupied by the marginal feed holes, 78 positions are allowed. In other words, tape has a capacity of 19 and half digit columns, or sufficient capacity to be punched, if desired, with representation of nineteen decimal digits and a sign. Hence, this row of 19 and one-half index positions illustrated in Fig. 1 is called a "word."

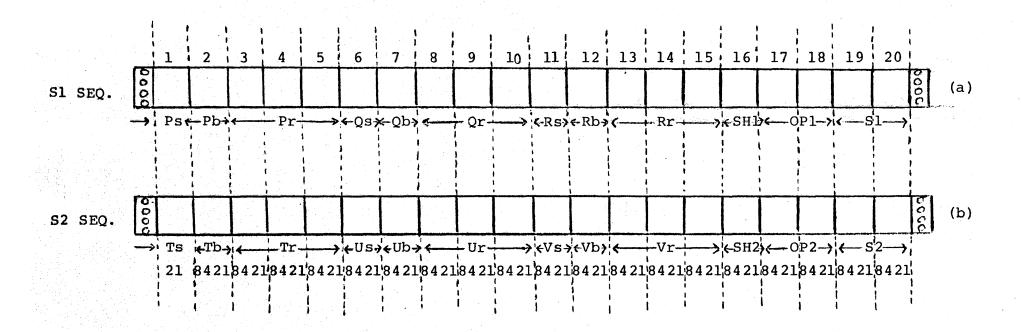

Figure 1

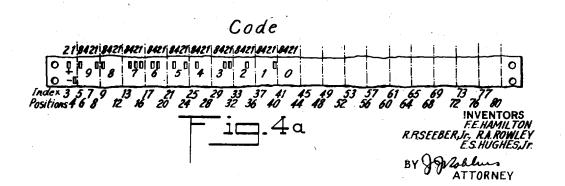

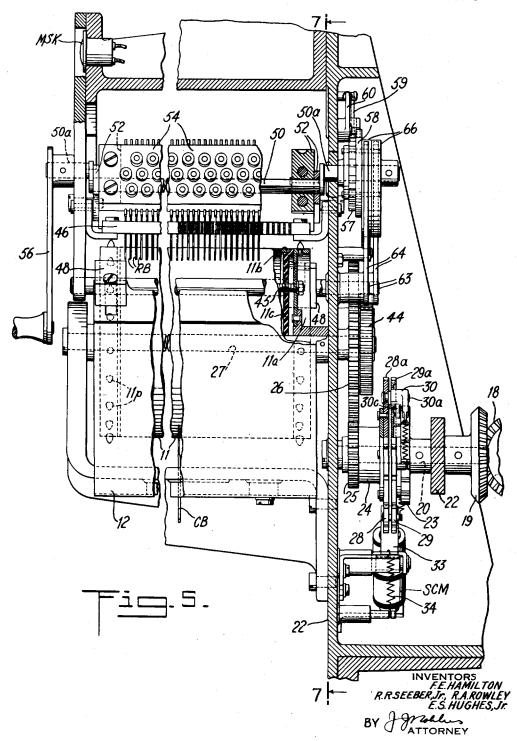

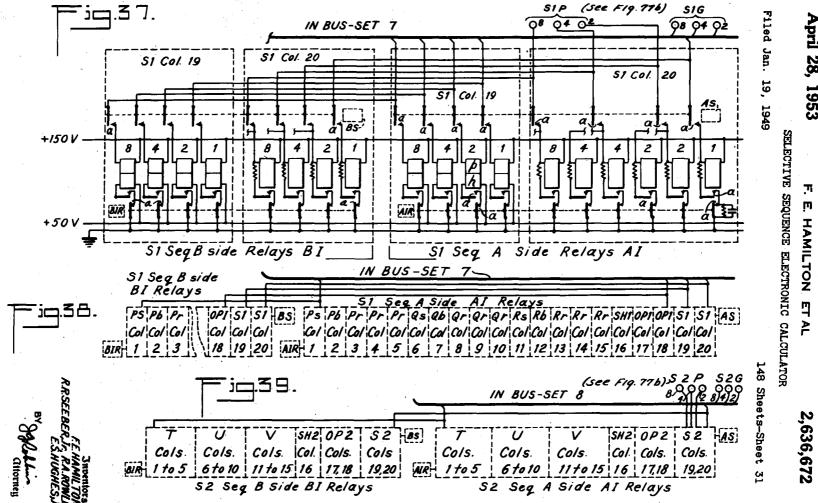

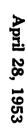

#### PROGRAM TAPES

Programming or sequencing of machine operation is controlled by the program tapes illustrative portions of which appear in Fig. 1 (a) and (b). Successive designation lines of the program tapes bear sequence data which may be referred to as an "instruction word," or as "sequence data." A complete line of sequence data is made up of two designation lines on a pair of program tapes. One half of the line of sequence data or one "word" is a designation line on one tape and the other half is a designation line on another of the tapes. The values of words are differentiated as S1 Seq. and S2 Seq. portions. So a program tape will be punched with either S1 Seq. data or S2 Seq. data. Both S1 Seq. and S2 Seq. data are similar with respect to the arrangements of fields and subfields, but have certain differences with regard to programming functions. S1 Seq. portion is made up of fields P, Q, R, SH1, OP1 and S1 (Fig. 1(a)), whereas, S2 Seq. of portion is made of fields T, U, V, SH2, OP2 and S2 (Fig. 1(b)). The fields Q, R, U and T may be used as either IN or OUT fields. Field P is always an OUT field and field V is always an IN field. An OUT field is one which calls for the reading out of data from a selected tape or relay storage source to a selected electronic storage unit by way of the out bus set fixed by association with the electronic storage. An IN field is one which calls for transmission of data from a selected electronic storage unit along the corresponding IN bus set to a tape or relay storage distinction. Each of the fields P, Q, R, T, U and V are divided into three subfields, s, b and r. Ps subfield comprises column 1, which is actually half a column (2 bits) with decimal values 0, 1, 2 and 3 only, and is used to designate the operational sign which is to be applied for a number read from a source. A perforation in binary position 2 designates operational "+" sign, i.e., the number taken from the source named in Pr (see later) is to be handled in calculation without any change of its sign. A perforation in binary position 1 represents operational "-" sign, i.e., the number read to be operated upon with an inversion in its sign. The absence of perforation in Ps represents "0," which is for operational fixed "+" sign, i.e., regardless of the original sign of the number it is to be treated as a positive number. Perforations in both binary 2 and 1 position represents decimal 3 which

means operational fixed "-" sign, or treating the number as "-" regardless of the original sign. Pb subfield is the column 2, which may contain the decimal values 1, 2, 3 ... 8, designating the electronic storage unit and corresponding out bus set involved.

Pr subfield is made up of columns 3, 4 and 5 bearing the hundreds, tens and units digits of the Code number for the source from which a value is to be transmitted to the electronic storage unit named in Pb.

When a subfield "b" in any program field P, Q, R, U, V and T is blank, it represents "0" and calls for the field to be, in effect, skipped over, during a scanning sequence of the program line. When a subfield r in an OUT field is blank, then it calls for transmission from the electronic storage unit named in its b field to the electronic storage unit named in the b subfield of an IN field, which may also be blank in its r subfield. Field Q may be used either as IN field or an OUT field. Subfield Qs is a complete decimal column, unlike Ps, and occupies column 6, in which 0, 1, 2, and 3 have same designation as Ps. Additionally, any of these numbers in Qs characterize Q field as an OUT field. Any digit in Qs higher than 3 makes Q an IN field. Besides the values 4 to 9 designate the tens denomination of a column shift and whether the shift to be executed to the left or right. The value 4 in Qs thus designates Q as an IN field and also calls for a shift to the right with a zero tens order. A 5 has same interpretation only with a shift to the left. The value 6 calls for right shift with a tens order shift of 1. 7 calls for the same amount of left shift. The value 8 calls for a right shift with a tens order shift of 2. 9 does the same for a left shift.

Subfield b, in column 7, is used to designate the electronic storage unit number to send or to receive data, depending on whether Q is an IN field or an OUT field. Qr is located in columns 8, 9 and 10 to represent the source from which a number is to be sent to the electronic storage unit if the field Q is an OUT field or to represent the receiving unit to which the number is to be transmitted from the electronic storage unit if the field Q is an IN field.

Field R is contained in columns 11 to 15 and its subfields are similar to the field Q and its subfield.

Field SH1 in column 16 designates the units order amount of column shift to be executed.

Field OP1, in column 17 and 18 calls for the fundamental calculating operations to be performed, such as accumulation, multiplication, division, etc.

The field S1 is a two column field in 19 and 20 which designates the source for next left half line of sequence data.

The right half line of programming, S2 Seq., has fields and subfields similar to those of the left half line, S1 Seq. Generally, all fields and subfields of S2 Seq. correspond to those of S1 Seq. with the following exceptions:

- 1. As mentioned before, field V is always an IN field while P is always an OUT field.

- 2. The field T can be either IN or OUT field depending on the code in the field OP2.

When the latter field has the designation O1, it characterizes T as an IN field. In all other cases, the field T is an OUT field.

It is important to understand the sequential nature of the scanning and execution of the elementary operations called for in a line of sequence: The left half line, or word, is executed first; then the right half line; then the next half line, etc. Furthermore, within a half line, the fields are interpreted and the specified elementary operations executed also from left to right.

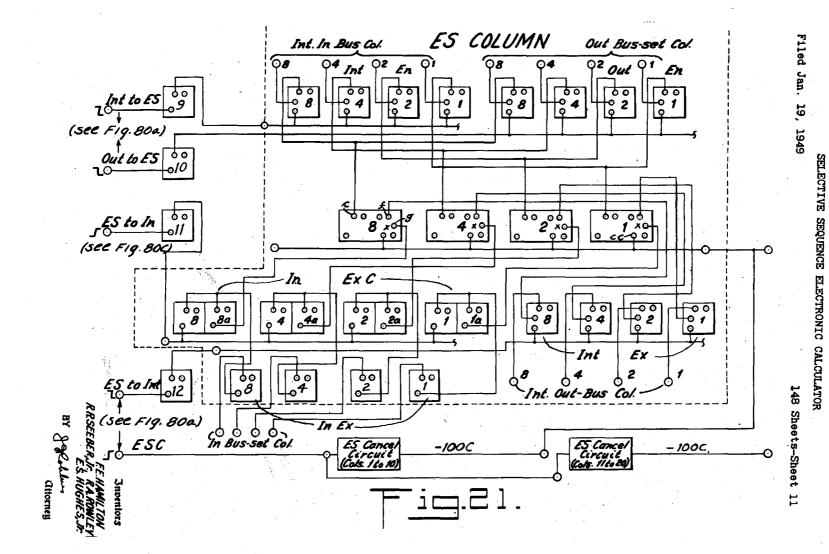

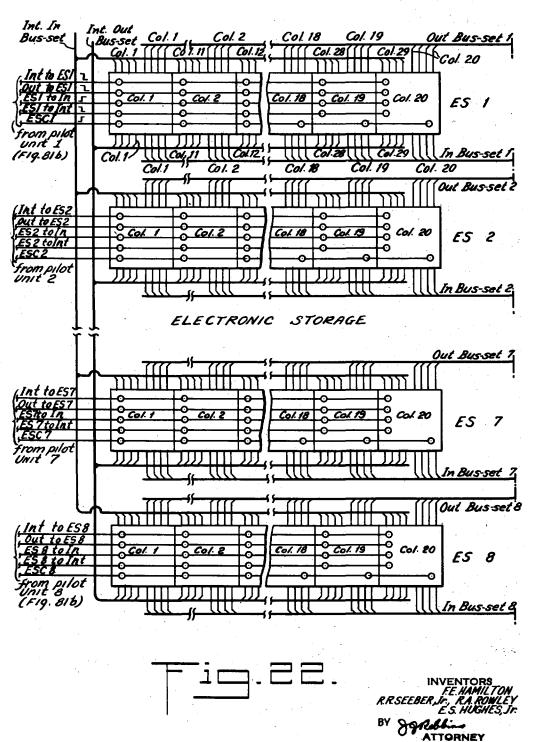

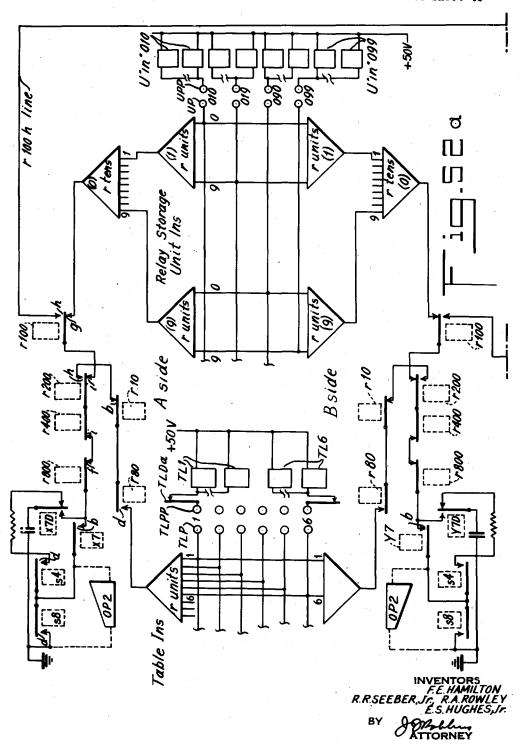

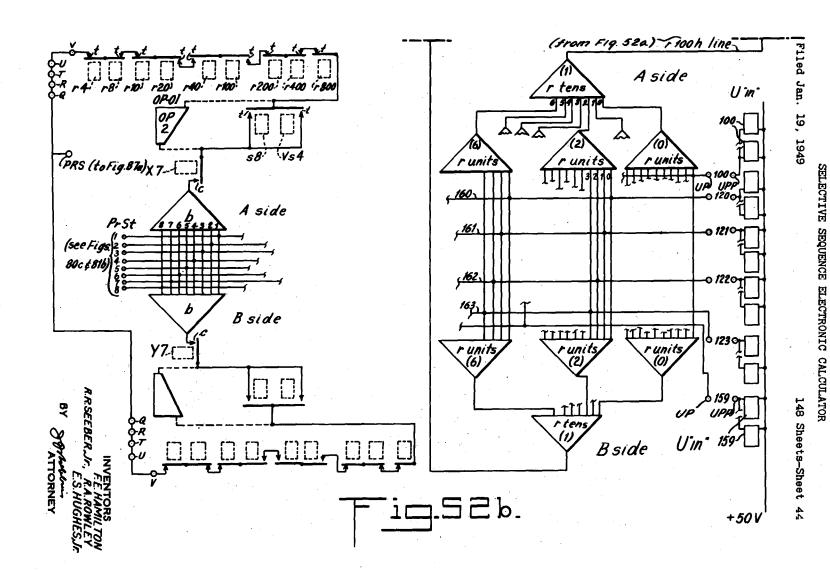

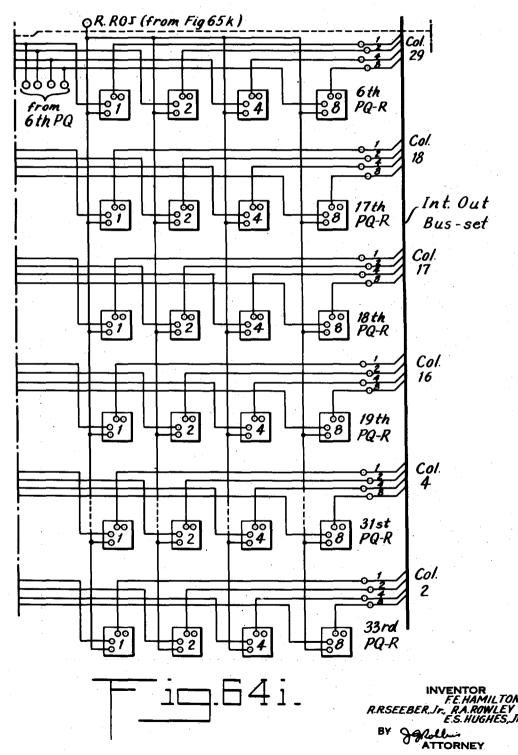

### **ELECTRONIC STORAGE**

The electronic storage units are used for the temporary storage of numbers, and may be compared to the general arithmetic registers of a modern computer.

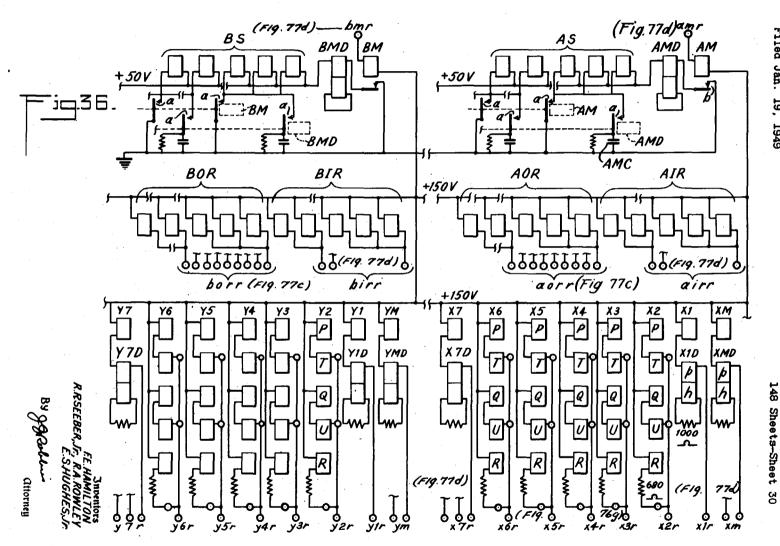

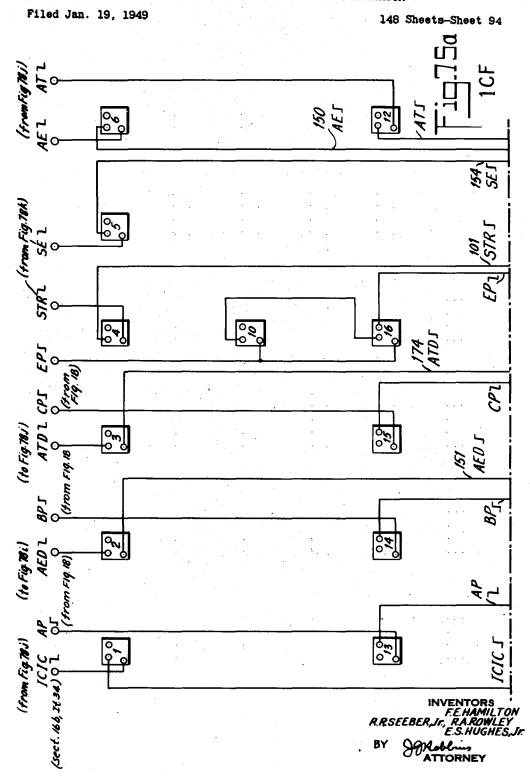

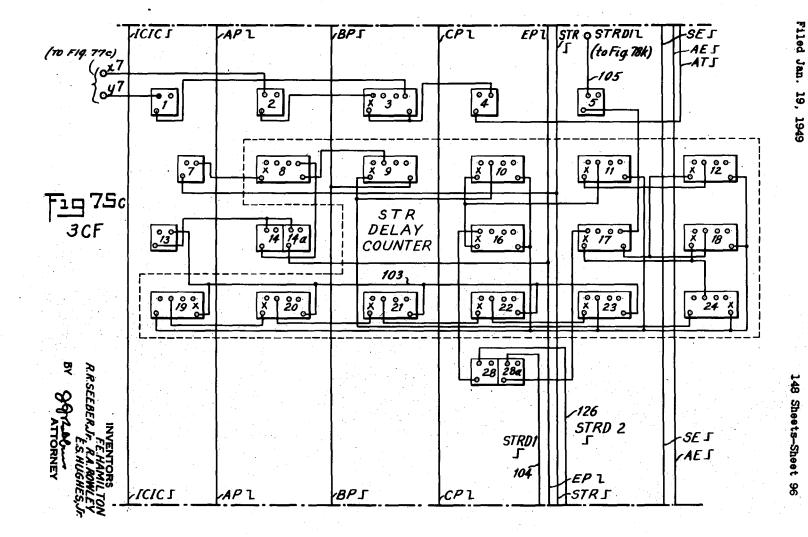

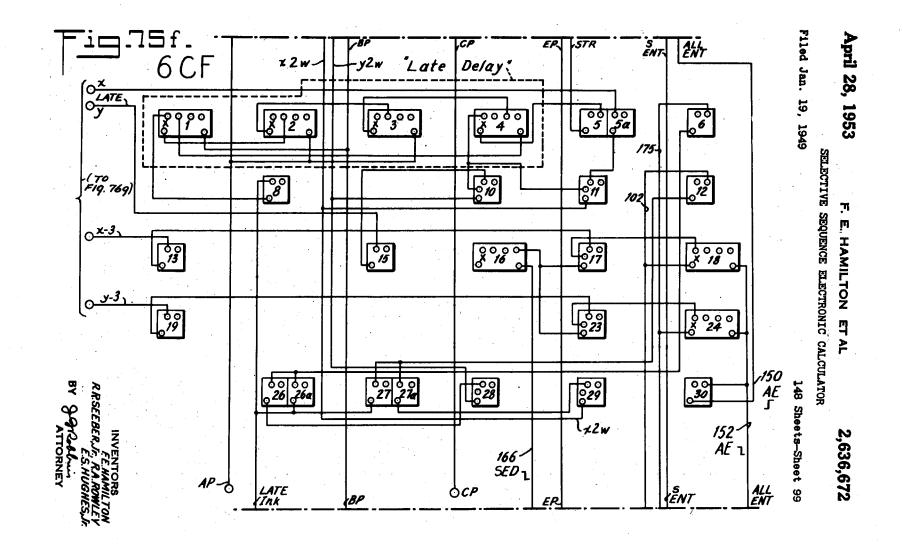

There are eight similar electronic storage units designated as ES1, ES2 ..., ES8. Each has twenty columns (eighty bits) of decimal digit storage capacity. Entry into the ES may be made from the internal IN bus set or alternatively from the corresponding numbered OUT bus set. Read out or exit from an ES unit may be into the internal OUT bus set or alternatively into the corresponding numbered IN bus set.

All control and timing signals of ES are provided by the eight correspondingly numbered pilot units. Whenever any transfer occurs, the data are passed through the electronic storage unit. All numbers on the OUT bus sets enter electronic storage on their way to selected destinations.

All numbers on the IN-bus sets, with the exception of the artificial line of sequence from the dial switches, are taken from the associated electronic storage units and directed to the specified receiving units. The electronic storage units are numbered 1, 2, 3, ..., 8 and can be accessed by the use of corresponding digits in the single-column "b" subfield in the program sequence.

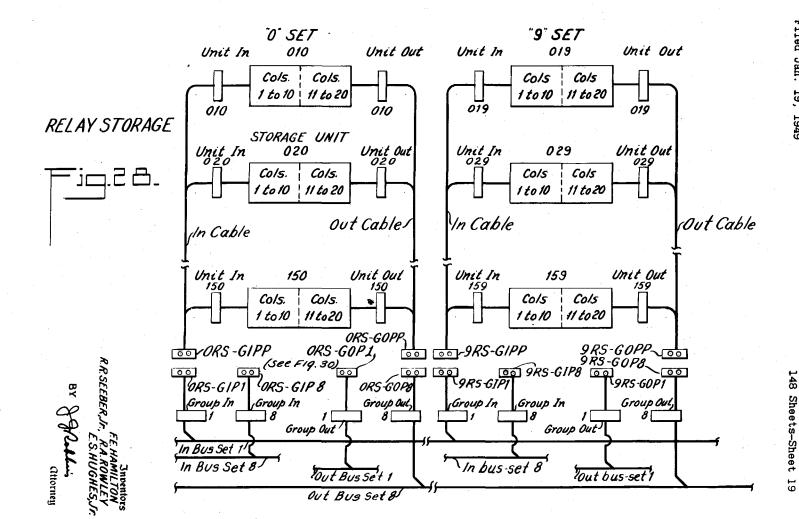

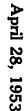

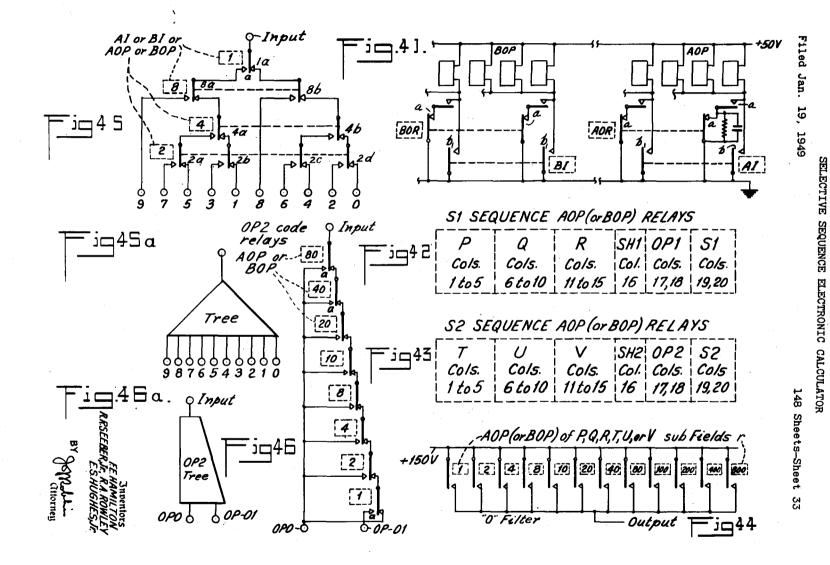

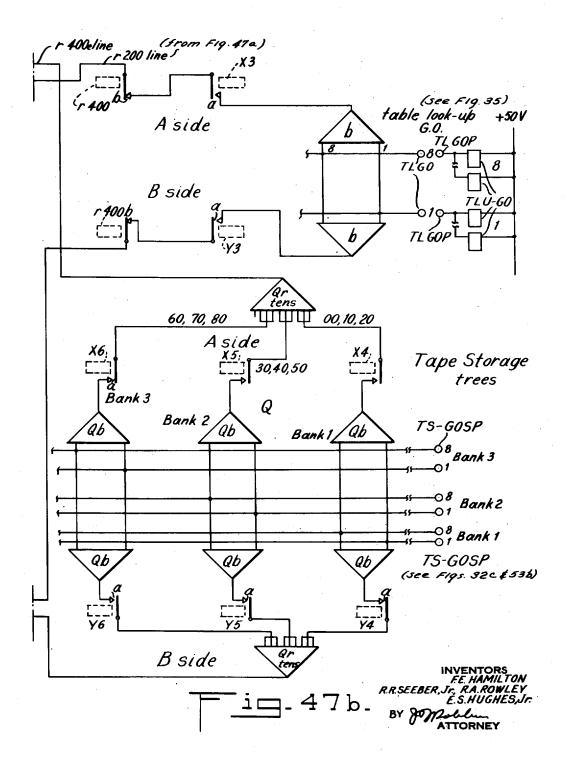

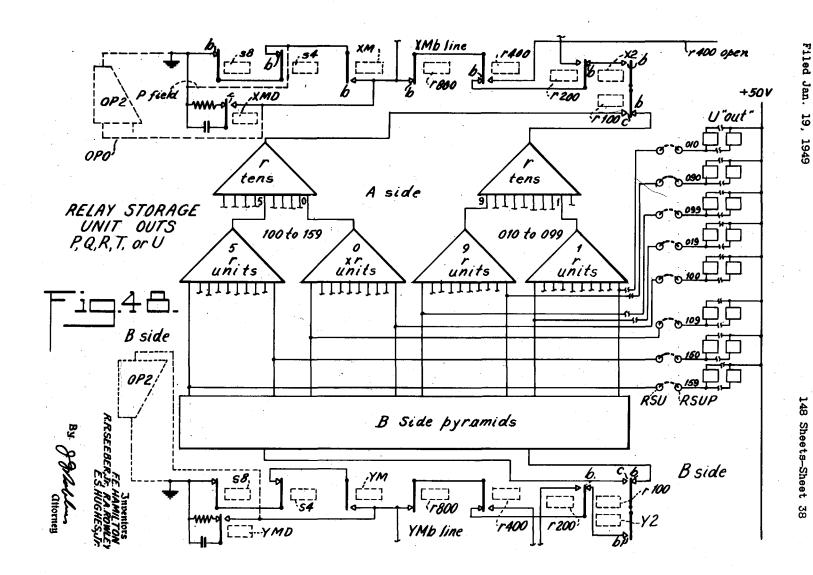

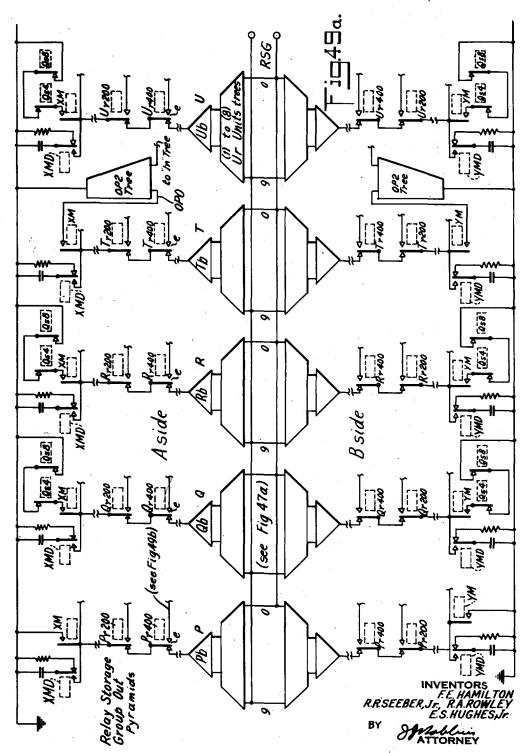

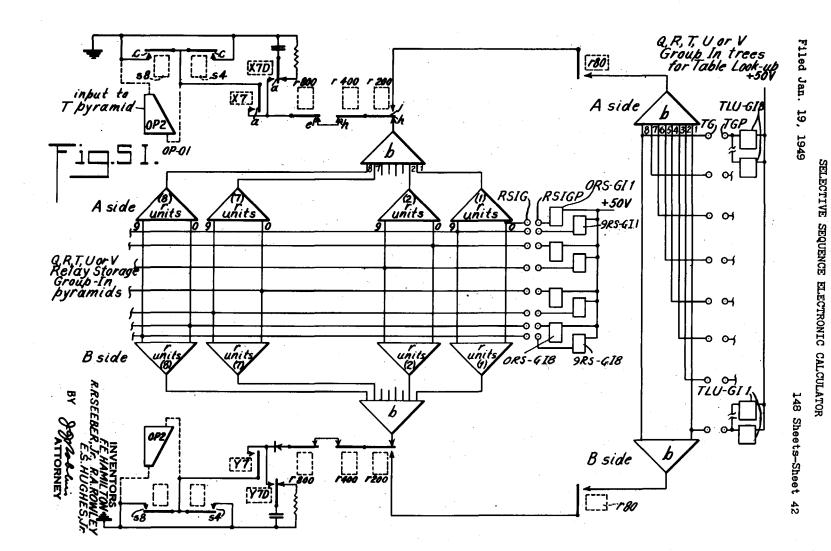

#### **RELAY STORAGE**

Relay storage consists of sets of relay storage registers, also called relay storage units, which receive numbers from the IN bus sets and store them until called out for transmission along the OUT bus sets. Certain of these relay storage units also serve to control the printing unit, as will be explained later (in printing section). There are ten sets of storage relays designated as the 0, 1, ..., 9 sets. Each set has fifteen storage units and each unit has twenty columns of storage relays, each column capable of storing a decimal digit. As the decimal digit is represented in BCD code, there are four relays in each column, which may be called "8," "4," "2" and "1" relays of a column. Each relay storage unit is identified by a three-decimaldigit number, which may appear in the "r" subfield of any IN/OUT field. The digit in units place is the number of the relay storage set containing that unit of storage. The two left hand digits form the unit identification number. Thus in relay storage set "0," the fifteen units are designated as 010, 020, 030, ..., 150; and for example, unit 159 is the 15th unit in the set 9. The code numbers for selecting relay storage units are the same as the identification numbers of these units except for certain special numbers relating to selection of relay storage units for controlling record operations. As mentioned earlier, all the numbers on an IN/OUT bus set from any source or to any receiving means are passed through ES (with the minor exception of the artificial line of sequence). Hence, when the program calls for a number to be entered into or taken out from a relay storage unit, it is necessary to refer one of the ES also, which is done by using the corresponding "b" subfield.

If only 10 column numbers are to be handled, then each storage unit can be used as a split storage device to store two numbers each with 9 digits and a sign. Right and left half of the storage unit can be reset and written independently. All these are done by plugging as has been explained in the Patent.

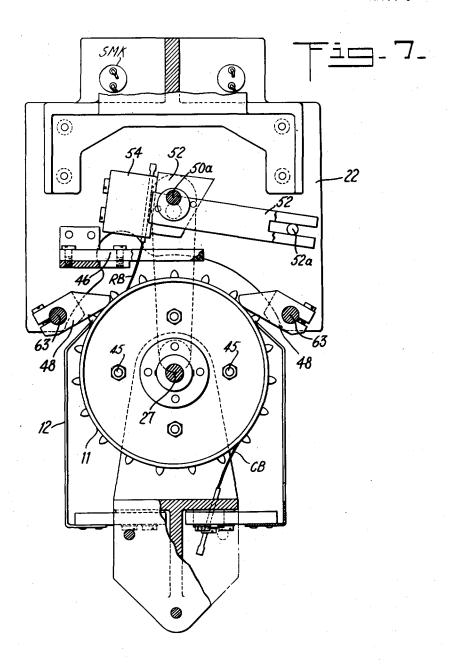

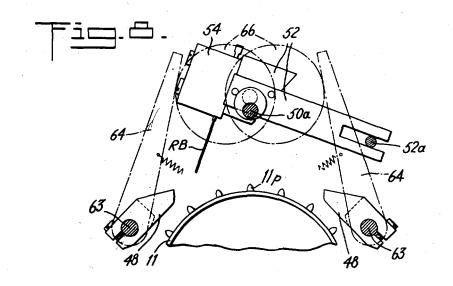

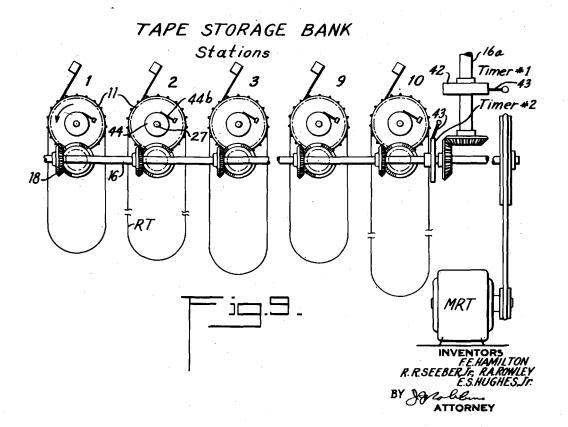

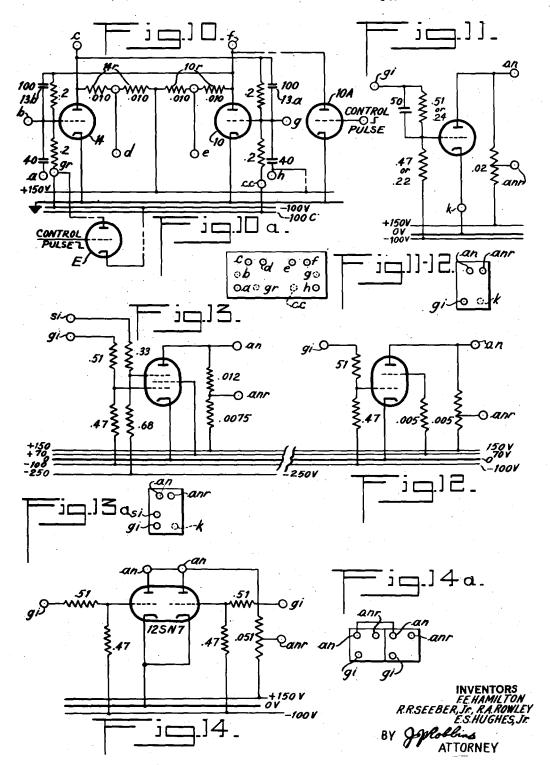

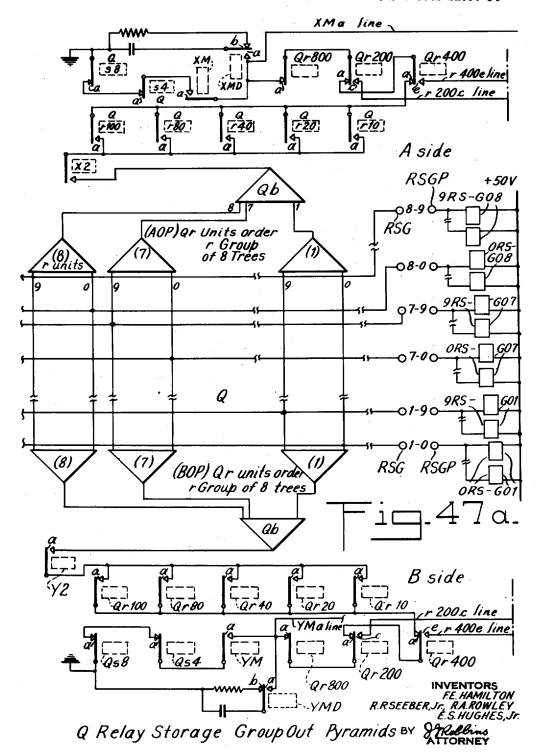

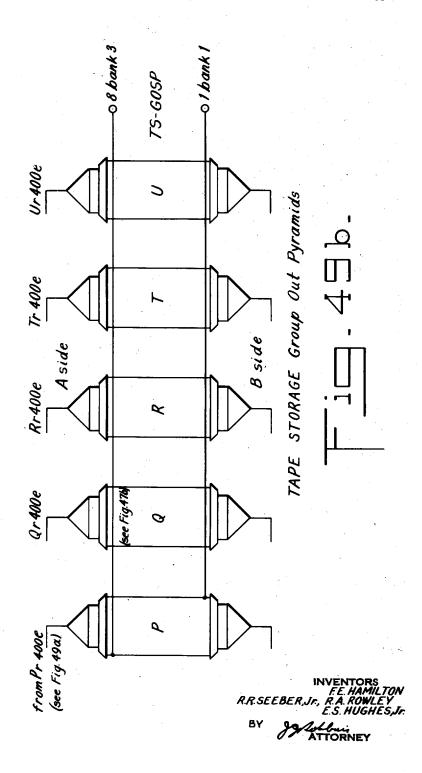

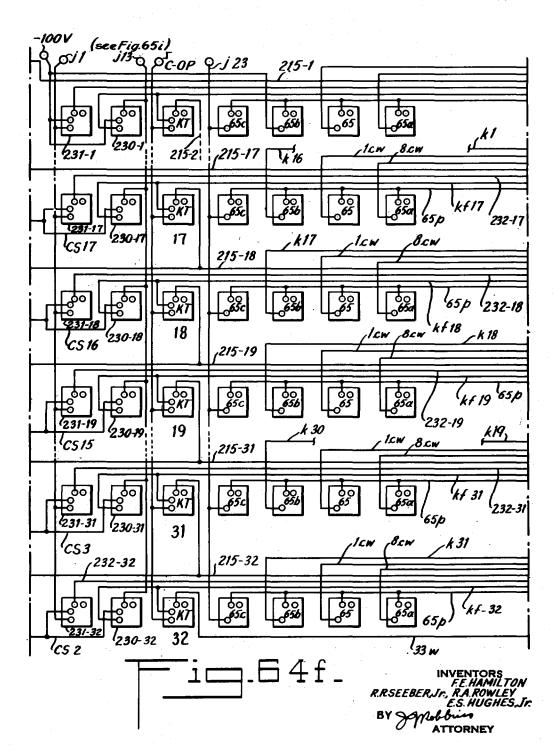

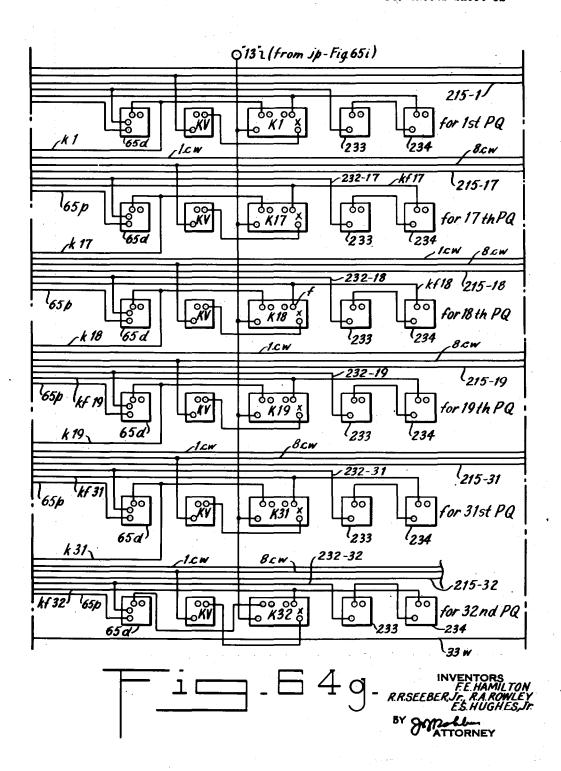

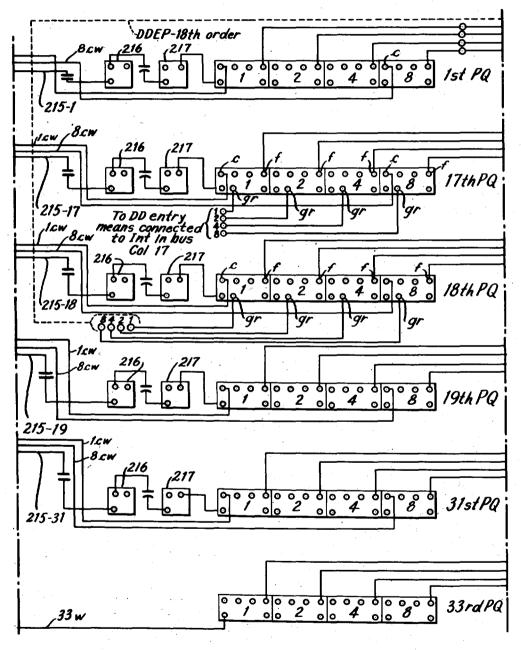

### TAPE STORAGE

Tape storage comprises three banks Nos. 1, 2 and 3, each with ten tape stations. Each bank has eight group sets associated with eight OUT bus sets 1 to 8. Selection of a unique tape storage location, therefore, requires selection of a tape storage bank and selection of one of its group outs. The selection of a bank is determined by the tape storage code number in the r subfield and selection of one of the group outs from this bank is determined by the digit in the adjacent b subfield. The code number for the tape storage stations run from 403 to 422 and 503 to 522 for bank 1; from 433 to 452 and 533 to 552 for bank 2; and from 463 to 482 and 563 to 582 for bank 3. It is clearly seen that the hundred order digit 4 or 5 identifies tape storage, and of tens order digits 0, 1, and 2 identifies bank 1, any of tens order digits 3, 4 and 5 identifies bank 2 and any of tens order digit 6, 7 and 8 identifies bank 3. The following section is not needed for programming purposes, but is included for better understanding.

# TAPE STORAGE BANK

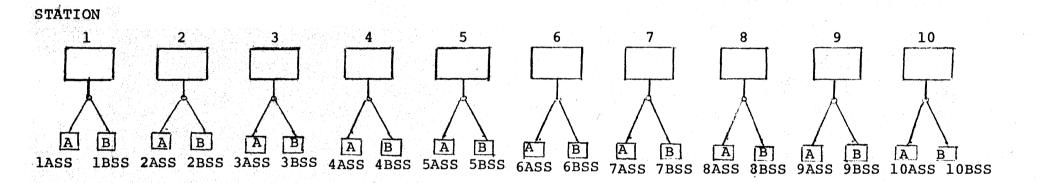

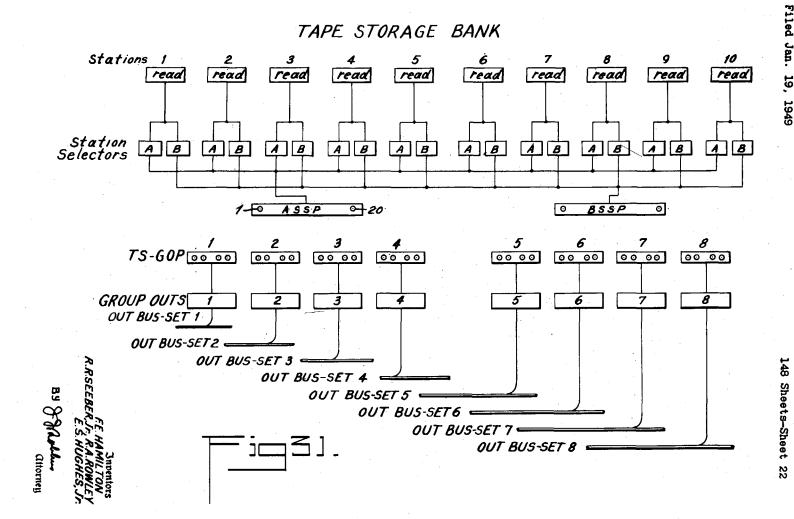

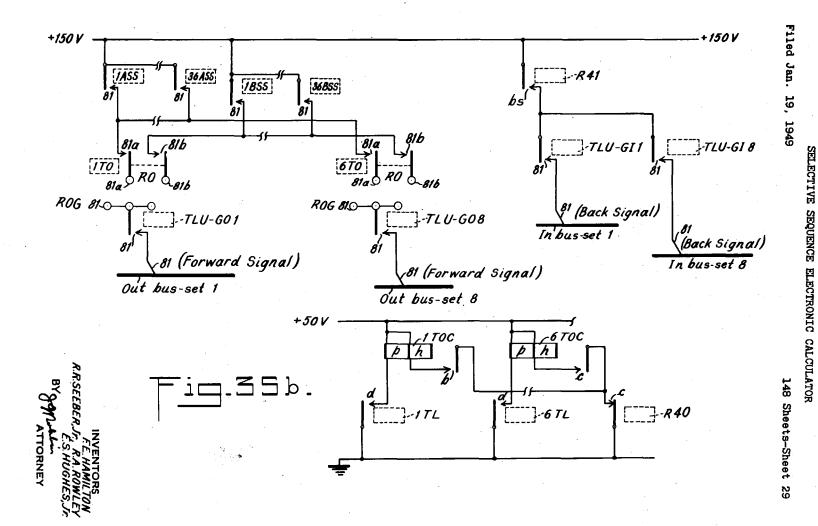

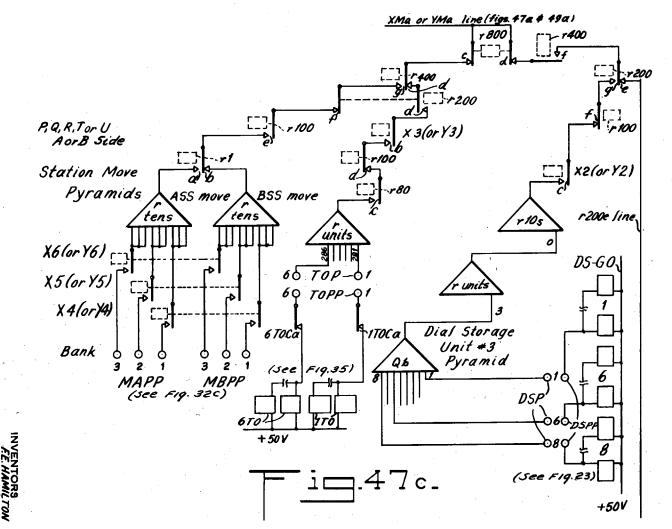

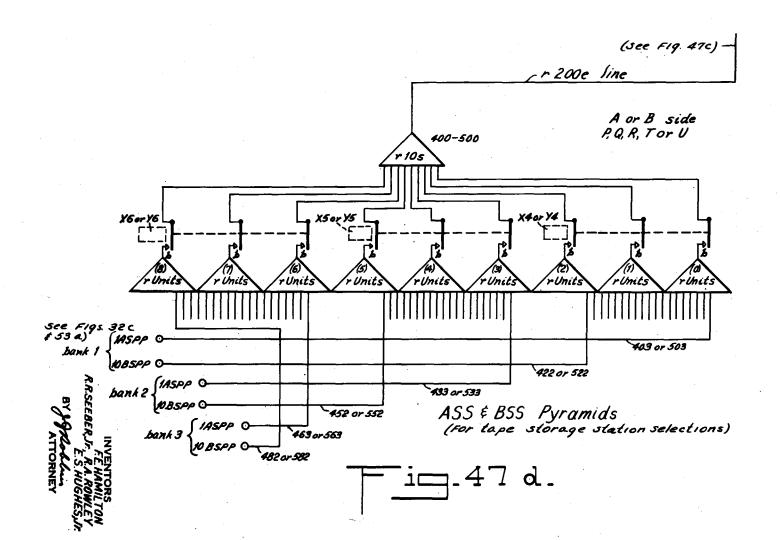

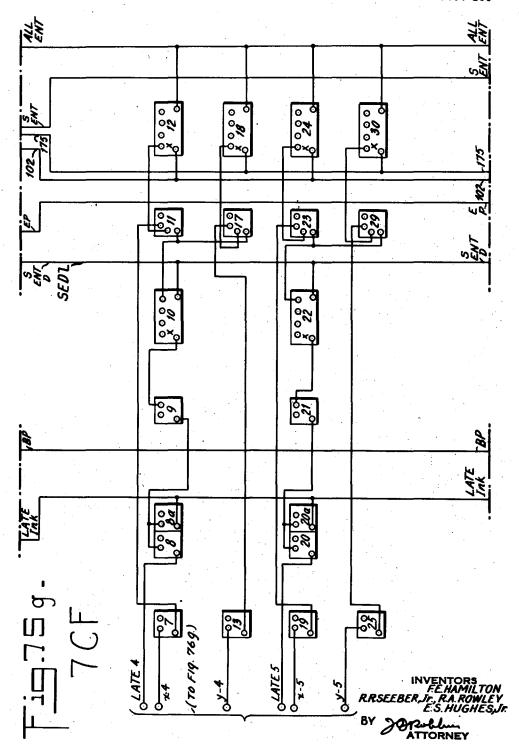

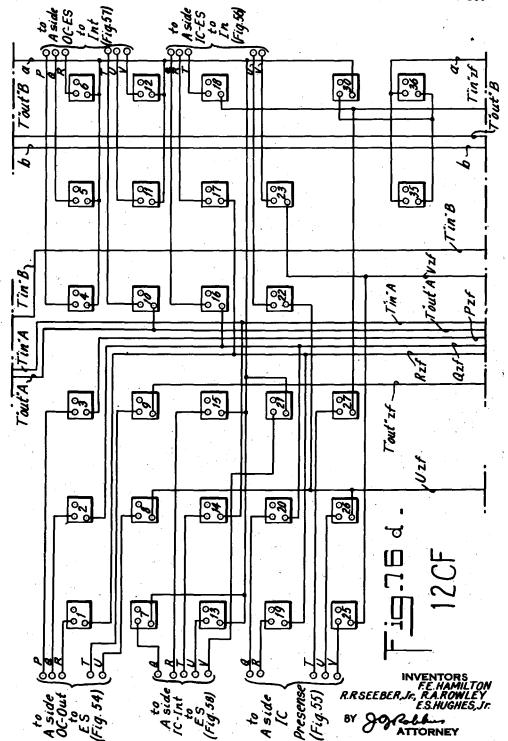

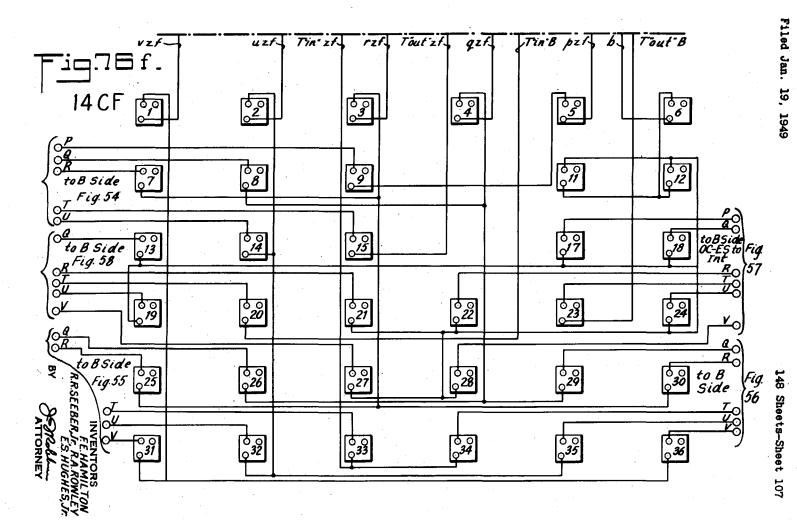

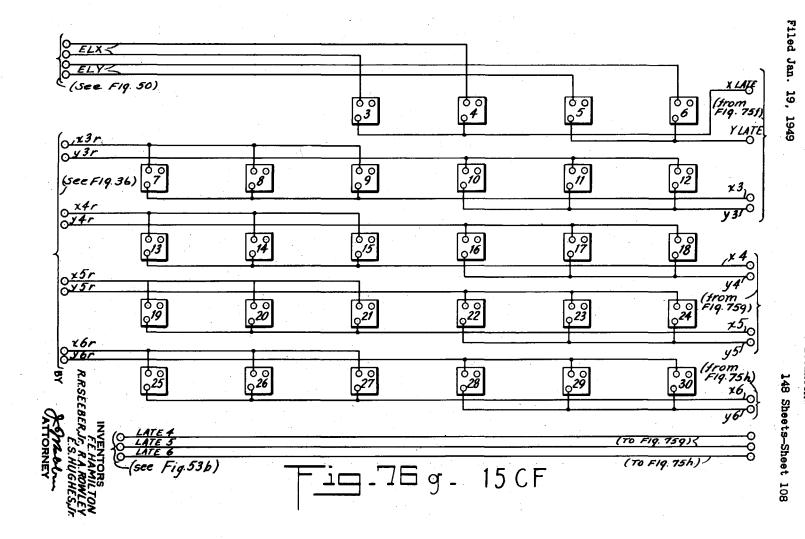

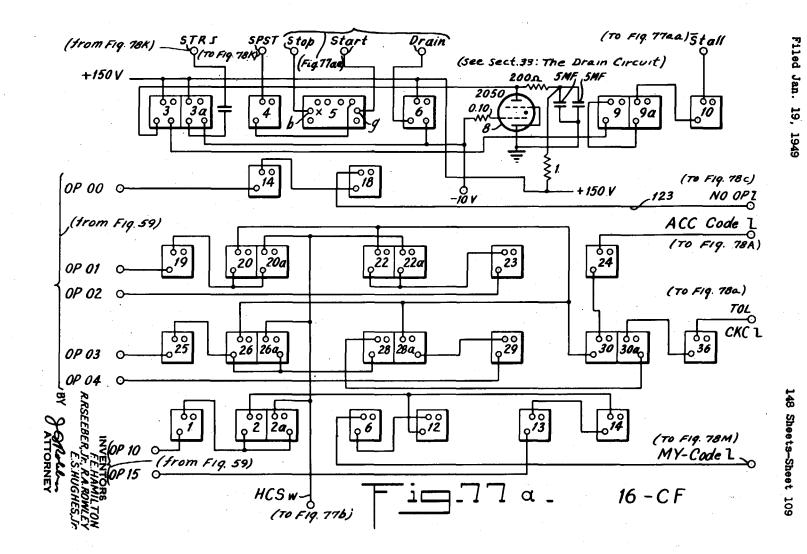

Figure 2

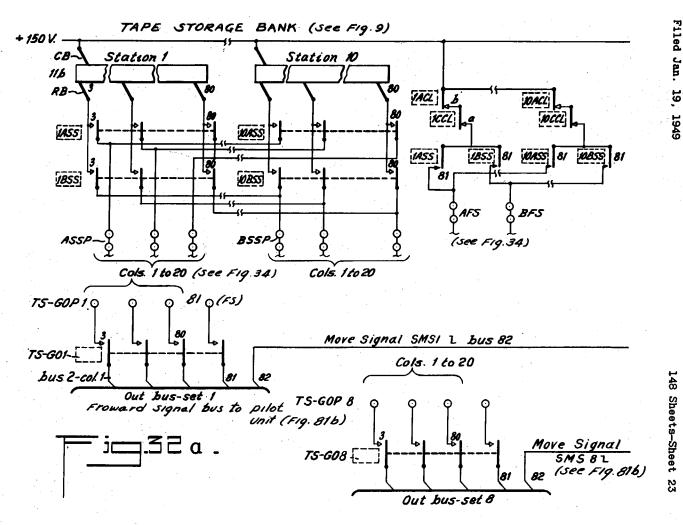

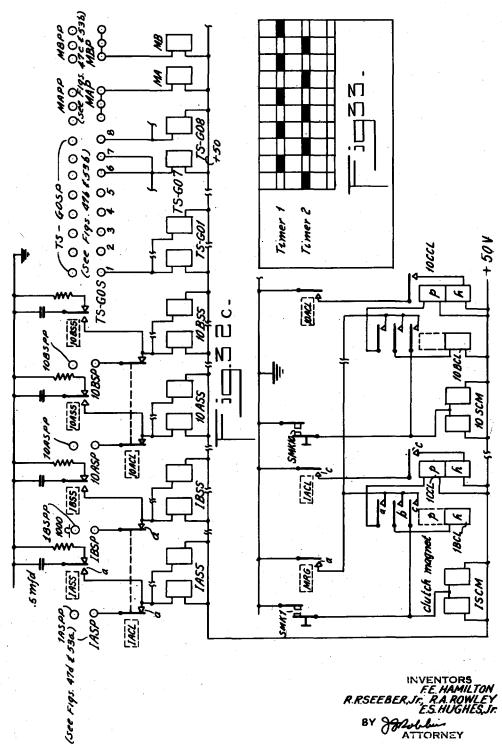

Figure 2 shows the ten tape stations in one bank. Associated with each station there are two outlets called station selector A and B. Each of the station selectors A comprise a gang relay ASS and each of the station selectors B includes a gang relay BSS. The station relays may be differentiated by a prefixed number corresponding to the associated station, e.g., relays 1ASS are associated with station 1. As there are thirty stations in all there are sixty station relays ASS and BSS. The tape storage code number calls for a particular one of these station relays. As explained before, all tape storage code numbers have 4 or 5 in their hundreds order digits. The distinction is that the hundred order digit 5 calls for the station tape to move after being read out while hundred order digit 4 calls for the station tape to remain at rest after being read out. Regardless of whether the hundreds order digit is 4 or 5, tens order digit 0, 1, 2 characterize code numbers for station relays in tape storage bank 1, tens order digit 3, 4 and 5 are in the code number for the relays in bank 2 and tens order digit 6, 7 and 8 select the relays of bank 3. Units order digits which are odd relate to relays ASS and those which are even related to relays BSS. The ten station relays in bank one identified as follows (ignoring the digit 4 and 5 in hundred order places): 1ASS by 03, 2ASS by 05, 3ASS by 07, 4ASS by 09, 5ASS by 11, 6ASS by 13, 7ASS by 15, 8ASS by 17, 9ASS by 19 and 10ASS by 21. The ten BSS relays in bank 1 are identified as follows: 1BSS by 04, 2BSS by 06, 3BSS by 08, 4BSS by 10, 5BSS by 12, 6BSS by 14, 7BSS by 16, 8BSS by 18, 9BSS by 20, and 10BSS by 22. Similarly the relays 1ASS to 10ASS of bank 2 are identified by code numbers 4 or 5 in hundreds order followed by 33 to 51 (all odds) and relays 1BSS to 10BSS in bank 2 by numbers 34 to 52 (all evens). The relays 1ASS to 10ASS in bank 3 are identified by 63 to 81 (all odds) and the relays 1BSS to 10BSS by 64 to 82 (all evens).

There are two more relays MA and MB for each bank of ten stations which, when energized, cause the tapes to move. Relay MA when energized allows any of the selected ASS relays of the bank to transmit the effect of a move signal to the related move network. Relay MB serves the same purpose in relation with the BSS relays. If the code number in the r field for a tape storage station had the hundreds order digit 4 then neither the MA nor MB

ASS is selected or relay MB will be energized if any station relay BSS is selected. Thus, there are three factors to be considered in this selection or nonselection of the move relay. One, whether the hundreds order digit is 4 or 5; another, whether the units order digit is odd or even (i.e., whether ASS or BSS relay, whether MA or MB) and finally with respect to the selection of a move relay from a particular storage bank, whether the tens order digit is in one of the three mentioned group of digits.

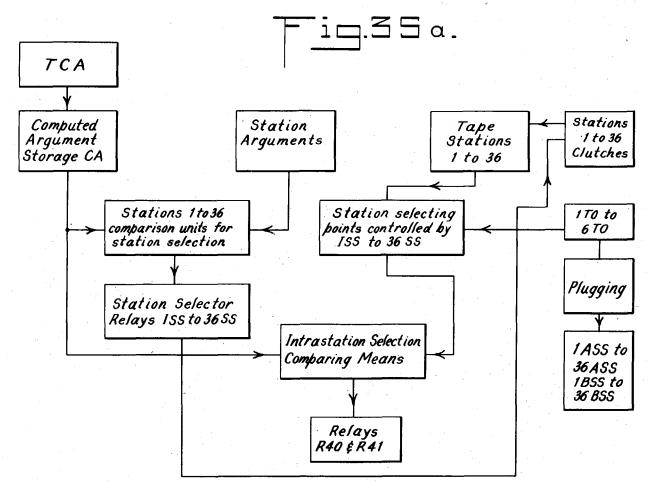

#### TABLE-LOOKUP UNIT

This unit is used to look up table values by comparing arguments punched in the tape with the computed arguments received from electronic storage units. The table lookup unit is used also to read sequence and value tapes.

This unit includes 36 tape stations which may carry tapes bearing tables of arguments and related function values. The tape argument may consist of from 1 to 5 columns of numerical digits punched in the left portion of the tape, starting with binary position 3 but not exceeding position 24. (3 and 4 contain the sign). The unit will handle up to 6 tables of one or two tape width, which can be arranged by plugs and connections. A table may consist of maximum 36 tapes in length if the table is only one tape wide, with a limitation of maximum width of 12 tapes wide.

The lookup operation is conducted by comparing the arguments portion of each successive word from tape with the computed argument. The argument selected is the last one that does not go beyond the computed argument. This determination is facilitated by the inclusion of a pair of reading stations. At that time the function value corresponding to the selected argument is available for reading out from the electronic storage unit via its associated bus.

The code for a table lookup is one of the numbers 281 to 286 in an "r" subfield. A program for this operation is:

which calls for a transfer of a computed argument from relay storage 127 to the table lookup apparatus (since 281 in "r" subfield represents Table 1) via ES1.

The selected functional value is positioned at the reading station of the selected tape unit.

During the lookup operation other computations may be performed following the above line of instruction. After such calculation, the following line may be used for reading out the selected functional values.

The selected functional value will be read out to ES1 after the execution of this line, and stored in the relay storage unit 127.

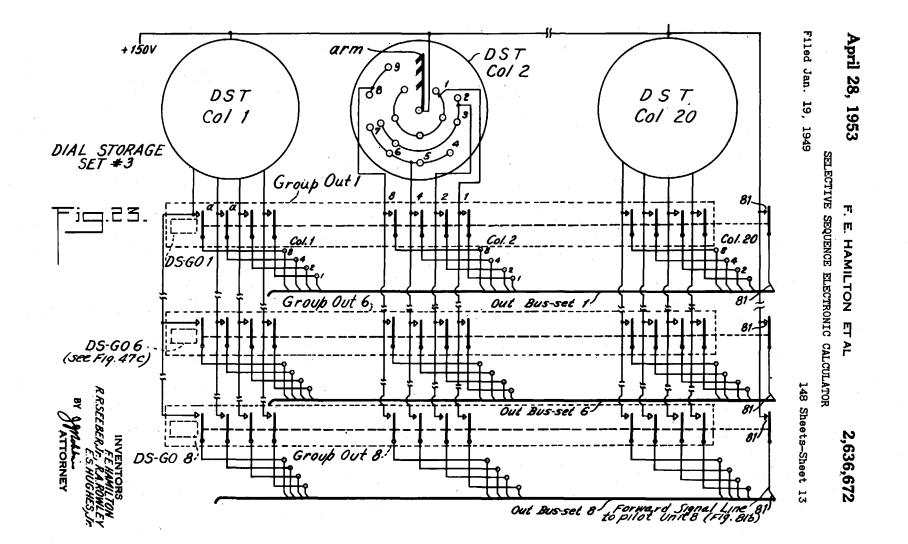

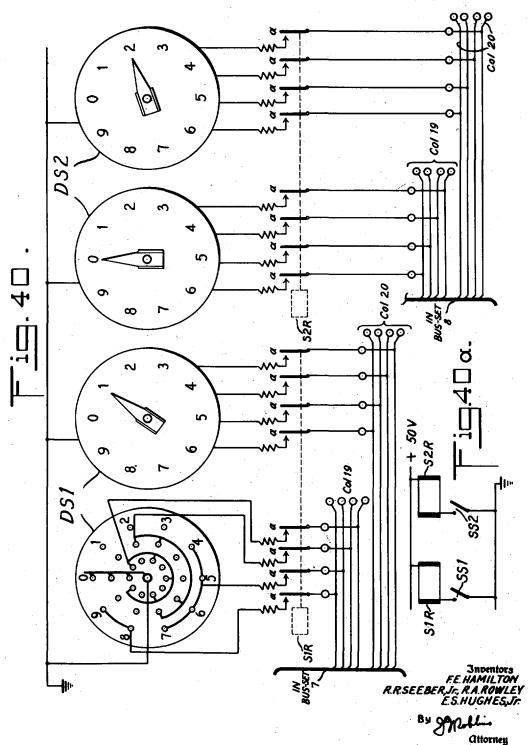

# **DIAL STORAGE**

Here, unlike all other storage, data can be set manually by the operator. A dial storage bank consists of a set of twenty dial switches named as DS1, DS2, ..., DS20. Each dial switch is manually settable to a desired decimal digit. Thus, twenty digits, i.e., a whole word, may be registered by the set of dial switches. The switches are further identifiable as column 1 to column 20 switches to conform with the numbering of the bus columns. If the code number in an r subfield is "603," it calls for a value to be read out from the dial storage unit no. 3. The corresponding subfield "b" selects the dial storage group out and electronic storage, depending on which OUT bus set is to receive the value from the dial storage.

# PLUGGABLE STORAGE

Besides the various memory storage units, the machine provides pluggable storage as a convenient means for applying constants to the OUT-bus sets to be entered in electronic storage. Several pluggable storage units are provided. Ten of these are designated by code numbers 610 to 619, which may occur in subfield r of an OUT field of a line of sequence.

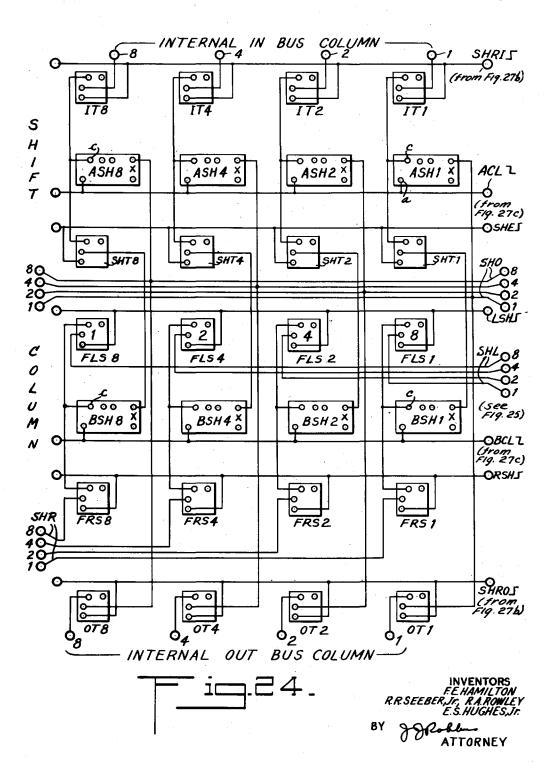

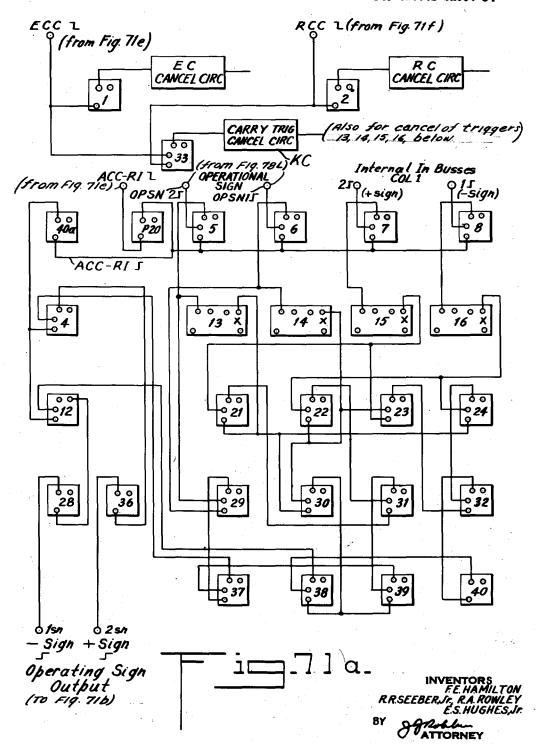

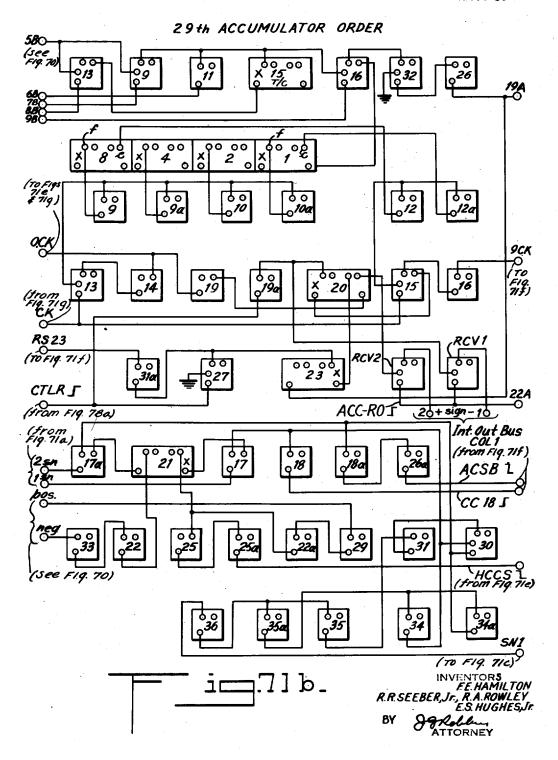

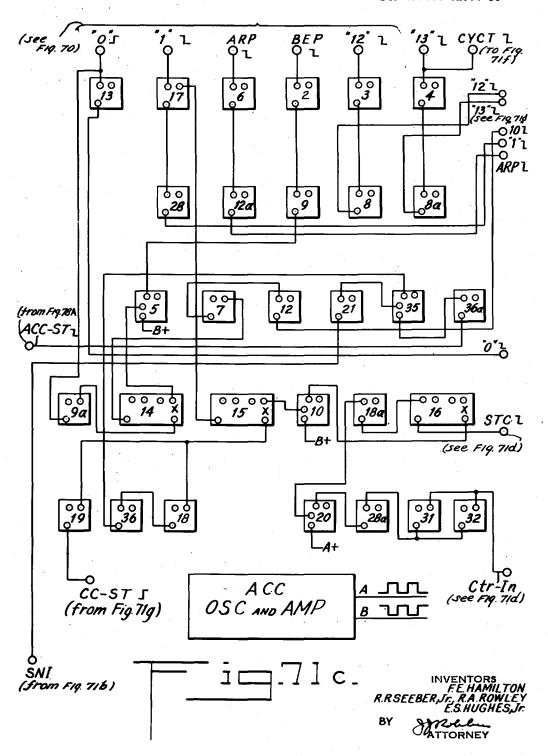

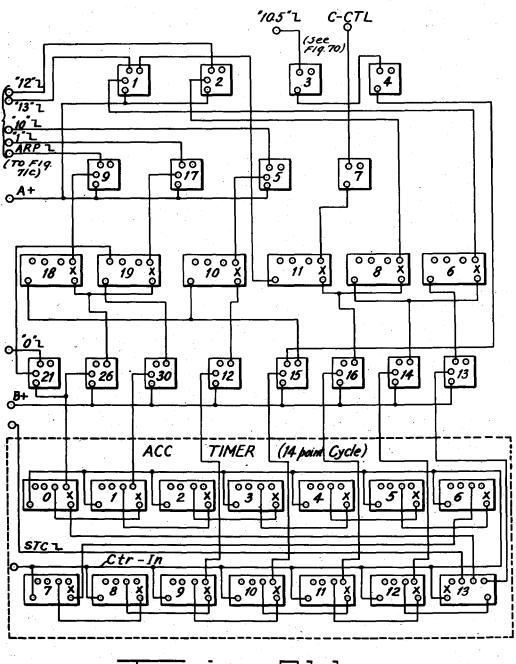

#### THE ELECTRONIC ACCUMULATOR UNIT

This is an arithmetical unit in the electronic computing section. When accumulation is called for, the accumulator unit receives numbers successively in binary coded decimal form (19 decimal digits) from the columns 11 to 29 of the internal IN bus. Along with each number, the internal IN bus set will supply the sign of the number to this unit. This unit can perform simple accumulation of positive and negative numbers. Means are also provided for rounding off up to a desired order of the result in the accumulator. The accumulator may also perform a special accumulation operation called tolerance check which will be discussed later.

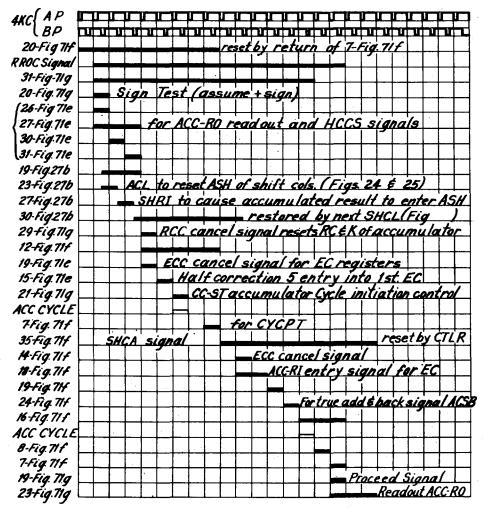

Associated with the accumulator unit is a so-called internal commutator which subsequences all the operations of the accumulator upon reception of certain signals from main sequence.

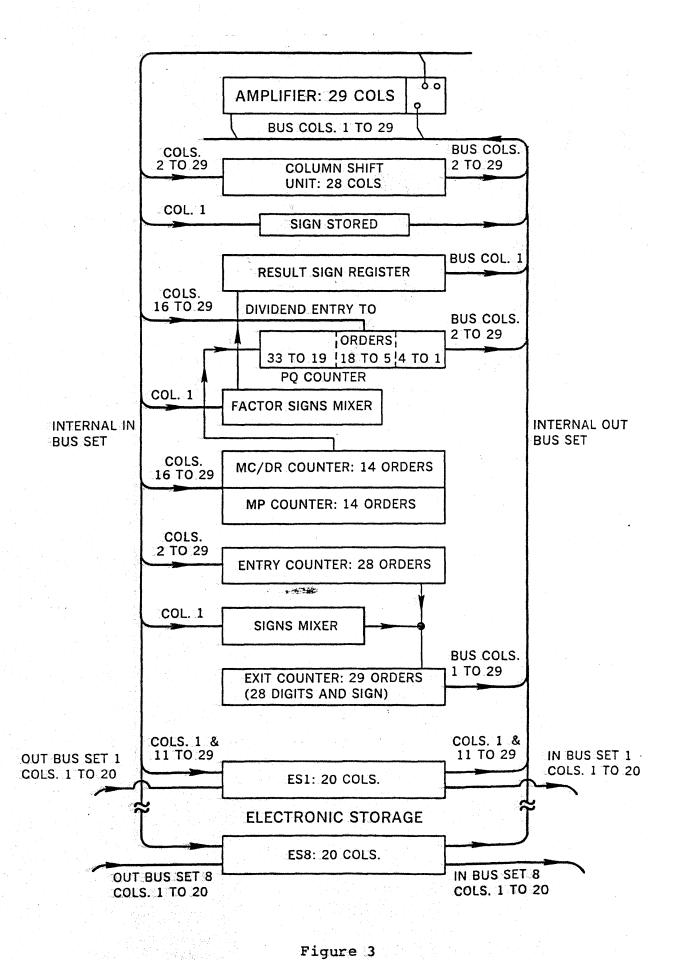

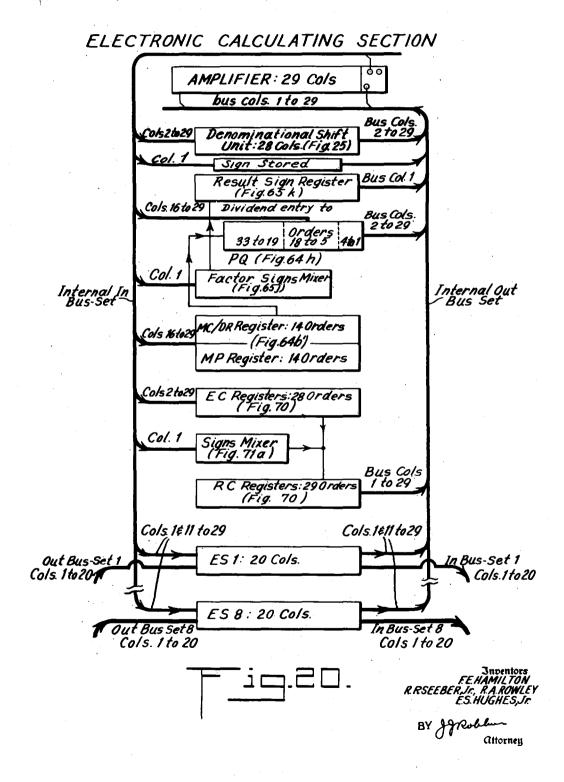

A block diagram representation of the electronic calculating circuit has been attached (Fig. 3). The accumulator has 29 orders, of which the 29th is a result sign evaluating order. The internal IN bus columns 2 to 29 are connected respectively to entry means for accumulator orders 28 to 1. However, in the present case only the bus columns 11 to 29 may carry significant digits since it is only these columns which receive digits from electronic storage. These bus columns 29 to 11 are associated with accumulator orders 1 to 19 respectively. With regard to orders 20 to 28, they will receive "0" entries from the bus columns 2 to 10. The internal IN bus column 1 which carries the algebraic sign of the number to be entered in the accumulator is connected into a "sign mixing" circuit. The outputs of orders 1 to 28 are connected to the internal OUT bus columns 29 to 2 respectively and that of the 29th order is connected to the internal OUT bus column 1 to apply the sign of the result.

The operation will consist, in general, in entering the number from the internal IN bus set into the entry registers and thereafter from there transmitting the number to the corresponding

orders of the accumulating registers. The first set of registers is called the entry counter. The second set of registers, the exit counter, comprises the accumulating device per se and its register orders are denominationally associated by carry means. Both "+" and "-" numbers may be accumulated and an albegraic sum obtained. All numbers are represented on the busses in true, binary form if the operation sign is "+." But if it is "-," then tens complement of the number in entry registers will be read out therefrom to the accumulating registers. The sign of a number and the operational sign may be 0, 1, 2 or 3, as previously explained.

#### **ACCUMULATION**

Assume a line of sequence data selected by S1 and S2 numbers is as follows:

| S1 Seq→ | Ps | Pb | Pr  | Qs | Qb | Qr  | Rs | Rb | Rr  | SH1 | OP1 | S1 |

|---------|----|----|-----|----|----|-----|----|----|-----|-----|-----|----|

|         | 2  | 1  | 010 | 2  | 2  | 011 | 4  | 1  | 030 | 0   | 02  | 16 |

| S2 Seq→ | Ts | Tb | Tr  | Us | Ub | Ur  | Vs | Vb | Vr  | SH2 | OP2 | S2 |

|         | 1  | 3  | 433 | 2  | 6  | 552 | 4  | 5  | 151 | 6   | 04  | 02 |

P is always an OUT field. The code number in this field calls for an amount to be read out of relay storage unit 010 (Pr) to OUT bus set 1 (Pb) and without a change in sign. The Q field is characterized as an OUT field by number 2 in QS and this number also specifies that the number to be read out of relay storage unit 011 (Qr) to OUT bus set 2 (Qb) is to be handled without any change of sign. The R field is characterized as an IN field by the 4 in RS which also calls for a shift to the right with a zero tens order. In its entirety, therefore, the R field calls for the result to be entered into relay storage unit 030 from accumulator via IN bus set 1 with a denominational shift to the right of zero tens order. The code number "0" in SH1 signifies the shift in units place digit will be zero. So it is clear that the denominational shift will be zero. Code number 02 in OP field calls for accumulation without half correction.

In brief, the instruction given by P, Q, R, SH1 and OP1 fields are to send numbers from relay storage 010 and 011 via electronic storage units 1 and 2, respectively, to the accumulator to be accumulated without change in sign of the numbers and without half correction and for the algebraic sum to be routed through the denominational shift unit without column shifting and then via electronic storage 1 to relay storage unit 030.

The T field is classed by 04 in OP2 as an out field. 433 in Tr calls for the number to be read from the tape at station 1 in the tape storage bank via the A outlet of this station via electron-

ic storage ES3 (Tb) and for the tape to remain at rest after the number has been read out. Ts signifies that the sign of the number is to be changed. Field U is classed as an out field by 2 in Us which signifies further that no change of sign should take place. Number 552 in Ur calls for the number to be read out of the tape at station 10 in bank 2 via the B outlet of this station through the ES6 (Ub) and for the tape to be moved after the number has been read out. Field V is always an IN field, and 4 at Vs calls for a zero tens place right shift. Digit 5 in Vb indicates that the transferred should be through IN bus set 5 via ES5. Vr represents relay storage 151 which is the 15th unit of set 1 and which is the destination of the result from accumulator. Code 04 in OP2 instructs the machine to perform accumulator, with half correction of the result.

In short, the instructions given by T, U, V, SH2 and OP2 are that the numbers from stations 1 and 10 of bank 2 be applied via their A and B outlets to out bus sets 3 and 6, respectively, to be routed through electronic storage units 3 and 6; that the tape at station 10, bank 2 be advanced after the number has been read; that the sign of the number taken from station 1, bank 2 be changed; that the result be shifted by the denominational shift unit 6 places to the right; that the half correction entry of 5 be made in the 5th order of the sum before denominational shift is completed and that the rounded off result be routed via electronic storage unit 5 to relay storage unit 151.

In the preceding example, we have seen instructions for combining pairs of numbers in one instance by addition and without half correction or shift, and in the other instance by subtraction with half correction and denominational shift of the result.

Suppose another line of sequence of data is:

| S1 Seq→ | $\mathbf{P}\mathbf{s}$ | Pb | Pr  | Qs | Qb | Qr  | Rs | Rb | Rr  | SH1 | OP1 | <b>S</b> 1 |

|---------|------------------------|----|-----|----|----|-----|----|----|-----|-----|-----|------------|

|         |                        |    |     |    |    |     |    |    |     |     |     |            |

|         | 2                      | 1  | 012 | 2  | 2  | 013 | 1  | 3  | 030 | 0   | 01  | 01         |

The code 01 in OP1 calls for accumulation without half correction of the accumulated result. The interpretation of this program sequence is as follows. A number is to be taken from relay storage unit 012 (Pr) and applied to OUT bus set 1 (Pb) without any change of sign (PS=2). A second number is to be taken from relay storage unit 013 (Qr) and applied to OUT bus set 2(Qb) without any change of sign (QS=2). A third number to be read out of relay storage unit 030 (Rr) to OUT bus set 3 (Rb) to be handled with a change in sign (RS=1). These numbers are to be entered successively to the accumulator (OP1=01). The accumulated result and sign are to be transmitted to relay storage unit 121 (Tr) via IN bus set 5 (Tb) as T field is characterized as an IN field (OP2=01).

After executing one in field (i.e., storing one result) the machine clears the accumulator and proceeds to scan the rest of the sequence. The number in relay storage unit 151 (Ur) is routed to accumulator via ES4 (Ub) with a change in sign (Us is 1). The number changed in sign is to be transmitted via the denominational shift unit without column shifting (VS=4, SH2=0) via ES1 (Vb) to relay storge unit 122 (Vr). This program shows the accumulation of three numbers and utilization of T field as an IN field. Also it shows that other operations are possible with multi word accumulation. If in this example we should use 02 for OP2 then T field would be an OUT field. In that case the terms selected by P, Q, R T (OUT field) and U fields would be accumulated and their result stored in the unit selected by V field. A single line of sequence thus may call for successive accumulation of a maximum of five numbers. If it is desired to accumulate more than five numbers, two or more lines of sequence may be used. In that case, V field of each line except the last line will be left blank and will act as a skip field. The V field of last line will be the IN field to store the result of accumulation and its sign. Obviously, any number of terms may be accumulated successively and directly in this manner.

# **MULTIPLICATION**

If the code number in OP field is 10, multiplication without half correction is called for and if it is 15, then multiplication with half correction is ordered. A maximum of two multiplications can be ordered by a complete line of sequence with each multiplication in one half lines. An example of S1 Seq. of data calling for multiplication without half correction is given below:

The above program calls for a number from relay storage unit 01 (Pr) to be sent to ES1 (Pb) and thence to the MD unit (multiplying and dividing unit) to serve as the multiplicand and for the "-" operational sign to be applied to the sign mixing circuit; for the number from storage unit 158 (Qr) to be sent to ES2 (Qb) and from there to the MD unit to serve as multiplier and for the "+" operational sign to be applied; the product to be noted through the denomination shift unit without column shifting and to ES3 (Rb) and transmitted from there to relay storage unit 139 (Rr) with the sign of the product being determined by the sign mixing network.

# XIII

### **DIVISION**

The code number 20 in the OP field calls for division without half correction which may be ordered by a half line of sequence. The code number 25 in the OP field calls for division with half correction of quotient. A sample half line of S2 Seq. for a division without half correction is,

This program instructs the machine to take the divisor from relay storage unit 151 (Tr) and direct it via ES1 (Tb) to the MD unit without sign change; to take the dividend from relay storage unit 142 (Ur) and bring it through ES2 (Rb) to the MD unit; to pass the quotient to the denominational shift unit where it shall be shifted nine places to the right (VS = 4, SH2 = 9), and to transmit the shifted quotient to ES3 (Vb) and thence to relay storage unit 136 (Vr).

# COMPUTED OR MODIFIED SEQUENCE

For some problems the course and characteristics of the calculation have no deviations, and pre-chosen program paths and instructions may be used. For other problems, the course or extent of calculations varies according to computed results and completely preselected sequence lines are not suitable. Because simple, computable numbers have been used as instructions, the lines of sequence may be computed to steer (a) the course, (b) the nature, and (c) the extent of subsequent calculation. In this section we will show an example of the first of the capabilities, computed selection of the sequence path. Let's consider a program for finding the square root of a number N using Newton's formula

$$X(NEW)=(X(OLD)+\frac{N}{X(OLD)})/2.$$

As by this time we are already familiar with the way in which accumulation, multiplication, division, etc. are accomplished in the SSEC program, we won't discuss those elaborately. Instead, the terms shown in parenthesis in the program will carry the information about calculations in progress.

|        | P                            | Q                    | R                            | SH1 OP | 1 <u>s1</u>    |   | T        | U                      | V                                   | SH2   | OP2 | S2             |

|--------|------------------------------|----------------------|------------------------------|--------|----------------|---|----------|------------------------|-------------------------------------|-------|-----|----------------|

| s<br>2 |                              | b r<br>2 6 128<br>N  | s b r<br>4 2 032<br>(N/X(0)) | 8 2    | 5 22           |   | b r<br>2 | s b r<br>2 5<br>(X(0)  | s b r<br>4 3 033<br>+N/X(0))        |       | 02  | 21             |

| 2      | 3 (X(0)                      | 2 4 614<br>+N/X(0))/ | 4 5 129<br>'2=X(N)           | 1 1    | 5 22           | 0 | 0        |                        | 4 1 100<br>10 <sup>5</sup> =t (tole |       |     | 21             |

| 2      | 5<br>(X(N)-X(0)              |                      | 4 2 034<br>erence)           | 0      | 2 22           | 2 |          | 3 2<br>d)='+' or '     | 6 3 157                             | 9     | 02  | 21             |

| 2      | 5 157 2<br>(27 <u>+</u> 5) = |                      | 4 1 152                      | 0      | 2 22           | 2 |          | 2 5<br>+5)=31 or 2     | 4 4 153                             | -<br> | 02  | 21             |

|        |                              |                      |                              |        | 32<br>or<br>22 |   | (X       | 2 5 129<br>(N) goes to | 4 5 031<br>unit 031)                |       | 02  |                |

|        |                              |                      |                              |        |                |   |          |                        |                                     |       |     | 31<br>or<br>21 |

X(0)=X(OLD) is the first guessed square root which is preliminarily put into storage unit 031. The first calculated approximation of square root X(N) is to be used to obtain tolerance. Tolerance is computed in the second half of the second line by dividing X(N) by 105, which is equivalent to shifting it five places to the right. The second half of 3rd line computes (t-d) and shifts the result to the right, 19 places to discard the numerical value of the result and to leave the sign only, which is enough information to know whether the computed value is less or greater than the tolerance. The "+" or "-" sign is transmitted from ES3 to column 1 of relay storage unit 157, which has been preliminarily plugged so that its two halves will be reset and receive data independently. The constant 5 is preliminarily entered in the right hand column of the right half of storage unit 157 through pluggable storage. Hence standing in 157 is +5. Pluggable storage has been preliminarily set to apply the number 27 to out bus set 3. The Q field of the 4th line of sequence does that. The same half of the 4th line does the accumulation of +5 and 27 and transmits the result 32 or 22 in relay storage unit 152 during the execution of the R field. During the execution of the second half of the 4th line number, 26 is directed from pluggable storage to the ES2 and hence to the accumulator after which  $\pm 5$ , which was buffered in ES5 by unit 157, is applied to the accumulator and the result 31 or 21 is transmitted in relay storage unit 153.

Now present in relay storage units 152 and 153 are computed S1 and S2 numbers. The output hubs 52 and 53 of S1 and S2 pyramid are preliminarily plugged to relay storage hubs 152 and 153, respectively. During the execution of the 5th line of sequence, therefore, the next computed line of sequence is called out from relay storage 152 and 153 and transmitted to sequence storage. The computed line of sequence just transmitted comprises S1 and S2 numbers 32 and 31 respectively, if the first calculated approximation X(N) and the first guess X(0) do not differ from each other by more than "t." This means the square root of N has been calculated to the required degree of accuracy so the main sequencing path may be resumed for the continuation of the main calculation. On the other hand, if the computed S1 and S2 numbers are 22 and 21, i.e., the difference d is greater than the tolerance t then the

iteration sequence is repeated. During the execution of the 2nd half of the 5th line the first calculated square root X(N) is transmitted from unit 129 to unit 031 and so has replaced the first guess for the next iteration sequence.

In this manner the above loop can be run as many times as necessary to obtain a square root with required accuracy and when it has been obtained, the computed S1 and S2 numbers will be 32 and 31 and will direct the calculation into the main path. Besides the modification of sequence codes, other modifications of the program through computation are possible. These include, for example, computed operation code, shift code, address code (any of the six "r" subfields), bus code, operational sign code. An example of each of these has been given in the SSEC patent.

#### **TOLERANCE CHECK**

This check ordinarily serves for checking the accuracy of computations. programming, the same computation is done by two different methods and the results are stored and later brought to the accumulator -- one as a negative and one as a positive number -- so that accumulator can obtain the difference, if any, between the two computation results. This difference is then read out of the accumulator and re-entered therein as a negative absolute number. The main sequence then selects the source for a tolerance number which is usually set up in dial storage no. 3. This tolerance number is the allowable difference between the results of two computations of a particular problem. This number is entered into the accumulator unit as a positive number. If the tolerance number is less than the difference between the two computations, then the result of the comparison is negative and out of tolerance, and machine operation is interrupted. If the tolerance number is equal to or greater than the difference between the two computations then the result is positive and the scanning of sequences is continued. In other words, if the 29th order of the accumulator is at "0," then the algebraic sum of two numbers sent to the accumulator is positive, hence, in present case the program continues, but if the 29th order is at "9," then it is negative and program is interrupted. An illustrative line of sequence ordering an answer tolerance check is given below:

| S1 Seq. | Ps | Pb | Pr  | Qs | Qb | Qr  | Rs | Rb | Rr | SH1 | OP1 | S1        |

|---------|----|----|-----|----|----|-----|----|----|----|-----|-----|-----------|

|         | 2  | 3  | 016 | 1  | 2  | 137 | 4  | 1  |    | 0   | 02  | 01        |

| S2 Seq. | Ts | Tb | Tr  | Us | Ub | Ur  | Vs | Vb | Vr | SH2 | OP2 | <b>S2</b> |

|         | 2  | 6  | 603 | 3  | 1  |     | 4  |    |    | 0   | 03  | 02        |

S1 Seq. calls for the answer relay storage unit 016 (Pr) to be sent via electronic storage unit ES3 (Pb) to the accumulator unit to be acted on without a change in sign (Ps is 2); the

answer in relay storage unit 137 (Qr) to be brought via electronic storage ES2 (Qb) to the accumulator unit to be subtracted (Qs is 1; which implies "-" sign of the number) from the number previously accumulated, and the difference will be stored in electronic storage unit 1 (Rb), because R field is an IN field (Rs is 4). The S2 Seq. of the above line calls for the tolerance number, which is set from the outside to be read out (OP2 is not 01, hence T is OUT field) of dial storge unit no. 3 (Tr is 603) and via ES6 to the accumulator unit to be handled without a change of sign; the answer difference in electronic storage unit 1, (Ub is 1) which was stored there by R field to be sent to the accumulator unit to have its absolute value subtracted (Us is 3) from the tolerance number and the proceed signal will be produced (Vs is 4), if the tolerance check (required code is 03 at OP2) finds the answer difference to be equal to or less than the tolerance number.

The tolerance check can be used for some other purposes. For instance, it can be used to stop computations, when a table of f(x) has been computed between the limits of +0.001 and 0.0075. To check the upper limit, the tolerance number +0.0075 may be used and f(x) value is subtracted therefrom, and to check the lower limit the number -0.001 is added to each f(x) value. This check may be made after each computation of f(x). The line of sequence is:

| S1 Seq. | Ps | Pb | Pr  | Qs | Qb | Qr  | Rs | Rb | Rr | SH1 | OP1 | <b>S</b> 1 |

|---------|----|----|-----|----|----|-----|----|----|----|-----|-----|------------|

|         | 16 | 1  | 012 | 1  | 2  | 013 | 4  |    |    | 0   | 03  | 01         |

| S2 Seq. | Ts | ТЬ | Tr  | Us | Ub | Ur  | Vs | Vb | Vr | SH2 | OP2 | S2         |

|         | 2  | 3  | 014 | 2  | 2  |     | 4  |    |    | . 0 | 03  | 02         |

The upper tolerance value +0.0075 is in relay storage unit 012 (Pr) and the lower tolerance value -0.001 is in relay storage unit 014 (Tr). The value of f(x) obtained from the last computation is in relay storage unit 013 (Qr). As the code for both OP1 and OP2 is 03, the tolerance check means will be used in both half of scanning sequence. At the first of calculating steps the entry of upper tolerance limit into ES1 (Pb), the value of f(x) into ES2

(Qb) and the lower tolerance limit into ES3 (Tb) will be made from corresponding relay storage. In the second step, the upper limit is transferred from ES1 to the accumulator without any change in the sign (Ps is 2) and the value of f(x) will be transferred from ES2 to accumulator with a change in sign (Qs is 1). This change in sign of one of the two numbers being sent to the accumulator, causes the subtraction. If the value of f(x) is equal to or less than the upper tolerance limit in the result of the accumulation or the number in accumulator is positive then proceed signal will be generated. If check result is negative then the scanning sequence will stop. Assuming as above, the value of f(x) is less than the upper tolerance, then the program will start the second half of the scanning sequence. First step of this half that the accumulator will be cancelled and the previous values will be cleared, then the lower tolerance limit will be transferred from ES3 to the accumulator without any sign change. If the value of f(x) is not smaller than +0.001, then the addition of this value to the lower tolerance number -0.001 will produce a positive number, otherwise negative. During the scanning of V field, the result of the second check will be tested and proceed signal will be generated if the test result is positive.

# HALF CORRECTION

The number of digits in the product is either equal to or one less than the sum of the digits in the multipliers and multiplicand factors. The rounding off of a result is called for only in connection with a column shift to the right. The number of digits to be discarded is equal to the column shift to the right. The product may be a maximum of 28 digits (as allowed maximum number of decimal digits in both multiplier and multiplicand is 14), but the receiving unit is designed to receive a maximum of 19 digits plus the sign. Therefore, when the product is the full 28 digits, then at least 9 rightmost digits must be discarded through the operation of denominational shift. In such a case, the column shift amount will be nine and a shift to the right will be signalled for. The half correction or rounding off operation consists of adding 5 to the order of the number at the right of the rightmost digit to be transmitted through the receiving unit.

### XVII

# **PRINTERS**

Each of the two printers is capable of printing, on one line, the numbers stored in four relay storage units. For printer No. 1, the storage units are 120, 121, 122, and 123. It prints, on one line, either four 19-digit numbers with their four signs, or eight 9-digit numbers with their eight signs, depending on how these relay storage units are being used. The units may be filled in any order and printing may be called for upon filling the fourth storage unit by substituting a "6" for the "2" in the middle digit of the code number for that unit. (See Table 3.) A line of sequence calling for printing may also include one or two calculations. The printer code number will always appear in the last program field that specifies entry into relay storage units 120-123. Consider a programming example:

| S1 SEQ | Ps | Pb | Pr  | Qs | Qb | Qr  | Rs | Rb | Rr  | SH1 | OP1  | S1 |

|--------|----|----|-----|----|----|-----|----|----|-----|-----|------|----|

|        | 2  | 1  | 010 | 2  | 2  | 011 | 4  | 3  | 123 | 0   | 01   | 01 |

| S2 SEQ | Ts | Tb | Tr  | Os | Ob | Or  | Vs | Vb | Vr  | SH2 | OP2  | S2 |

|        | 0  | 4  | 121 | 4  | 5  | 122 | 4  | 6  | 160 | 0   | - 01 | 02 |

This program calls for the accumulation of the number in storage 010 and 011, the transmission of the result to storage 123, to 121 (T is an infield), to 122 and to 120 (160=120). At this point (Vr=160) when 160 is recognized, a printing cycle is called in to print numbers placed in 120, 121, 122, and 123. (This program may be used to check the relay storage unit.) Another printing program is:

| S1 SEQ. | Ps | Pb | Pr  | Qs | Qb | Qr  | Rs | Rb | Rr  | SH1 | OP1 | S1 |

|---------|----|----|-----|----|----|-----|----|----|-----|-----|-----|----|

|         | 0  | 0  | 0   | 2  | 1  | 151 | 6  | 2  | 161 | 0   | 02  | 01 |

| S2 SEQ. | Ts | Tb | Tr  | Us | Ub | Ur  | Vs | Vb | Vr  | SH2 | OP2 | S2 |

|         | 2  | 3  | 010 | 2  | 4  | 011 | 4  | 5  | 012 | 5   | 15  | 02 |

In this case, the number in relay storage unit 151 is transmitted to storage unit 121 (Rr being 161) with a shift of ten places to the right, and the printing is called into operation to print the numbers in 120, 121, 122, and 123. Here, if any of the relay storages 120-123 is blank, then the machine will print nothing for those storage. Actually this program assumes that the numbers are already present in storage 120, 122, and 123. The second half of the sequence schedules a multiplication, showing that other calculation can be performed concurrently with printing. Third example is:

| S1 SEQ. | Ps                                      | Pb | Pr  | Qs | Qb | Qr  | Rs | Rb | Rr   | SH1 | OP1 | S1 |

|---------|-----------------------------------------|----|-----|----|----|-----|----|----|------|-----|-----|----|

|         | 2 2 2 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 | 1  | 101 | 2  | 2  | 011 | 4  | 3  | ,120 | 0   | 02  | 01 |

| S2 SEQ. | Ts                                      | Tb | Tr  | Us | Ub | Ur  | Vs | Vb | Vr   | SH2 | OP2 | S2 |

|         | 2                                       | 4  | 121 | 2  | 5  | 122 | 4  | 6  | 163  | 0   | 10  | 02 |

The first half of the program calls for addition of the numbers in storage unit 010 and 011 and entry of the sum in 120. The second half calls for the multiplication of the numbers in 121 and 122 and entry the product into 123 (vr=163). Since, Vr is 163, the sum is 120, the factors in 121 and 122 and the product in 123 will all be printed on the same line.

Comment - One discrepancy is that whenever the program calls for printing the contents of 120-123, all are printed. No one of them can be printed individually.

### XVIII

### OTHER INPUT/OUTPUT DEVICES

The input data for the SSEC is entered in two ways, by punched cards or by punched tapes. There are two card readers each of which reads 200 eighty column cards in a minute. There are two types of coding provided for read out of data from cards, one that causes a read out followed by a card feed operation and one that causes only read out. The card readers deliver the numbers from the cards they read to memory units 150-154 for Reader No. 1 and 155-159 for Reader No. 2. If only one number is to be read from a card then the other four memory units for that card reader are available for normal relay memory use. When certain numbers are required repeatedly in the course of a problem or at very close intervals or in great numbers, a tape is automatically prepared in advance by means of an auxiliary reproducing punch which is arranged to read 300 cards and punch 300 lines of tape a minute. The punching done by this unit is checked in the same operation to give complete assurance of true copy of the card data on the tape. The tapes may be placed on any of the 66 tape reading stations (as described in Section VI). The data from the tape are read into the calculator directly over the main buses without the aid of special relay memory units. The operation and codes for addressing for tape reading have been described in the tape storage section (Section VI).

When intermediate or final results or data are to be delivered as an output, they are supplied to the user in three ways, by printing, by punched cards and by punched tapes. The relay storage units and corresponding address codes for printing have been discussed in the printing unit section (Section XVII) for Printer No. 1. Similar coding applies for printer no. 2, but the corresponding relay storage units are 126-129. Even if only one number is to be printed, the other three storage units corresponding to that printer cannot be used as normal relay storage units while printing continues. The numbers stored in punched cards are usually final results. Eighty column cards may be punched at the rate of 100 a minute on any of the

two card punches. Four pairs of relay memory units are associated with each punch. Each pair of relays is used in an alternating mode to be described shortly. When more than one pair of memory unitd are used, the entry of the last number before punching is done by a sequence code that directs the unit to store and also initiates the operation of the punch. Results to be punched on cards are placed in memory units 130-133, 136-139, 140-143 and 146-149. The numbers which are punched in paper tapes on one of the three tape memory units are sent to designated relay memory units associated with each of the tape units, namely units 134 and 144; 135 and 145; 115 and 125 for tape units no. 1, no. 2 and no. 3, respectively. The instruction to store in a tape memory unit causes the tape punch on the tape unit to operate after the number has been stored in one of the two alternate relay memory units. While a number is being punched, the correct punching of the previous number is being checked against the number standing in the alternate memory unit.

Thus, as we see from the above discussion, 40 units (16 units for card punch, 6 units for tape punch, 8 units for printers and 10 units for card readers) out of 150 relay storage units are used as auxiliary storage in connection with the input and output devices of the SSEC. The rest of 110 relay storage units are solely memory units. Of course, those forty units can also be used as memory, if programmed accordingly. Whether they will be used as normal memory, or for input/output transfer is established by programming, using the sequence codes given in table No. III.

| SEQUENCE     | FIELD       | SUB<br>FIELD<br>(DIGITS) | VALUES       | INTERPRETATION                                                                                                                                |

|--------------|-------------|--------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

|              |             |                          | 0            | Operational Fixed Positive sign.                                                                                                              |

|              |             | s                        | . 1          | Inversion in the original sign.                                                                                                               |

| *            | 1           | (1/2)                    | 2            | No change of sign.                                                                                                                            |

|              | 1           | (-, -,                   | 3            | Operational fixed negative sign.                                                                                                              |

|              | P           |                          | 0            | Corresponding field to be skipped                                                                                                             |

|              | (only       | . Р                      | 1-8          | Electronic storage unit and corresponding in/out bus                                                                                          |

|              | out         | (1)                      |              | set (for in/out field)                                                                                                                        |

|              | field)      |                          |              | Destination/source (for in/out field, as applicable) of                                                                                       |

|              |             | r                        | -            | data or program word in storage including relay storag                                                                                        |

|              | 1           | (3)                      |              | dial storage, tape storage, pluggable storage and table                                                                                       |

|              | <u></u>     | L                        |              | look-up unit. (See Table No. 2)                                                                                                               |

|              |             | 1                        | 0-3          | Same as Ps, in addition, any of them characterize the                                                                                         |

|              |             | ļ .                      |              | field as an out field                                                                                                                         |

|              | 1           |                          | 4            | The field is an in field and a shift to the right with a                                                                                      |

|              | 1           |                          |              | tens order shift of '0'                                                                                                                       |

|              | 1           | ·                        | 5            | The field is an in field and a shift to the left with a tens order shift of '0'                                                               |

| LEFT         |             |                          | 6            | The field is an in field and a shift to the right with a                                                                                      |

| LEFT<br>HALF | Q           | s<br>(1)                 | U            | tens order shift of '1'                                                                                                                       |

| HALF         | (both       |                          | 7            | The field is an in field and a shift to the left with a                                                                                       |

|              | out         |                          | . '          | tens order shift of '1'                                                                                                                       |

|              | and in      |                          | 8            | The field is an in field and a shift to the right with a                                                                                      |

|              | field)      |                          | ū            | tens order shift of '2'                                                                                                                       |

|              | 110.07      |                          | 9            | The field is an in field and a shift to the left with a                                                                                       |

|              | 1           |                          |              | tens order shift of '2'                                                                                                                       |

|              | •           | b(1)                     | 0-8          | Same as Pb                                                                                                                                    |

|              |             | r(3)                     | · -          | Same as Pr                                                                                                                                    |

|              | <del></del> |                          | <del></del>  |                                                                                                                                               |

| •            | R           | s(1)                     | 0-9          | Same as Qs (see note below)                                                                                                                   |

|              | (both       | b(1)                     | 0-8          | Same as Pb                                                                                                                                    |

|              | out and     | r(3)                     | -            | Same as Pr                                                                                                                                    |

|              | in field)   |                          |              |                                                                                                                                               |

|              |             |                          |              |                                                                                                                                               |

|              | SH1(        | <u>D</u>                 | 0-9          | Units order of column shift                                                                                                                   |

|              |             |                          | 00           | No operation of the accumulator                                                                                                               |

|              |             |                          | 01           | Accumulation without half correction                                                                                                          |

|              |             |                          | 02           | Accumulation without half correction                                                                                                          |

|              | OPI         | (2)                      | 03           | Tolerance check                                                                                                                               |

|              |             |                          | 04           | Accumulation with half correction of the sum                                                                                                  |

|              |             |                          | 10           | Multiplication without half correction                                                                                                        |

|              |             | · 1                      | 15           | Multiplication with half correction of the product                                                                                            |

| ,            |             |                          | 20           | Division without half correction                                                                                                              |

|              | 61/2        |                          | 25           | Division with half correction of the quotient Source for the next left half line of sequence data                                             |

|              | S1(2        | ·                        | <del>-</del> | Source for the next left han line of sequence data                                                                                            |

|              | T*          | s(1/2)                   | 0-3          | Same as Qs (see note below)                                                                                                                   |

|              | (both in    | b(1)                     | 0-3          | Same as Pb                                                                                                                                    |

|              | and out     | r(3)                     |              | Same as Pr                                                                                                                                    |

|              | field)      | .(3)                     |              |                                                                                                                                               |

|              |             |                          |              |                                                                                                                                               |

|              | U           | s(1)                     | 0-9          | Same as Qs (see note below)                                                                                                                   |

|              | (both in    | b(1)                     | 0-8          | Same as Pb                                                                                                                                    |

| RIGHT        | and out     | r(3)                     | - ,          | Same as Pr                                                                                                                                    |

| HALF         | field)      |                          |              | N                                                                                                                                             |

|              |             | S(1)                     | 0-3          | Not used, as they are not necessary, (see note below)                                                                                         |

|              | V           |                          | 4-9          | Same as Qs with an exception that this field is always                                                                                        |

|              |             |                          |              | an in field                                                                                                                                   |

| 1            | (only in    | b(1)                     | 0-8          | Same as Pb                                                                                                                                    |

|              | field)      | r(3)                     |              | Same as Pr<br>Same as SH1                                                                                                                     |

|              | SH2         | U                        | 0-9          | Same as OP1 with an exception only when the code is                                                                                           |

|              |             |                          | •            | Same as Or I with an exception only when the code is                                                                                          |

|              | 000         | (2)                      |              | I O I which characterizes T field as an in field                                                                                              |

|              | OP2         | (2)                      |              | 01, which characterizes T field as an in field.                                                                                               |

|              | OP2         |                          | <u> </u>     | O1, which characterizes T field as an in field.  In all other cases T field is an out field.  Source for the next right half line of sequence |

<sup>\*</sup> See interpretation of field OP2.

Note: As the sign of result is already determined, digits 0-3 are invalid in 's' subfield of any in field.

| Type<br>of<br>Storage     | Code<br>Number    | INTERPRETATION OF CODE NO.                                                                                                     |                                                                           |  |

|---------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--|

| Relay<br>Storage<br>(1)   | 010-<br>159       | Units digit identifies one of the ten sets of relay storage units. The two left digits distinguish one of 15 units in the set. |                                                                           |  |

| Table<br>Look-up<br>Unit  | 281 to<br>286     | Address of Table 1-6 respectively.                                                                                             |                                                                           |  |

|                           | 4**<br>5**        | Station tape remains at rest after being read out.  Station tape is to be moved after read out.                                |                                                                           |  |

| ТАРЕ                      | *0*<br>*1*<br>*2* | IDENTIFIES BANK 1                                                                                                              | ODD UNITS ORDER DIGITS<br>RELATE TO ASS RELAYS,<br>EVEN UNITS ORDER DIGIT |  |

| STORAGE *3*<br>*4*<br>*5* |                   | IDENTIFIES BANK 2                                                                                                              | RELATES TO BSS RELAYS.                                                    |  |

| (2)                       | *6*<br>*7*<br>*8* | IDENTIFIES BANK 3                                                                                                              |                                                                           |  |

| Dial<br>Storage           | 603               | Address of dial storage no. 3                                                                                                  | (3)                                                                       |  |

| Pluggable<br>Storage      | 610 to<br>609     | Address of ten units of pluggable storage.                                                                                     |                                                                           |  |

- (1) For special use of relay storage, see Table 3.

- (2) See Section VI also.

- (3) Dial storage no. 1 and no. 2 are used for artificial line of sequence.

TABLE 2

INTERPRETATION OF STORAGE CODES

| I/O DEVICE            |                                         | CODES USED      |                                 |                               |

|-----------------------|-----------------------------------------|-----------------|---------------------------------|-------------------------------|

|                       | NORMAL<br>RELAY<br>STORAGE<br>OPERATION | I/O<br>TRANSFER | ALTERNATI<br>NO I/O<br>TRANSFER | NG STORAGE<br>I/O<br>TRANSFER |

| 1. CARD READER #1     | 150 - 154                               | 170 - 174       |                                 |                               |

| 2. CARD READER #2     | 155 - 159                               | 175 - 179       |                                 |                               |

| 3. CARD PUNCH #1      | 130 - 133<br>140 - 143                  |                 | 180 - 183                       | 190 - 193                     |

| 4. CARD PUNCH #2      | 136 - 139<br>146 - 149                  |                 | 186 - 189                       | 196 - 199                     |

| 5. TAPE READERS: AS C | GIVEN IN SECTIO                         | N VI AND TAI    | BLE 2.                          |                               |

| 6. TAPE PUNCH #1      | 134<br>144                              |                 |                                 | 194                           |

| 7. TAPE PUNCH #2      | 135<br>145                              |                 |                                 | 195                           |

| 8. TAPE PUNCH #3      | 115<br>125                              |                 |                                 | 185                           |

| 9. PRINTER #1         | 120 - 123                               | 160 - 161       |                                 |                               |

| 10. PRINTER #2        | 126 - 129                               | 166 - 169       |                                 |                               |

TABLE 3

CODES FOR SPECIAL USES OF RELAY STORAGE AS I/O BUFFER

0 000 0

10 11 12 13 14 15 16 17 18 19 20

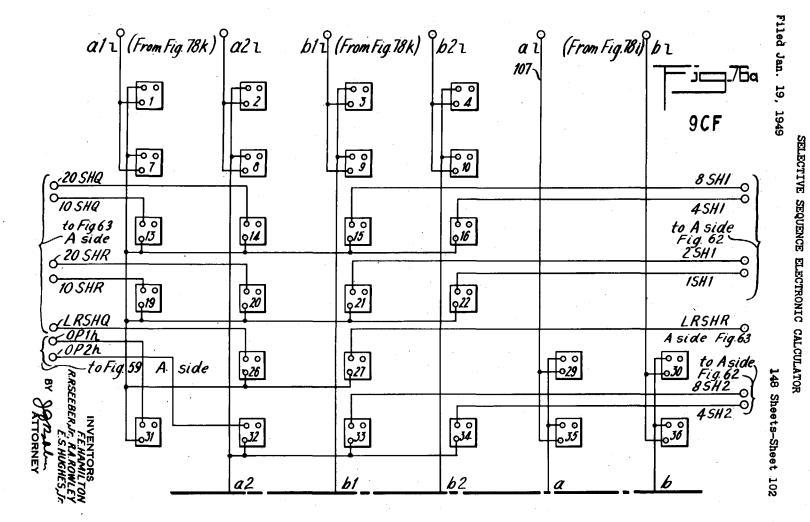

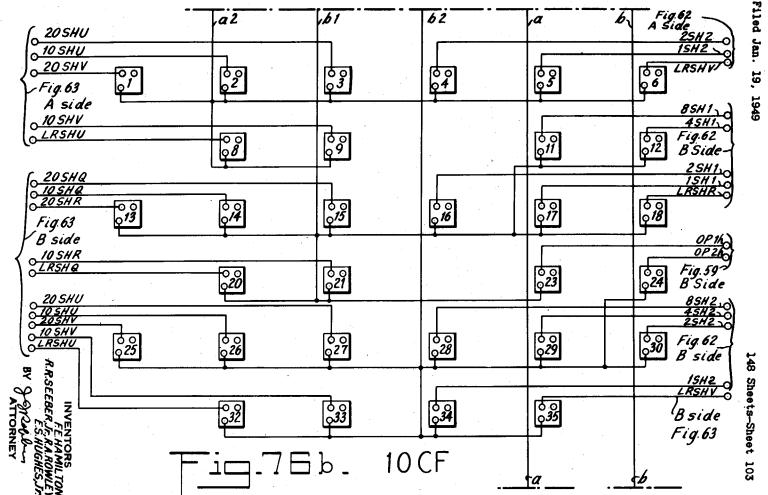

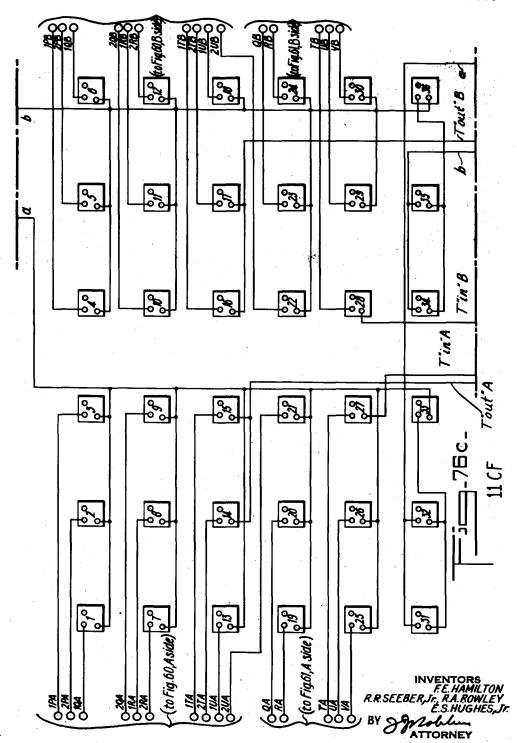

SELECTIVE SEQUENCE ELECTRONIC CALCULATOR

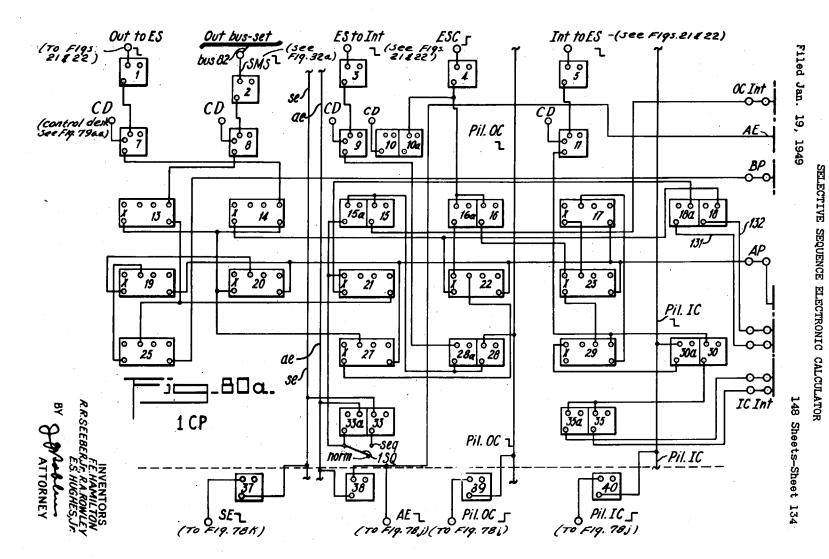

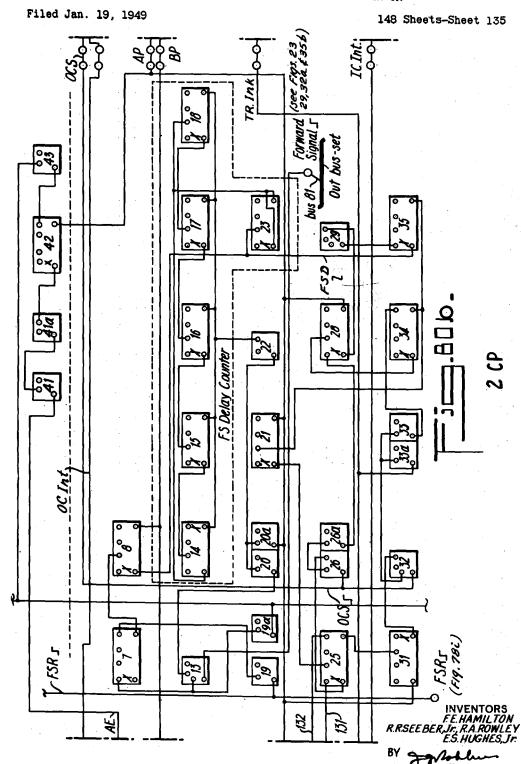

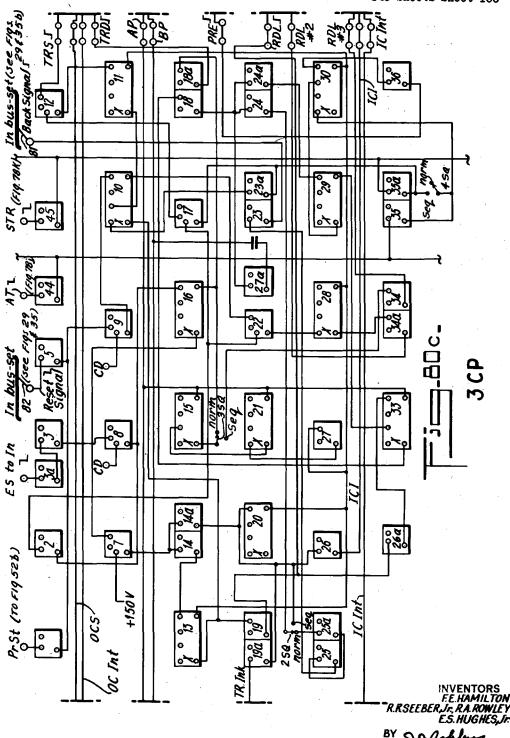

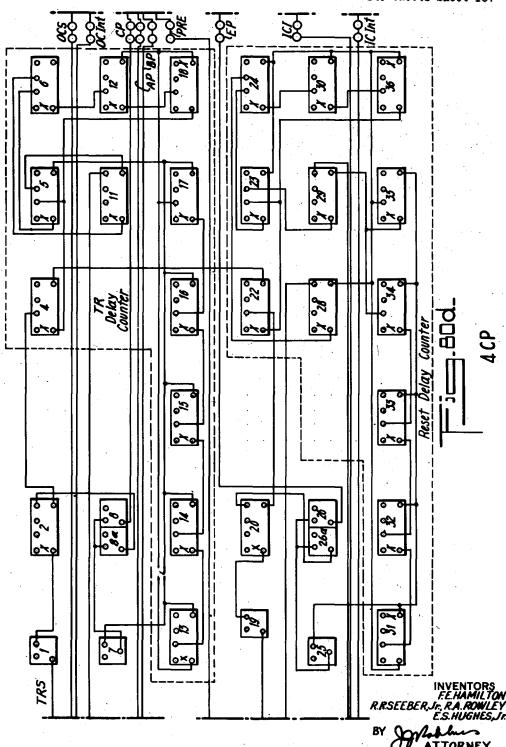

Filed Jan. 19, 1949

Filed Jan. 19, 1949

Filed Jan. 19, 1949

Filed Jan. 19, 1949

148 Sheets-Sheet 5

INVENTORS

FE HAMILTON

RRSEEBERJF, RAROWLEY

ES HUGHESJF.

BY JANAGER

ATTORNEY

Filed Jan. 19, 1949

Filed Jan. 19, 1949

Filed Jan. 19, 1949

Filed Jan. 19, 1949

Filed Jan. 19, 1949

F. E. HAMILTON ET AL

Filed Jan. 19, 1949

Filed Jan. 19, 1949

Filed Jan. 19, 1949

148 Sheets-Sheet 16

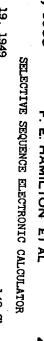

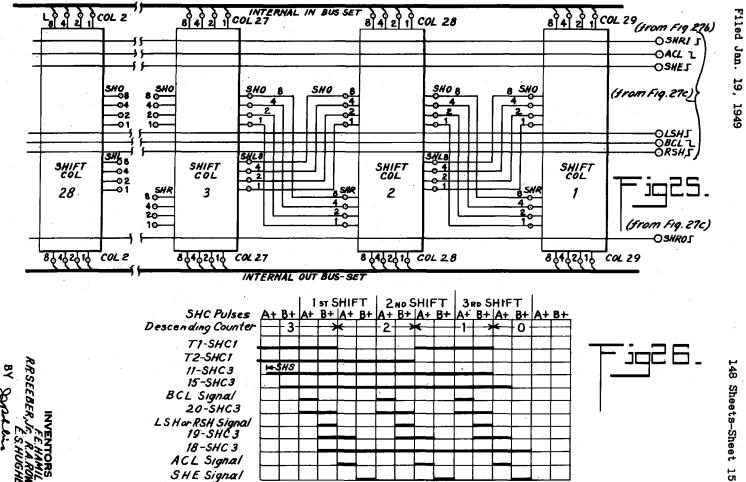

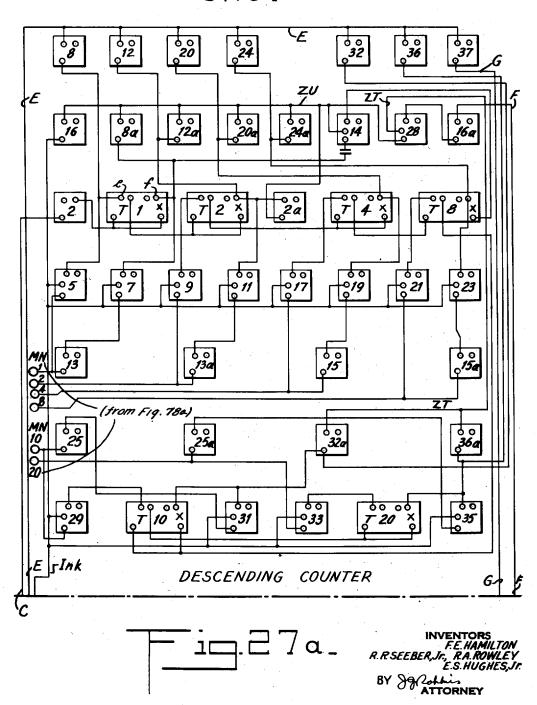

# SHC 1

Filed Jan. 19, 1949

Filed Jan. 19, 1949

SELECTIVE SEQUENCE ELECTRONIC CALCULATOR E. HAMILTON ET AL

2,636,672

2,636,672

| binary<br>positions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RELAY STORA                                                     |                                                        |                                                                    | April                                             |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------|--|--|

| 8 0 0 0 0 0 0 0 82<br>RS-GIP 4 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 000 000<br>000 000<br>000 000<br>000 000                        |                                                        | 000 000<br>000 000<br>000 000<br>000 000<br>1 2 3 18 19 20         | ril 28, 1953                                      |  |  |

| RS-GIPP 82 0-0-0-0-0 83 0-0-0-0-0 84 0-0-0-0-0   COIS: 1 23 18 19 20   RS-GIPP 82 0-0-0-0-0-0 84 0-0-0-0-0   RS-GIPP 4 0-0-0-0-0-0-0 0-0-0 0-0-0 0-0-0 0-0-0 0-0-0 0-0-0 0-0-0 0-0-0 0-0-0 0-0-0-0 0-0-0-0 0-0-0-0 0-0-0-0 0-0-0-0 0-0-0-0 0-0-0-0 0-0-0-0 0-0-0-0 0-0-0-0 0-0-0-0 0-0-0-0 0-0-0-0 0-0-0-0 0-0-0-0 0-0-0-0 0-0-0-0 0-0-0-0 0-0-0-0 0-0-0-0 0-0-0-0 0-0-0-0 0-0-0-0 0-0-0-0 0-0-0-0 0-0-0-0 0-0-0-0 0-0-0-0 0-0-0-0 0-0-0-0 0-0-0-0 0-0-0-0 0-0-0-0 0-0-0-0 0-0-0-0 0-0-0-0 0-0-0-0 0-0-0-0 0-0-0-0-0 0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0- |                                                                 |                                                        |                                                                    |                                                   |  |  |

| 8 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6<br>000 000<br>000 000<br>000 000<br>000 000<br>1 2 3 18 19 20 | 7<br>00 00<br>00 00<br>00 00<br>00 00<br>1 2 19 20     | 8<br>00 00<br>00 0082<br>00 00<br>00 00                            | E. HAMILTON ET SEQUENCE ELECTRONIC                |  |  |

| RS-GOP 4000 000 000 000 000 000 000 000 000 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | "OUT" Plugh                                                     | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | 000 5 000<br>000 000<br>000 000<br>000 000<br>1 2 3 18 19 20       | ET AL  IC CALCULATOR  148 Sheets                  |  |  |

| 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                 | 000 000 0                                              | 000 000 000<br>000 000 000<br>000 000 000<br>000 000 000<br>RS-GOP | ,636,672<br>S-Sheet 21<br>0 0 0 0 0 0<br>18 19 20 |  |  |

INVENTORS

FE HAMILTON

RESEEBERJE, RA. ROWLEY

ES. HUGHES, JE

BY SALLAL

BY ATTORNEY

Filed Jan. 19, 1949

148 Sheets-Sheet 24

STATION I MOVE NETWORK +150V IACL A P MRG 1000 A IBCL) .0035 -0012 .051 Stations 2 to 10 Station 1 **≸.**57 IMSA MSG Timer 2 Move Circuit Trigger -100V i —.3 ≥ b . + 150 V *75-60P8* 82 Q TS-GOPI *AMS* 0+0-0-1 BM5 0-10-0-5 .005 ≸ bus 82

Out bus-set 1

Move Signal SMS/1 75-G08 TS-G0I .01 .51 10/155 10.655 IASS 1855 ₹051 MSTR .51 .020 To Station 10 Move Control Circuit bus 82 of Out Bus-set 8 Move Signal SMS8 L -100V

ATTORNEY

Filed Jan. 19, 1949

Filed Jan. 19, 1949