## First Edition (March 1990)

This edition of the Assembler Language Reference for IBM AIX Version 3 for RISC System/6000 applies to Version 3 of IBM AIX RISC System/6000 Licensed Program and to all subsequent releases of these products until otherwise indicated in new releases or technical newsletters.

The following paragraph does not apply to the United Kingdom or any country where such provisions are inconsistent with local law: INTERNATIONAL BUSINESS MACHINES CORPORATION PROVIDES THIS MANUAL "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESSED OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Some states do not allow disclaimer of express or implied warranties in certain transactions; therefore, this statement may not apply to you.

This publication could include technical inaccuracies or typographical errors. Changes are periodically made to the information herein; these changes will be incorporated in new editions of the publication. IBM may make improvements and/or changes in the product(s) and/or the program(s) described in this publication at any time.

It is possible that this publication may contain reference to, or information about, IBM products (machines and programs), programming, or services that are not announced in your country. Such references or information must not be construed to mean that IBM intends to announce such IBM products, programming, or services in your country. Any reference to an IBM licensed program in this publication is not intended to state or imply that you can use only IBM's licensed program. You can use any functionally equivalent program instead.

Requests for copies of this publication and for technical information about IBM products should be made to your IBM Authorized Dealer or your IBM Marketing Representative.

A reader's comment form is provided at the back of this publication. If the form has been removed, address comments to IBM Corporation, Department 997, 11400 Burnet Road, Austin, Texas 78758–3493. IBM may use or distribute whatever information you supply in any way it believes appropriate without incurring any obligation to you.

- © Copyright AT&T, 1984, 1985, 1986, 1987, 1988, 1989. All rights reserved.

- © Copyright INTERACTIVE Systems Corporation 1984. All rights reserved.

- © Copyright International Business Machines Corporation 1987, 1990. All rights reserved.

Notice to U.S. Government Users – Documentation Related to Restricted Rights – Use, duplication or disclosure is subject to restrictions set forth in GSA ADP Schedule Contract with IBM Corporation.

# **Trademarks and Acknowledgements**

The following trademarks and acknowledgements apply to this book:

AIX is a trademark of International Business Machines Corporation.

IBM is a registered trademark of International Business Machines Corporation.

RISC System/6000 is a trademark of International Business Machines Corporation.

UNIX was developed and licensed by AT&T and is a registered trademark of AT&T Corporation.

# **About This Book**

This book provides information on application programming interfaces to the Advanced Interactive Executive Operating System (referred to in this text as AIX) for use on the RISC System/6000.

# Who Should Use This Book

This book is intended for experienced assembler language programmers. To use this book effectively, you should be familiar with AIX or UNIX System V commands, assembler instructions and pseudo-ops, and processor register usage.

## How to Use This Book

#### **Overview of Contents**

This book contains the following sections consisting of processor information, syntax and semantics, addressing information, the instruction set, information on running a program, and pseudo-ops.

- Overview of Processing and Storage on the RISC System/6000 Microprocessor

- Syntax and Semantics Overview

- Addressing Overview

- Instruction Set in alphabetical order

- Assembling, Linking, and Running a Program Overview

- Pseudo-ops Overview and alphabetical listing of Pseudo-ops

## Highlighting

The following highlighting conventions are used in this book:

Bold Identifies instructions, pseudo-ops, commands, and other items whose

names are predefined by the system.

**Italics** Identifies parameters whose actual names or values are to be supplied

by the user.

Monospace Identifies examples of specific data values, examples of text similar to

what you might see displayed, examples of portions of program code similar to what you might write as a programmer, messages from the

system, or information you should actually type.

# What is Not in This Book

This book does not teach readers how to program or operate their IBM RISC System/6000. Furthermore, this book contains little or no information about:

Any commands, system calls, subroutines, or programming aids that are part of the AIX Operating System, except for limited information on the as, Id, and cc commands.

- Error messages generated by the **as** command. These messages are shown in *Task Index and Glossary for IBM RISC System/6000*.

- Any hardware features. This book does give brief explanations about some processor registers and their use.

- · Details about privileged instructions.

## **Related Publications**

The following books contain information about or related to assembler language programming:

- IBM RISC System/6000 in POWERstation and POWERserver Hardware Technical Reference General Information, SA23–2643.

- AIX Files Reference for IBM RISC System/6000, SC23–2200.

- AIX Commands Reference for IBM RISC System/6000, SC23–2199.

- Task Index and Glossary for IBM RISC System/6000, SC23-2201.

# **Ordering Additional Copies of This Book**

To order additional copies of this book, use Order Number SC23-2197.

# Contents

| Chapter 1. Processing and Storage                                           | 1-1          |

|-----------------------------------------------------------------------------|--------------|

| Overview of Processing and Storage on the RISC System/6000 Microprocessor . | 1-2          |

| Branch Processor Overview                                                   | 1-3          |

| Fixed Point Processor Overview                                              | 1–6          |

| Floating Point Processor Overview                                           | 1–12         |

| Chaper 2. Syntax and Semantics                                              | 2–1          |

| Syntax and Semantics Overview                                               | 2–2          |

| Understanding The Character Set                                             | 2–2          |

| Understanding Reserved Words                                                | 2–3          |

| Understanding Line Format                                                   | 2–3          |

| Understanding Statements                                                    | 2–3          |

| Understanding Symbols                                                       | 2–5          |

| Understanding Constants                                                     | 2–9          |

| Understanding Operators                                                     | 2–11         |

| Understanding Expressions                                                   | 2–12         |

| Chapter 3. Addressing                                                       | 3–1          |

| Addressing Overview                                                         | 3–2          |

| Understanding the Location Counter                                          | 3–4          |

| Chapter 4. Assembling, Linking, and Running                                 | 4–1          |

| Assembling, Linking, and Running A Program Overview                         | 4–2          |

| Understanding Assembler Passes                                              | 4–2          |

| Assembling and Linking with the cc Command                                  | 4–3          |

| Interpreting an Assembler Listing                                           | 4–3          |

| Subroutine Linkage Convention                                               | 4–6          |

| Understanding the TOC                                                       | 4–14         |

| Running the Program                                                         | 4–17         |

| Chapter 5. Instruction Set                                                  | 5–1          |

| a (Add) Instruction                                                         | 5–2          |

| abs (Absolute) Instruction                                                  | 5-4          |

| ae (Add Extended) Instruction                                               | 5–6          |

| ai (Add Immediate) Instruction                                              | 5–8          |

| ai. (Add Immediate and Record) Instruction                                  | 5–9          |

| ame (Add to Minus One Extended) Instruction                                 | 5–10         |

| and (AND) Instruction                                                       | 5–12         |

| andc (AND With Complement) Instruction                                      | 5–14         |

| andil. (AND Immediate Lower) Instruction                                    | 5–16         |

| andiu. (AND Immediate Upper) Instruction                                    | 5-17         |

| aze (Add To Zero Extended) Instruction                                      | 5–18         |

| b (Branch) Instruction                                                      | 5-20         |

| bb (Branch on Condition Register Bit) Instruction                           | 5-22         |

| bc (Branch Conditional) Instruction                                         | 5–25<br>5–28 |

| DEG (DIGNOI CONUMENTALE COUNT REGISTER) INSTRUCTION                         | J-20         |

| bcr (Branch Conditional Register) Instruction                      | 5-30                 |

|--------------------------------------------------------------------|----------------------|

| cal (Compute Address Lower) Instruction                            | 5–32                 |

| cau (Compute Address Upper) Instruction                            | 5-33                 |

| cax (Compute Address) Instruction                                  | 5–34                 |

| cmp (Compare) Instruction                                          | 5-36                 |

|                                                                    | 5–36<br>5–38         |

| cmpi (Compare Immediate) Instruction                               |                      |

| cmpl (Compare Logical) Instruction                                 | 5-40                 |

| cmpli (Compare Logical Immediate) Instruction                      | 5–42                 |

| cntlz (Count Leading Zeros) Instruction                            | 5-44                 |

| crand (Condition Register AND) Instruction                         | 5–45                 |

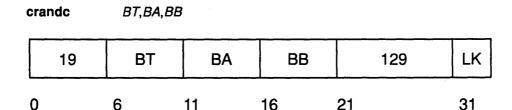

| crandc (Condition Register AND with Complement) Instruction        | 5–46                 |

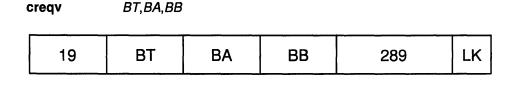

| creqv (Condition Register Equivalent) Instruction                  | 5–47                 |

| crnand (Condition Register NAND) Instruction                       | 5–48                 |

| crnor (Condition Register NOR) Instruction                         | 5–49                 |

| cror (Condition Register OR) Instruction                           | 5–50                 |

| crorc (Condition Register OR with Complement) Instruction          | 5–51                 |

| crxor (Condition Register XOR) Instruction                         | 5–52                 |

| div (Divide) Instruction                                           | 5–53                 |

| divs (Divide Short) Instruction                                    | 5-56                 |

| doz (Difference or zero) Instruction                               | 5-58                 |

| dozi (Difference or Zero Immediate) Instruction                    | 5-60                 |

| eqv (Equivalent) Instruction                                       | 561                  |

| exts (Extend Sign) Instruction                                     | 5-63                 |

| fa (Floating Add) Instruction                                      | 5–65                 |

| fabs (Floating Absolute Value) Instruction                         | 5–67                 |

| fcmpo (Floating Compare Ordered) Instruction                       | 5–69                 |

| fcmpu (Floating Compare Unordered) Instruction                     | 5-71                 |

| fd (Floating Divide) Instruction                                   | 5–73                 |

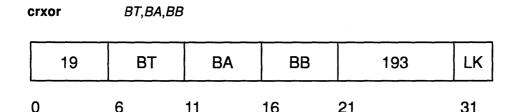

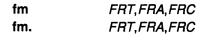

| fm (Floating Multiply) Instruction                                 | 5-75                 |

| fma (Floating Multiply Add) Instruction                            | 5-77                 |

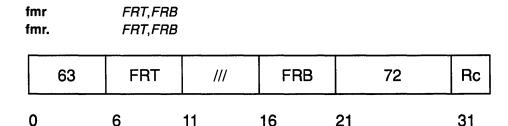

| fmr (Floating Move Register) Instruction                           | 5–79                 |

|                                                                    | 5–7 <i>9</i><br>5–81 |

| fms (Floating Multiply Subtract) Instruction                       | 5–83                 |

| fnabs (Floating Negative Absolute Value) Instruction               |                      |

| fineg (Floating Negate) Instruction                                | 5-85                 |

| fnma (Floating Negative Multiply Add) Instruction                  | 5–87                 |

| fnms (Floating Negative Multiply Subtract) Instruction             | 5–89                 |

| frsp (Floating Round to Single Precision) Instruction              | 5–92                 |

| fs (Floating Subtract) Instruction                                 | 5–95                 |

| I (Load) Instruction                                               | 5–97                 |

| lbrx (Load Byte Reverse Indexed) Instruction                       | 5–99                 |

| lbz (Load Byte And Zero) Instruction                               | 5–101                |

| Ibzu (Load Byte And Zero With Update) Instruction                  | 5–102                |

| Ibzux (Load Byte And Zero With Update Indexed) Instruction         | 5–104                |

| lbzx (Load Byte And Zero Indexed) Instruction                      | 5–106                |

| Ifd (Load Floating Point Double) Instruction                       | 5–107                |

| Ifdu (Load Floating Point Double With Update) Instruction          | 5-109                |

| Ifdux (Load Floating Point Double With Update Indexed) Instruction | 5-111                |

| Ifdx (Load Floating Point Double Indexed) Instruction              | 5–113                |

| Ifs (Load Floating Point Single) Instruction                       | 5-115                |

| Ifsu (Load Floating Point Single With Update) Instruction          | 5-117                |

| Ifsux (Load Floating Point Single With Undate Indexed) Instruction | 5_119                |

| Ifsx (Load Floating Point Single Indexed) Instruction        | 5-121 |

|--------------------------------------------------------------|-------|

| Iha (Load Half Algebraic) Instruction                        | 5–123 |

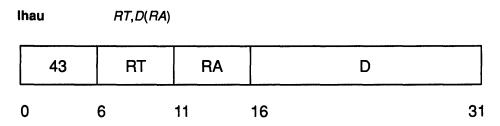

| Ihau (Load Half Algebraic With Update) Instruction           | 5–125 |

| Ihaux (Load Half Algebraic With Update Indexed) Instruction  | 5–127 |

| Ihax (Load Half Algebraic Indexed) Instruction               | 5–129 |

| Ihbrx (Load Half Byte Reverse Indexed) Instruction           | 5-131 |

| Ihz (Load Half And Zero) Instruction                         | 5-133 |

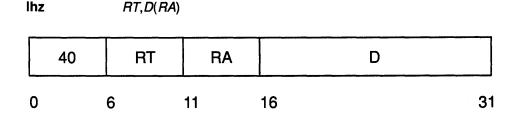

| Ihzu (Load Half And Zero With Update) Instruction            | 5–135 |

| Ihzux (Load Half And Zero With Update Indexed) Instruction   | 5-137 |

| Ihzx (Load Half And Zero Indexed) Instruction                | 5-139 |

| lil (Load Immediate Lower) Instruction                       | 5-141 |

| liu (Load Immediate Upper) Instruction                       | 5-142 |

| Im (Load Multiple) Instruction                               | 5-143 |

| Iscbx (Load String And Compare Byte Indexed) Instruction     | 5-145 |

| Isi (Load String Immediate) Instruction                      | 5-148 |

| lsx (Load String Indexed) Instruction                        | 5-150 |

| lu (Load With Update) Instruction                            | 5-152 |

| lux (Load With Update Indexed) Instruction                   | 5-154 |

| lx (Load Indexed) Instruction                                | 5-156 |

| maskg (Mask Generate) Instruction                            | 5-158 |

| maskir (Mask Insert From Register) Instruction               | 5-160 |

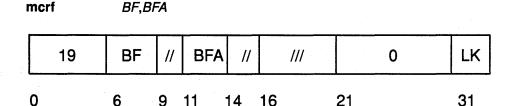

| mcrf (Move Condition Register Field) Instruction             | 5-162 |

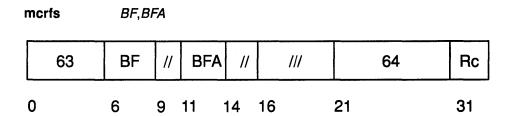

| mcrfs (Move To Condition Register From FPSCR) Instruction    | 5-163 |

| mcrxr (Move To Condition Register From XER) Instruction      | 5-165 |

| mfcr (Move From Condition Register) Instruction              | 5-166 |

| mffs (Move From FPSCR) Instruction                           | 5-167 |

| mfmsr (Move From Machine State Register) Instruction         | 5-169 |

| mfspr (Move From Special Purpose Register) Instruction       | 5-170 |

| mtcrf (Move To Condition Register Fields) Instruction        | 5-172 |

| mtfsf (Move To FPSCR Fields) Instruction                     | 5-174 |

| mtfsfi (Move To FPSCR Field Immediate) Instruction           | 5-176 |

| mtfsb1 (Move To FPSCR Bit 1) Instruction                     | 5-178 |

| mtfsb0 (Move To FPSCR Bit 0) Instruction                     | 5-180 |

| mtspr (Move To Special Purpose Register) Instruction         | 5-182 |

| mul (Multiply) Instruction                                   | 5-184 |

| muli (Multiply Immediate) Instruction                        | 5-186 |

| muls (Multiply Short) Instruction                            | 5-187 |

| nabs (Negative Absolute) Instruction                         | 5-189 |

| nand (NAND) Instruction                                      | 5-191 |

| neg (Negate) Instruction                                     | 5-193 |

| nor (NOR) Instruction                                        | 5-195 |

| or (OR) Instruction                                          | 5-197 |

| orc (OR With Complement) Instruction                         | 5-199 |

| oril (OR Immediate Lower) Instruction                        | 5-201 |

| oriu (OR Immediate Upper) Instruction                        | 5-202 |

| rlimi (Rotate Left Immediate Then Mask Insert) Instruction   | 5-202 |

| rlinm (Rotate Left Immediate Then AND With Mask) Instruction | 5-205 |

| rlmi (Rotate Left Then Mask Insert) Instruction              | 5-207 |

| rlnm (Rotate Left Then Mask insert) instruction              | 5-209 |

| rrib (Rotate Right And Insert Bit) Instruction               | 5-211 |

| ef (Subtract From) Instruction                               | 5-213 |

| sfe (Subtract From Extended) Instruction                             | 5–215 |

|----------------------------------------------------------------------|-------|

| sfi (Subtract From Immediate) Instruction                            | 5–217 |

| sfme (Subtract From Minus One Extended) Instruction                  | 5-218 |

| ,                                                                    | 5–220 |

| si (Subtract Immediate) Instruction                                  | 5–222 |

| si. (Subtract Immediate and Record) Instruction                      | 5-223 |

| sl (Shift Left) Instruction                                          | 5–225 |

| sle (Shift Left Extended) Instruction                                | 5–227 |

| sleq (Shift Left Extended with MQ) Instruction                       | 5–229 |

| sliq (Shift Left Immediate with MQ) Instruction                      | 5–231 |

| slliq (Shift Left Long Immediate With MQ) Instruction                | 5–233 |

| sllq (Shift Left Long with MQ) Instruction                           | 5–235 |

| slq (Shift Left with MQ) Instruction                                 | 5–237 |

| sr (Shift Right) Instruction                                         | 5–239 |

| sra (Shift Right Algebraic) Instruction                              | 5–241 |

| srai (Shift Right Algebraic Immediate) Instruction                   | 5–243 |

| sraiq (Shift Right Algebraic Immediate With MQ) Instruction          | 5–245 |

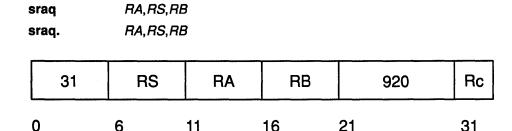

| sraq (Shift Right Algebraic With MQ) Instruction                     | 5–247 |

| sre (Shift Right Extended) Instruction                               | 5–249 |

| srea (Shift Right Extended Algebraic) Instruction                    | 5–251 |

| sreq (Shift Right Extended With MQ) Instruction                      | 5-253 |

| sriq (Shift Right Immediate With MQ) Instruction                     | 5-255 |

| srliq (Shift Right Long Immediate With MQ) Instruction               | 5–257 |

| srlq (Shift Right Long With MQ) Instruction                          | 5-259 |

| srq (Shift Right with MQ) Instruction                                | 5–261 |

| st (Store) Instruction                                               | 5-263 |

| stb (Store Byte) Instruction                                         | 5-265 |

| stbrx (Store Byte Reverse Indexed) Instruction                       | 5-266 |

| stbu (Store Byte With Update) Instruction                            | 5-268 |

| stbux (Store Byte With Update Indexed) Instruction                   | 5-270 |

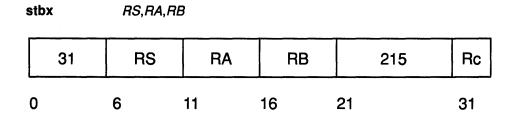

| stbx (Store Byte Indexed) Instruction                                | 5-272 |

| stfd (Store Floating Point Double) Instruction                       | 5-273 |

| stfdu (Store Floating Point Double With Update) Instruction          | 5-275 |

| stfdux (Store Floating Point Double With Update Indexed) Instruction | 5-277 |

| stfdx (Store Floating Point Double Indexed) Instruction              | 5-279 |

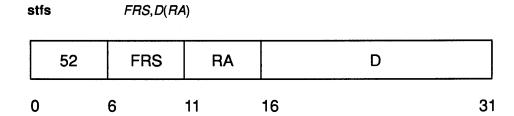

| stfs (Store Floating Point Single) Instruction                       | 5-281 |

| stfsu (Store Floating Point Single With Update) Instruction          | 5-283 |

| stfsux (Store Floating Point Single With Update Indexed) Instruction | 5-285 |

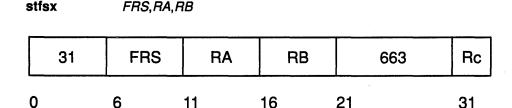

| stfsx (Store Floating Point Single Indexed) Instruction              | 5-287 |

| sth (Store Half) Instruction                                         | 5-289 |

| sthbrx (Store Half Byte Reverse Indexed) Instruction                 | 5-291 |

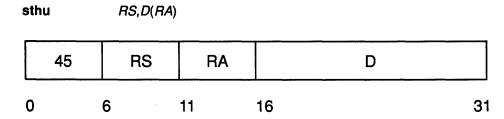

| sthu (Store Half With Update) Instruction                            | 5-293 |

| sthux (Store Half With Update Indexed) Instruction                   | 5-295 |

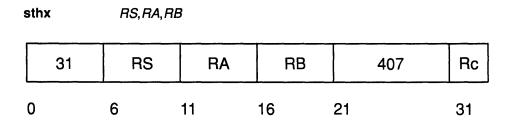

| sthx (Store Half Indexed) Instruction                                | 5-297 |

| stm (Store Multiple) Instruction                                     | 5-299 |

| stsi (Store String Immediate) Instruction                            | 5-301 |

| stsx (Store String Indexed) Instruction                              | 5-303 |

| stu (Store With Update) Instruction                                  | 5-305 |

| stux (Store with Update Indexed) Instruction                         | 5-307 |

| stx (Store Indexed) Instruction                                      | 5-309 |

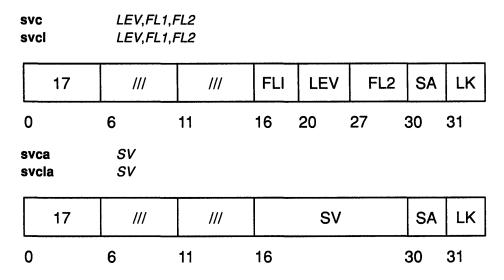

| svc (Supervisor Call) Instruction                                    | 5-311 |

| t (Trap) Instruction                    |       |

|-----------------------------------------|-------|

| ti (Trap Immediate) Instruction         | 5-315 |

| xor (XOR) Instruction                   | 5–317 |

| xoril (XOR Immediate Lower) Instruction | 5-319 |

| xoriu (XOR Immediate Upper) Instruction | 5-320 |

|                                         |       |

| Chapter 6. Pseudo-ops                   | 6–1   |

| Pseudo-ops Overview                     | 6–2   |

| Notational Conventions                  | 6–4   |

| .align Pseudo-op                        | 6–7   |

| .bb Pseudo-op                           | 6-9   |

| .bc Pseudo-op                           | 6–10  |

| .bf Pseudo-op                           | 6–11  |

| .bi Pseudo-op                           | 6–12  |

| .bs Pseudo-op                           | 6–13  |

| .byte Pseudo-op                         | 6-14  |

| .comm Pseudo-op                         | 6-15  |

| .csect Pseudo-op                        | 6-17  |

| .double Pseudo-op                       | 6-20  |

| .drop Pseudo-op                         | 6–21  |

| .dsect Pseudo-op                        | 6-22  |

| .eb Pseudo-op                           | 6-23  |

| .ec Pseudo–op                           | 6–24  |

| .ef Pseudo–op                           | 625   |

| .ei Pseudo-op                           | 6–26  |

| .es Pseudo-op                           | 6-27  |

| .extern Pseudo-op                       | 6-28  |

| .file Pseudo-op                         | 6–29  |

| .float Pseudo-op                        | 6-30  |

| .function Pseudo-op                     | 6–31  |

| .globl Pseudo-op                        | 6–32  |

| .hash Pseudo-op                         | 6–33  |

| .lcomm Pseudo-op                        | 6-34  |

| .line Pseudo-op                         | 6–36  |

| long Pseudo-op                          | 6–37  |

| .org Pseudo-op                          | 6–38  |

| rename Pseudo-op                        | 6-39  |

| .set Pseudo-op                          | 6-40  |

| .short Pseudo-op                        | 6-41  |

| space Pseudo-op                         | 6-42  |

| .stabx Pseudo-op                        | 6-43  |

| .string Pseudo-op                       | 6-44  |

| ·                                       | 6-45  |

| .tbtag Pseudo-op                        | 6-45  |

| .tc Pseudo-op                           | 6-49  |

| .toc Pseudo-op                          |       |

| .tocof Pseudo-op                        | 6–50  |

| .using Pseudo-op                        | 6-52  |

| .vbyte Pseudo-op                        | 6-54  |

| .xline Pseudo-op                        | 6–55  |

| Appendix A. Opcode and Mnemonic Tables  | A-1   |

| Instruction Set, Indexed by Primary Opcode | A-2 |

|--------------------------------------------|-----|

| Instruction Set, Indexed by Mnemonic       | A-7 |

# Chapter 1. Processing and Storage

# Overview of Processing and Storage on the RISC System/6000 Microprocessor

The characteristics of the RISC System/6000 Microprocessor's processor and storage influence its assembler language. The capabilities of the processor and the nature of available storage determine what the assembler can do.

This chapter gives an overview of the RISC System/6000 Microprocessor and tells you how data is stored both in main memory and in registers. This information will give you some of the conceptual background necessary to understanding the function of the RISC System/6000 Microprocessor's instruction set and pseudo-ops.

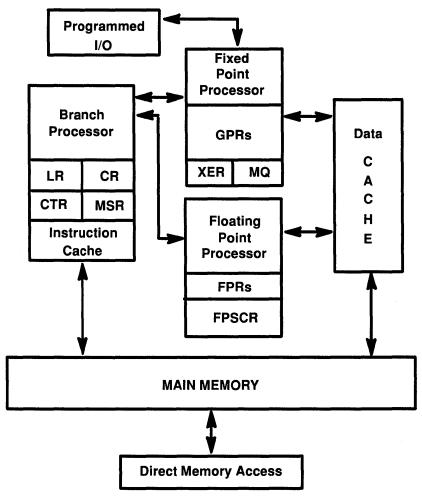

The processor unit contains the sequencing and processing controls for instruction fetch, instruction execution and interrupt action. The following figure shows the logical partitioning of the RISC System/6000 Microprocessor.

The processing unit is a word oriented fixed point processor functioning in tandem with a doubleword oriented Floating Point processor. The microprocessor uses 32-bit word-aligned instructions and provides for byte, halfword, word, and doubleword operand fetches and stores between storage and a set of 32 General Purpose Registers, and between storage and a set of 32 Floating Point Registers.

### **Branch Processor Overview**

The Branch Processor has four 32-bit registers.

- The Condition Register

- The Link Register

- The Count Register

- The Machine State Register

Branch, Supervisor Linkage, Trap, Return From Interrupt, and Condition Register instructions effect the various registers of the Branch Processor.

## Understanding Branch Instructions

Use branch instructions to change the sequence of instruction execution.

Since all branch instructions are on word boundaries, the processor performing the branch ignores bits 30 and 31 of the generated branch target address. All branch instructions can be used in unprivileged state.

A branch instruction computes the target address in one of four ways:

- The target address is the sum of a constant and the address of the branch instruction itself.

- The target address is the absolute address given as argument to the instruction.

- The target address is the address found in the Link Register.

- The target address is the address found in the Count Register.

Using the first two of these methods, the target address can be computed sufficiently ahead of the branch instructions to prefetch instructions along the target path.

Using the third and fourth methods, prefetching instructions along the branch path is also possible provided the Link Register or the Count Register is loaded sufficiently ahead of the branch instruction.

In the case of conditional branch instructions, instruction prefetching is done on each path of the branch.

In the various target forms, branches generally either branch only, branch and provide a return address, branch conditionally, or branch conditionally and provide a return address. If the particular branch instruction has the I in the syntax form, then it sets the link bit to 1 and the Link Register stores the return address from an invoked subroutine. The return address is the address of the instruction immediately following the branch instruction.

**b** (Branch) Instruction

ba (Branch Absolute) Instruction

**bb** (Branch on Condition Register Bit) Instruction

bc (Branch Conditional) Instruction

bca (Branch Conditional Absolute) Instruction

**bcc** (Branch Conditional to Count Register) Instruction

bcr (Branch Conditional Register) Instruction

Conditional branch instructions require the specification of branch option bits and condition type and may use an optional link flag.

#### **Extended Mnemonics**

These extended instructions are based on branch instructions and facilitate setting specified bits. The branch condition is specified by a Branch Code which replaces the **XX** in each Extended Mnemonic instruction.

bxx, bxxi (Branch on Condition Extended) Instruction

bXXa, bXXIa (Branch on Condition Extended Absolute) Instruction

bXXc, bXXcI (Branch Count Register on Condition) Instruction

bXXr, bXXrI (Branch Register on Condition) Instruction

bbta, bbfa, bbfla, bbfla (Branch on Condition Register Bit) Instruction

bbtc, bbfc, bbtcl, bbfcl (Branch on Condition Register Bit) Instruction

bbtr, bbfr, bbfrl, bbtrl (Branch on Condition Register Bit) Instruction

bctr (Branch to Count Register) Instruction

bdz, bdn, bdzl, bdnl (Branch and Decrement CTR) Instruction

bdzXX, bdnXX (Branch and Decrement CTR on Condition) Instruction

bdza, bdna, bdzla, bdnla (Branch Absolute and Decrement CTR) Instruction

bdzr, bdnr, bdzrl, bdnrl (Branch Register and Decrement CTR) Instruction

| <b>Branch Code</b> | Meaning                   |

|--------------------|---------------------------|

| lt                 | less than*                |

| gt                 | greater than*             |

| eq                 | equal to*                 |

| so                 | summary overflow*         |

| ge                 | greater than or equal to* |

| le                 | less than or equal to*    |

| ne                 | not equal to*             |

| ns                 | not summary overflow*     |

| nl                 | not less than             |

| ng                 | not greater than          |

| Z                  | zero                      |

| nz                 | not zero                  |

**Note:** The **bdzXX** and **bdnXX** instructions use only the first eight Branch Codes (marked by \*) in place of **XX**.

## **Understanding Supervisor Linkage Instructions**

There are two Branch Processor instructions for system control.

svc (Supervisor Call) Instruction

svca (Supervisor Call Absolute) Instruction

## **Understanding Trap Instructions**

You can use the trap instructions to test for a specified set of conditions during the execution of your program. You can define traps for events that should not occur during program execution, such as an index out or range, or the use of an invalid character. If any of the defined trap conditions are met, a Program Interrupt occurs. If the tested conditions are not met, instruction execution continues normally.

These instructions compare the contents of a General Purpose Register with a 32-bit value. This comparison results in five test conditions. These are ANDed with five condition bits provided in the instruction TO field. If the result is not zero, then a Program interrupt occurs.

The five test conditions are:

| TO bit | ANDed with Condition            |

|--------|---------------------------------|

| 6      | Compares Less Than              |

| 7      | Compares Greater Than           |

| 8      | Compares Equal                  |

| 9      | Compares Logically Less Than    |

| 10     | Compares Logically Greater Than |

The available Trap Instructions are:

t (Trap) Instruction

ti (Trap Immediate) Instruction

# **Understanding Condition Register Instructions**

## **Condition Register Field Instructions**

The following instruction copies one Condition Register field to another.

mcrf (Move Condition Register Field) Instruction

### **Condition Register Logical Instructions**

The following instructions perform logical operations with the Condition Register fields.

crand (Condition Register AND) Instruction

crandc (Condition Register AND with Complement) Instruction

creqv (Condition Register Equivalent) Instruction

crnand (Condition Register NAND) Instruction

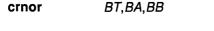

crnor (Condition Register NOR) Instruction

cror (Condition Register OR) Instruction

crorc (Condition Register OR with Complement) Instruction

crxor (Condition Register XOR) Instruction

### **Related Information**

Fixed Point Processor Overview on page 1-6, Floating Point Processor Overview on page 1-12.

See the following articles in POWERstation and POWERserver Hardware Technical Reference — General Information: Condition Register, Link Register, Count Register, Machine State Register.

#### **Fixed Point Processor Overview**

The Fixed Point Processor uses a set of 32-bit Registers that includes:

- Thirty-two 32-bit General Purpose Registers

- One 32-bit Fixed Point Exception Register

- One 32-bit Multiply Quotient Register

## **Understanding General Purpose Registers**

The thiry-two 32-bit General Purpose Registers constitute the principal internal storage mechanism in the Fixed Point Processor.

Each General Purpose Register is 32 bits wide.

## **Understanding Fixed Point Load Instructions**

The Fixed Point Load Instructions move information from a location in memory into one of the General Purpose Registers.

The Load instructions compute the effective address when moving data. If the storage access does not cause an Alignment Interrupt or a Data Storage Interrupt, the byte, halfword, or word in storage addressed by the effective address is loaded into a target General Purpose Register.

The following Load instructions are available.

I (Load) Instruction

Ibrx (Load Byte Reverse Indexed) Instruction

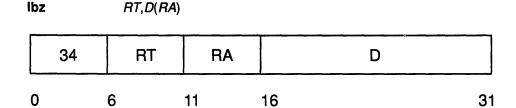

Ibz (Load Byte and Zero) Instruction

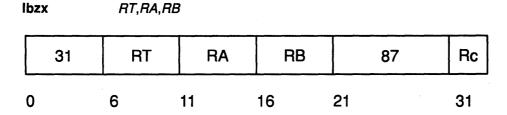

Ibzx (Load Byte and Zero Indexed) Instruction

Iha (Load Half Algebraic) Instruction

Ihax (Load Half Algebraic Indexed) Instruction

Ihbrx (Load Half Byte Reverse Indexed) Instruction

Ihz (Load Half and Zero) Instruction

Ihzx (Load Half and Zero Indexed) Instruction

III (Load Immediate Lower) Instruction

liu (Load Immediate Upper) Instruction

Im (Load Multiple) Instruction

ix (Load Indexed) Instruction

# **Understanding Fixed Point Load with Update Instructions**

The Fixed Point Load with Update Instructions move information from a location in memory into one of the General Purpose Registers.

The Load With Update instructions compute an elective address when moving data. This address can replace the contents of the Base General Purpose Register. If the storage

access does not cause an Alignment Interrupt or Data Storage Interrupt, the instruction then copies the byte, halfword, or word contents of the specified location in memory into a second target General Purpose Register.

There are four conditions under which a newly calculated effective address is not saved.

- The General Purpose Register to be updated is the same as the target General Purpose Register. Under this circumstance the updated Register contains data loaded from memory.

- The General Purpose Register to be updated is GPR 0.

- The storage access causes an Alignment Interrupt.

- The storage access causes a Data Storage Interrupt.

The following Load with Update Instruction are available:

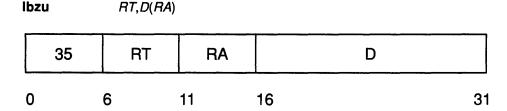

Ibzu (Load Byte And Zero With Update) Instruction

Ibzux (Load Byte And Zero With Update Indexed) Instruction

Ihau (Load Half Algebraic With Update) Instruction

Ihaux (Load Half Algebraic With Update Indexed) Instruction

Ihzu (Load Half And Zero With Update) Instruction

Ihzux (Load Half And Zero With Update Indexed) Instruction

lu (Load With Update) Instruction

lux (Load With Update Indexed) Instruction

# **Understanding Fixed Point Store Instructions**

If the storage access does not cause an Alignment Interrupt or a Data Storage Interrupt, the contents of a source General Purpose Register are stored into the byte, halfword, or word in storage addressed by the effective address.

st (Store) Instruction

stb (Store Byte) Instruction

stbrx (Store Byte Reverse Indexed) Instruction

stbx (Store Byte Indexed) Instruction

sth (Store Half) Instruction

sthbrx (Store Half Byte Reverse Indexed) Instruction

sthx (Store Half Indexed) Instruction

stm (Store Multiple) Instruction

stx (Store Indexed) Instruction

# **Understanding Fixed Point Store with Update Instructions**

If the storage access does not cause an Alignment Interrupt or a Data Storage Interrupt, the contents of a source General Purpose Register are stored into the byte, halfword, or word in storage addressed by the effective address. If the General Purpose Register does not

contain the address to be updated and is not General Purpose Register 0 and no interrupt occurs, then the effective address is placed into the Base General Purpose Register.

stbu (Store Byte With Update) Instruction

stbux (Store Byte With Update Indexed) Instruction

sthu (Store Half With Update) Instruction

sthux (Store Half with Update Indexed) Instruction

stu (Store With Update) Instruction

stux (Store With Update Indexed) Instruction

## **Understanding Fixed Point String Instructions**

The Fixed Point String Instructions allow the movement of data from storage to registers or from registers to storage without concern for alignment. These instructions can be used for a short move between arbitrary storage locations or to initiate a long move between unaligned storage fields. Load String Indexed and Store String Indexed Instructions of zero length do not alter the target register.

Iscbx (Load String And Compare Byte Indexed) Instruction

Isi (Load String Immediate) Instruction

Isx (Load String Indexed) Instruction

stsi (Store String Immediate) Instruction

stsx (Store String Indexed) Instruction

## **Understanding Fixed Point Address Computation Instructions**

There are three fixed point instructions for address computation.

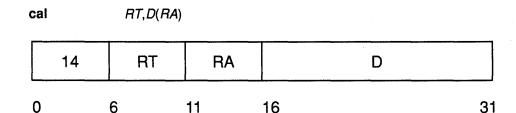

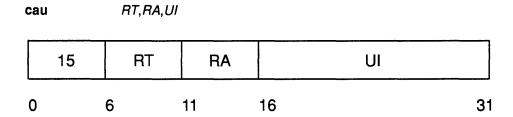

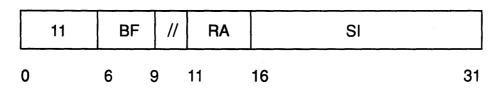

cal (Compute Address Lower) Instruction

cau (Compute Address Upper) Instruction

cax (Compute Address) Instruction

# **Understanding Fixed Point Arithmetic Instructions**

The Fixed Point Arithmetic Instructions treat the contents of registers as 32-bit signed integers.

a (Add) Instruction

abs (Absolute) Instruction

ae (Add Extended) Instruction

ai (Add Immediate) Instruction

ai. (Add Immediate and Record) Instruction

ame (Add To Minus One Extended) Instruction

aze (Add To Zero Extended) Instruction

div (Divide) Instruction

divs (Divide Short) Instruction

doz (Difference or Zero) Instruction

dozi (Difference or Zero Immediate) Instruction

mul (Multiply) Instruction

muli (Multiply Immediate) Instruction

muls (Multiply Short) Instruction

nabs (Negative Absolute) Instruction

neg (Negate) Instruction

sf (Subtract From) Instruction

sfe (Subtract From Extended) Instruction

sfi (Subtract From Immediate) Instruction

sfme (Subtract From Minus One Extended) Instruction

sfze (Subtract From Zero Extended) Instruction

si (Subtract Immediate) Instruction

si. (Subtract Immediate and Record) Instruction

## **Understanding Fixed Point Logical Instructions**

The Logical Instructions perform the indicated operations in a bit-wise fashion.

and (AND) Instruction

andc (AND With Complement) Instruction

andil. (AND Immediate Lower) Instruction

andiu. (AND Immediate Upper) Instruction

cntlz (Count Leading Zeros) Instruction

eqv (Equivalent) Instruction

exts (Extend Sign) Instruction

nand (NAND) Instruction

nor (NOR) Instruction

or (OR) Instruction

orc (OR With Complement) Instruction

oril (OR Immediate Lower) Instruction

oriu (OR Immediate Upper) Instruction

xor (XOR) Instruction

xoril (XOR Immediate Lower) Instruction

xoriu (XOR Immediate Upper) Instruction

# **Understanding Fixed Point Rotate Instructions**

The Fixed Point Processor performs rotate operations on data from a General Purpose Register. The result of the rotate with mask instructions is either inserted into the register under control of the provided mask or ANDed with the mask before the result is placed in the

register. The rotate operations move a specified number of bits to the left. The bits that exist from bits position 0 enter at bit position 31.

When the rotate with insert is used, the result of the rotate operation is placed into the target General Purpose Register under control of the provided mask. If a mask bit is 1, then the associated bit of the rotated data (0 or 1) is placed into the target General Purpose Register. If the mask bit is 0, the associated data bit (0 or 1) from the register remains unchanged.

The rotate left instructions allow rotate right instructions to be performed (in concept) by a rotate left of 32-N bits, where N is the number of positions to rotate right.

#### **Fixed Point Bit Mask Instructions**

maskg (Mask Generate) Instruction

maskir (Mask Insert From Register) Instruction

rrib (Rotate Right And Insert Bit) Instruction

#### **Fixed Point Rotate With Mask Instructions**

rlimi (Rotate Left Immediate Then Mask Insert) Instruction

rlinm (Rotate Left Immediate Then AND With Mask) Instruction

rlmi (Rotate Left Then Mask Insert) Instruction

rlnm (Rotate Left Then AND With Mask) Instruction

## Understanding Fixed Point Shift Instructions

The Fixed Point Shift Instructions logically perform left and right shifts. The result of a shift instruction is placed in a General Purpose Register under control of a generated mask.

When the result of a shift instruction is placed into register RA, the target register, under the control of a generated mask, one of the following occurs:

- If the mask bit is a 1, the respective bit from either the rotated word or a word of zeroes is placed into the target General Purpose Register.

- If the mask bit is a 0, the corresponding bit from either the Multiply Quotient Register or a word of 32 sign bits from the source General Purpose Register is placed into the target General Purpose Register.

Setting the instruction's Record bit to 1 sets bits in the Condition Register according to the value of the contents of the target General Purpose Register at the completion of the instruction. The Condition Register is a set as if a compare between the contents of the target General Purpose Register and the value zero had been performed.

sl (Shift Left) Instruction

sle (Shift Left Extended) Instruction

sleq (Shift Left Extended With MQ) Instruction

sliq (Shift Left Immediate With MQ) Instruction

sllig (Shift Left Long Immediate with MQ) Instruction

sllq (Shift Left Long With MQ) Instruction

slq (Shift Left With MQ) Instruction

sr (Shift Right) Instruction

sra (Shift Right Algebraic) Instruction srai (Shift Right Algebraic Immediate) Instruction sraig (Shift Right Algebraic Immediate With MQ) Instruction sraq (Shift Right Algebraic With MQ) Instruction sre (Shift Right Extended) Instruction srea (Shift Right Extended Algebraic) Instruction sreq (Shift Right Extended With MQ) Instruction sriq (Shift Right Immediate With MQ) Instruction srliq (Shift Right Long Immediate With MQ) Instruction srlq (Shift Right Long With MQ) Instruction srq (Shift Right With MQ) Instruction

## **Understanding Fixed Point Move To/From System Registers** Instructions

Several instructions move the contents of one system register into another system register or into a General Purpose Register.

mcrxr (Move To Condition Register From XER) Instruction

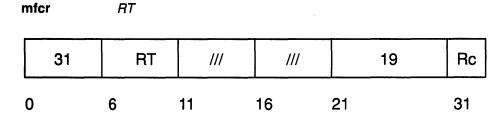

mfcr (Move From Condition Register) Instruction

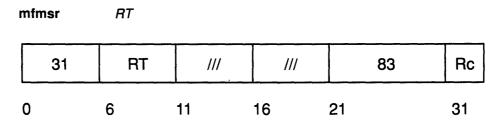

mfmsr (Move From Machine State Register) Instruction

mfspr (Move From Special Purpose Register) Instruction

mtcrf (Move To Condition Register Fields) Instruction

mtspr (Move To Special Purpose Register) Instruction

### **Related Information**

See the following articles in POWERstation and POWERserver Hardware Technical Reference — General Information: Condition Register, Machine State Register, General Purpose Registers, Fixed Point Exception Register, Multiply Quotient Register.

Branch Processor Overview on page 1-3.

# **Floating Point Processor Overview**

The Floating Point Processor instructions are provided to perform arithmetic operations in floating point registers and move floating point data between storage and these registers.

## **Understanding Floating Point Numbers**

A floating point number consists of a signed exponent and a signed significand, and expresses a quantity that is the product of the significand and the number 2\*\*exponent. Encodings are provided in the data format to represent:

- Finite numeric values

- +- Infinity

- Values which are "Not a Number" (NaN)

Operations involving infinities produce results obeying traditional mathematical conventions. NaNs have no mathematical interpretation. Their encoding permits a variable diagnostic information field. They may be used to indicate uninitialized variables and can be produced by certain invalid operations.

## Understanding Floating Point Processor Registers Floating Point Registers

There are thiry-two 64-bit Floating Point Registers, numbered from Floating Point Register 0-31. All Floating Point instructions provide a 5-bit field that is used to specify which Floating Point Registers are to be used in the execution of the instruction. Every instruction that interprets the contents of a Floating Point Register as a floating point value uses the double precision floating point format for this interpretation.

All floating point instructions other than loads and stores are performed on operands located in Floating Point Registers and place the results in a Floating Point Register. The Floating Point Status and Control Register and the Condition Register maintain status information about the outcome of some floating point operations.

## **Double and Single Format Conversions on Load and Store**

Load and store double instructions transfer 64 bits of data without conversion between storage and a Floating Point Register in the Floating Point Processor. Load single instructions convert a stored single floating format value to the same value in double floating format and transfer that value into a Floating Point Register. Store single instruction, do the opposite, converting a double floating format value in a Floating Point Register into a single floating format value, prior to storage.

# Understanding The Floating Point Status and Control Register

The Floating Point Status and Control Register is a 32-bit register that contains control flags which govern the handling of Floating Point Exceptions (bits 20-31) and record information about the results of floating point operations (bits 0–19).

## Understanding Floating Point Load Instructions

There are load instructions for single precision and double precision. Double precision data is loaded directly into a Floating Point Register. Since Floating Point Registers only support floating point double precision operands, the processor converts single precision data to double precision prior to loading.

Ifd (Load Floating Point Double) Instruction

Ifdu (Load Floating Point Double with Update) Instruction

Ifdux (Load Floating Point Double with Update Indexed) Instruction

Ifdx (Load Floating Point Double Indexed) Instruction

Ifs (Load Floating Point Single) Instruction

Ifsu (Load Floating Point Single with Update) Instruction

Ifsux (Load Floating Point Single with Update Indexed) Instruction

Ifsx (Load Floating Point Single Indexed) Instruction

## Understanding Floating Point Store Instructions

There are store instructions for single precision and double precision. Single precision stores convert Floating Point Register contents to single precision proir to storage.

stfd (Store Floating Point Double) Instruction

stfdu (Store Floating Point Double With Update) Instruction

stfdux (Store Floating Point Double With Update Indexed) Instruction

stfdx (Store Floating Point Double Indexed) Instruction

stfs (Store Floating Point Single) Instruction

stfsu (Store Floating Point Single With Update) Instruction

stfsux (Store Floating Point Single With Update Indexed) Instruction

stfsx (Store Floating Point Single Indexed) Instruction

# Understanding Floating Point Move Instructions

The Floating Point Move Instructions copy data from one Floating Point Register to another. Data may be modified depending upon the instruction.

fabs (Floating Absolute Value) Instruction

fmr (Floating Move Register) Instruction

fnabs (Floating Negative Absolute Value) Instruction

fneg (Floating Negate) Instruction

## **Understanding Floating Point Arithmetic Instructions**

The Floating Point Arithmetic Instructions perform arithmetic functions using floating point data.

fa (Floating Add) Instruction

fd (Floating Divide) Instruction

fm (Floating Multiply) Instruction

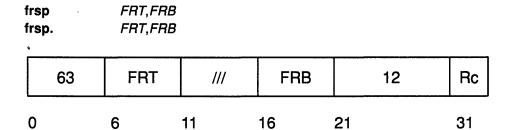

frsp (Floating Round to Single Precision) Instruction

fs (Floating Subtract) Instruction

## Understanding Floating Point Accumulate Instructions

The Floating Point Accumulate Instructions combine a multiply and an add operation without an intermediate rounding operation.

fma (Floating Multiply Add) Instruction

fms (Floating Multiply Subtract) Instruction

fnma (Floating Negative Multiply Subtract) Instruction

fnms (Floating Negative Multiply Subtract) Instruction

## Understanding Floating Point Compare Instructions

There are two instructions for performing ordered and unordered compares of the contents of two Floating Point Registers. You specify which field in the Condition Register receives the result of the compare.

fcmpo (Floating Compare Ordered) Instruction

fcmpu (Floating Compare Unordered) Instruction

These instructions set one bit in the field to one, and the others to zero. The compare result bits have the following interpretations:

| Bit 0 | ( <i>FRA</i> ) < ( <i>FRB</i> ) | Less Than    |

|-------|---------------------------------|--------------|

| Bit 1 | (FRA) > (FRB)                   | Greater Than |

| Bit 2 | (FRA) = (FRB)                   | Equal        |

| Bit 3 | (FRA) ? (FRB)                   | Unordered    |

## Understanding Floating Point Status and Control Register Instructions

These instructions manipulate data in the Floating Point Status and Control Register.

mcrfs (Move to Condition Register from FPSCR) Instruction

mffs (Move from FPSCR) Instruction

mtfsf (Move to FPSCR Fields) Instruction

mtfsfi (Move to FPSCR Fields Immediate) Instruction

mtfsb1 (Move to FPSCR Bit 1) Instruction

mtfsb0 (Move to FPSCR Bit 0) Instruction

#### **Related Information**

The frsp (Floating Round to Single Precision) instruction, mtcrf (Move to Condition Register Fields) instruction, mtfsf (Move to FPSCR Fields) instruction, mtfsfi (Move to FPSCR Fields Immediate) instruction, mtfsb1 (Move to FPSCR Bit 1) instruction, mtfsb0 (Move to FPSCR Bit 0) instruction.

See the following articles in POWERstation and POWERserver Hardware Technical Reference — General Information: Floating Point Data Representation, Floating Point Resource Management, Floating Point Exceptions, Machine State Register.

# **Chaper 2. Syntax and Semantics**

# **Syntax and Semantics Overview**

This overview explains the syntax and semantics of assembler language, including The Character Set, Reserved Words, Line Format, Statements, Symbols, Constants, Operators, and Expressions.

## **Understanding The Character Set**

All letters and numbers are allowed. The assembler discriminates between uppercase and lowercase letters. To the assembler, the symbols *Name* and *name* identify distinct symbols.

Some blank spaces are required, while others are optional. The assembler allows you to substitute tabs for spaces.

The following characters have special meaning in RISC System/6000 assembler language.

#### , (comma)

Operand separator. Commas are allowed in statements only between operands.

Example:

a 3,4,5

#### # (pound sign)

Comments. Anything after the #to the end of the line is ignored by the assembler. A #can be the first character in a line, or it can be preceded by any number of characters, blank spaces, or both.

#### Example:

```

a 3,4,5 # Puts the sum of GPR4 and GPR5 into GPR3.

```

#### : (colon)

Defines a label. The : always appears immediately after the last character of the label name and defines a label equal to the value contained in the location counter at the time the assembler encounters the label.

#### Example:

#### ; (semicolon)

Instruction separator. A semicolon separates two instructions that appear on the same line. Spaces around the semicolon are optional.

A single instruction on one line does not have to end with a semicolon.

#### Example:

```

a 3,4,5  # These two lines have

a 4,3,5  # the same effect as...

a 3,4,5; a 4,3,5  # ...this line.

```

#### \$ (dollar sign)

Refers to the current value in the assembler's current location counter.

#### Example:

```

dino: .long 1,2,3

size: .long $ - dino

```

## **Understanding Reserved Words**

There are no reserved words in the RISC System/6000 Microprocessor assembler language. The mnemonics for instructions and pseudo-ops are not reserved and can be used in the same way as any other symbols.

There may be restrictions on the names of symbols that are passed to programs written in other languages.

## **Understanding Line Format**

The RISC System/6000 Microprocessor assembler language is written in free format. There are no requirements for certain things to be in any particular column position.

The assembler language puts no limit on the number of characters that can appear on a single input line. If a code line is longer than one line on a terminal, line wrapping will depend on the editor used. However, the listing will only display 100 ASCII characters per line.

Blank lines are allowed; the assembler ignores them.

## **Understanding Statements**

The RISC System/6000 Microprocessor assembler language has three kinds of statements: instruction statements, pseudo-operation statements, and null statements. The Assembler also uses Separator Characters, Labels, Mnemonics, Operands, and Comments.

## Instruction Statements and Pseudo-operation Statements

An instruction or pseudo-op statement has the following syntax:

```

[label:] mnemonic [operand1[,operand2...]] [# comment]

```

The assembler recognizes the end of a statement when one of the following appears:

- An ASCII new-line character

- A comment character (#)

- A semicolon(;).

#### **Null Statements**

A null statement does not have a mnemonic or any operands. It can contain a label, a comment, or both. Processing a null statement does not change the value of the location counter.

Null statements are useful mainly to make assembler source code easier for people to read.

A null statement has the following syntax:

```

[label:] [# comment]

```

The spaces between the label and the comment are optional.

If the null statement has a label, the label receives the value of the next statement, even though that state is on a different line. The assembler gives the label the value contained in the current location counter. For example,

here:

a 3,4,5

is synonymous with

here: a 3,4,5

**Note:** Certain pseudo-ops may prevent a null statement's label from receiving the value of the address of the next statement.

#### **Separator Character**

The separator characters are spaces, tabs, and commas. Commas separate operands. Spaces or tabs separate the other parts of a statement. A tab can be used wherever a space is shown in this book.

The spaces shown are required. You can optionally put one or more spaces after a comma, before a pound sign (#), and after a #.

#### Labels

The label entry is optional. A line may have zero, one, or more labels. A line may have a label but no other contents.

To define a label, follow a symbol with a colon (:). The assembler gives the label the value contained in the assembler's current location counter. This value represents a relocatable address.

#### Example:

```

# The label subtr: receives the value

# of the address of the sf instruction.

# You can now use subtr in subsequent statements

# to refer to this address.

```

If the label is in a statement with an instruction that causes data alignment, the label receives its value before the alignment occurs.

#### Example:

```

# Assume that the location counter now

# contains the value of 98.

place: .long expr

# When the assembler processes this statement, it

# sets place to address 98. But the .long is a pseudo—op that

# aligns expr on a fullword. Thus, the assembler puts

# expr at the next available fullword boundary, which is

# address 100. In this case, place is not actually the address

# at which expr is stored; referring to place will not put you

# at the location of expr.

```

#### **Mnemonics**

The mnemonic field identifies whether a statement is an instruction statement or a pseudo-op statement. Each mnemonic requires a certain number of operands in a certain format.

For an instruction statement, the mnemonic field contains an abbreviation like **ai** (Add Immediate) or **sf** (Subtract From). This mnemonic describes an operation where the RISC System/6000 Microprocessor processes a single machine instruction that is associated with a numerical operation code (opcode). All instructions are 4 bytes long. When the assembler encounters an instruction, the assembler increments the location counter by the required number of bytes.

For a pseudo-op statement, the mnemonic represents an instruction to the assembler program itself. There is no associated opcode, and the mnemonic does not describe an operation to the processor. Some pseudo-ops increment the location counter; others do not.

#### **Operands**

The existence and meaning of the operands depends on the mnemonic used. Some mnemonics do not require any operands. Other mnemonics require one or more operands.

The assembler interprets each operand in context with the operand's mnemonic. Many operands are expressions that refer to registers or symbols. For instruction statements, operands can be immediate data that is to be directly assembled into the instruction.

#### **Comments**

Comments are optional and are ignored by the assembler. Every line of a comment must be preceded by a pound sign (#); there is no other way to designate comments.

## **Understanding Symbols**

A symbol is a single character or combination of characters used as a label or operand. Symbols may consist of numeric digits, underscores, periods, uppercase or lowercase letters, or any combination of these. The symbol cannot contain any blanks or special characters, and cannot begin with a digit. Uppercase and lowercase letters are distinct.

From the assembler and loader's perspective, the length of a symbol name is limited only by the amount of storage you have. Also note that other routines linked to the assembler language files may have their own constraints on symbol length.

With the exception of .csect or TOC entry names, symbols may be used to represent storage locations or arbitrary data. The value of a symbol is always a 32-bit quantity.

The following are valid symbol names:

READER

XC2345

result.a

resultA

balance\_old

label9

.myspot

The following are not possible symbol names:

7\_sum (begins with a digit)

#ofcredits (the # makes this a comment)

aa\*1 (contains \*, a special character)

IN AREA (contains a blank)

You can define a symbol by using it in one of two ways:

- As a label for an instruction or pseudo-op

- As the name operand of a .set, .comm, .lcomm, .dsect, or .csect pseudo-op.

### Defining a symbol with a Label

You can define a symbol by using it as a label.

#### Example:

| _            | .using  | dataval[RW],5 |

|--------------|---------|---------------|

| loop:        |         |               |

|              | bgt     | cont          |

| •            |         |               |

| •            |         |               |

|              | bdz     | loop          |

| cont:        | 1       | 3,dataval     |

|              | a       | 4,3,4         |

| •            |         |               |

| •            |         |               |

| .csect datav | val[RW] |               |

| dataval:     | .short  | 10            |

The assembler gives the value of the location counter at the instruction or pseudo-op's leftmost byte. In the example above, the object code for the I instruction contains the location counter value for *dataval*.

At runtime, an address is calculated from *dataval*, the offset, and GPR 5, which needs to contain the address of **csect dataval[RW]**. In the example above, the I instruction uses the 16 bits of data stored at *dataval*'s address.

Note that the value referred to by the symbol actually occupies a memory location. A symbol defined by a label is a relocatable value.

The symbol itself does not exist at runtime. However, you can change the value at the address represented by a symbol at runtime, if some code changes the contents of the location represented by *dataval*.

#### Defining a Symbol with a Pseudo-op

Use a symbol as the name operand of a .set pseudo-op to define the symbol. This pseudo-op has the format:

```

.set name, exp

```

The assembler evaluates the *exp* operand, then assigns the value and type of *exp* to the symbol *name*. When the assembler encounters that symbol in an instruction, the assembler puts the symbol's value into the instruction's object code.

For example:

```

.set number,10

.

.

ai 4,4,number

```

In the example above, the object code for the ai instruction contains the value assigned to number, that is, 10.

Note that the value of the symbol is assembled directly into the instruction, and does not occupy any storage space. A symbol defined with a .set can have an absolute or relocatable type, depending on the type of the *exp* operand. Also, because the symbol occupies no storage, you cannot change the value of the symbol at runtime; reassembling the file will give the symbol a new value.

A symbol can also be defined by using it as the *name* operand of a .comm, .lcomm, .csect or, .dsect pseudo-op. Except for .dsect, the value assigned to the symbol does describe storage space.

## **CSECT and TOC Entry Names**

A symbol can also be defined when used as the *qualname* operand of the .csect or .tc pseudo-op. When used in this context, the symbol is defined as the name of a csect or a TOC entry with the specified storage class. Therefore, the storage class qualifier is *required* when naming csects or TOC entries. Once defined, the symbol takes on a storage class that corresponds to the name qualifier.

For csects, different csects can have the same name but different storage classes; therefore, the storage class identifier must be used when referring to a csect name as an operand of other pseudo-ops. However, this is not the case with the binder. If csect names are externalized, establish unique names for the externalized csects. A csect operand name takes the form of:

```

or

symbol{XX}

```

where the required square brackets []]) or curly ({ }) brackets both produce the same results and surround a two-character storage class identifier which can be one of the following:

| PR | RO  |

|----|-----|

| DB | GL  |

| XO | sv  |

| RW | UA  |

| DS | TI  |

| TB | LC  |

| TC | TC0 |

in uppercase or lowercase. The following example illustrates the definition and a possible use of a csect:

```

.csect progldata[rw]

# Defines a csect called "progldata"

# of storage class 'RW'.

.

.

.long progldata[RW]

```

For TOC entries, different TOC entries can have the same name but will be considered the same TOC entry. The storage class identifier must be used when using the TOC entry name as an operand. A TOC entry operand name takes the form of:

```

symbol[TC]

```

where *TC* stands for TOC entry. The following example illustrates the definition and a possible use of a TOC entry name:

```

.tc pldata[TC],pldata[RW]

.long pldata[TC]

```

#### The Special Symbol TOC

Provisions have been made for the special symbol TOC. In XCOFF format modules, this symbol is reserved for the TOC anchor, or the first entry in the TOC. The symbol TOC has been predefined in the assembler so that the symbol TOC can be referred to if its use is required. The .toc pseudo—op creates the TOC anchor entry. For example, the following data declaration declares a word that contains the address of the beginning of the TOC.

```

.long TOC[TC0]

```

This symbol is undefined unless a .toc pseudo-op is contained within the assembler file.

## Using a Symbol Before Defining It

It is possible to use a symbol before you define it. Using a symbol, and then defining it later in the same file, is called forward referencing. In other words, the following is acceptable.

If the symbol is not defined in the file in which it occurs, it is called an external symbol. When the assembler finds undefined symbols, it gives an error message. External symbols may be declared in an .extern statement.

## **Declaring an External Symbol**

If a local symbol is used that is defined in another module, the **.extern** pseudo-op is used to declare that symbol in the local file as an external symbol. Any undefined symbols that do not appear in an **.extern** or **.globl** statement will be flagged with an error.

## **Understanding Constants**

The RISC System/6000 Microprocessor assembler language provides four kinds of constants:

- Arithmetic constants

- Character constants

- Symbolic constants

- String constants

When the assembler encounters an arithmetic or character constant that is being used as an instruction's operand, the value of that constant is assembled into the instruction. When the assembler encounters a symbol being used as a constant, the value of the symbol is assembled into the instruction.

#### **Arithmetic Constants**

There are four kinds of arithmetic constants:

- Decimal

- Octal

- Hexadecimal

- Floating Point

The largest signed positive integer number that can be represented is the decimal value 2\*\*31–1. The largest negative value is –231. Regardless of the base (e.g., decimal, hexadecimal or octal), the as assembler regards integers as 32-bit constants.

#### **Decimal Constants**

Base 10 is the default base for arithmetic constants. If you want to specify a decimal number, just type the number in the appropriate place.

```

ai 5,4,10

# Add the decimal value 10 to the contents

# of GPR 4 and put the result in GPR 5.

```

Do not prefix decimal numbers with a zero. A leading zero indicates that the number is octal.

#### **Octal Constants**

To specify that a number is octal, prefix the number with the *numeral* 0.

```

ai 5,4,0377

# Add the octal value 0377 to the contents

# of GPR 4 and put the result in GPR 5.

```

#### **Hexadecimal Constants**

To specify a hexadecimal number, prefix the number with **0X** or **0x**. You can use either uppercase or lowercase for the hexadecimal numerals A through F.

```

ai 5,4,0xF

# Add the hexadecimal value 0xF to the

# contents of GPR 4 and put the result

# in GPR 5.

```

#### **Floating Point Constants**

A floating point constant has the following components in order.

**Integer Part**

Must be one or more digits.

**Decimal Part**

Optional

**Fraction Part**

Must be one or more digits.

**Exponent Part**

Optional. Consists of an e or E, possibly followed by a + or -, followed

by one or more digits.

For assembler input, you may omit the fraction part. For example, the following are valid floating point constants.

0.45 1e+5 4E-11

0.99E6 357.22e12

Floating point constants are only allowed wherever fcon expressions are found.

There is no bounds checking for the operand.

Note: The atof subroutine is called to get the floating point number from input. Check current documentation for restrictions and return values.

#### **Character Constants**

To specify an ASCII character constant, prefix the constant with a ' (single quote mark). Character constants can appear anywhere an arithmetic constant is allowed, but you can only specify one character constant at a time. For example 'A represents the ASCII code for the character A.

Character constants are convenient when you want to use the code for some character as a constant.

```

cal 3,'X(0)

# Loads GPR 3 with the ASCII code for

# the character X (that is, 0x58).

# After the cal instruction executes, GPR 3 will

# contain binary

# 0x0000 0000 0000 0000 0000 0000 0101 1000.

```

## **Symbolic Constants**

A symbol can be used as a constant. A symbol can be given a value so that the value can be referred to by name, instead of using the value itself.

Using a symbol as a constant is convenient if a value occurs frequently in a program. Define the symbolic constant once by giving the value a name. To change its value, simply change the definition, not every reference to it in the program. The changed file must be reassembled before the symbol constant is valid.

A symbolic constant can be defined by using it as a label or by using it in a .set statement.

#### **Strings**

String constants are different than other types of constants in that they can only be used as operands to certain pseudo-ops, such as .rename, .byte, or .string pseudo-ops.

The syntax of string constants are any number of characters enclosed in double quotes (").

```

"any number of characters"

```

The double quote character is obtained with two double quotes.

"a double quote character is specified like this "" "

## **Understanding Operators**

The RISC System/6000 Microprocessor assembler language provides the following operators.

All of these operators evaluate from left to right except for the unary operators which evaluate from right to left.

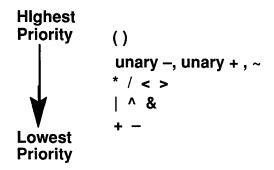

#### Operator Precedence

Operator precedence for 32-bit expressions is shown in the following figure.

All the operators perform 32-bit signed integer operations.

The division operator produces an integer result; the remainder has the same sign as the dividend. For example:

| Operation | Result | Remainder |

|-----------|--------|-----------|

| 8/3       | 2      | 2         |

| 8/–3      | -2     | 2         |

| (-8)/3    | -2     | <b>–2</b> |

| (-8)/(-3) | 2      | <b>–2</b> |

The left shift (<) and right shift (>) operators take an integer bit value for the right-hand operand. For example:

```

.set mydata,1

.set newdata,mydata<2</pre>

# Shifts 1 left 2 bits.

# Assigns the result to newdata.

```

## Understanding Expressions

An expression is a constant, a symbol, or a combination of constants, symbols, and operators. The assembler evaluates each expression into a single value, and then uses that value as an operand. Expressions have a type as well as a value.

There are five types of expressions.

- Absolute Expressions

- Relocatable Expressions

- External Expressions

- Restricted External Expressions

- TOC Relative Expressions

The type of an expression depends on the type of its operands. Expression types are important for two reasons. First, some pseudo-ops and instructions require expressions of a particular type. Second, only certain operators are allowed in certain types of expressions, as described below.

#### **Absolute Expressions**

The value of an absolute expression is independent of any possible code relocation. The value of an absolute expression stays the same, no matter where the runtime segment containing the expression is loaded.

An absolute expression is one of the following:

- A integer or character constant

- A symbol set to an absolute

- absolute<operator>absolute, where <operator> is any arithmetic binary operator

- -absolute

- +absolute

- relocatable relocatable, where the two "relocatable's" refer to or are contained within the same assembler csect.

The definitions of "absolute" and "relocatable" given above are recursive. For example,

absolute<operator>absolute<operator>relocatable, - relocatable is a valid expression.

Any expression not covered by the above rules is invalid. An example of an invalid expression is relocatable+relocatable.

#### **Relocatable Expressions**

The value of a relocatable expression depends on the location of the csect containing the relocatable expression. If the csect moves to a different storage location, the value of the relocatable expression changes accordingly.

Since the csects can be relocated independently, the type of a relocatable expression includes the csect that contains it.

A relocatable expression is one of the following:

- A label

- A symbol set to a relocatable expression

- relocatable + absolute

- relocatable absolute

- absolute + relocatable

- absolute relocatable

The definitions of "absolute" and "relocatable" above are recursive. For example,

```

absolute+(relocatable+absolute)

```

is a valid relocatable expression.

Any expression not covered by the above rules is invalid. Examples of invalid relocatable expressions are:

```

relocatable*absolute

absolute / relocatable

```

All expressions that are based on the location counter are relocatable.

The final resolution of the value represented by a relocatable expression is performed at load time.

#### **External Expressions**

External expressions refer to external symbols (symbols not defined, but declared in the current file).

If the external expression is used as a label, the expression is relocatable. An external expression cannot be used as the subject of a .set.

An external expression is one of the following:

- A symbol declared with .comm

- A symbol declared with .extern

- An undefined symbol declared with .glob!

- external + absolute

- external absolute