# Customer Engineering Manual of Instruction

| Issued to:                                                               |

|--------------------------------------------------------------------------|

| Branch Office:                                                           |

| Department:                                                              |

| Address:                                                                 |

| If this manual is misplaced, it should be returned to the above address. |

Data Processing System, Model 1

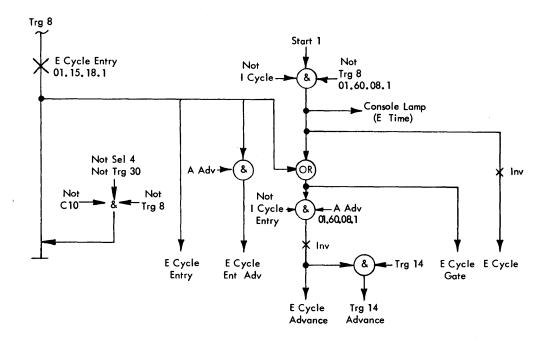

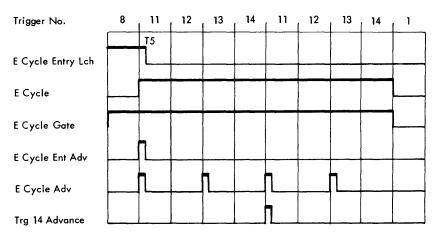

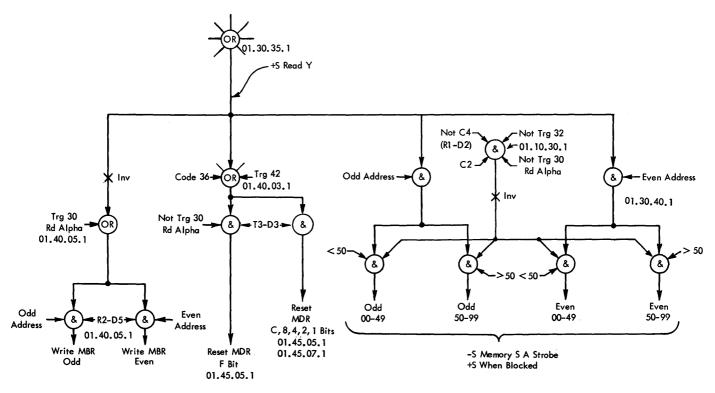

1620 Central Processing Unit, Model 1

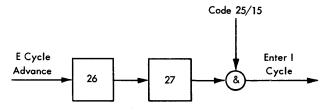

This edition, Form 227-5751-1 is a merge of Form 227-5751-0 and its supplement, Form S27-5850-0.

Copies of this and other IBM publications can be obtained through IBM Branch Offices. Comments concerning the contents of this publication may be addressed to:

IBM, Product Publications Department, San Jose, Calif. 95114

© 1962 by International Business Machines Corporation

# CONTENTS

| SECTION 1 GENERAL INFORMATION · · · · · · · · 1.1              | TFC Card                                                     |

|----------------------------------------------------------------|--------------------------------------------------------------|

| Description of System • • • • • • • • • • • 1.1                | WJ Card                                                      |

| Machine Language · · · · · · · · 1.2                           | WY Card                                                      |

| Character Code · · · · · · · · · · · · · ·                     | YGB and YGC Cards · · · · · · · · · · · · 4. 19              |

| Instruction Format · · · · · · · · · · · · · · · · · 1.3       | YGH, YGJ, and YGN Cards · · · · · · · · · 4. 19              |

| Data Format · · · · · · · · · · · · · · · · · · ·              | YGA and YJB Cards · · · · · · · · · · · · · 4.19             |

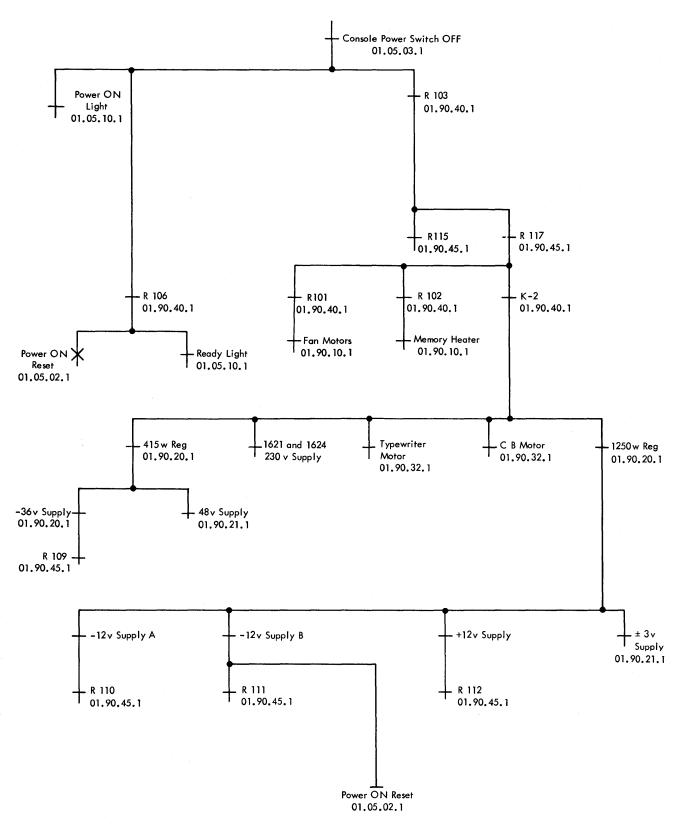

| Stored Program Concept                                         | Power Supplies · · · · · · · · 4. 19                         |

| Stored Frogram Concept. 1.4                                    |                                                              |

| CECTION 2 MEMORY ADDRESSING AND DATA                           | SMS Power Supplies                                           |

| SECTION 2 MEMORY ADDRESSING AND DATA  FLOW                     | Power-On Sequence                                            |

| FLOW 2. 1                                                      | Power-Off Sequence · · · · · · · · · · · · · · · · · 4.21    |

| Introduction · · · · · · 2.1                                   | SECTION 5 FUNCTIONAL UNITS · · · · · · · · · 5.1             |

| Memory • • • • • • • • • • • • • • • • • • 2. 1                |                                                              |

| Sense Amplifiers and Memory Buffer Register (MBR) • • • • 2.2  | Clock and Timing Chart ••••• 5.1                             |

| Memory Data Register (MDR) · · · · · · · · · · · 2. 2          | Memory • • • • • • • • • • • • • • • • • • •                 |

| Memory Address Register Storage (MARS) · · · · · · · 2.3       | Memory Buffer Register (MBR) · · · · · · · · · · · · 5. 12   |

| Increment/Decrement Switch · · · · · · · · · · · · 2.4         | Memory Data Register (MDR) • • • • • • • • • • • • 5.13      |

|                                                                | Memory Address Register Storage (MARS) • • • • • • • • 5.14  |

| SECTION 3 PROGRAMMING · · · · · · · · · · 3.1                  | Memory Address Register (MAR) · · · · · · · · · · 5. 15      |

|                                                                | Increment/Decrement Switch • • • • • • • • • • • • 5.16      |

| Development of a Program · · · · · · · · · · · · · · · · · 3.1 | Operation Register and Decoder ••••••• 5. 17                 |

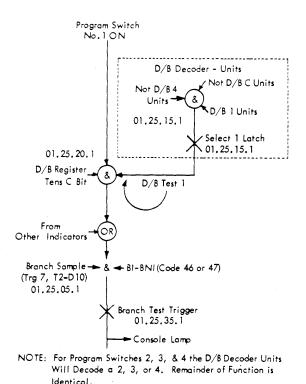

| Insertion of a Program Into Memory (Typewriter Keyboard) • 3.1 | Digit/Branch (D/B) Register and Decoder · · · · · · · · 5.17 |

| Execution of a Program · · · · · · · · · · · · · 3.1           | True/Complement (T/C) Switch • • • • • • • • • • 5.20        |

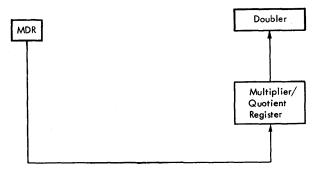

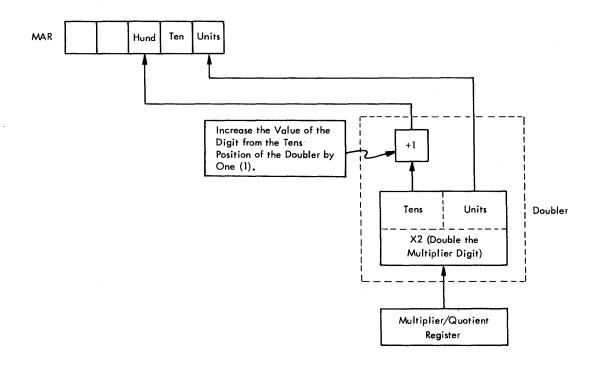

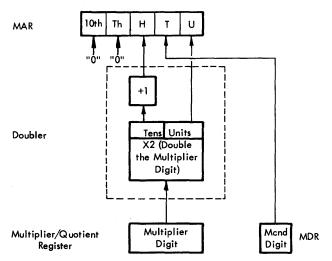

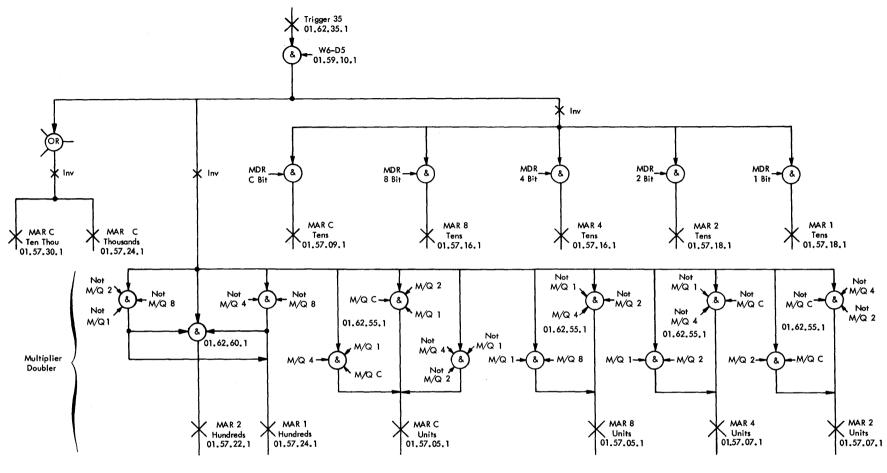

| Automatic Program Repetition (Program Loop) • • • • • • • 3.3  | Multiplier/Quotient (M/Q) Register • • • • • • • • • • 5.20  |

|                                                                | Multiplier-Doubler • • • • • • • • • • • • • • • • 5. 21     |

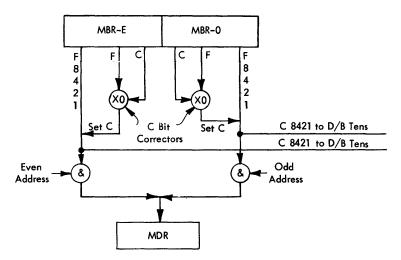

| SECTION 4 COMPONENTS AND POWER SUPPLY • • • • • • 4.1          | C-Bit Correctors •••••• 5. 21                                |

|                                                                | MBR to MDR ••••• 5. 21                                       |

| Magnetic Cores · · · · · · · · · · · · · · · · · 4.1           | MDR to MBR ••••• 5.21                                        |

| Memory Cores · · · · · · · · · · · · · · · · 4.1               |                                                              |

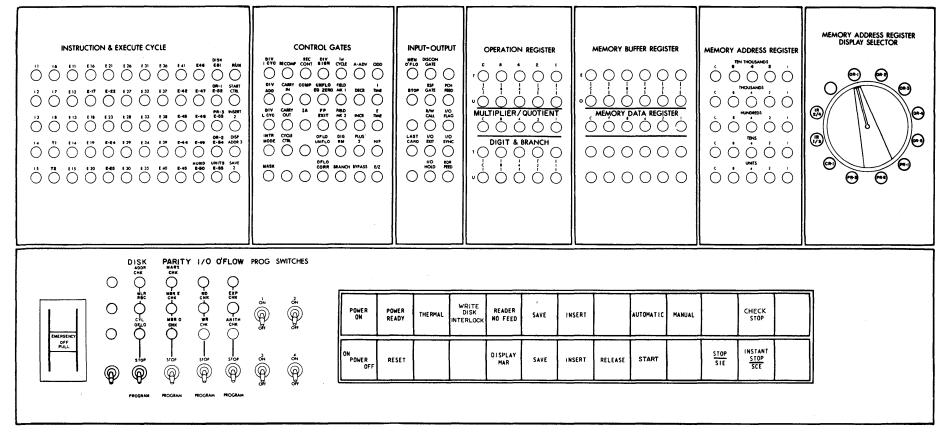

| Switch Cores · · · · · · · · · · · · · · · · 4.2               | SECTION 6 CONSOLE AND CE PANEL 6.1                           |

| Component Circuits · · · · · · · · · · · · · · 4. 2            |                                                              |

| AFR Card · · · · · · · · · · · · · · · · · 4.5                 | Console • • • • • • • • • • • • • • • • • • •                |

| AHK, CAB, CD, DAW, DAX, MX, TAG, TAH, VE,                      | Register Displays • • • • • • • • • • • • • • • 6. 1         |

| and VF Cards · · · · · · · · 4.6                               | Machine Check Trigger Lights • • • • • • • 6.1               |

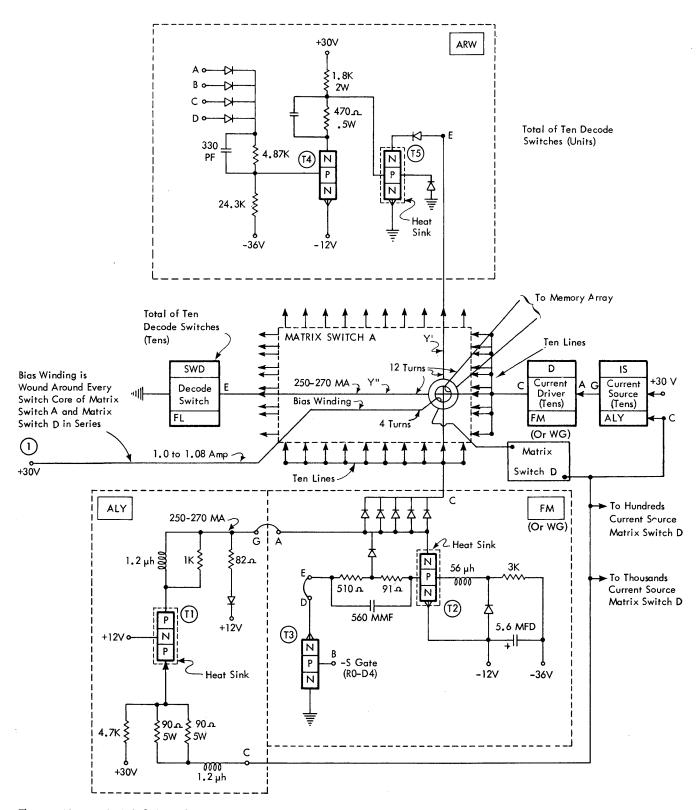

| ALY, ARW and FM Cards 4.7                                      | Machine Timer Trigger, Auxiliary Trigger, and                |

| AYX Cards · · · · · · · · · · · · · · · · · · ·                | Control Gate Lights · · · · · · · · 6.3                      |

| CAU and DFD Cards · · · · · · · · · · · 4.10                   | Switches · · · · · · · · · · · · · · · · · · ·               |

| CEYB Card 4, 10                                                | Control Keys · · · · · · · · 6.4                             |

| DEQ Card 4.10                                                  | Signal Lights · · · · · · · · · · · · · · · 6.10             |

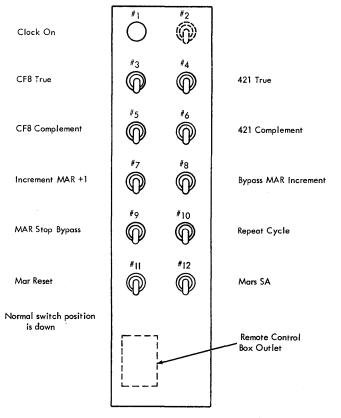

| DES Card 4.11                                                  | Customer Engineering Panel · · · · · · · · · · · 6.11        |

| DEV Card 4.11                                                  | CE Switch Functions · · · · · · · · · · · 6.12               |

| DEW Card 4.11                                                  |                                                              |

| DFB Card 4.11                                                  | SECTION 7 INSTRUCTION CYCLE · · · · · · · · 7.               |

| DFC Card 4.11                                                  | •                                                            |

| DFE Card 4.12                                                  | Objectives · · · · · · · · · · · · · · · · · · ·             |

| DFG Card 4.12                                                  | Functions · · · · · · · · · · · · · · · · · · ·              |

| DFP Card 4.13                                                  | Auxiliary Triggers · · · · · · · · · · · · 7.4               |

| MH Card 4.13                                                   | I-Timer Triggers · · · · · · · · · · · · · · · 7.4           |

| NN Card 4.13                                                   |                                                              |

| NP Card ····· 4.14                                             | SECTION 8 EXECUTION CYCLE 8.1                                |

| QU Cards · · · · · · · 4.14                                    |                                                              |

| RE Card · · · · · · 4.14                                       | Objective · · · · · · · · · · · · · · · · · · ·              |

| TAF Card · · · · · · · 4.14                                    | Functions · · · · · · · · 8.1                                |

| TAJ Card · · · · · · · 4.14                                    | E-Timer Triggers · · · · · · · · 8.1                         |

| TAL Card 4.16                                                  | Auxiliary Triggers · · · · · · · · · · · · 8.1               |

| TC7 Cards 4 16                                                 | Functions of Anviliant Triggors                              |

| Read-Y Point · · · · · · · · · · · · · · · · · · ·                                | 8.4   | Branch No Record Mark (Code 45 - BRN) • • • • • • • • •                   | 10.6           |

|-----------------------------------------------------------------------------------|-------|---------------------------------------------------------------------------|----------------|

| Block Memory Sense Amplifiers · · · · · · · · · · · · · · · · · · ·               | 8.5   | Objectives • • • • • • • • • • • • • • • • • • •                          | 10.6           |

| Significance of P & Q Parts of Instructions · · · · · · · · · · · · · · · · · · · |       | Functions                                                                 | 10.6           |

|                                                                                   |       | Auxiliary Trigger Status                                                  | 10.6           |

| SECTION 9 INTERNAL TRANSMISSION OPERATIONS · · · ·                                | 9.1   | E-Timer Trigger Objectives                                                |                |

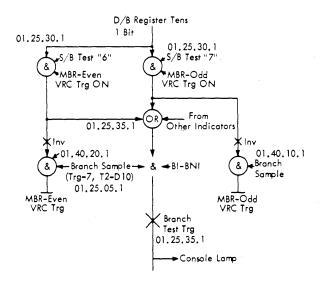

|                                                                                   |       | Branch Indicator (Code 46-BI) · · · · · · · · · · · · · · · · · · ·       |                |

| Transmit Digit (Code 25 - TD) · · · · · · · · · · · · · · · · · · ·               | 9.1   | Objectives                                                                |                |

| Objective · · · · · · · · · · · · · · · · · · ·                                   | 9.1   | Functions                                                                 |                |

| Functions                                                                         | 9.1   | Auxiliary Trigger Status                                                  |                |

|                                                                                   |       | E-Timer Trigger Objectives · · · · · · · · · · · · · · · · · · ·          |                |

| Auxiliary Triggers                                                                | 9.1   |                                                                           |                |

| E-Timer Trigger Objectives · · · · · · · · · · · · · · · · · · ·                  |       | Branch No Indicator (Code 47 - BNI) · · · · · · · · · · · · · · · · · · · |                |

| Transmit Digit Immediate (Code 15 - TDM) · · · · · · · · · · · · · · · · · · ·    |       | Objectives • • • • • • • • • • • • • • • • • • •                          |                |

| Objective ••••••••                                                                | 9.1   | Functions                                                                 |                |

| Functions                                                                         |       | Auxiliary Trigger Status                                                  |                |

| Auxiliary Triggers · · · · · · · · · · · · · · · · · · ·                          |       | E-Timer Trigger Objectives •••••••••                                      | 10.9           |

| E-Timer Objectives · · · · · · · · · · · · · · · · · · ·                          |       |                                                                           |                |

| Transmit Field (Code 26 - TF) · · · · · · · · · · · · · · · · · · ·               | 9.2   | SECTION 11 INPUT/OUTPUT OPERATIONS · · · · · · · · ·                      | 11.1           |

| Objective · · · · · · · · · · · · · · · · · · ·                                   | 9.2   |                                                                           |                |

| Functions · · · · · · · · · · · · · · · · · · ·                                   | 9.2   | General · · · · · · · · · · · · · · · · · · ·                             | 11.1           |

| Auxiliary Trigger Status • • • • • • • • • • • • • • • • • • •                    | 9.2   | Typewriter                                                                | 11.1           |

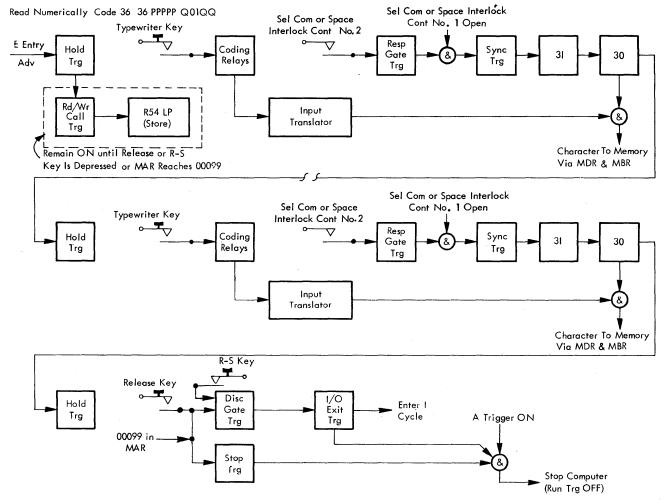

| E-Timer Trigger Objectives · · · · · · · · · · · · · · · · · · ·                  |       | Read Numerically (Code 36 - RN)                                           |                |

| Transmit Field Immediate (Code 16 - TFM) • • • • • • • •                          |       | Objectives                                                                |                |

| Objective · · · · · · · · · · · · · · · · · · ·                                   |       | Functions                                                                 |                |

| Functions · · · · · · · · · · · · · · · · · · ·                                   |       | Auxiliary Trigger Status                                                  |                |

| Auxiliary Triggers Status • • • • • • • • • • • • • • • • • • •                   |       | E-Timer Trigger Objectives · · · · · · · · · · · · · · · · · · ·          |                |

| E-Timer Triggers · · · · · · · · · · · · · · · · · · ·                            |       | Relay Functions                                                           |                |

|                                                                                   |       | ·                                                                         |                |

| Transmit Record (Code 31 - TR) · · · · · · · · · · · · · · · · · · ·              | 9.3   | Read Alphamerically (Code 37 - RA) · · · · · · · · · · · · · · · · · · ·  |                |

| Objective · · · · · · · · · · · · · · · · · · ·                                   | 9.3   | Objectives                                                                |                |

| Functions                                                                         | 9.3   | Functions                                                                 |                |

| Auxiliary Trigger Status • • • • • • • • • • • • • • • • • • •                    | 9.3   | Auxiliary Trigger Status • • • • • • • • • • • • • • • • • • •            |                |

| E-Timer Trigger Objectives · · · · · · · · · · · · · · · · · · ·                  | 9.4   | E-Timer Trigger Objectives • • • • • • • • • • • • • • • • • • •          |                |

|                                                                                   |       | Relay Functions                                                           |                |

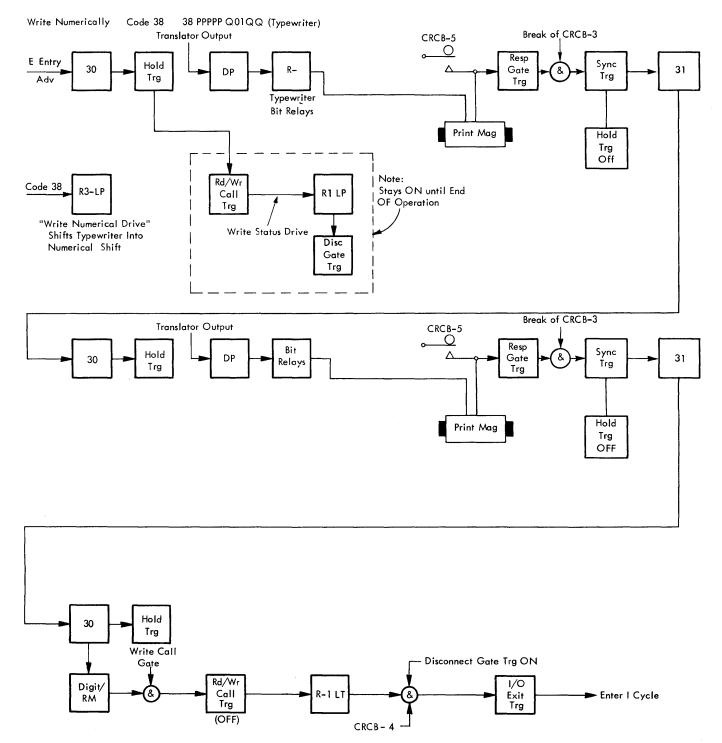

| SECTION 10 BRANCH OPERATIONS · · · · · · · · · · · · · · · · · · ·                | 10, 1 | Write Numerically (Code 38 - WN) · · · · · · · · · · · · · · · · · · ·    | 11.10          |

|                                                                                   |       | Objectives • • • • • • • • • • • • • • • • • • •                          | 11.10          |

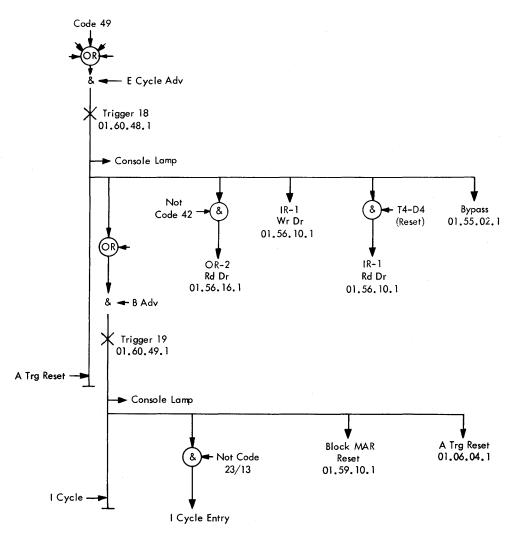

| Branch (Code 49 - B) · · · · · · · · · · · · · · · · · ·                          | 10.1  | Functions                                                                 | 11.10          |

| Objective · · · · · · · · · · · · · · · · · · ·                                   | 10.1  | Auxiliary Trigger Status                                                  | 11. 12         |

| Functions · · · · · · · · · · · · · · · · · · ·                                   | 10.1  | E-Timer Trigger Objectives • • • • • • • • • • • • • • • • • • •          |                |

| Auxiliary Triggers • • • • • • • • • • • • • • • • • • •                          | 10.1  | Relay Functions • • • • • • • • • • • • • • • • • • •                     |                |

| E-Timer Trigger Objectives · · · · · · · · · · · · · · · · · · ·                  | 10.1  | Dump Numerically (Code 35 - DN) · · · · · · · · · · · · · · · · · · ·     |                |

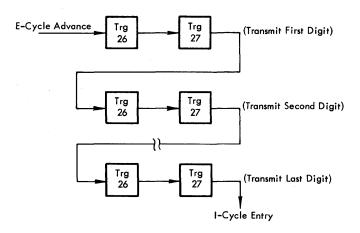

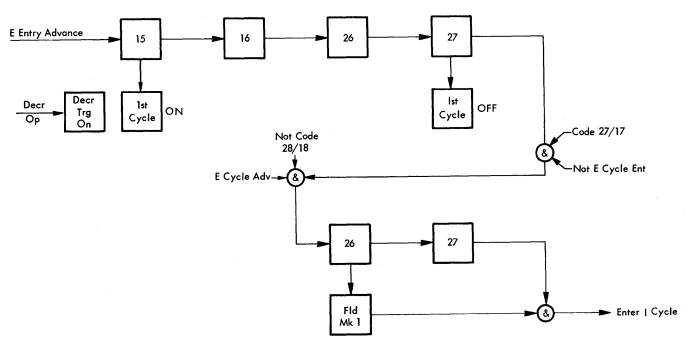

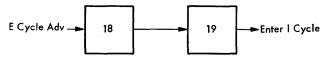

| Branch and Transmit (Code 27 - BT) · · · · · · · · · · · · · · · · · · ·          | 10. 1 | Objectives · · · · · · · · · · · · · · · · · · ·                          |                |

| Objective · · · · · · · · · · · · · · · · · · ·                                   | 10, 1 | Functions                                                                 |                |

| Functions                                                                         |       | Auxiliary Trigger Status · · · · · · · · · · · · · · · · · · ·            |                |

|                                                                                   | 10.2  |                                                                           |                |

| Auxiliary Trigger Status •••••••                                                  | 10.2  | E-Timer Trigger Objectives · · · · · · · · · · · · · · · · · · ·          |                |

| E-Timer Trigger Objectives                                                        | 10.2  | Write Alphamerically (Code 39 - WA) · · · · · · · · · ·                   | 11.18          |

| Branch and Transmit Immediate (Code 17 -BTM) • • • • • •                          | 10.3  | Objectives · · · · · · · · · · · · · · · · · · ·                          |                |

| Objectives · · · · · · · · · · · · · · · · · · ·                                  | 10.3  | Functions • • • • • • • • • • • • • • • • • • •                           |                |

| Functions                                                                         | 10.3  | Auxiliary Trigger Status ••••••••••••••••••••••••••••••••••••             | 11. <b>1</b> 9 |

| Auxiliary Triggers · · · · · · · · · · · · · · · · · · ·                          |       | E-Timer Trigger Objectives                                                |                |

| E-Timer Triggers · · · · · · · · · · · · · · · · · · ·                            |       | Relay Functions                                                           | 11.19          |

| Branch Back (Code 42-BB) · · · · · · · · · · · · · · · · · ·                      | 10.3  | Parity Checking Write Operations                                          | 11.20          |

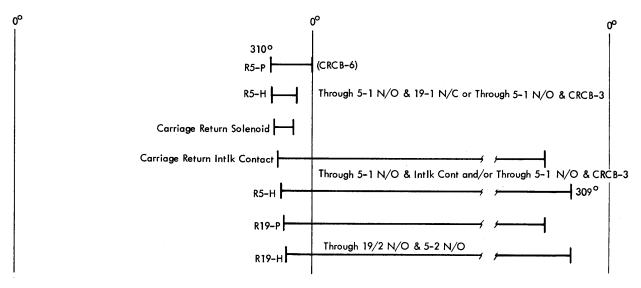

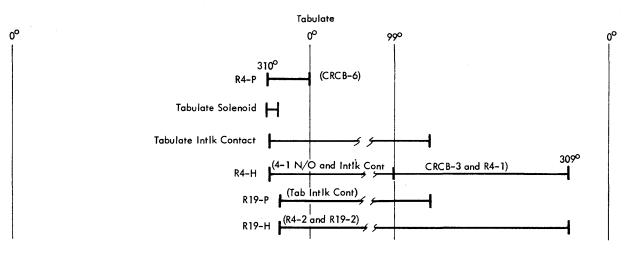

| Objectives · · · · · · · · · · · · · · · · · · ·                                  |       | End-of-Line Carriage Return · · · · · · · · · · · · · · · · · · ·         | 11.23          |

| · ·                                                                               | 10.3  | Single-Cycle Operation · · · · · · · · · · · · · · · · · · ·              | 11.23          |

| Auxiliary Trigger Status                                                          |       | Control (Code 34 - K)                                                     | 11.24          |

| E-Timer Trigger Objectives                                                        |       | Objective · · · · · · · · · · · · · · · · · · ·                           |                |

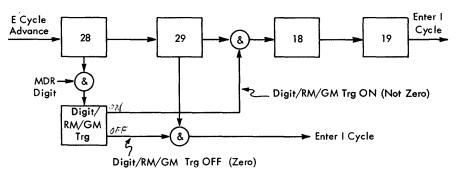

| Branch on Digit (Code 43 - BD)                                                    |       | Functions                                                                 |                |

|                                                                                   |       | Auxiliary Trigger Status · · · · · · · · · · · · · · · · · · ·            |                |

| Objectives                                                                        |       | E-Timer Trigger Objectives                                                |                |

| Functions                                                                         |       |                                                                           |                |

| Auxiliary Trigger Status                                                          |       | Relay Functions                                                           | 11.23          |

| E-Timer Trigger Status                                                            |       |                                                                           | 40.4           |

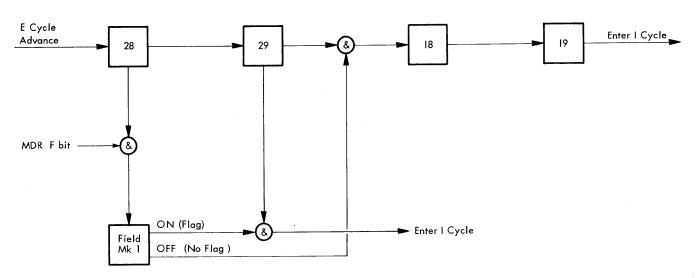

| Branch No Flag (Code 44 - BNF)                                                    |       | SECTION 12 MISCELLANEOUS OPERATIONS                                       | 12.1           |

| Objectives                                                                        | 10.5  |                                                                           |                |

| Functions                                                                         | 10.5  | Set Flag                                                                  |                |

| Auxiliary Trigger Status                                                          | 10.5  | Objective                                                                 |                |

| E-Timer Trigger Objectives                                                        | 10.5  | Functions                                                                 | 12. 1          |

| Auxiliary Triggers • • • • • • • • • 12.1                     | Subtract Immediate (Code 12 - SM) · · · · · · · · · · · 13.1   |

|---------------------------------------------------------------|----------------------------------------------------------------|

| E-Timer Trigger Objectives · · · · · · · · · · · · · 12.1     | Objective • • • • • • • • • • • • • • • • • • •                |

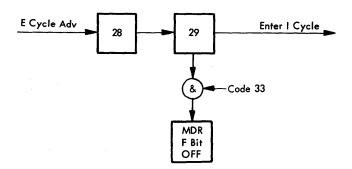

| Clear Flag (Code 33 - CF) · · · · · · · · · · · · 12.1        | Functions · · · · · · · · · · · · · · · · · · ·                |

| Objective · · · · · · · · · · · · · · · · · · ·               | Auxiliary Triggers ••••••••• 13.1                              |

| Functions · · · · · · · · · · · · · · · · · · ·               | E-Timer Triggers · · · · · · · · · · · · · · · · · 13.1        |

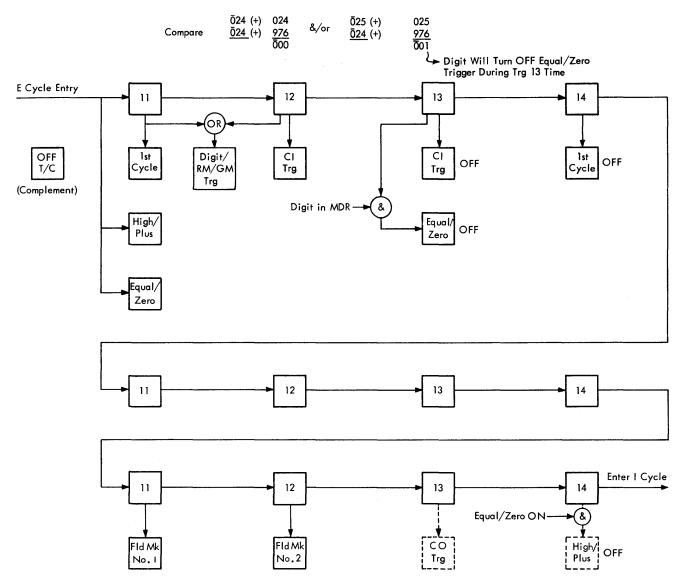

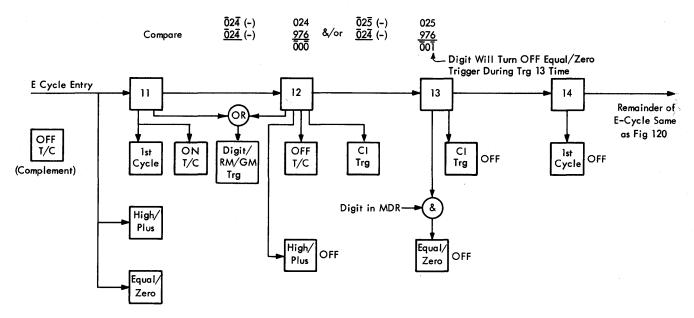

| Auxiliary Triggers · · · · · · · · · · · · · · · 12.2         | Compare (Code 24 - C)                                          |

| E-Timer Trigger Objectives · · · · · · · · · · · 12.2         | Objective • • • • • • • • • • • • • • • • • • •                |

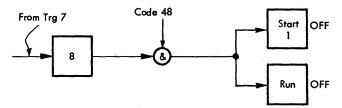

| Halt (Code 48 - H) 12.2                                       | Functions                                                      |

| Objective • • • • • • • • • • • • • • 12.2                    | Resulting Indicator Conditions                                 |

| Function • • • • • • • • • • • • • • 12.2                     | Auxiliary Trigger Status • • • • • • • • • • • • • • • • 13.1  |

| Auxiliary Triggers · · · · · · · · · · · · · · · · 12.2       | Sign Analysis · · · · · · · · · · · · · · · · · ·              |

| E-Timer Triggers · · · · · · · · · · · · · · · · · · 12.2     | E-Timer Trigger Objectives • • • • • • • • • • • 13.1          |

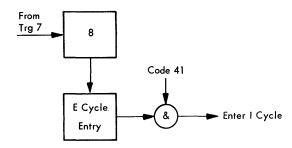

| No Operation (Code 41 - NOP) · · · · · · · · · · · · · · 12.3 | Compare Immediate (Code 14 - CM) · · · · · · · · · · 13.1      |

| Objective • • • • • • • • • • • • • • • • • 12.3              | Objective • • • • • • • • • • • • • • • • • • •                |

| Functions 12.3                                                | Functions • • • • • • • • • • • • • • • • • • •                |

| Auxiliary Triggers • • • • • • • • • • • • • • 12.3           | Auxiliary Triggers •••••••••13.1                               |

| E-Timer Triggers · · · · · · · · · · · · · · · 12.3           | E-Timer Triggers • • • • • • • • • • • • • • • • • 13. 1       |

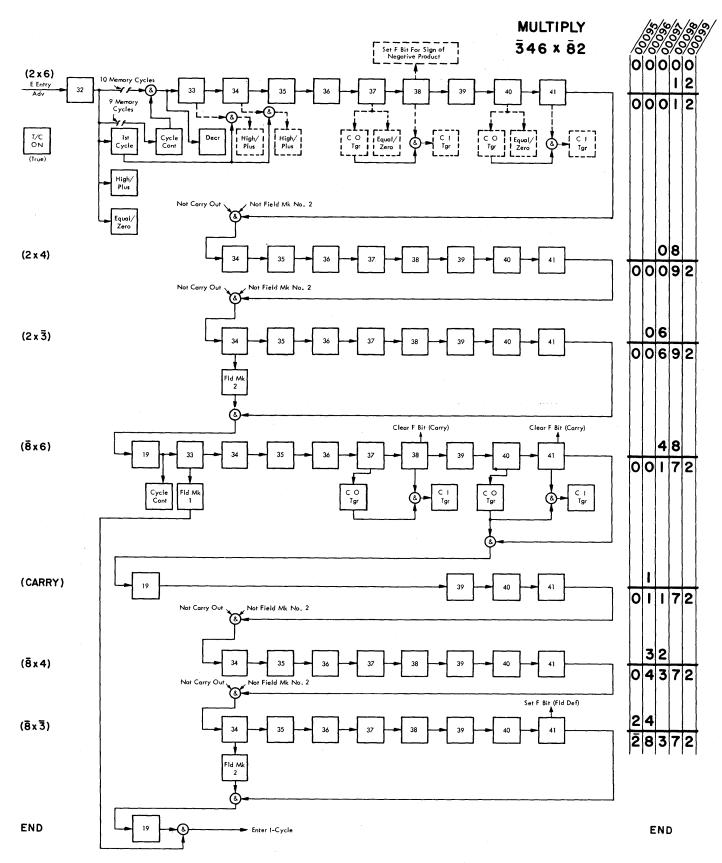

|                                                               | Multiply (Code 23 - M) • • • • • • • • • • • • • • • • 13. 1   |

| SECTION 13 ARITHMETIC OPERATIONS 13.1                         | Objective • • • • • • • • • • • • • • • • • • •                |

|                                                               | Functions · · · · · · · · · · · · · · · · · · ·                |

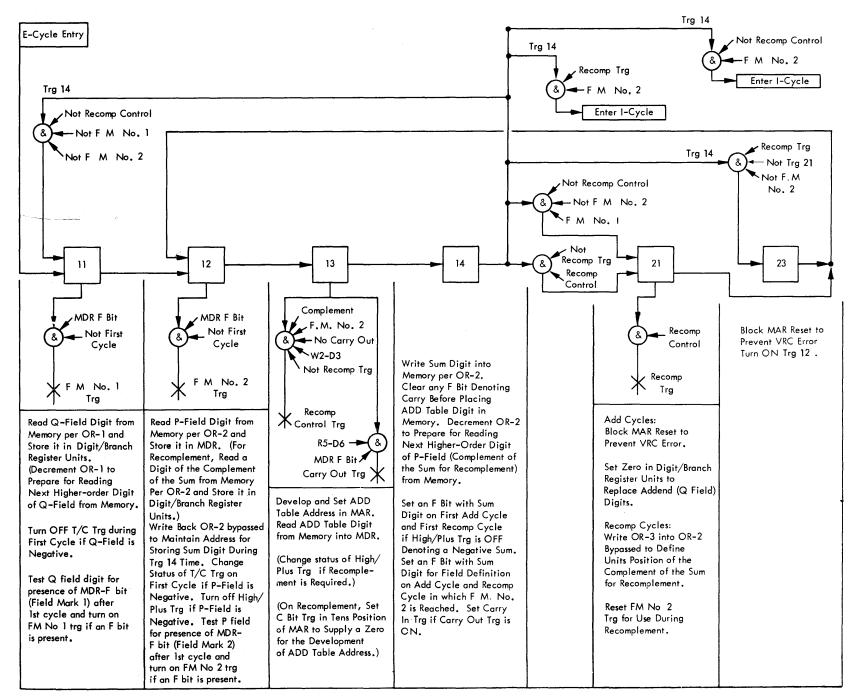

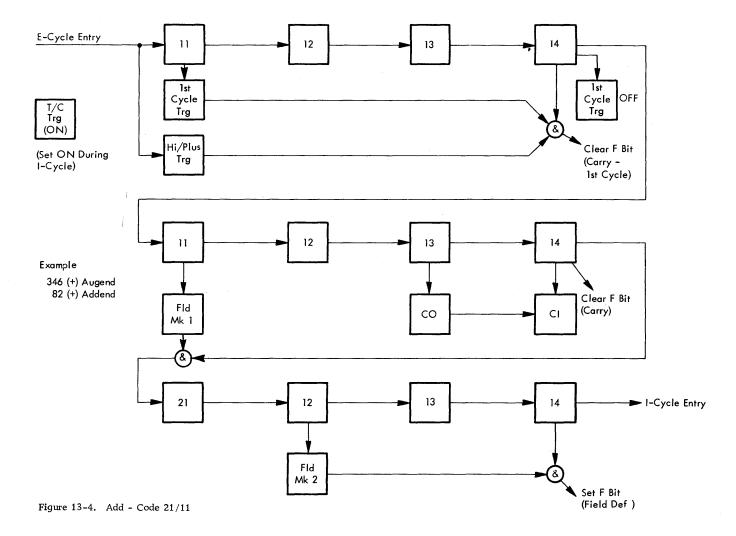

| Add (Code 21 - A)                                             | Resulting Indicator Conditions • • • • • • • • • • • • • 13.2  |

| Objective                                                     | Storage Register Functions • • • • • • • • • • • • • • • 13. 2 |

| Functions                                                     | Auxiliary Trigger Status • • • • • • • • • • • • • • 13.2      |

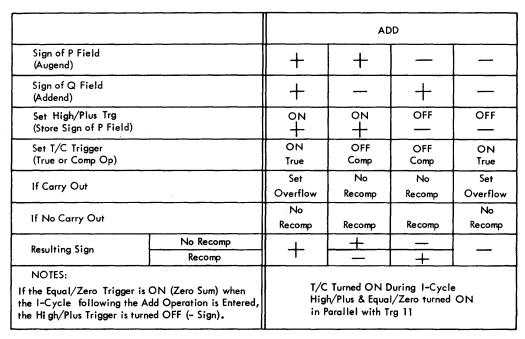

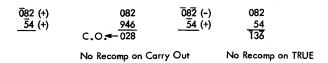

| Resulting Indicator Conditions • • • • • • • • • • 13.2       | E-Timer Trigger Objectives •••••••• 13. 2                      |

| Auxiliary Trigger Status                                      | Multiply Immediate (Code 13 - MM) 13. 2                        |

| Sign Analysis                                                 | Objective • • • • • • • • • • • • • • • • • • •                |

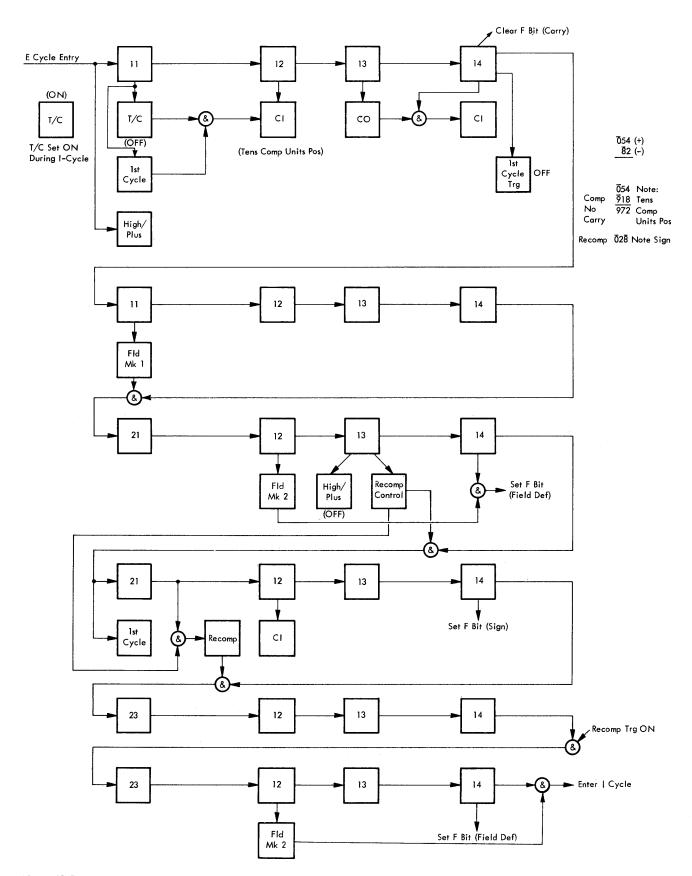

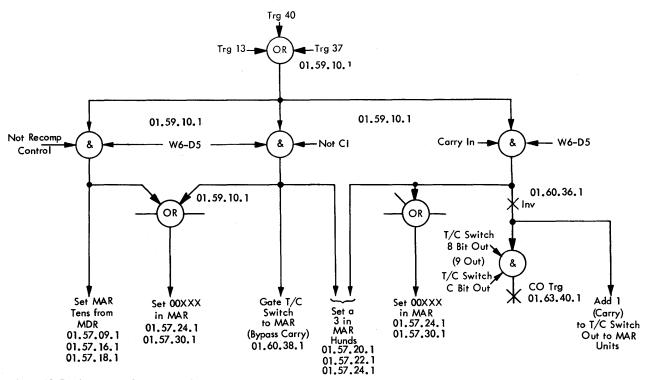

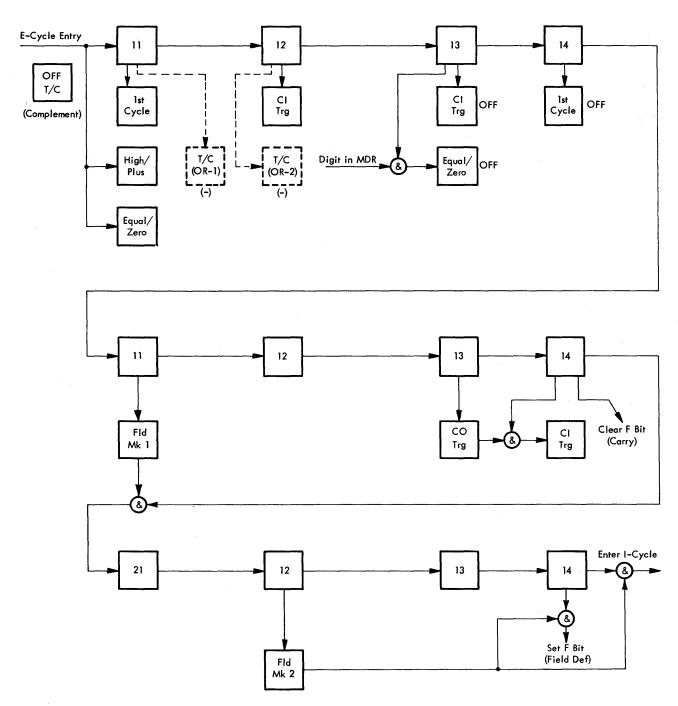

| E-Timer Trigger Objectives 13.6                               | Functions • • • • • • • • • • • • • • • • • • •                |

| Add Immediate (Code 11 - AM) 13.9                             | Auxiliary Triggers ••••••••••••••••••••••••••••••••••••        |

| Objective                                                     | E-Timer Triggers • • • • • • • • • • • • • • • • • • 13. 2     |

| Functions                                                     |                                                                |

| Auxiliary Triggers 13.9                                       |                                                                |

| E-Timer Trigger Objectives 13.9                               | Appendix A Terms and Abbreviations A. 1                        |

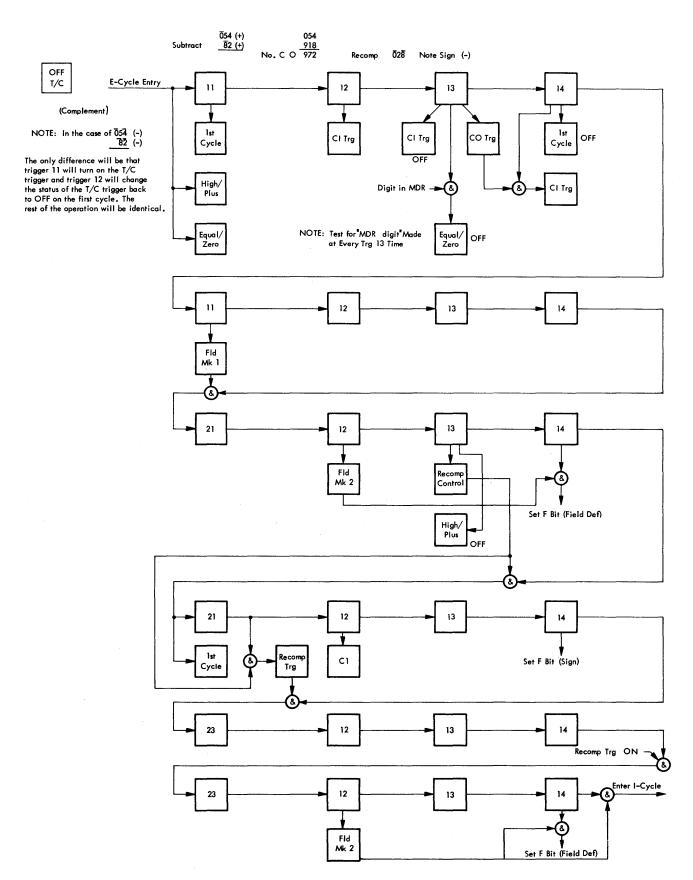

| Subtract (Code 22 - S)                                        | Appendix B Character Code Chart A. 2                           |

| Objective                                                     | Appendix C Numbered Triggers/Latches                           |

| Functions                                                     | Appendix D Named Triggers/Latches                              |

| Resulting Indicator Conditions 13.11                          | Appendix E Register Triggers/Latches                           |

| Auxiliary Trigger Status · · · · · · · · · · · · · · 13.11    | Appendix F E-Timer Trigger Chart                               |

| Sign Analysis · · · · · · · · · · · · · · · · · ·             | Appendix G Auxiliary Trigger Chart                             |

| E-Timer Trigger Objectives · · · · · · · · · · · · · 13.11    | Appendix H Bibliography                                        |

|                                                               | ispersons as Divitoqiapity                                     |

#### PREFACE

This manual, Form 227-5751, describes the IBM 1620 Data Processing System, Model 1 (1620-1), Serial 11550 and up. This manual replaces but does not make obsolete, Form 227-5647-0. Form 227-5647-0 describes the 1620-1 Data Processing System, Serial 10701 to 11550. Additional features associated with the 1620-1 are described in separate Customer Engineering Manuals of Instruction. See Appendix H, Bibliography.

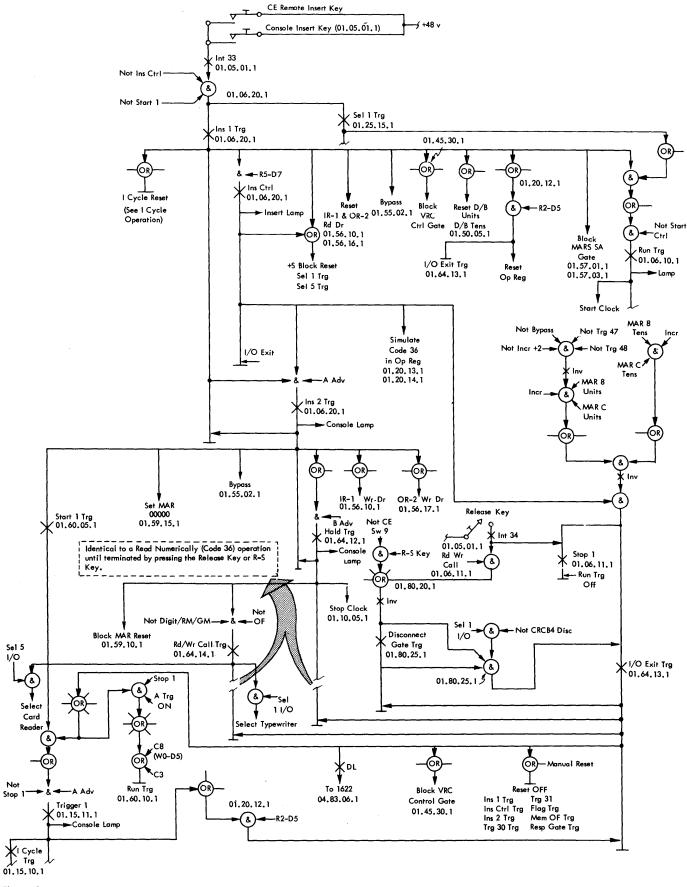

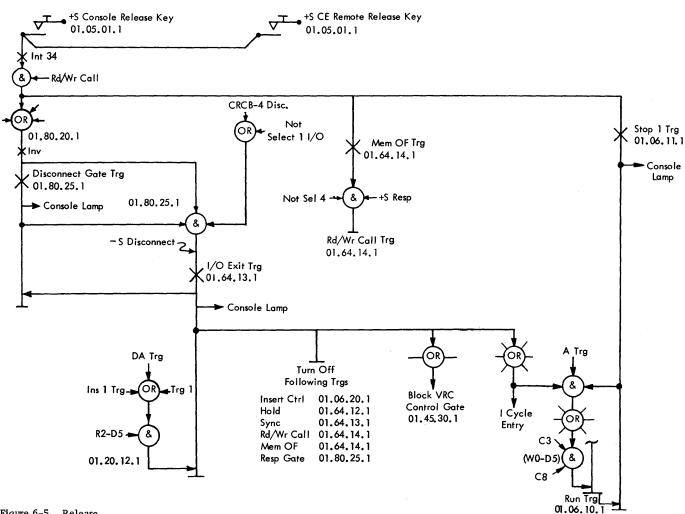

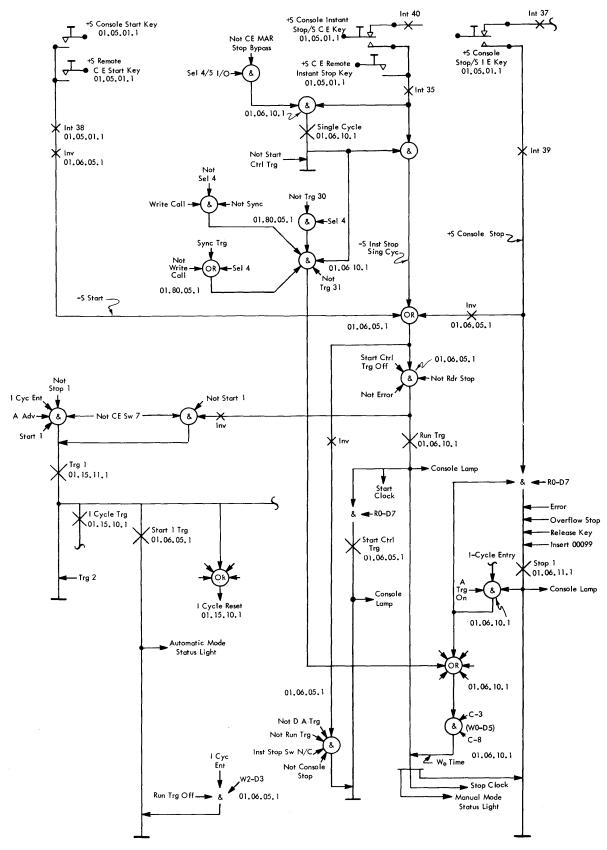

Customer Engineering Instructional System Diagrams for the 1620-1 Data Processing System (including additional features) are in three volumes, (Forms 227-5769, 227-5770, and 227-5771). In addition to the system diagrams, Form 227-5769 contains function charts for the basic 1620-1 features. Form 227-5771 contains function charts of the additional features as well as the system diagrams. Form 227-5770 contains system diagrams only.

# DESCRIPTION OF SYSTEM

The IBM 1620 Data Processing System is an electronic computer system designed for scientific and technological applications. The use of solid state circuit components and the availability of an additional 20,000 or 40,000 positions of core storage to augment the 20,000 positions in the 1620 Model 1 Processing Unit, provides the 1620 System with the capacity, reliability, and speed to solve problems that heretofore have required larger and more expensive data processing systems.

This manual, Form 227-5751, describes the 1620 Model 1 Central Processing Unit with no additional features attached or installed. Additional features available for installation in, or attachment to, the 1620 Central Processing Unit are described in separate Customer Engineering Manuals of Instruction. See Appendix H, Bibliography.

Data and instructions entered into the system are placed in memory as decimal digits. Each of the 20,000 positions of core storage (memory) can be addressed individually by a 5-digit address and can store one digit of information. Memory addresses extend from 00000 to 19999. The addressing system provides for the selection of any digit or group of digits within memory. The 1620 Computer processes numerical, alphabetic and special characters.

The computer is capable of performing more than 30 different standard operations with over 14 special feature operations available. Each operation is specified by a 12-digit instruction which contains a 2-digit operation code and two 5-digit addresses. Instructions comprising a program are normally stored in consecutive locations in memory and executed sequentially. However, the sequence of operations may be altered at any point in the program by conditional branch instructions. Conditional branch instructions make logical decisions by performing tests on indicators or switches set by the computer or the operator.

Arithmetic operations are accomplished by a table addressing method. There are 320 positions of memory assigned for use in arithmetic operations. Of these, 20 positions, 00080 through 00099, are used to store products or quotients, and 200

positions, 00100 through 00299, are assigned for the storage of a Multiply Table. The Multiply Table contains all possible 2-digit products. The remaining 100 positions, 00300 through 00399, are assigned for storage of an Add Table used in all arithmetic operations. The Add Table contains all possible 2-digit sums, with carries indicated. The memory positions containing the table data are addressable.

The 1620 is a variable field length computer. The shortest admissible field is two digits; the longest can be any number of digits within the capacity of memory. Accuracy of data is ensured by the parity check which is made when the data enters, exits, or is manipulated inside the system.

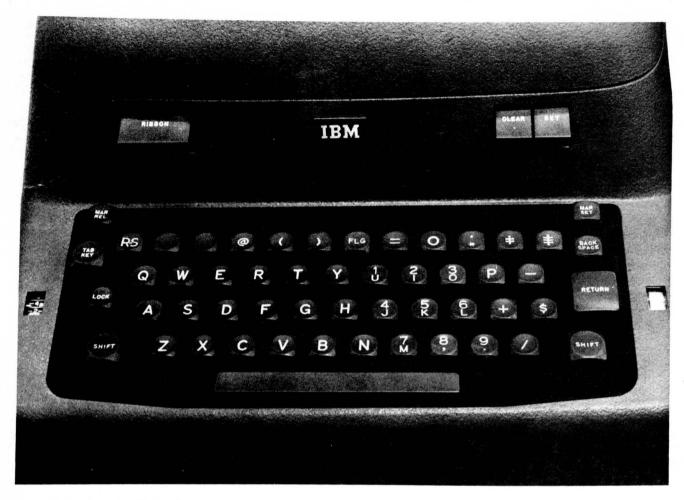

The Console of the 1620 consists of control keys, switches, an indicator panel, and a typewriter. The control keys and switches are used to control operation of the system. The console panel provides a visual indication of the contents of various registers and the status of control circuitry within the computer. The typewriter keyboard is used for manual entry of data and instructions into memory.

Information is entered into the system by the typewriter or by additional feature input or input-output devices. Output data is recorded by the typewriter or by additional feature output or input-output devices.

When the computer is reading from or writing on an input-output device and is in the numerical mode, each character received from or sent to the input-output device is represented in memory as a single digit and occupies one memory position. In the numerical mode, data must consist of numerical characters only. When the computer is reading from or writing on an input-output device and is in the alphameric mode, each character received from or sent to the input-output device is represented in memory as two digits occupying two adjacent memory positions. In the alphameric mode, data may consist of numerical, alphabetic, and special characters. The digits for numerical characters, in the alphameric mode, consist of an arbitrarily assigned digit (zone digit) and a second digit (numerical digit) represented by two arbitrarily assigned digits.

Figures 1-1 and 1-2 illustrate all characters and their assigned digital values for both numerical and alphameric modes.

| Character    | Input      | ut Core Storage |        | Output               |

|--------------|------------|-----------------|--------|----------------------|

| Character    | Typewriter | Zone            | Num    | Typewriter           |

| (Blank)      | (Space)    |                 | С      | 0                    |

| 0 (+)        | 0          |                 | U      | 0                    |

| 0 (-)        | ō          |                 | F      | 0                    |

| 1-9 (+)      | 1-9        |                 | 1-9    | 1-9                  |

| 1-9 (-)      | ī-9        |                 | F, 1-9 | 1-9                  |

| +            | ‡          |                 | C82    | ‡ (Stop, WN)<br>(DN) |

| ‡            | Ŧ          |                 | F82    | Ŧ                    |

| Num<br>Blank | @          |                 | C84    | . @                  |

Figure 1-1. Character Coding, Numerical

| Classication | Input      | Core S | torage | Output     |

|--------------|------------|--------|--------|------------|

| Character    | Typewriter | Zone   | Num    | Typewriter |

| (Blank)      | (Space)    | U      | U      | (Space)    |

| . (Period)   | •          | С      | 3      | •          |

| )            | )          | С      | 4      | )          |

| +            | +          | 1      | С      | +•         |

| \$           | \$         | 1      | 3      | \$         |

| *            | *          | 1      | 4      | *          |

| - (Hyphen)   | -          | 2      | С      | -          |

| /            | /          | 2      | 1      | /          |

| , (Comma)    | ,          | 2      | 3      | ,          |

| (            | (          | 2      | 4      | (          |

| =            | =          | 3      | 3      | =          |

| @            | @          | 3      | 4      | @          |

| A-I          | A-I        | 4      | 1-9    | A-I        |

| 0 (—)        | (None)     | 5      | С      | - (Hyphen) |

| J-R          | J-R        | 5      | 1-9    | J-R        |

| 1-9 (-)      | J-R        | 5      | 1-9    | J-R        |

| S-Z          | S-Z        | 6      | 2-9    | S-Z        |

| 0 (+)        | 0          | 7      | С      | 0          |

| 1-9 (+)      | 1-9        | . 7    | 1-9    | 1-9        |

| #            | #          | С      | C82    | (Stop)     |

Figure 1-2. Character Coding, Alphamerical

### MACHINE LANGUAGE

#### Character Code

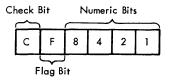

All data stored, transferred, and processed within the computer is represented as decimal digits in Binary Coded Decimal (BCD) form. A digit is represented by a particular combination of bits. The bit positions of each digit consist of four numerical bits (8, 4, 2, and 1), one flag (F) bit, and one check (C) bit (Figure 1-3). The value of a significant digit is the sum represented by the bits present in the 8, 4, 2, and 1 numerical bit positions. A zero is represented by a C-bit alone. Only bit combinations whose sum is nine or less are used. Considering only the numerical bit positions, the digit-6 is represented by a 4-bit and a 2-bit; the digit-7 by a 4-bit, a 2-bit, and a 1-bit; and the digit-8 by an 8-bit alone (Figure 1-4).

Figure 1-3. Bit Positions

Figure 1-4. Bit Configuration - Decimal Digits 0-9

The flag (F) bit is used in three ways. The presence or absence of the flag bit in the units position of a numerical field determines the sign of the field. Absence of the flag bit is interpreted as a

field signed plus. The presence of the flag bit is interpreted as a field signed minus. The flag bit is also used as a field mark defining the high-order position of a numerical field. A flag bit with a digit of the Add Table indicates a carry in arithmetic operations.

The C-bit is used for parity checking purposes. Each digit within the computer must consist of an odd total number of bits, or a parity error will be indicated. The C-bit will be present in a digit when the number of bits present in the numerical bit positions and the F-bit position consists of an even number of bits.

A special combination consisting of the C-bit, 8-bit, and 2-bit is used as a record mark.

#### Instruction Format

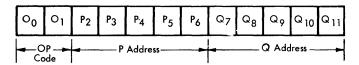

The IBM 1620 uses a 12-digit instruction divided into three parts; a 2-digit operation code, a 5-digit "P-part," and a 5-digit "Q-part" (Figure 1-5).

Figure 1-5. Instruction Format

The operation codes consist of two digits (00 through 99) which specify the operation to be performed. Figure 1-6 is a chart of operation codes and their associated mnemonics.

The functions of the P and Q-parts of an instruction are dependent upon the particular operation to be performed. The P-part of an instruction can represent the address in memory of a digit, a field, a record, or another instruction. The Q-part can represent the address in memory of a digit, field, or record; a data field itself; the "address" of an input-output device; the control function to be performed by an input-output device together with the "address" of the device; or the code for a switch or indicator. The specific use of the P and Q-parts will be described with each operation.

# Data Format

Data is stored in memory to form fields or records that can be of any length within the capacity of memory. Data can be classified as digits, fields or

| Arithmetic Instructions:               | MNEMONIC | CODE |

|----------------------------------------|----------|------|

| Add                                    |          |      |

| Add Immediate                          |          |      |

| Subtract                               |          |      |

| Subtract Immediate                     |          |      |

| Compare                                | c        | 24   |

| Compare Immediate                      | СМ       | 14   |

| Multiply                               | M        | 23   |

| Multiply Immediate                     | MM       | 13   |

| Internal Data Transmission Instruction |          |      |

| Transmit Digit                         | TD       | 25   |

| Transmit Digit Immediate               |          |      |

| Transmit Field                         | TF       | 26   |

| Transmit Field Immediate               |          |      |

| Transmit Record                        | TR       | 31   |

| Branch Instructions:                   |          |      |

| Branch                                 | B        | 49   |

| Branch No Flag                         | BNF      | 44   |

| Branch No Record Mark                  |          |      |

| Branch On Digit                        | BD       | 43   |

| Branch Indicator                       | BI       | 46   |

| Branch No Indicator                    | BNI      | 47   |

| Branch and Transmit                    | BT       | 27   |

| Branch and Transmit Immediate_         | BTM      | 17   |

| Branch Back                            | BB       | 42   |

| Input-Output Instructions:             |          |      |

| Read Numerically                       | RN       | 36   |

| Write Numerically                      | WN       | 38   |

| Dump Numerically                       | DN       | 35   |

| Read Alphamerically                    | RA       | 37   |

| Write Alphamerically                   | WA       | 39   |

| Control                                | K        | 34   |

| Miscellaneous Instructions:            |          |      |

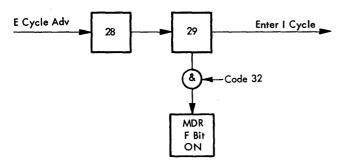

| Set Flag                               | SF       | 32   |

| Clear Flag                             | CF       | 33   |

| Halt                                   | H        | 48   |

| No Operation                           | NOP      | 41   |

Figure 1-6. Operation Codes and Mnemonics

records depending upon how they are addressed and the limiting factor of the data.

A digit occupies one memory position and is addressed individually.

Fields in memory consist of a number of consecutive digits and are composed of data related to arithmetic operations and internal field transmission. A field is addressed by its rightmost (low-order) position which occupies the highest numbered memory position of the field. Fields are processed from right to left into successively lower memory positions until a digit with a flag bit is sensed. The shortest admissible field consists of two digits, the addressed digit and the adjacent digit containing the field definition flag bit. Numerical fields are signed minus by a flag bit present in the units position. The absence of a

flag bit in the units position is interpreted as a field signed plus.

A record in memory consists of a field or fields of data related to input-output operations and internal record transmission. A record in memory is addressed at the leftmost (high-order) position, which occupies the lowest numbered memory position of the record. Records are processed serially from left to right into successively higher memory positions. Output and internal record transmission operations are terminated whenever a record mark is sensed. For memory to receive a record, data is entered starting at the addressed position and continuing from left to right into successively higher memory locations until terminated by an end-of-record signal from the input unit.

#### STORED PROGRAM CONCEPT

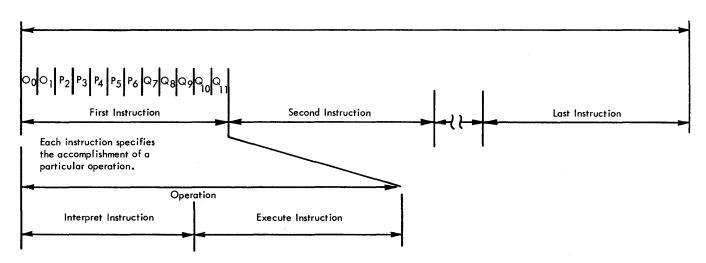

To solve a problem or to process data, a programmer selects from the different operations which the system is capable of performing, those which are required to accomplish the desired results. The series of instructions which designate the operations to be performed is called a program. Because the instructions comprising a program are written into memory from an input device and read from memory for interpretation and execution, the 1620 is called a stored program computer.

For interpretation by the computer, an instruction must be read from memory to registers, starting with the high-order digit and continuing through successively higher memory locations until all 12 digits have been read.

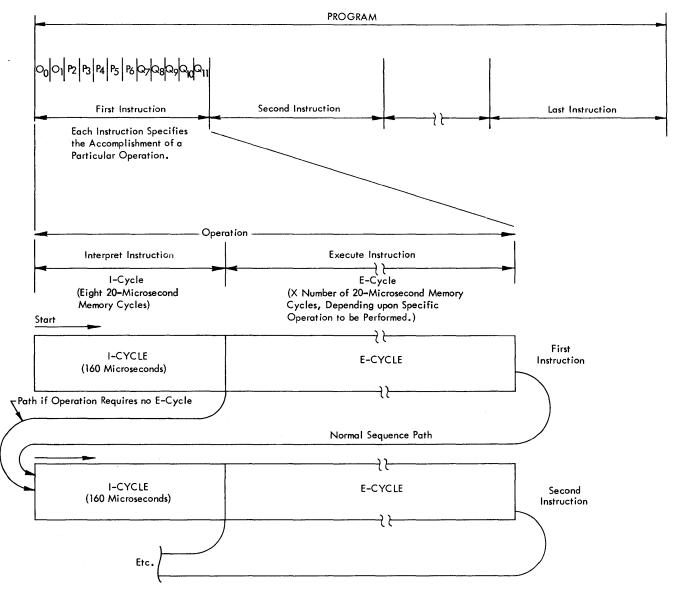

Instructions within a program are normally interpreted and executed sequentially; that is, execution of the first instruction is followed by interpretation and execution of the second instruction, etc. (Figure 1-7). However, this sequence can be altered by the use of conditional branch instructions that direct the computer to an instruction located at other than the next sequential position.

Additional instructions and/or data may be inserted into memory from an input device during the solution of a problem.

The only distinction between instructions and data, in memory, is the manner in which they are interpreted by the computer. If for any reason data was placed in memory locations assigned to instructions, the data would be acted upon as instructions. Conversely, the operation code or either address part of an instruction may be modified by treating the instruction parts as data. Flag bits may be stored with the digits of an instruction to permit operation on the instruction as data. The flag bits are ignored during interpretation of the instruction except when Indirect Addressing, an additional feature, is installed in the 1620.

Figure 1-7. Program

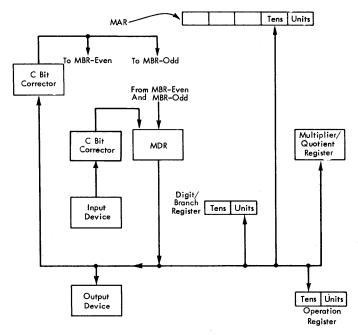

Figure 2-1. Data Flow

#### INTRODUCTION

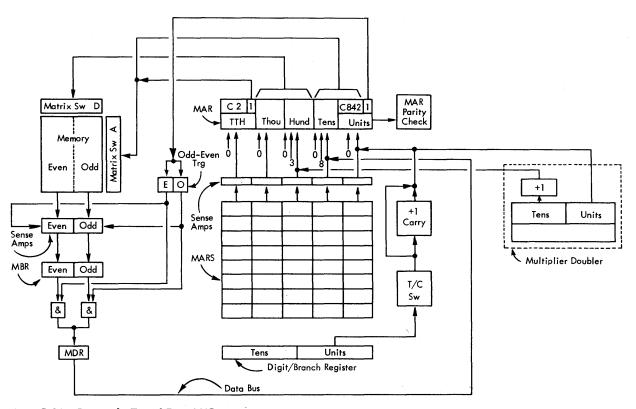

The IBM 1620 Computer normally processes data serially-by-digit, parallel-by-bit. However, the two digits which are read from memory for each address, are processed simultaneously under certain conditions.

Data, as such, is confined to Memory, Memory Buffer Register (MBR), Memory Data Register (MDR), and Input-Output areas. Digits of data which are presented to other registers by MBR and/or MDR are used to develop memory addresses or to control program execution.

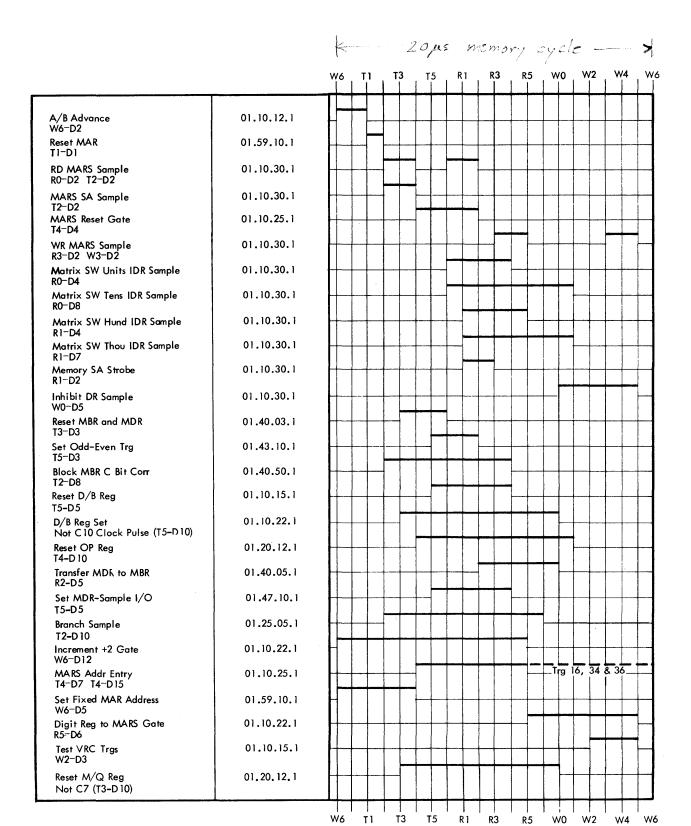

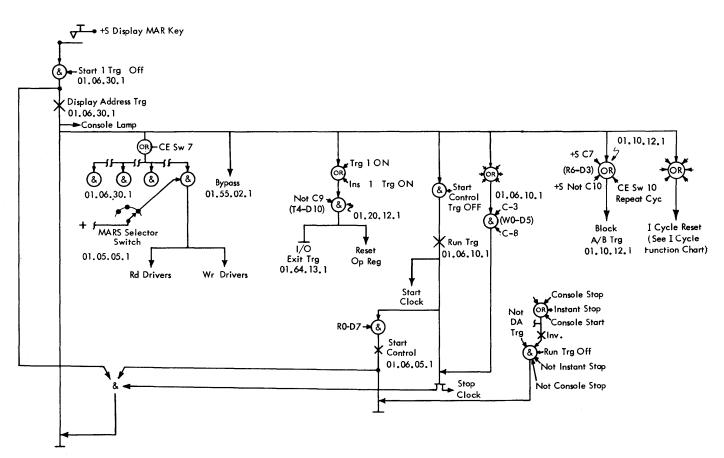

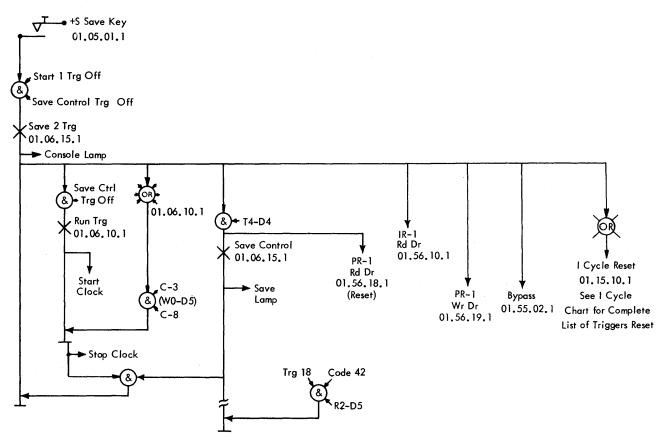

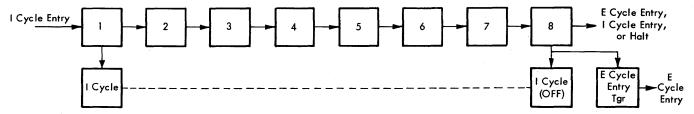

Each instruction of a program is interpreted and executed by a series of machine cycles. A machine cycle consists essentially of: addressing memory, reading out of a memory location, and writing into a memory location. Digits read from memory, that are to be used for addressing or control purposes, are set into registers from MBR and/or MDR within the cycle. Digits are presented to an output device or received from an input device within the machine cycle.

NOTE: The original design concepts of this system made extensive use of triggers. Therefore the functional nomenclature chosen included the term trigger (Trigger 21, First Cycle trigger, I-cycle trigger). Subsequent engineering changes have replaced all triggers with latches except in three cases. The True/Complement, High/Plus, and Clock Drive triggers are still binary connected triggers. The system diagrams still maintain the original "trigger" designation for many of the latches and line names. For this reason the terms trigger and latch are generally used synonymously throughout this manual. These terms are not intended to designate the actual type of component used. The functions of SMS card types used in the 1620 System are given in Section 4 of this manual.

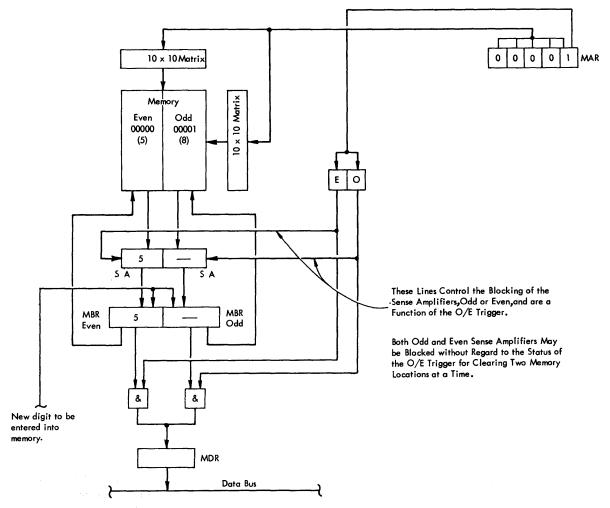

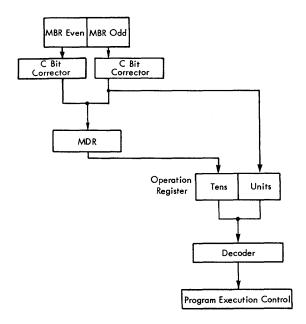

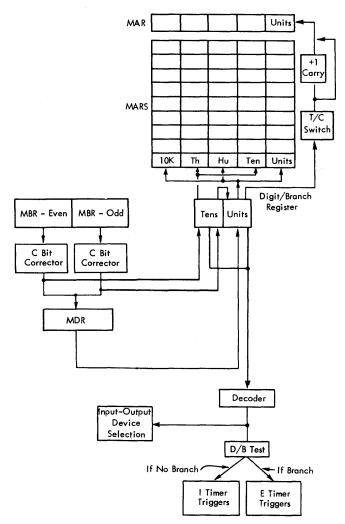

Refer to Figure 2-1 for the following discussion of data flow.

#### **MEMORY**

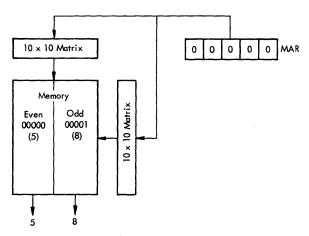

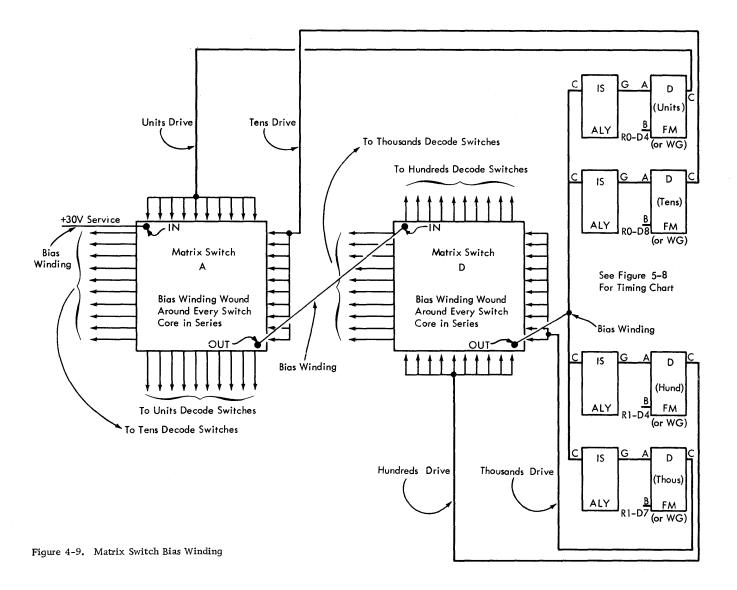

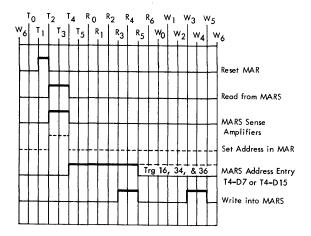

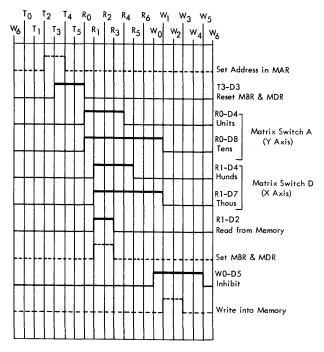

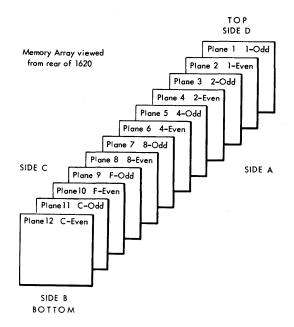

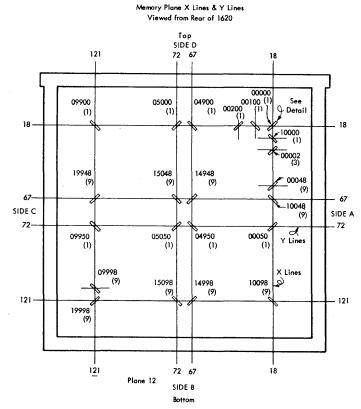

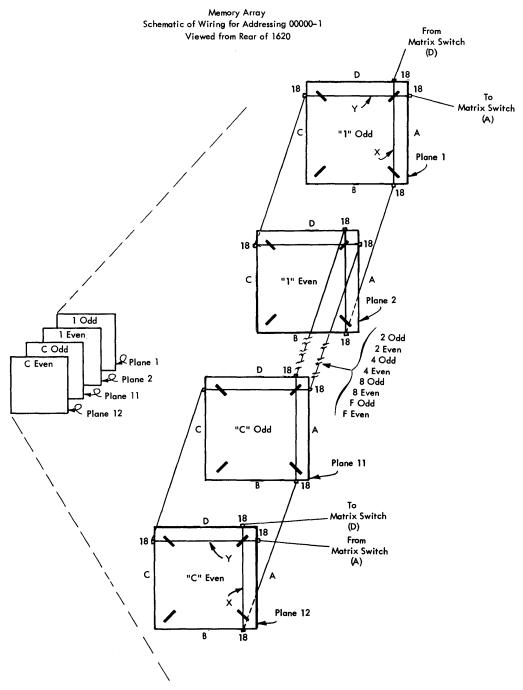

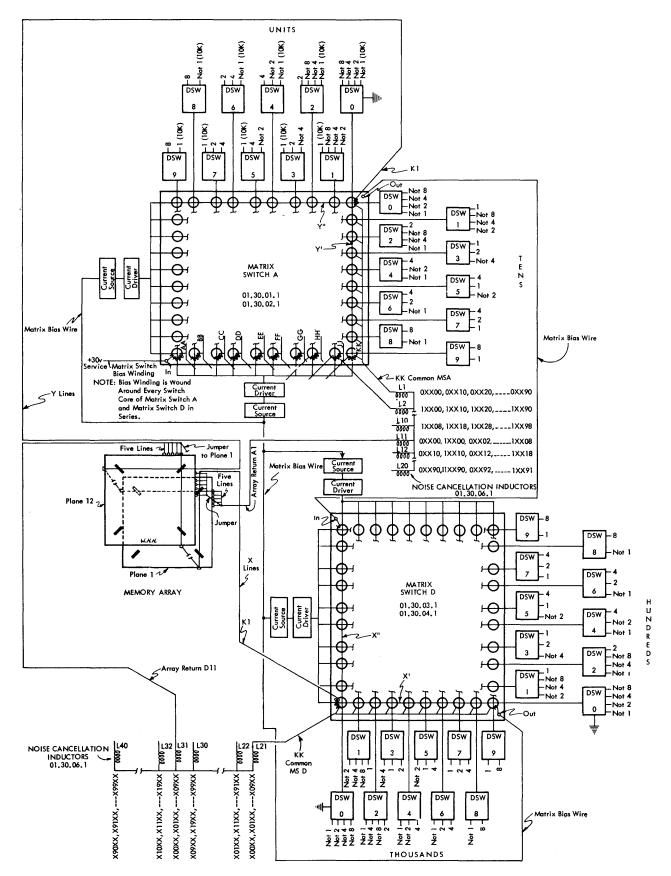

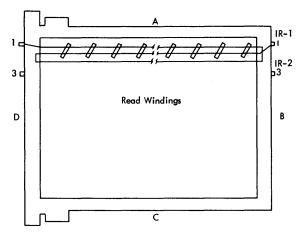

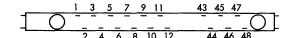

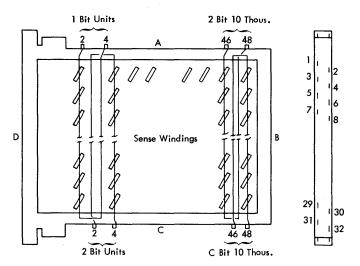

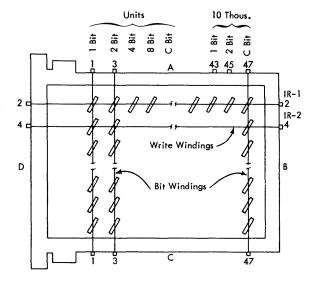

Memory is addressed by means of two matrix switches which select one "column" of 12 cores

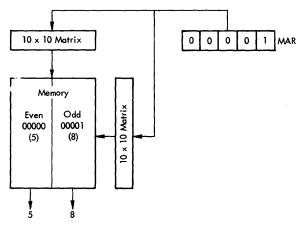

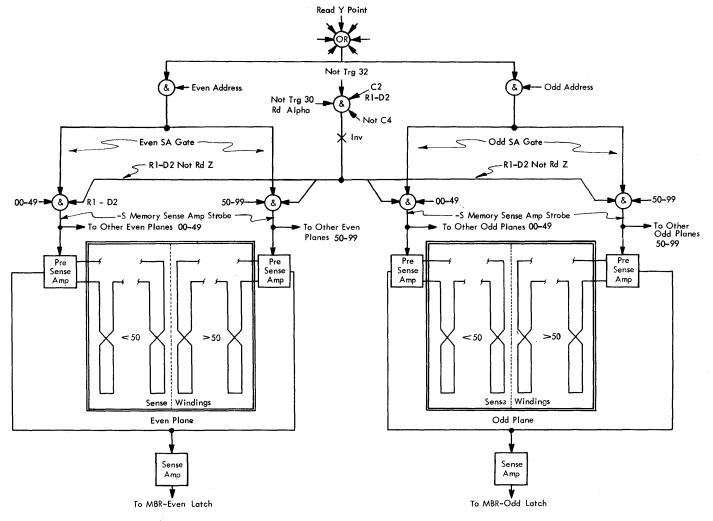

(one core in the same position in each plane). Since each digit position in memory consists of six bits (C, F, 8, 4, 2, 1), it follows that in selecting one column of 12 cores, two digits will be read out each time memory is addressed. Addressing is in the form of five digits (00000 to 19999) and is from a single register, Memory Address Register (MAR). Memory is divided into two sections, even and odd, by the wiring scheme. If memory is addressed per 00000, the digit at 00000 and at 00001 will be read out (Figure 2-2). If the address is 00001 the digit at 00001 and the digit at 00000 will be read out (Figure 2-3).

Figure 2-2. Memory Addressed per 00000

Figure 2-3. Memory Addressed per 00001

227-5751 (8-63)

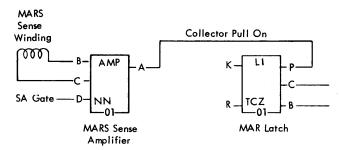

# SENSE AMPLIFIERS AND MEMORY BUFFER REGISTER (MBR)

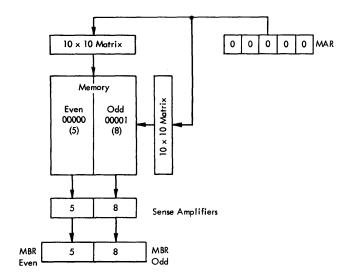

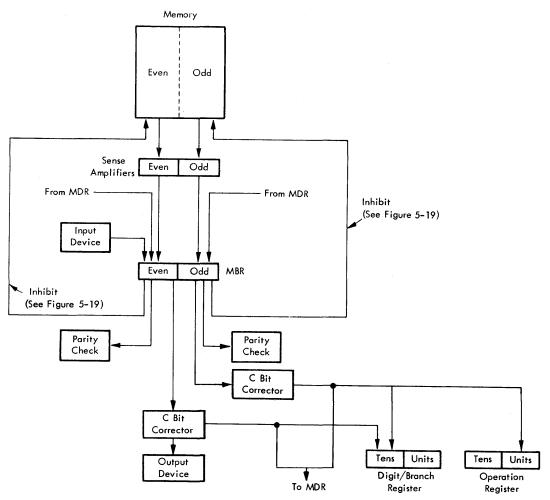

Digits which are read out of memory are sensed by sense amplifiers which in turn set latches in the MBR. The MBR is designated even (MBR-even) and odd (MBR-odd) and will receive the corresponding digit from memory (Figure 2-4).

Figure 2-4. Reading Out of Memory

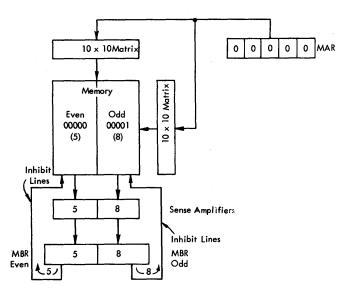

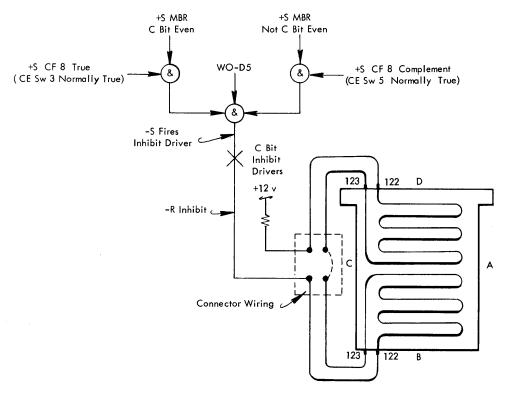

The readout of cores is destructive and therefore to retain the digits they must be written back into memory. The latches in MBR control inhibit lines which in turn permit the digits to be written back into memory (Figure 2-5).

Figure 2-5. Writing Into Memory

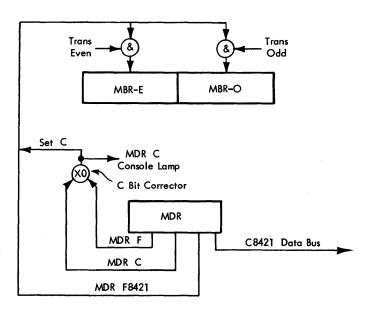

# MEMORY DATA REGISTER (MDR)

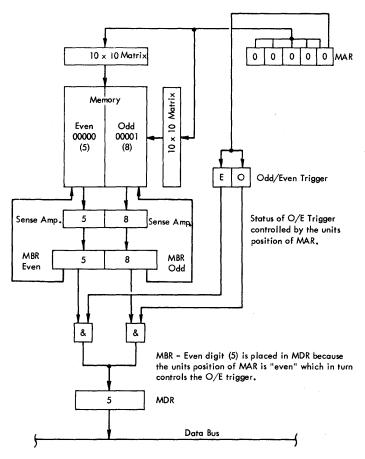

Generally the 1620 System will use only the specific digit addressed. Therefore, a single digit register called Memory Data Register is provided to receive and store the digit. Controls are provided to determine which digit in MBR (odd or even) is transferred to MDR. To accomplish this, the output of MBR-odd and -even is controlled by an Odd/Even trigger which in turn is controlled by the units position of MAR. Figure 2-6 shows Odd/Even trigger control of the data path for the digit-5 from memory to MDR. The digit is available to the data bus from MDR.

There are times when it is necessary to clear a location in memory. At this time, the Odd/Even trigger exercises control, as to which specific location (odd or even) is to be cleared, by blocking the odd or even sense amplifiers (Figure 2-7). There are functions requiring the clearing of two memory locations, both odd and even, at the same time. This is done by blocking both the odd and the even sense amplifiers without regard to the status of the Odd/Even trigger. The objective of clearing a memory location is to reset the cores at that address so that

Figure 2-6. MBR to MDR Data Flow with Odd/Even Trigger Control

Figure 2-7. Clearing Memory Locations

a new digit may be entered. The new digit will be placed in MBR. MBR controls the inhibit lines which permit writing the new digit into memory.

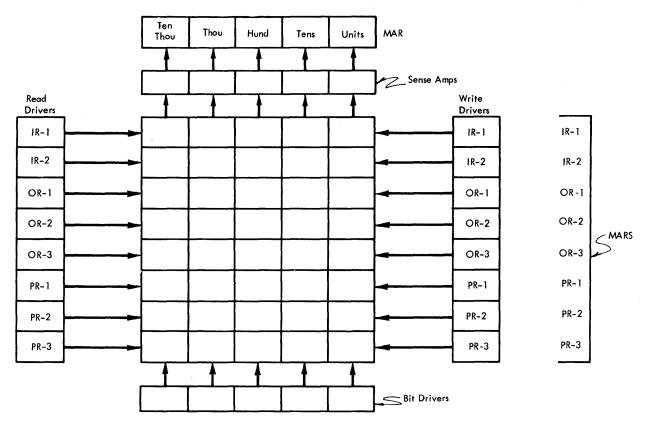

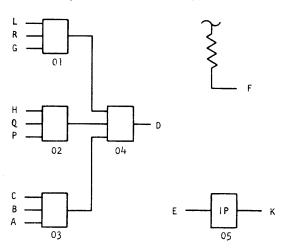

#### MEMORY ADDRESS REGISTER STORAGE (MARS)

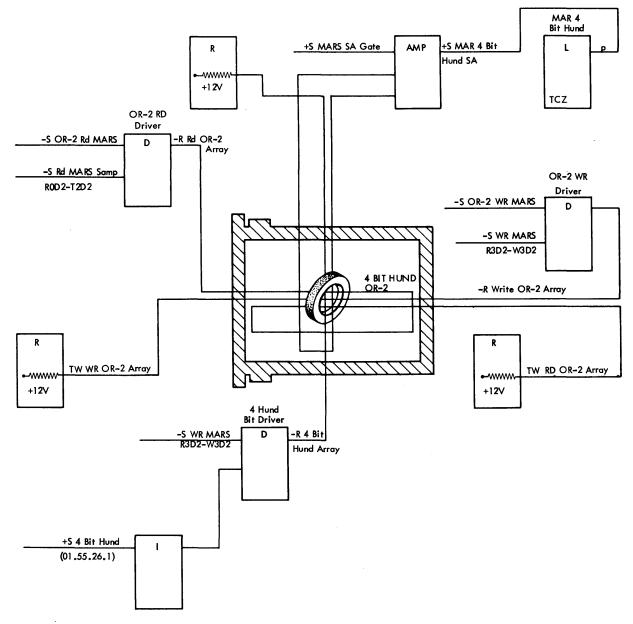

Memory Address Register Storage (MARS) is a single-plane core array in a 24 x 16 matrix. The basic 1620 System makes use of only a part of the available storage, using a 24 x 8 matrix. MARS is divided into eight sections, each section capable of storing a 5-digit address. Each section or register has its own read and write drivers so that selection may be made as to which register is to read into MAR and which MARS register (one or more) will be written into (Figure 2-8).

In order to address memory, an address must be placed in MAR. This is done by causing the read drivers of a particular MARS register to be operative. The read drivers cause the address stored in that MARS register to read out, through sense amplifiers, to MAR.

To reset a MARS register the read drivers for that register are made operative at a time when the sense amplifiers are not conditioned to function.

In order to write into a MARS register, coincidence of the MARS write drivers for that register and the bit drivers is required.

The bit drivers can be gated so that a complete 5-digit address is written into MARS at one time. Another gate can cause one or two digits, as needed, to be written into MARS.

Figure 2-8. Memory Address Register Storage (MARS)

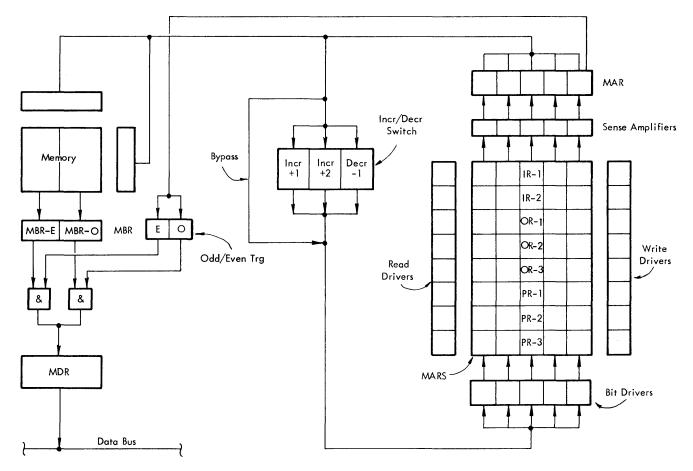

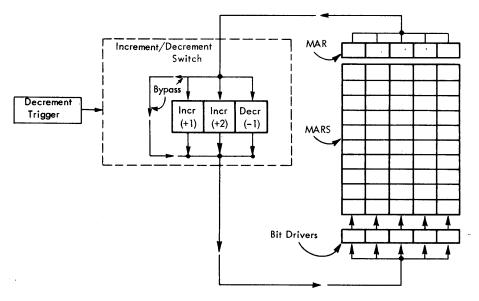

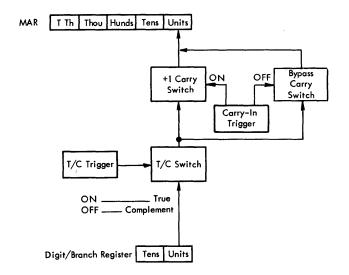

#### INCREMENT/DECREMENT SWITCH

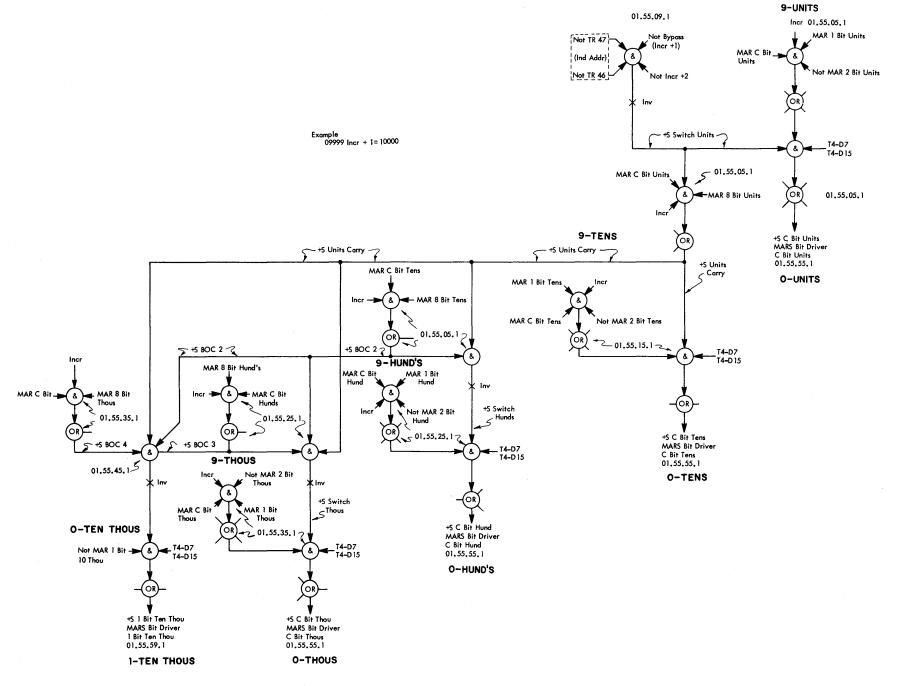

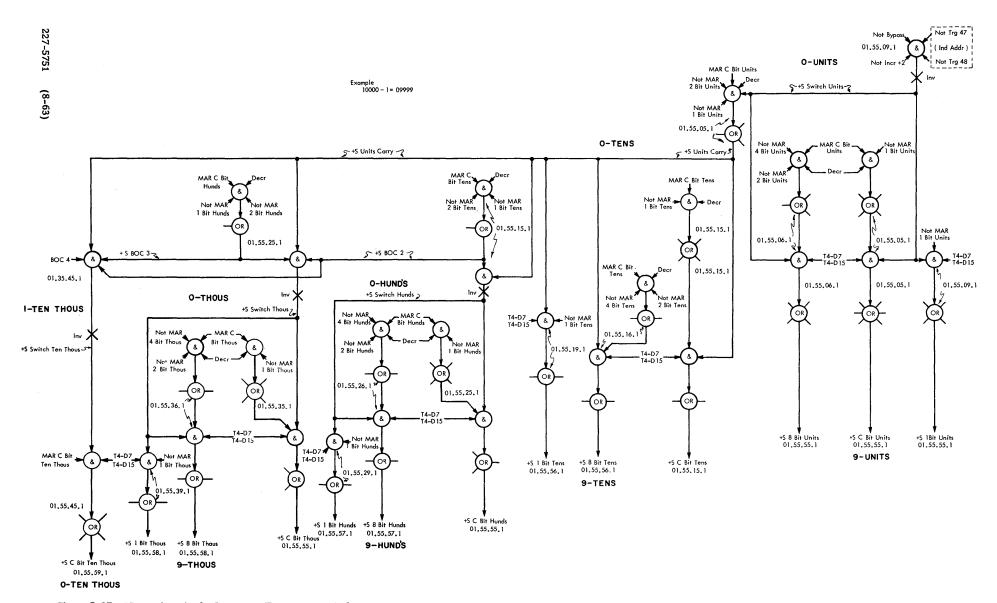

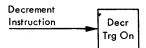

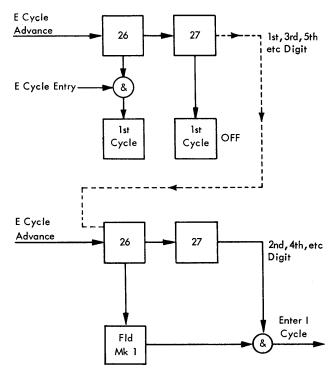

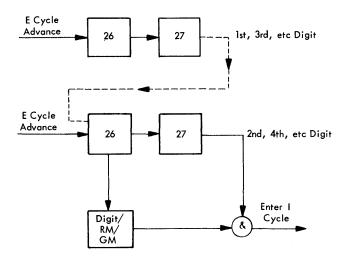

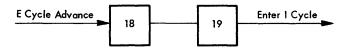

Each address read into MAR from MARS is the address of a single location in memory. Since a field or record consists of more than one digit, a means is provided to increase the address by one (increment +1) or decrease the address by one (decrement -1) depending upon the requirements of the operation being performed. There are operations which make use of two digits at a time for which an increment +2 is provided. A decrement of -2 is provided with the Indirect Addressing feature. The Increment/Decrement switch (Incr/Decr switch) consisting of a network of AND switches and OR switches performs these functions. The Decrement

trigger exercises control over the Incr/Decr switch. The status of the Decrement trigger is determined by the instruction to be executed. The output of all MAR bit triggers are connected to the inputs of the Incr/Decr switch. The outputs of the Incr/Decr switch are connected to the bit drivers. The coincidence of the bit drivers and the write drivers for a particular MARS register will write the MAR address (as altered by the Incr/Decr switch) into the MARS register.

There are operations requiring the readout of MARS to MAR where it is desired to write the address back into MARS unchanged. A bypass around the Incr/Decr switch accomplishes this function (Figure 2-9).

Figure 2-9. Increment/Decrement Switch

#### DEVELOPMENT OF A PROGRAM

Programming consists of defining the steps required to receive data, process data, and record results in terms of the operations which the computer system is capable of performing. Each step must be written as an instruction to the computer, with the series of instructions pertaining to an entire procedure constituting a program.

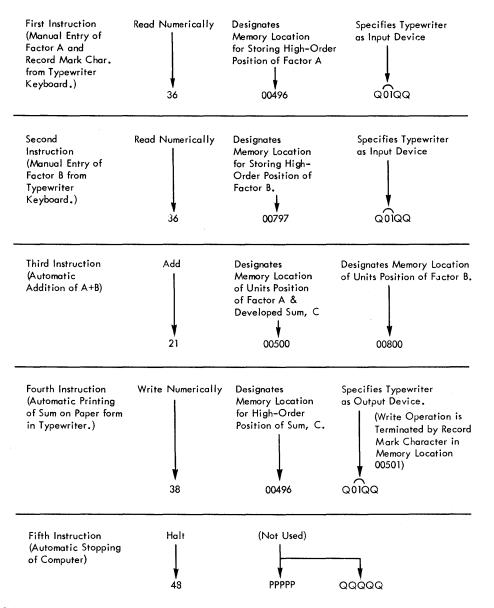

A program to accomplish entry of factors, solution of a simple problem, and printing of the result is presented to illustrate 1620 Computer programming (Figure 3-1).

#### Compute A + B = C

# Specifications:

- 1. Enter factors A and B into memory by means of the typewriter keyboard.

- 2. Store the units position of factor A at memory location 00500. (If the assigned field length for factor A is assumed to be five digits, the high-order position will be stored at location 00496.)

- 3. Store a record mark character at memory location 00501. (This record mark will be used to terminate the write operation demanded by Specification 5.)

- 4. Store the units position of factor B at memory location 00800. (If the assigned field length for factor B is assumed to be four digits, the high-order position will be stored at location 00797.)

- 5. Record the sum, C, on the paper form in the typewriter. (The developed sum will replace factor A and assume its location in memory.)

- Stop the computer upon completion of the program.

# INSERTION OF A PROGRAM INTO MEMORY (TYPEWRITER KEYBOARD)

Because the IBM 1620 is a stored program computer the instructions comprising a program must be written into memory for availability to the computer in the accomplishment of the program objectives. The program is stored in memory by pressing Insert on the console and then by typing each digit of the five instructions consecutively.

Pressing Insert places the typewriter in numerical shift; activates the typewriter keyboard; and prepares the computer to receive the high-order digit of the first 12-digit instruction at memory location 00000. By consecutively pressing the 3,6,0,0,4,9,6,0,0,1,0,0,3,6,0,0,7,9,7,0,0,1,0,0,2,1,0, etc. keys on the typewriter keyboard, the program is stored in memory locations 00000 through 00059. (In the program chart where the letters "P" or "Q" appear in the five instructions, any numerical key may be pressed. Those digit positions must be filled, but they are not used in the execution of the particular instruction.)

After entry of the low-order digit of the fifth instruction, pressing Release on the console terminates the insert operation. Pressing Start then initiates execution of the stored program. Pressing the R-S key on the typewriter keyboard performs the functions of Release followed by Start.

#### EXECUTION OF A PROGRAM

Instructions within a program are normally interpreted and executed sequentially: that is, if the first 12-digit instruction is stored in memory locations 00000 through 00011, the execution of that instruction is followed by the interpretation and execution of the instruction stored in locations 00012 through 00023, etc.

Each instruction is read from memory and stored in registers for interpretation, starting with the highorder digit and continuing through successively higher memory locations until all twelve digits have been read.

Because execution of the first instruction, 36 00496 00100, requires that factor A and a record mark character be entered into memory manually from the typewriter keyboard, the [flag], 0,0,3,2,1, and record mark keys are pressed consecutively by the operator. Pressing Release then terminates execution of the first instruction.

Pressing Start directs the computer to proceed with the program and the second instruction is interpreted.

|                       | Memory                      |            | Instruction | on           |                                                                                                  |

|-----------------------|-----------------------------|------------|-------------|--------------|--------------------------------------------------------------------------------------------------|

| Instruction<br>Number | Location for<br>Instruction | Op<br>Code | P-Part      | Q-Part       | Function to be Executed                                                                          |

| One                   | 00000                       | 36         | 00496       | Q01QQ        | Enter Factor A (00321) at Memory Location 00496 – 00500.<br>Enter Record Mark Character at 00501 |

| Two                   | 00012                       | 36         | 00797       | Q01QQ        | Enter Factor B (0067) at Memory Locations 00797 - 00800.                                         |

| Three                 | 00024                       | 21         | 00500       | 00800        | Add A + B and Store Sum, C, at Memory Locations 00496 - 00500.                                   |

| Four                  | 00036                       | 38         | 00496       | Q01QQ        | Type Sum, C, (00388) on Paper Form in Typewriter from Memory Locations 00496 – 00500.            |

| Five                  | 00048                       | 48         | PPPPP       | ବ୍ଦବ୍ଦବ୍ଦବ୍ଦ | Stop Computer                                                                                    |

Figure 3-1. Manual Insertion of a Program into Memory

Execution of the second instruction, 36 00797 00100, requires that factor B be entered into memory manually from the typewriter keyboard. The

(flag), 0,0,6, and 7 keys are depressed consecutively by the operator. Pressing Release terminates execution of the second instruction.

Pressing Start again directs the computer to proceed with the program and the third instruction is interpreted. No further manual entry of data is required by the program, so the third instruction is executed and the two remaining instructions are interpreted and executed automatically. The computer halts upon completion of the program.

# AUTOMATIC PROGRAM REPETITION (PROGRAM LOOP)

The program shown in Figure 3-1 computes the sum for only one problem, but by returning to the first instruction of the program and repeating the program as a loop, the sums for any number of problems can be computed. A program loop will be initiated if the halt instruction, 48 PPPPP QQQQQ, is replaced by the branch instruction, 49 00000 QQQQQ. The branch instruction directs the computer to the instruction located at its P-address, 00000, which is the address of the first instruction in the program. (A typewriter control instruction, 34 PPPPP Q01Q1 or 34 PPPPP Q01Q2, could be inserted into the program to cause the typewriter to line space and carriage return or simply space between sums.)

#### MAGNETIC CORES

# **Memory Cores**

A magnetic core is a small doughnut-shaped ring that is uniformly constructed of ferrite particles bonded together by a ceramic material. The ferrite particles have good magnetic properties and the core has a high retentivity of the magnetic flux lines after the magnetizing force is removed. It is this property of retentivity that makes a memory core useful as a storage device.

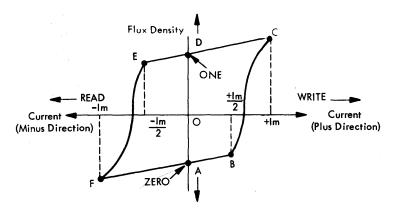

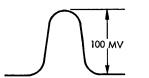

The operation of a memory core can best be described by reference to the hysteresis curve, Figure 4-1. This curve is a plot of the relationship between a magnetizing current  $(I_m)$  and the flux density.

A memory core is capable of maintaining indefinitely one of two stable magnetic states, either at point A or at point D on the hysteresis curve. Because the core has two stable states, it can be used as a binary storage device. At point A the core has a residual flux in a negative direction, and at point D a residual flux in the positive direction. These two directions can be arbitrarily assigned as binary "zero" and binary "one," respectively.

$I_m$  is the amount of current necessary to change the state of the core. Plus  $I_m$  is that amount of current flowing in one direction, and minus  $I_m$  the same amount of current flowing in the opposite direction.

On the hysteresis curve, it can be observed that a magnetizing current of plus  $I_{\rm m}$  will change the magnetism of the core from point A, a binary zero, to the magnetic saturation value in the positive direction at point C. When the current is removed, the total amount of magnetization drops back to point D (binary one). If, instead of full plus  $I_{\rm m}$ , a current of plus  $I_{\rm m}/2$  were applied, the flux would change only the small amount from point A to point B on the curve, and when the current returned to zero, the flux would return to its original value at point A.

A reverse current, minus  $I_m$ , develops flux of opposite polarity and changes the magnetic field of the core from point D to the magnetic saturation value in the negative direction at point F. The total amount of magnetization drops back to point A (binary zero) when the driving current is removed.

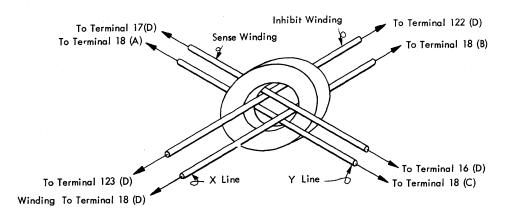

When a matrix of memory cores is constructed to store multiple bits of information, a specific core is selected (addressed) by the coincidence of  $I_m/2$  flowing through each of two wires threaded through the core, with a total effective current of full  $I_m$ . The state of the core is determined by the direction of the current flowing through these wires. A current  $I_m$  is passed to store a "1" in the core; this is called "writing" into cores. A current  $I_m$  is passed in the opposite direction to change a stored value of "1" to a "0" and can be considered a current of minus  $I_m$ ; this is called "reading" a core.

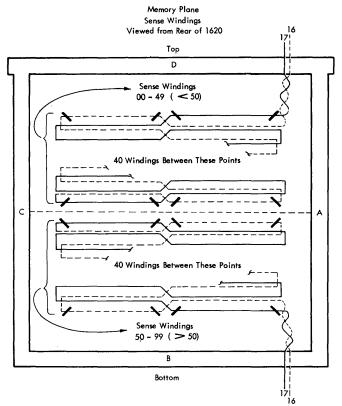

Reading a memory core depends on a system of sensing the state of the flux field within the core.

Figure 4-1. Hysteresis Curve

When the core contains a "0" and a current of minus  $I_m$  read current is passed through the core, the field changes from point A to point F on the hysteresis curve, which is a very small change in total flux density. If the core contains a "1" and a minus  $I_m$  read current is passed through the core, the field changes from point D to point F and a large change in the flux field occurs. A third wire, called the "sense" wire, is threaded through the core to recognize these changes in the magnetic field. Circuits are used to discriminate against low value "0" signals and amplify the large signal that results when a "1" is read from a core.

#### **Switch Cores**

The construction of the switch cores is similar to memory cores, but the switch cores are physically larger. Switch cores, however, are not used to store or retain information, but are used as transformers, making use of the induced current pulses when the core is flipped. The induced current pulses are used to read into or write from memory cores.

The memory addressing scheme selects two specific switch cores. The outputs of the two switch cores are used to establish X and Y coordinate lines for addressing a memory location.

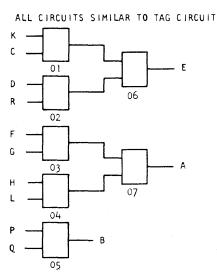

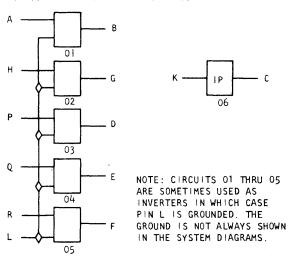

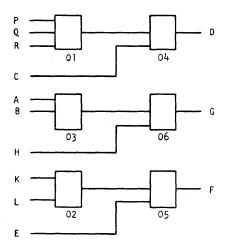

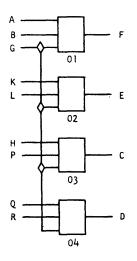

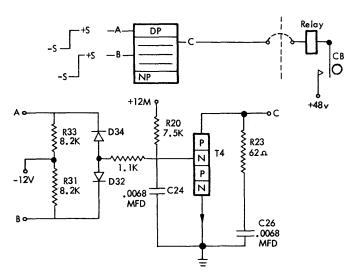

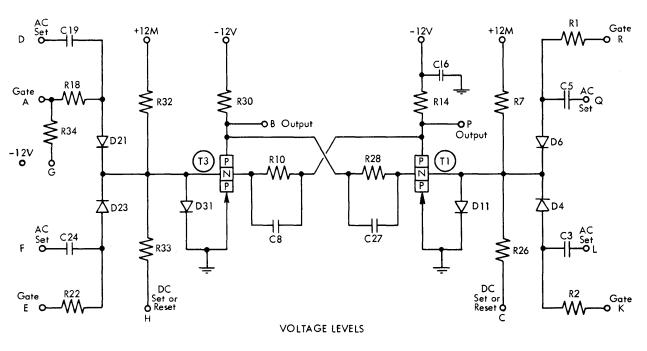

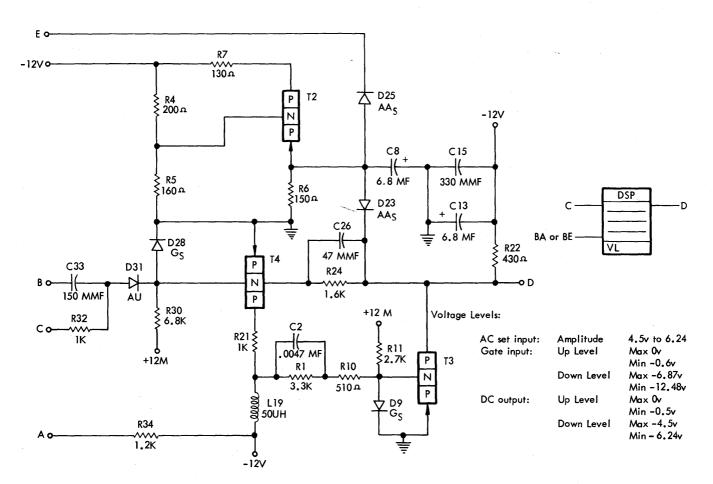

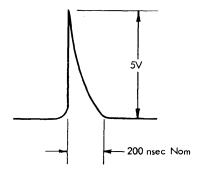

#### COMPONENT CIRCUITS

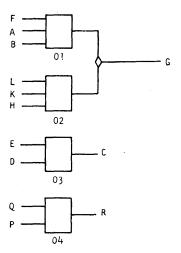

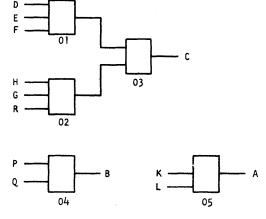

Discussion of electronic or transistor theory is not intended in this manual. Other IBM manuals have been written to provide such information. Samples of the various types of SMS cards including Multiple Use Package (MUP) cards are described to provide the Customer Engineer with sufficient information to interpret System Diagrams and understand machine functions.

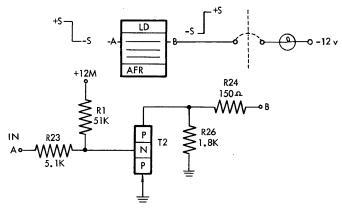

The SMS Card Index, Figure 4-2a, 4-2b, and 4-2c, lists the card types, used by the basic 1620 Computer System, by card code. Circuit schematics, part numbers, and associated logic block symbols for the cards are shown in the 1620 System Diagrams.

| Card Code    | Symbol            | Systems Diagrams | Description                                                                                                            |

|--------------|-------------------|------------------|------------------------------------------------------------------------------------------------------------------------|

| AFR          | LD or ID          | C.00.05.1        | Lamp Driver. A -S input level causes a +S output level. Example on 01.06.10.1.                                         |

| АНК          | A, O, or I        | C.00.05.1        | Two-way alloy type extender for AND or OR latches. Example on 01.06.10.1                                               |

| *AHU         | Vor V             | C.00.07.1        | See AYX.                                                                                                               |

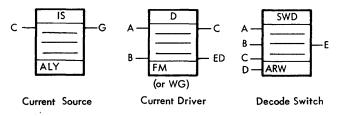

| ALY          | DP                | C.00.07.1        | Constant current source for matrix switches. Example on 01.30.10.1.                                                    |

| ARW          | SWD               | C.00.08.1        | Decode Switch. Four -S inputs are required to cause conduction. Example on 01.30.16.1.                                 |

| AYX          | V or V            | C.00.08.1        | Exclusive OR. Like inputs produce a +S output and unlike inputs produce a -S output. Example on 01,40.20.1.            |

| САВ          | E                 | C.00.10.1        | Three-way alloy extender card. The collectors are not internally connected to a load resistor.  Example on 01.06.11.1. |

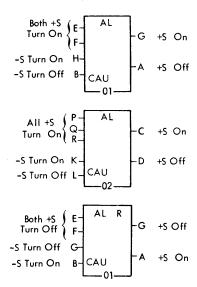

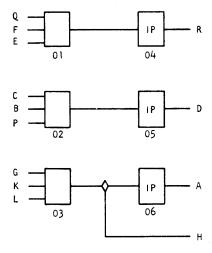

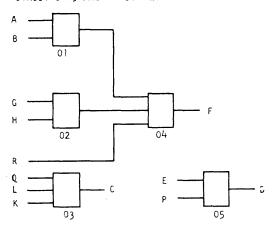

| CAU          | AL                | C.00.10.1        | AND Latch-alloy type (MUP-15). Example on 01.06.11.1.                                                                  |

| CD           | A, O, or E        | C.00.12.1        | Three-way alloy AND, OR, or Extender. Example on 01.06.11.1.                                                           |

| CEYB<br>(CE) | DE                | C.00.12.1        | Emitter follower-alloy type. Example on 01.06.20.1.                                                                    |

| DAW          | Е                 | C.00.17.1        | Three-way drift extender card. Example on 01.40.03.1                                                                   |

| DEQ          | I, IP, A,<br>or O | C.00.22.1        | Three-way drift A, O, or I with a power inverter (MUP-3). Example on 01.10.05.1.                                       |

<sup>\*</sup> See System Diagram Page 01.00.05.1, Interchangeable Cards.

Figure 4-2a. SMS Card Index

| Card Code | Symbol           | Systems Diagrams | Description                                                                                                              |

|-----------|------------------|------------------|--------------------------------------------------------------------------------------------------------------------------|

| DES       | A or O           | C.00.23.1        | A three-way, two 2-ways feeding a 3-way, and a 2-way drift type AND or OR blocks (MUP-5). Example on 01.40.50.1.         |

| DEV       | A or O           | C.00.23.1        | Two-way drift type AND or OR circuits (MUP-7). Example on 01.30.65.1.                                                    |

| DEW       | A, IP, I<br>or O | C.00.24.1        | Five 2-way, drift type, AND or OR circuits with one input common, and a power inverter (MUP-8). Example on 01.55.55.1.   |

| DFB       | A or O           | C.00.25.1        | A 3-way feeding a 2-way and two 2-ways feeding two 2-ways, drift type, AND or OR circuits (MUP-13). Example 01.55.15.1   |

| DFC       | A or O           | C.00.25.1        | Four 3-way drift type AND or OR circuits uits with one input common (MUP-14). Example on 01.55.03.1.                     |

| DFD       | AL               | C.00.30.1        | AND latch, drift type. Example on 01.45.05.1.                                                                            |

| DFE       | A,O, or E        | C.00.30.1        | A six-way and two 2-way drift type And or OR circuits (MUP-16). Example on 01.40.03.1.                                   |

| DFG       | A or O           | C.00.33.1        | Two 3—way feeding a 2—way and two sep—<br>arate 2—way drift type AND or OR circuits<br>(MUP–18). Example on 01.55.06.1.  |

| DFP       | A, O, or<br>IP   | C.00.33.1        | Three 3-way feeding a 3-way drift type AND or OR circuits and a separate power inverter (MUP-20). Example on 01.55.06.1. |

| *FL       | SWD              | C.00.35.1        | See ARW.                                                                                                                 |

| *FM       | D                | C.00.38.1        | Current driver, alloy type. Used with ARW card to provide matrix switch input currents. Example on 01.30.10.1.           |

| *FQ       | DP               | C.00.07.1        | See ALY.                                                                                                                 |

| мн        | 1                | C.00.40.1        | Power inverter. Example on 01.06.20.1.                                                                                   |

| MX        | A,O, or I        | C.00.40.1        | Two-way alloy type AND, OR, Extender or Inverter. Example on 01.06.10.1.                                                 |

| NN        | AMP, AM<br>or R  | C.00.41.1        | Sense amplifier. Used with MARS. Example on 01.57.01.1.                                                                  |

| NP        | DP               | C.00.41.1        | Relay and light driver. Used with typewriter relays and console lights. Example on 01.82.52.1.                           |

| *QF       | LD or ID         |                  | See AFR.                                                                                                                 |

| QU        |                  |                  | Differential amplifier card for SMS Power Supplies in some 1620's.                                                       |

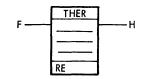

| RE        | THER             | C.00.45.1        | Thermoswitch. Used for checking gate temperature. Example on 01.90.42.1.                                                 |

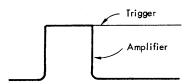

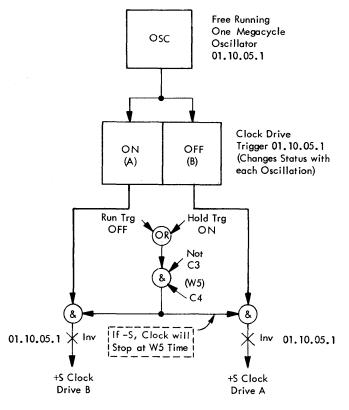

| TAF       | OSC              | C.00.46.1        | Oscillator, one megacycle. Used as basic timer for 1620 clock circuits. Example on 01.10.05.1.                           |

| TAG       | A, O, or         | C.00.47.1        | Two-way AND, OR, or Inverter, drift type.<br>Example on 01.59.10.1.                                                      |

Figure 4-2b. SMS Card Index

<sup>\*</sup> See System Diagram Page 01.00.05.1, Interchangeable Cards.

| Card Code         | Symbol     | Systems Diagrams | Description                                                                                                                                  |

|-------------------|------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| TAH               | A,O, or E  | C.00.47.1        | Three-way AND, Or, or extender, drift type.<br>Example on 01.55.45.1                                                                         |

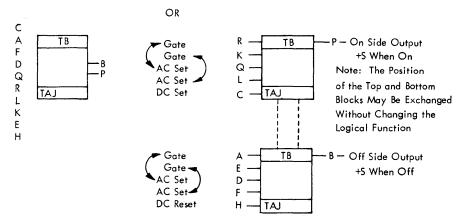

| TAJ               | ТВ         | C.00.48.1        | Binary trigger. Example on 01.63.20.1                                                                                                        |

| TAK               | ł          | C.00.60.1        | See TFC.                                                                                                                                     |

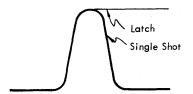

| TAL               | DSP        | C.00.48.1        | Sample pulse generator. Used to provide the rapid rise time required to change the state of a binary trigger. Example on 01.63.20.1.         |

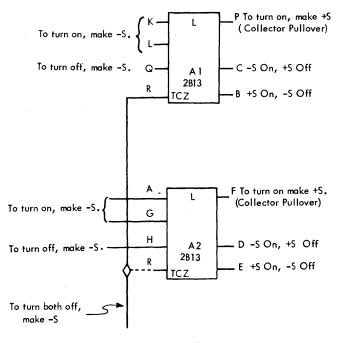

| TCZ               | L, LI      | C.00.55.1        | Latch, inverting drift type (MUP – 12)                                                                                                       |

| TFC               | Ī          | C.00.60.1        | Power inverter, drift type. Example on 01.10.30.1                                                                                            |

| *пх               | СР         | C.00.61.1        | See NP.                                                                                                                                      |

| *VE               | A, O, or I | C.00.47.1        | See TAG.                                                                                                                                     |

| *VF               | A, O, or E | C.00.47.1        | See TAH.                                                                                                                                     |

| *VG               | OSC        | C.00.46.1        | See TAF.                                                                                                                                     |

| *\1               | тв         | C.00.48.1        | See TAJ.                                                                                                                                     |

| *VL               | DSP        | C.00.48.1        | See TAL.                                                                                                                                     |

| *VM               | 1          | C.00.60.1        | See TFC.                                                                                                                                     |

| WF                | SWD        | C.00.35.1        | See ARW.                                                                                                                                     |

| *WG               | D          | C.00.61.1        | See FM.                                                                                                                                      |

| ΜJ                | D          | C.00.63.1        | Current driver, alloy type. Example on 01.55.55.1.                                                                                           |

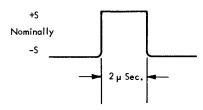

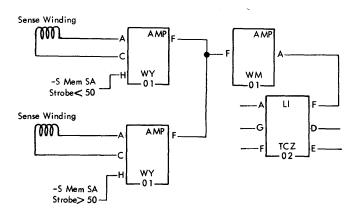

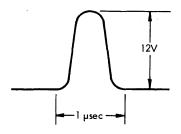

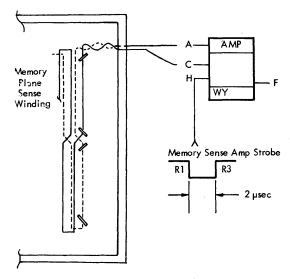

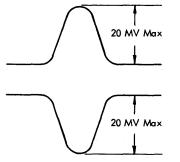

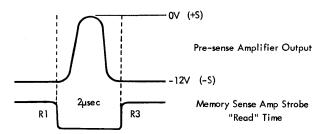

| WM                | АМР        | C.00.63.1        | Single shot sense amplifier, alloy type. Input from memory presense amplifier. Provides a 1 sec pulse to MBR latches. Example on 01.30.50.1. |

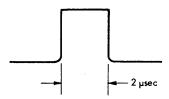

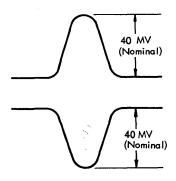

| WY                | АМР        | C.00.65.1        | Pre-sense amplifier, alloy type. Used to amplify a nominal 40 mv signal. Example on 01.30.50.1.                                              |

| YGB               |            | C.00.69.1        | Overvoltage protection, 12 volt power supply. Example on 01.90.23.1.                                                                         |

| YGC               |            | C.00.69.1        | Overvoltage protection, 36 volt power supply. Example on 01.90.22.1.                                                                         |

| YGH               |            | C.00.71.1        | Differential amplifier, 36 volt power supply. Example on 01.90.22.1.                                                                         |

| ٨Ġ٦               |            | C.00.71.1        | Differential amplifier, 12 volt power supply. Example on 01.90.23.1                                                                          |

| YGN               |            | C.00.75.1        | Differential amplifier, 30 volt power supply. Example on 01.90.25.1.                                                                         |

| YJA<br>and<br>YJB | R          | C.00.77.1        | Load resistors. Example on 01.55.55.1.                                                                                                       |

|                   |            |                  |                                                                                                                                              |

Figure 4-2c. SMS Card Index

<sup>\*</sup> See System Diagram Page 01.00.05.1, Interchangeable Cards.

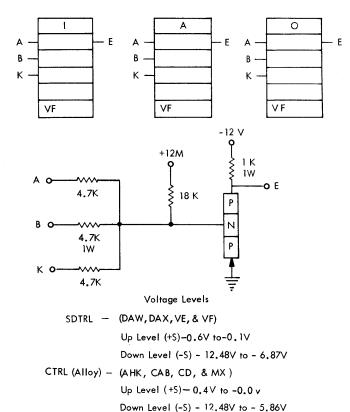

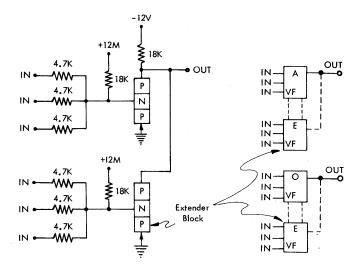

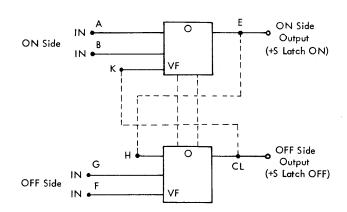

The 1620 Computer uses a type of circuitry known as Transistor Resistor Logic (TRL). This type of circuit uses resistors in voltage dividing networks to control the functions of transistors. TRL is also called NOR, Negative OR.

There are two types of transistors used in the 1620: alloy and drift. The drift type is also called saturating drift. The term SDTRL, used with an SMS card, means Saturating Drift Transistor Resistor Logic and indicates that the transistor or transistors used in that card are of the drift type. The difference between alloy and drift transistors is in transition times. The drift is faster than the alloy and is used in areas where speeds are critical.

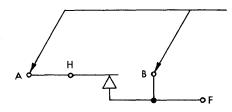

The term CTRL means Complementary Transistor Resistor Logic which indicates that inputs and outputs can be of a different level. For example a  $\pm S$  level input can result in  $a \pm R$  level output. R levels are  $\pm R = +12v$  and  $\pm R = 12v$ . The relay thyratron drivers, DP cards, are an example, having  $\pm 48v$  on the output. CTRL cards are not necessarily used with the complementary function.

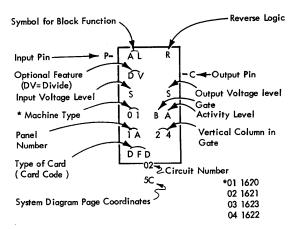

Figure 4-3 depicts a typical "block," as shown in 1620 System Diagrams, with symbols defined. If the additional features line is blank, the block is a basic 1620 logic block. If a code appears in the line, the block is associated with the additional feature specified by the code. The logic block coding for additional features is as follows:

| Code          | Feature                              |

|---------------|--------------------------------------|

| DV            | Divide                               |

| IA or IF      | Indirect Addressing                  |

| $\mathbf{DI}$ | DV or IA or Both                     |

| CRP           | Card Read-Punch - Card I/O-IBM 1622  |

| TN            | Special Instructions - TNS, TNF, MF  |

| <b>M</b> 1    | Additional Core Storage - 20 or 40 K |

|               | IBM 1623                             |

| M2            | Additional Core Storage - 40 K only  |

|               | IBM 1623                             |

| M1N2          | Additional Core Storage - 20 K only  |

|               | IBM 1623                             |

| $\mathbf{FP}$ | Floating Point                       |

| RAM           | Disk Storage Drive - IBM 1311        |

| CF            | CRP and RAM                          |

| C/F           | CRP or RAM or Both                   |

| FP/F          | FP or RAM or Both                    |

| M1/F          | M1 or RAM or Both                    |

| M2/F          | M2 or RAM or Both                    |

| NM1           | Not M1                               |

| FNM1          | RAM Not M1                           |

| PT            | Paper Tape - IBM 1621 - 1624         |

| PR            | Printer - IBM 1443                   |

Figure 4-3. 1620 System Diagram (Logic) "Block"

The following logic block codes are associated with the IBM 1710 Control System:

| Code          | <u>Feature</u>              |

|---------------|-----------------------------|

| INT           | Interrupt                   |

| $\mathbf{F}1$ | 1710 Attachment             |

| $\mathbf{F}2$ | 1710 Additional Features    |

| $\mathbf{F}3$ | 1711 Compatibility          |

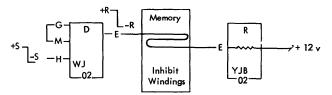

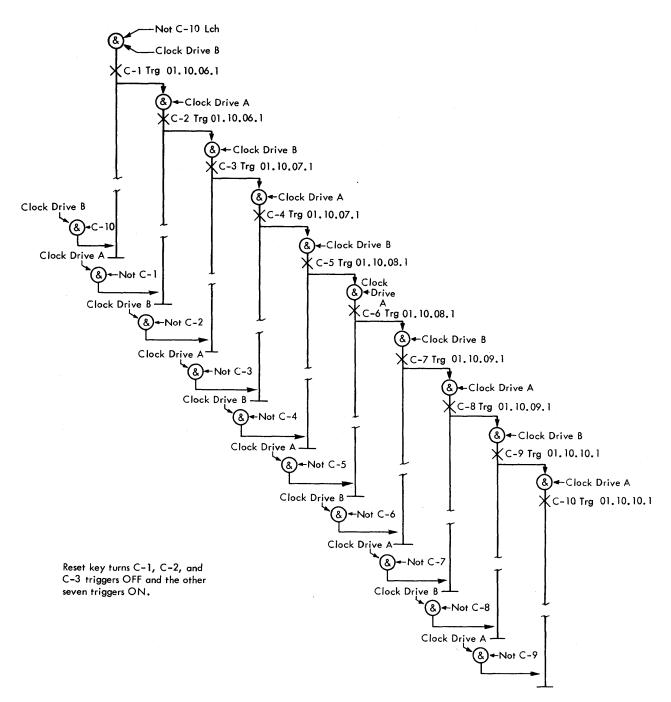

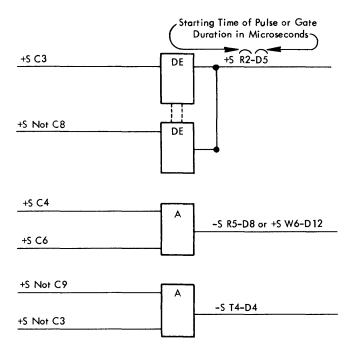

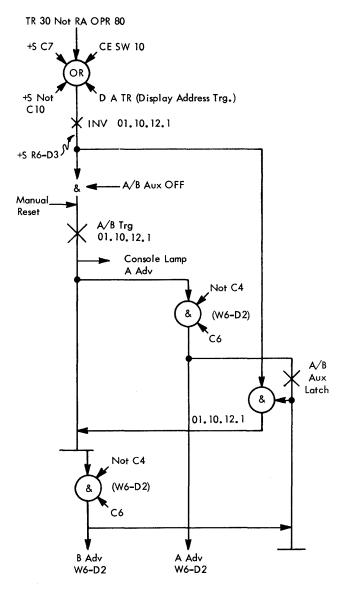

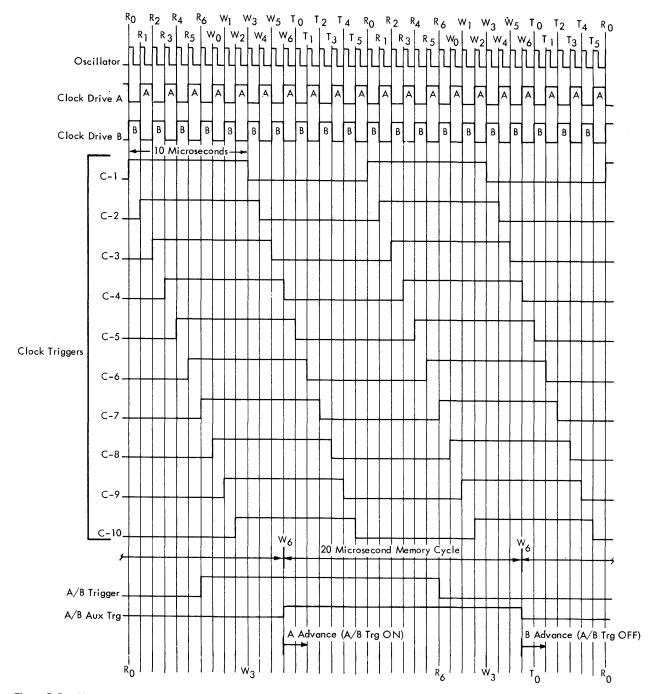

| SIOC          | Serial Input/Output Channel |