# HP 3000 SERIES III COMPUTER SYSTEM

### REFERENCE/TRAINING MANUAL

Manual Part No. 30000-90143

Printed in U.S.A. 6/79

#### NOTICE

The information contained in this document is subject to change without notice.

HEWLETT-PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance or use of this material.

This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied or reproduced without the prior written consent of Hewlett-Packard Company.

### LIST OF EFFECTIVE PAGES

The List of Effective Pages gives the date of the current edition and of any pages changed in updates to that edition. Within the manual, any page changed since the last edition is indicated by printing the date the changes were made on the bottom of the page. Changes are marked with a vertical bar in the margin. If an update is incorporated when an edition is reprinted, these bars are removed but the dates remain. No information is incorporated into a reprinting unless it appears as a prior update.

All pages in this manual are original issue.

### **PRINTING HISTORY**

New editions are complete revisions of the manual. Update packages, which are issued between editions, contain additional and replacement pages to be merged into the manual by the customer. The date on the title page and back cover of the manual changes only when a new edition is published. When an edition is reprinted, all the prior updates to the edition are incorporated. No information is incorporated into a reprinting unless it appears as a prior update. The edition does not change.

First Edition. . . . . . . . . . . . . . . . Jun 1979

### **PREFACE**

This manual contains hardware-oriented reference information for the HP 3000 Series III Computer Systems. Specifically, this manual contains reference reading material for all persons that are to attend Hewlett-Packard's 3000 Series III Computer System Hardware Training Courses. Since the information contained in this manual is approximately the same as that presented during classroom lectures, this manual should be used for classroom reference, note taking purposes, and post school reference.

The HP 3000 Series III Computer Systems are divided into two product lines; the HP 32421A Series III and the HP 32435A Series III. Unless otherwise stated, the content of this manual applies equally to both product lines.

### **CONTENTS**

| SECTION I | - | INTRODUCTIO | N |

|-----------|---|-------------|---|

|-----------|---|-------------|---|

| Paragraph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Page                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| SYSTEM FEATURES Stack Architecture Microprogrammed Operations Data Base Management Facilities Five Programming Languages Virtual Memory Fault Control Memory Concurrent I/O and CPU Operations Reentrant Code and Private Data Operating System HARDWARE FEATURES SOFTWARE FEATURES SYSTEM CONFIGURATIONS                                                                                                                                                                                            | 1-1<br>1-2<br>1-2<br>1-2<br>1-2<br>1-2<br>1-3<br>1-3<br>1-4                            |

| SECTION II - SYSTEM/CPU OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                        |

| Paragraph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Page                                                                                   |

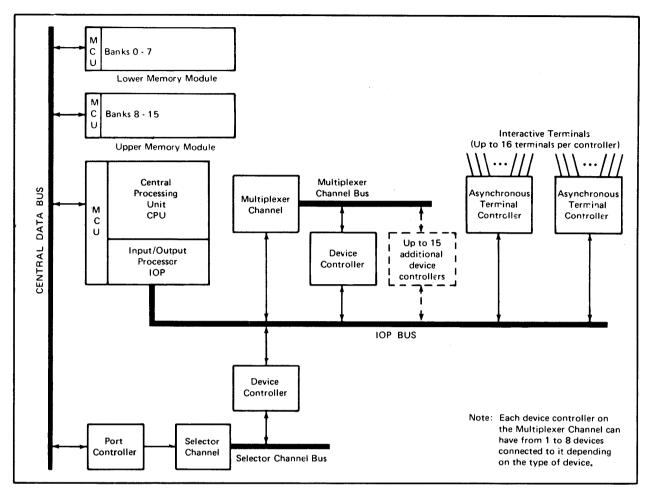

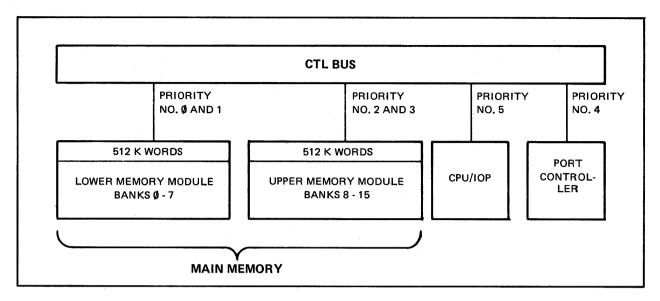

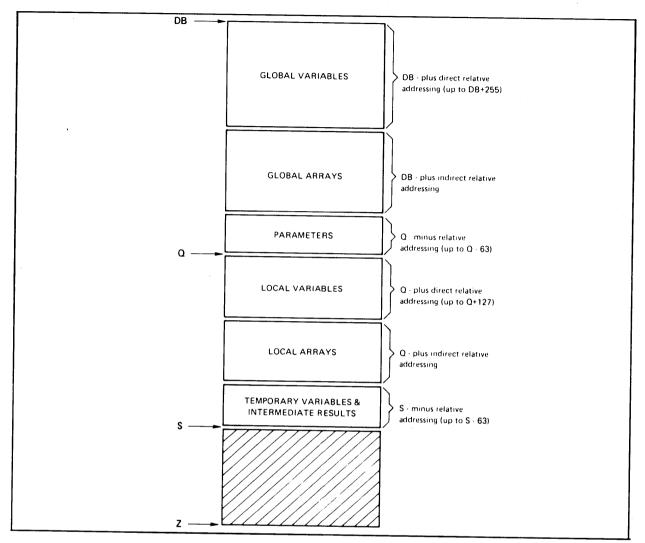

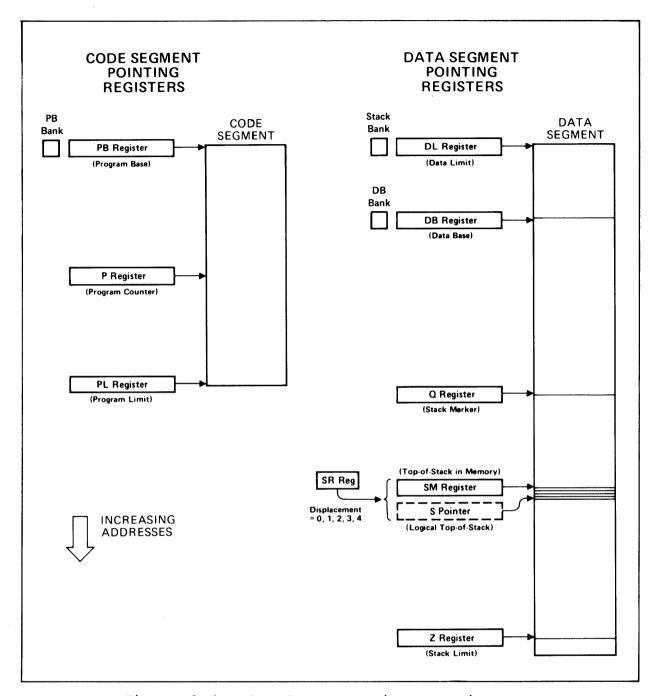

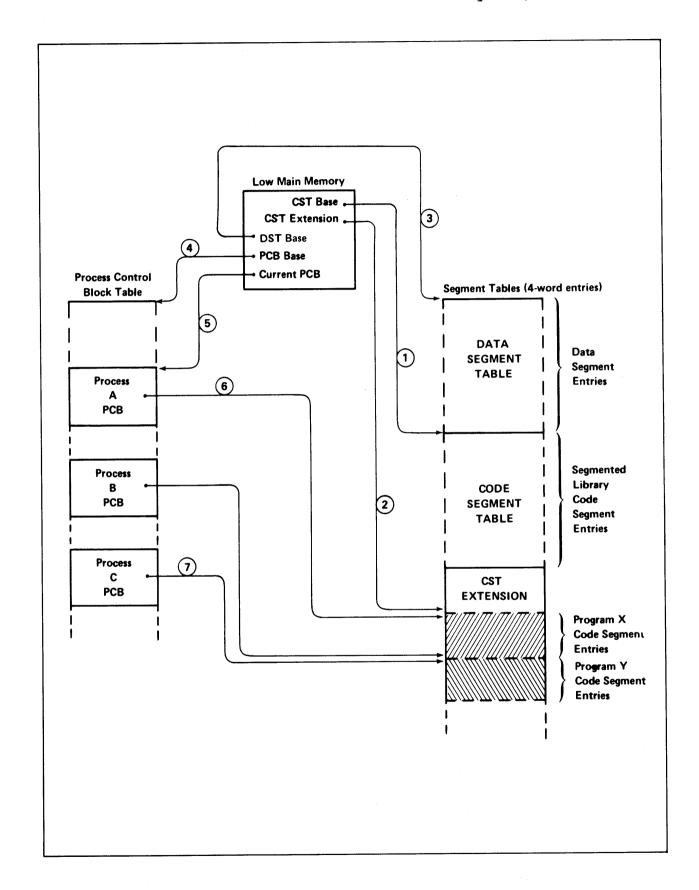

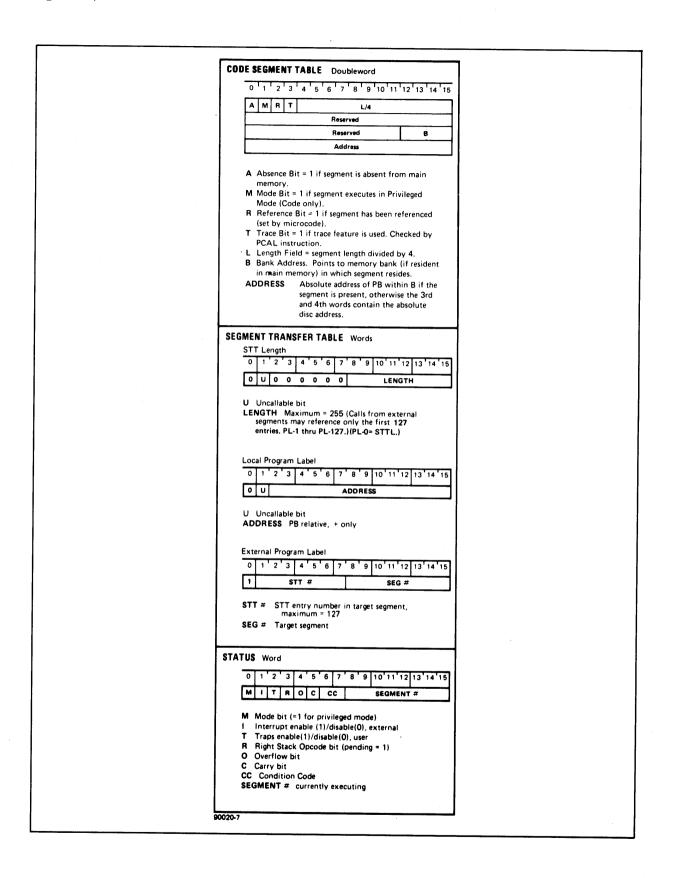

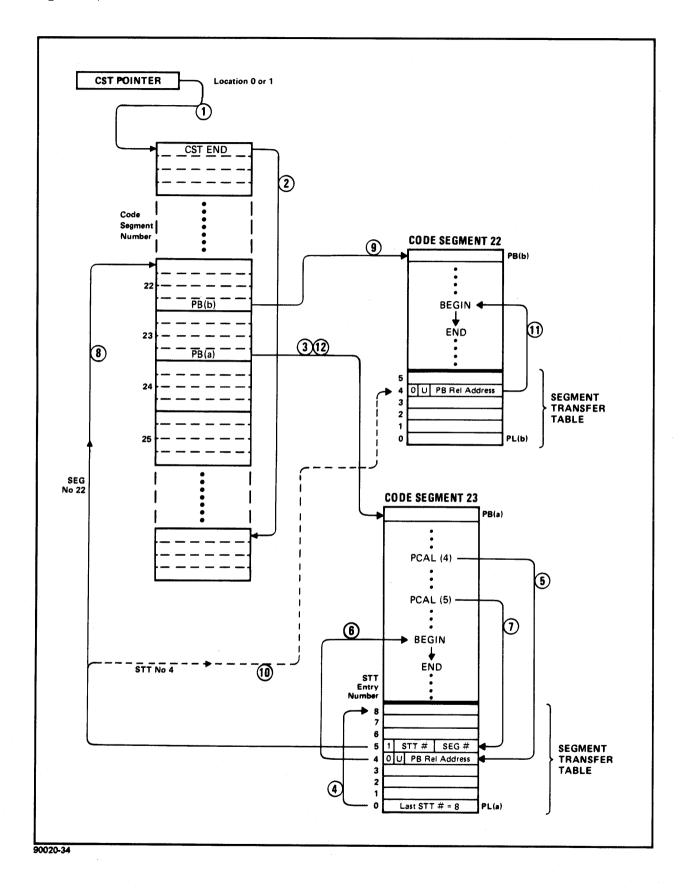

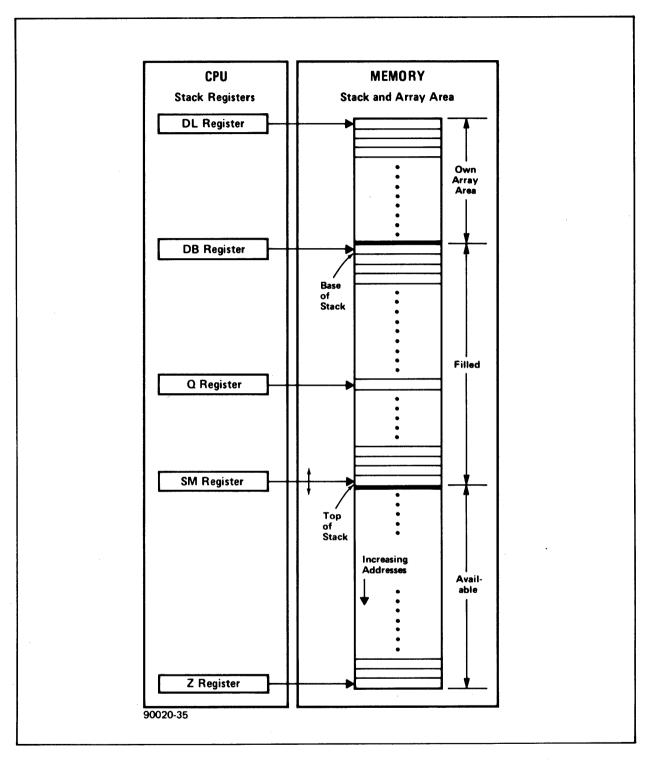

| HARDWARE ORGANIZATION  Bus System  CTL BUS  IOP BUS  SELECTOR CHANNEL BUS PORT CONTROLLER BUS MULTIPLEXER CHANNEL BUS POWER BUS  Functional Hardware Elements CENTRAL PROCESSOR MODULE MAIN MEMORY MULTIPLEXER CHANNEL PORT CONTROLLER/SELECTOR CHANNEL DEVICE CONTROLLERS CTL BUS Priority  OPERATING ENVIRONMENT Virtual Memory Variable-Length Segmentation Processes Data Stacks CPU Registers CODE SEGMENT REGISTERS BASIC TABLE STRUCTURES CODE SEGMENT TABLE AND CODE SEGMENT TABLE EXTENSION | 2-1 2-1 2-1 2-2 2-3 2-3 2-3 2-3 2-3 2-4 2-5 2-6 2-7 2-7 2-7 2-7 2-7 2-9 2-11 2-15 2-15 |

### SECTION II (CONT)

| Paragraph                           | Page         |

|-------------------------------------|--------------|

| DATA SEGMENT TABLE                  | 2-16         |

| Code Segment Linkage                | 2-16         |

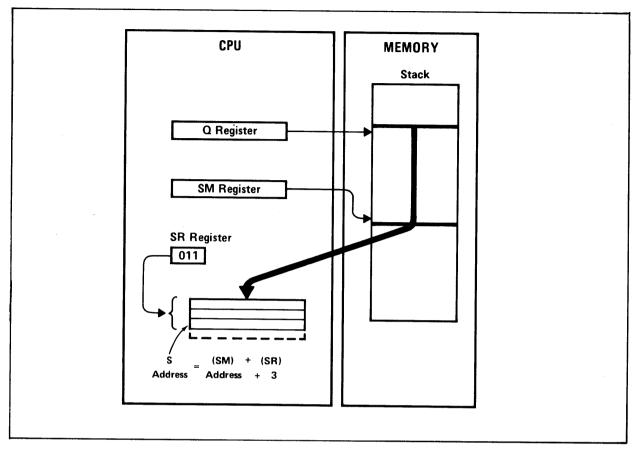

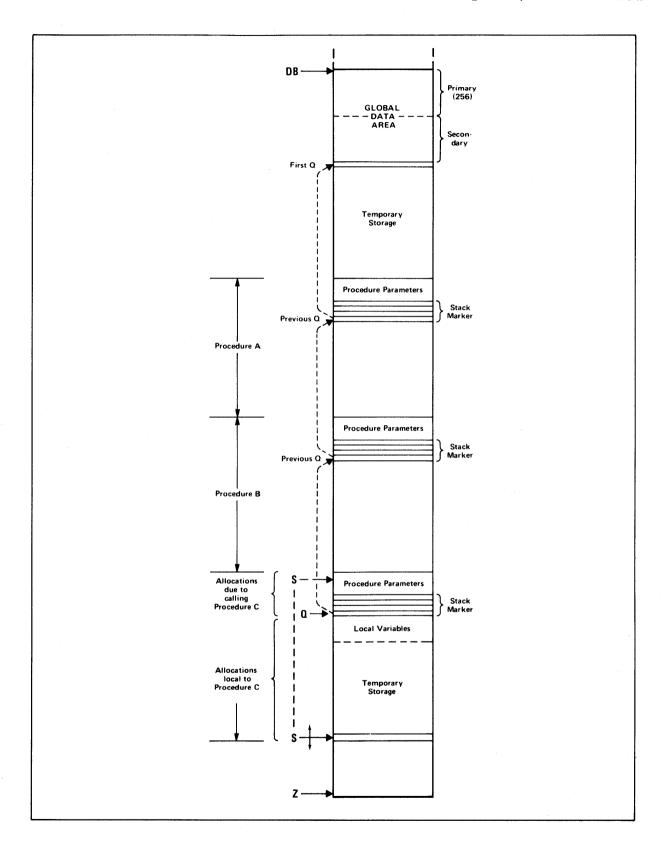

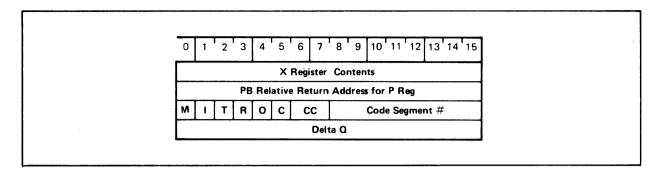

| Stack Operation                     | 2-22         |

| INSTRUCTION AND STATUS WORD FORMATS | 2-27         |

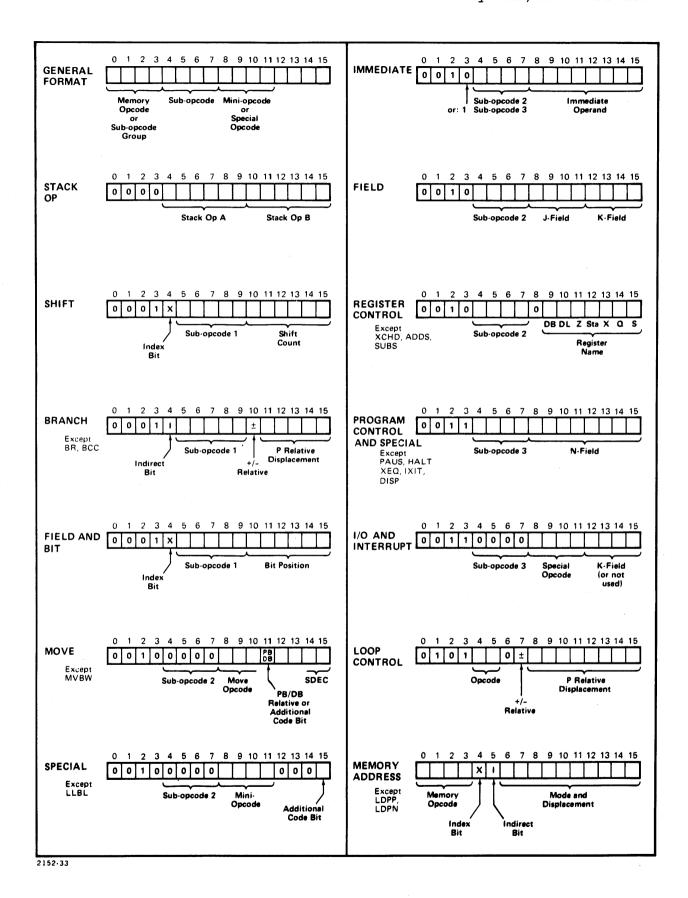

| Instruction Formats                 | 2-27         |

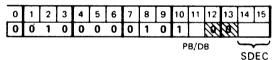

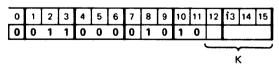

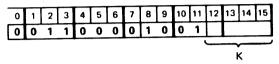

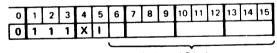

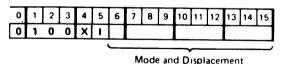

| GENERAL FORMAT                      | 2-28         |

| STACK OP                            | 2-28         |

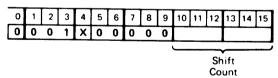

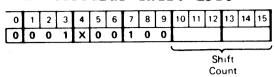

| SHIFT                               | 2-28<br>2-28 |

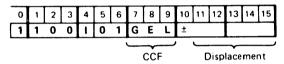

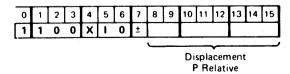

| BRANCH                              |              |

| BIT TEST                            | 2-30         |

| MOVE                                | 2-30         |

| SPECIAL                             | 2-30         |

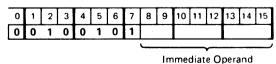

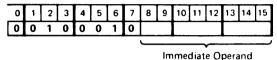

| IMMEDIATE                           | 2-30         |

| FIELD                               | 2-30         |

| REGISTER CONTROL                    | 2-30         |

| PROGRAM CONTROL                     | 2-30         |

| I/O AND INTERRUPT                   | 2-30         |

| LOOP CONTROL                        | 2-30         |

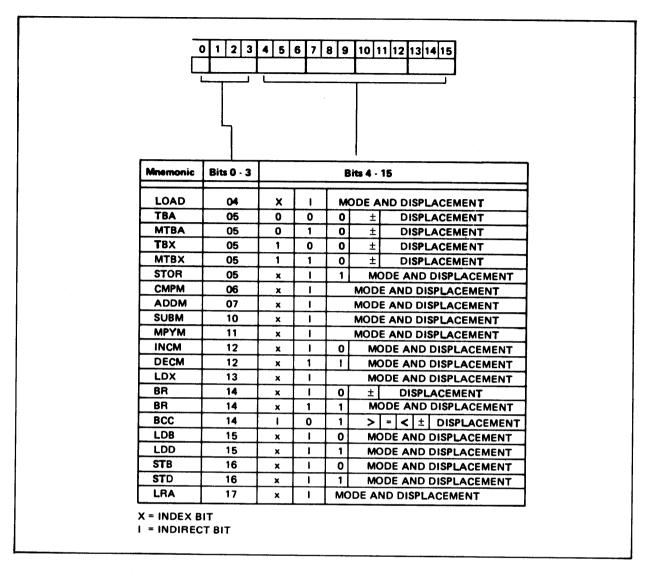

| MEMORY ADDRESS                      | 2-31         |

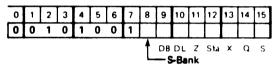

| Status Word Format                  | 2-31         |

| Condition Codes                     | 2-32         |

| OPERATING MODES                     | 2-34         |

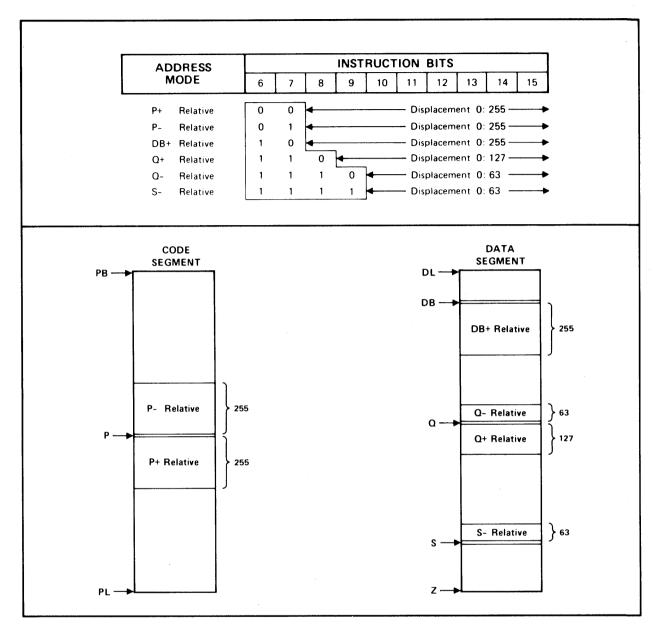

| ADDRESSING CONVENTIONS              | 2-35<br>2-35 |

| Memory Addressing                   | 2-35         |

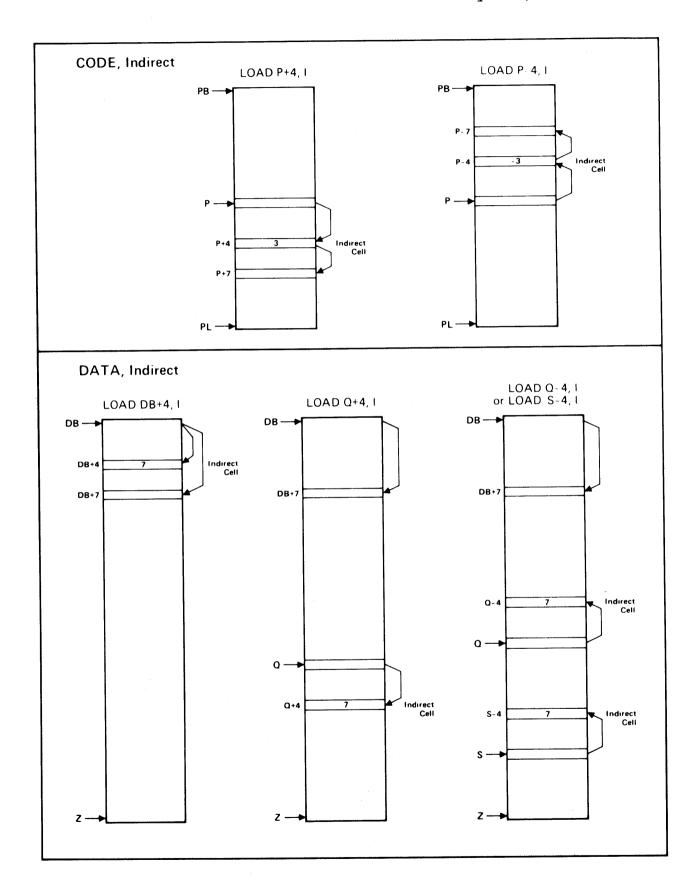

| CODE INDIRECT                       | 2-30         |

| DATA INDIRECT                       | 2-38         |

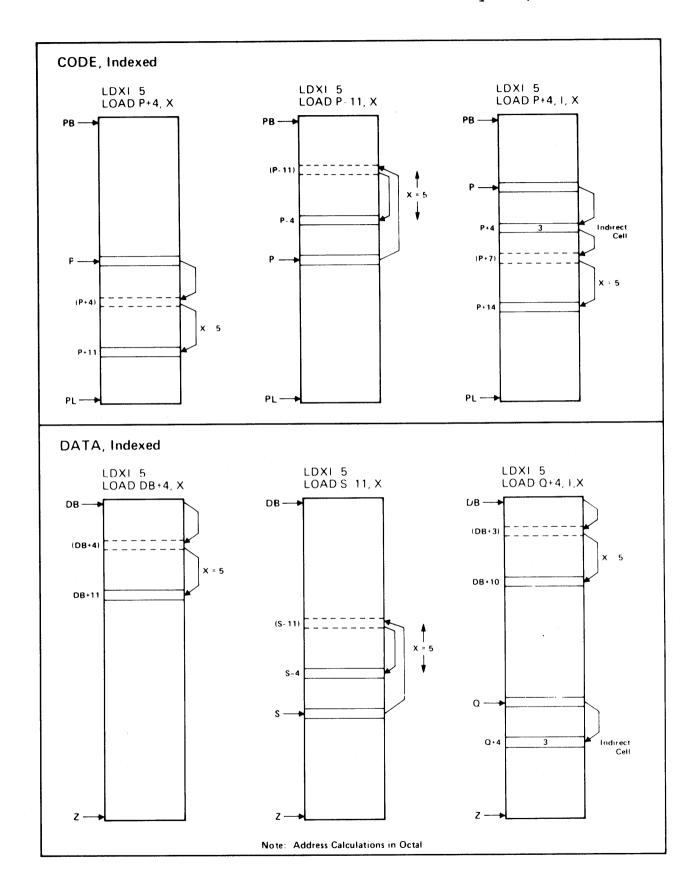

| Indexing                            | 2-38         |

| CODE INDEXING                       | 2-38         |

| DATA INDEXING                       | 2-40         |

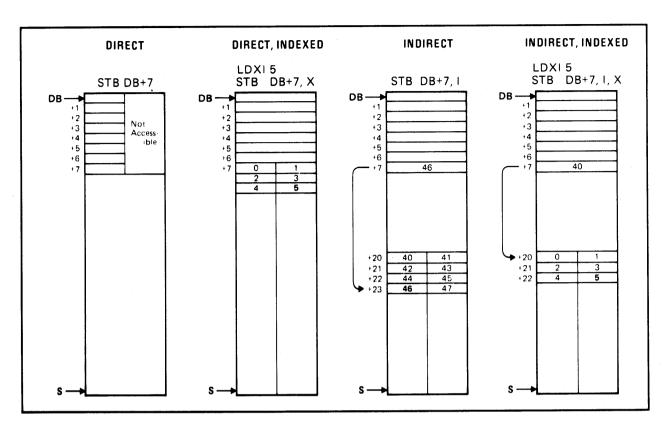

| Byte Addressing                     | 2-40         |

| DIRECT BYTE ADDRESSING              | 2-40         |

| DIRECT, INDEXED BYTE ADDRESSING     | 2-41         |

| INDIRECT BYTE ADDRESSING            | 2-41         |

| INDIRECT, INDEXED BYTE ADDRESSING   | 2-41         |

| Double-Word Indexing                | 2-42         |

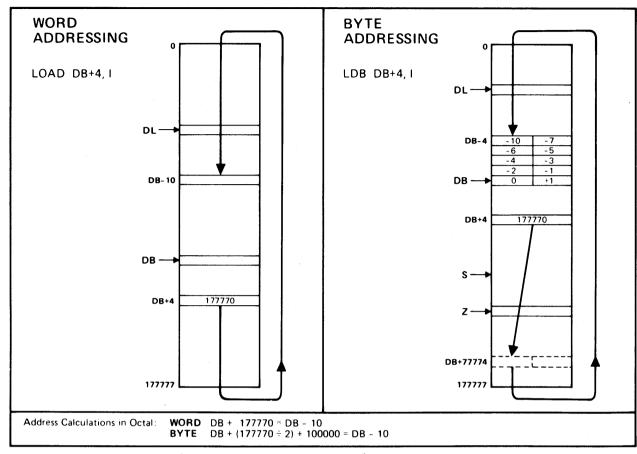

| Accessing DB- Area                  | 2-42         |

| WORD ADDRESSING                     | 2-42         |

| BYTE ADDRESSING                     | 2-42         |

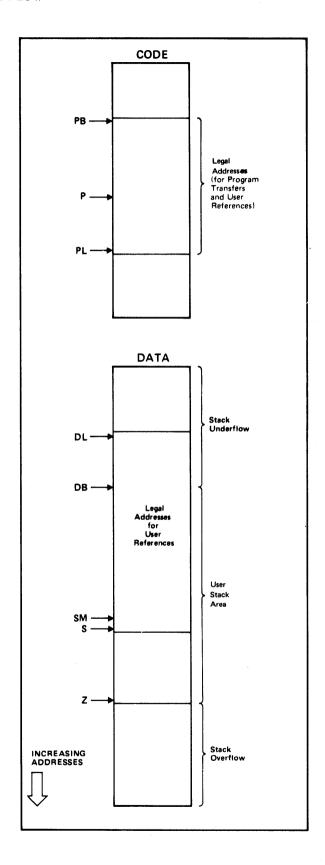

| Bounds Checking                     | 2-43         |

| PROGRAM TRANSFER LIMIT              | 2-45         |

| PROGRAM REFERENCE LIMITS            | 2-45         |

| DATA REFERENCE LIMITS               | 2-45         |

| STACK OVERFLOW LIMIT                | 2-45         |

| STACK UNDERFLOW LIMIT               | 2-45         |

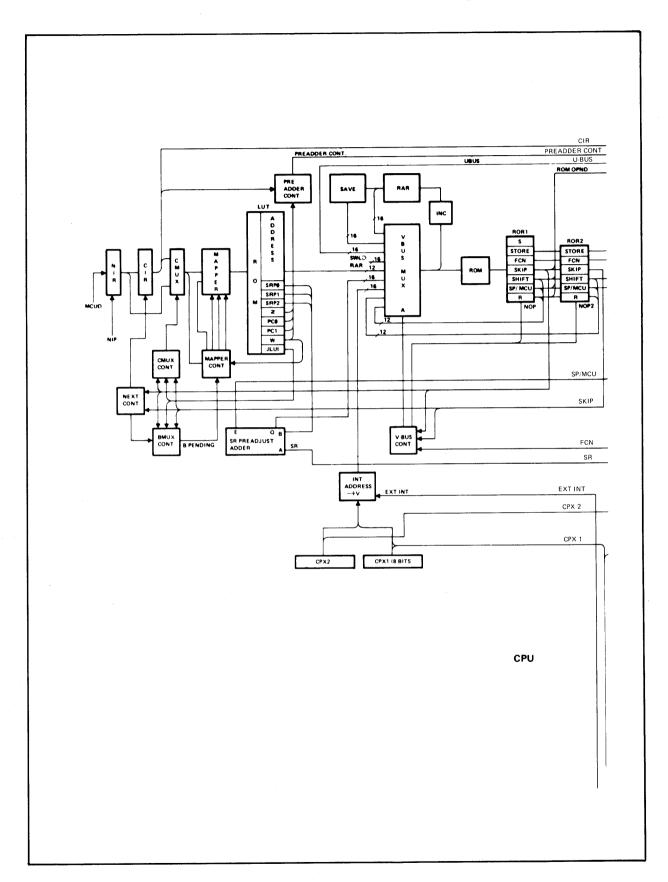

| CPU OVERVIEW                        | 2-45         |

| Pipelines                           | 2-46         |

| DATA PIPELINE                       | 2-46         |

| MICROCODE PIPELINE                  | 2-49         |

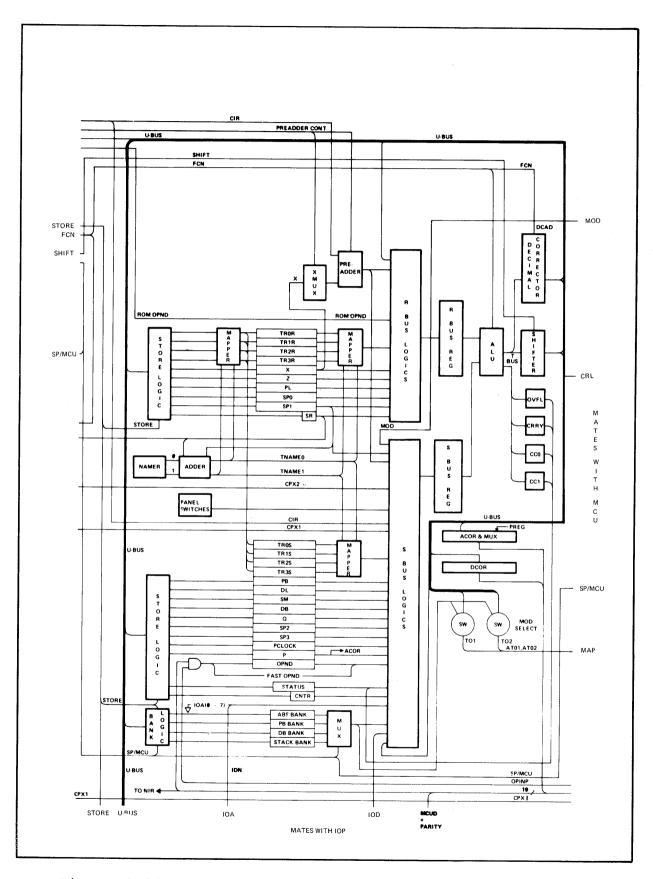

| CPU Component Descriptions          | 2-50         |

| NIR                                 | 2-50         |

SECTION II (CONT)

| Paragraph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Page                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| CIR CMUX AND CMUX CONTROL MAPPER AND MAPPER CONTROL LUT ROM VBUS MUX AND VBUS CONTROL RAR SAVE REGISTER ROM ROR1 AND ROR2 Microcode Jumps S-Bus Field Decoder (S) Store Field Decoder (STORE) Function Field Decoder (FCN) Skip Field Decoder (SKIP) Shift Field Decoder (SHIFT) Special Field Decoder (SP) MCU Option Field Decoder (MCU) R-Bus Field Decoder (R) PROCESSOR REGISTERS Renamer Logic TOS Registers Index Register (X) Stack Limit Register (Z) Program Limit Register (FL) Scratch Pad 1 Register (SP1) Stack Register (SR) Program Base Register (PB) Data Limit Register (SR) Program Base Register (PB) Data Limit Register (SR) Program Base Register (PB) Data Limit Register (SR) Program Base Register (SR) Program Base Register (PB) Data Base Register (PC) Scratch Pad 2 Register (SP3) Process Clock Register (PCLOCK) Program Counter Register (PCLOCK) Program Counter Register (PND) Status Register (STA) Counter Register (CNTR) OVERPLOW FLIP-FLOP (OVFL) CARRY FLIP-FLOP (OVFL) | 2-50<br>2-51<br>2-51<br>2-51<br>2-52<br>2-52<br>2-53<br>2-55<br>2-55<br>2-55<br>2-55<br>2-55 |

| CARRY FLIP-FLOP (CRRY)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-60<br>2-60<br>2-60                                                                         |

| R-BUS REGISTER S-BUS REGISTER ALU SHIFTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2-60<br>2-60<br>2-60<br>2-60                                                                 |

| DECIMAL CORRECTOR  ADDRESS COMPUTER OUTPUT REGISTER (ACOR)  DATA COMPUTER OUTPUT REGISTER (DCOR)  INTERRUPT STATUS REGISTER 1 (CPX1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-60<br>2-60<br>2-60                                                                         |

| SECTI | ON | ΙI | (CONT) |

|-------|----|----|--------|

|       |    |    |        |

| Paragraph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Page                                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| INTERRUPT STATUS REGISTER 2 (CPX2)  CPU Servicing Information                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-61<br>2-61<br>2-61<br>2-62<br>2-63<br>2-64                                                                         |

| SECTION III - SYSTEM VERIFICATION AND TROUBLESHOOTING                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                      |

| Paragraph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Page                                                                                                                 |

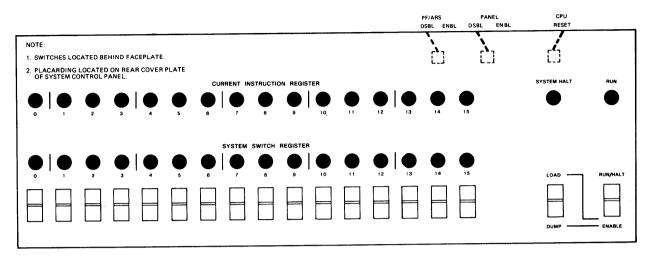

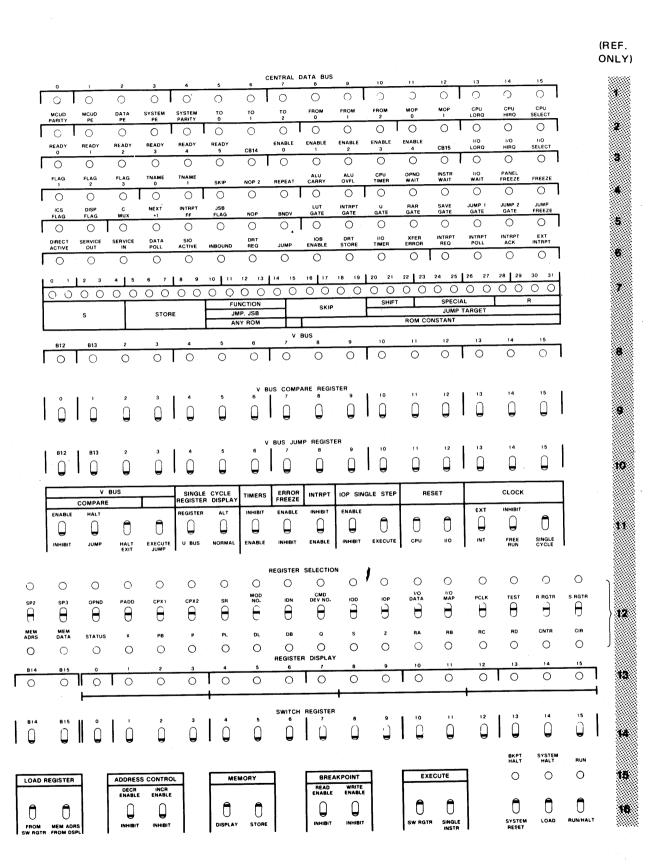

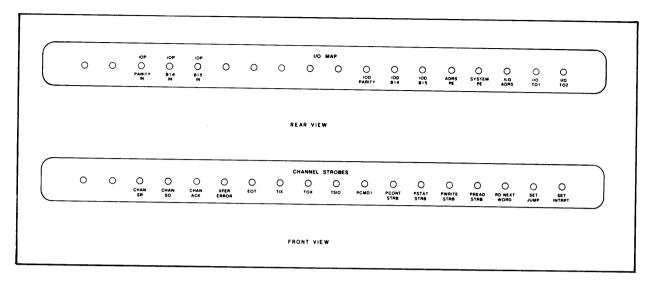

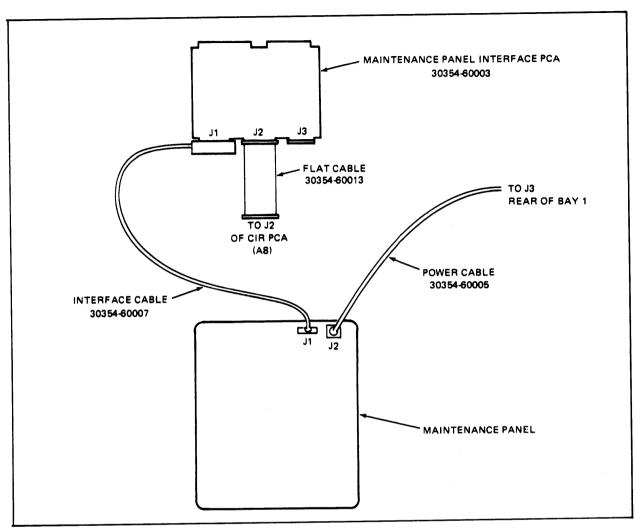

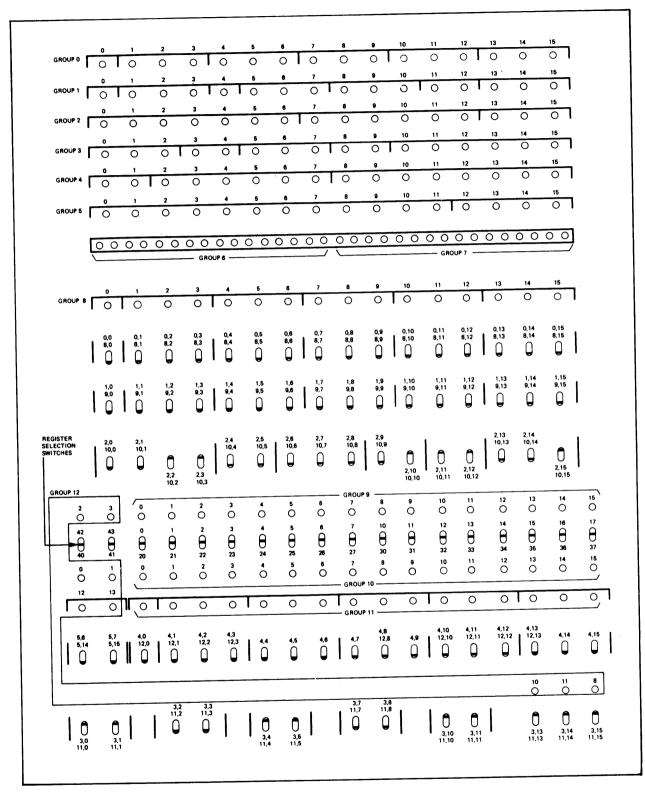

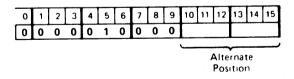

| DIAGNOSTIC AND VERIFICATION PROGRAMS On-Line Verification Programs Stand-Alone Diagnostic Programs Microdiagnostics SLEUTH 3000  SYSTEM TROUBLESHOOTING AND REPAIR  SYSTEM CONTROL PANEL  MAINTENANCE PANEL Switch/Lamp Identification and Description Operating Precautions Preparation For Use General Operating Method Using Maintenance Panel and System Control Panel Stack Register Loading CPU Register Displays General-Use Display Maintenance Panel Test LAMP TEST SWITCH TEST | 3-1<br>3-1<br>3-1<br>3-2<br>3-2<br>3-2<br>3-4<br>3-6<br>3-23<br>3-24<br>3-25<br>3-26<br>3-26<br>3-26<br>3-26<br>3-28 |

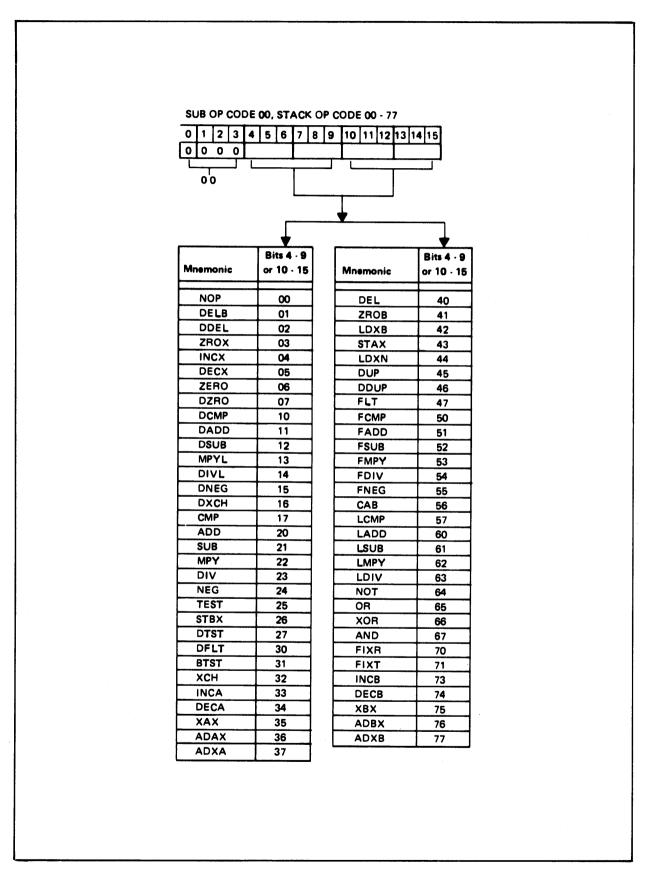

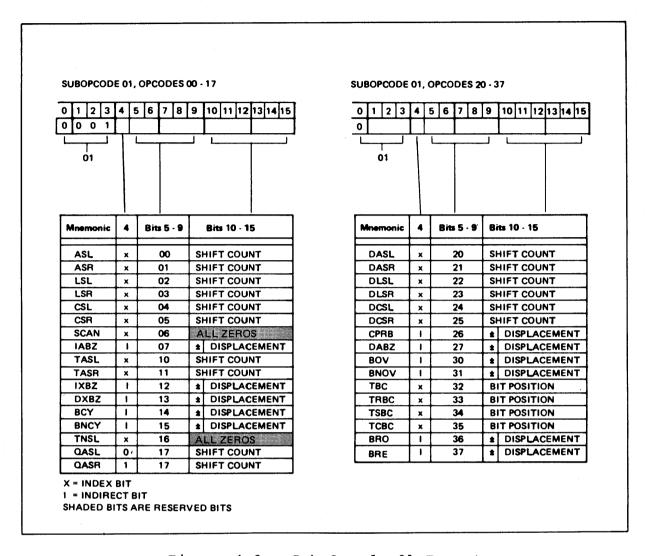

| SECTION IV - MACHINE INSTRUCTIONS AND STACK OPERATIONS  Paragraph                                                                                                                                                                                                                                                                                                                                                                                                                        | Page                                                                                                                 |

| INSTRUCTION DECODING TRAPS AND INTERRUPTS  CONDITION CODE INSTRUCTION FORMATS INSTRUCTION DEFINITIONS Stack Op Instructions Shift Instructions Branch Instructions Privileged Memory Reference Instructions Immediate Instructions Register Control Instructions Program Control and Special Instructions I/O Instructions                                                                                                                                                               | 4-1<br>4-3<br>4-3<br>4-3<br>4-10<br>4-11<br>4-12<br>4-13<br>4-14<br>4-15<br>4-17                                     |

|  | S | E | CT | Ι | ON | ΙV | (CONT) |

|--|---|---|----|---|----|----|--------|

|--|---|---|----|---|----|----|--------|

| Paragraph                                                                                                                                                                                                                                                                                                                                                                            | Page                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

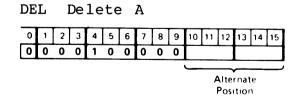

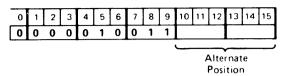

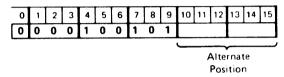

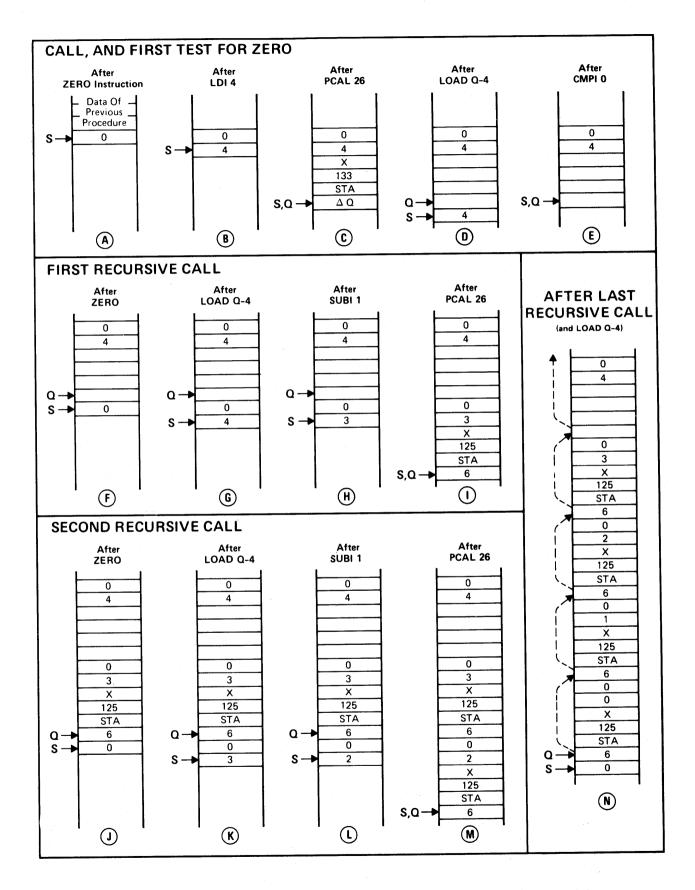

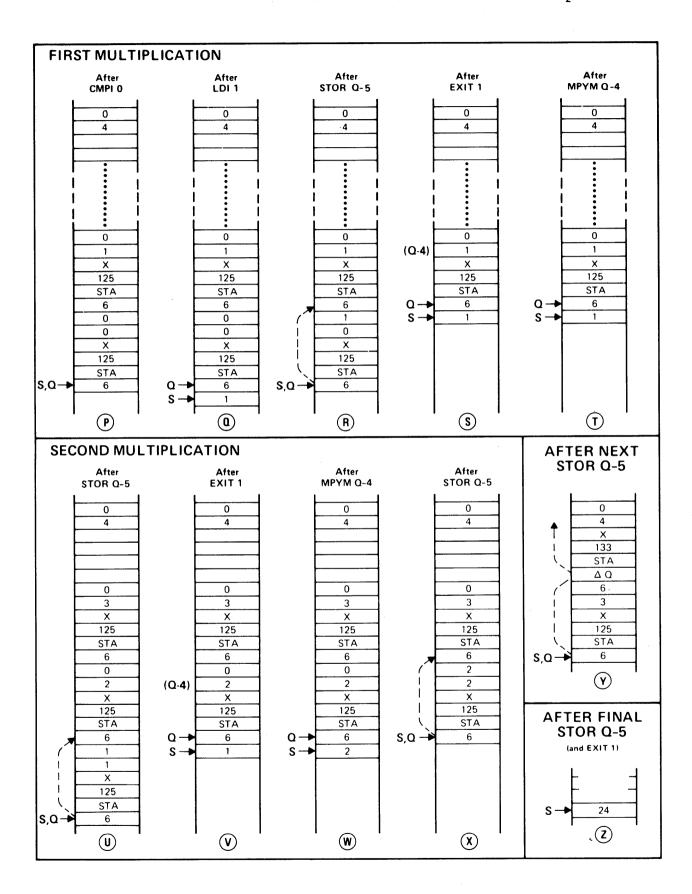

| Memory Address Instructions Instruction Commentary  STACK OPERATION EXAMPLES Basic Arithmetic Procedure Calls Recursion  MAIN PROGRAM CALL TEST FOR ZERO FIRST RECURSIVE CALL SUCCESSIVE RECURSIONS FIRST EXIT FIRST RECURSIVE EXIT SUCCESSIVE EXITS                                                                                                                                 | 4-19<br>4-21<br>4-37<br>4-37<br>4-39<br>4-43<br>4-46<br>4-46<br>4-46<br>4-48<br>4-48<br>4-48 |

| SECTION V - SYSTEM MICROCODE                                                                                                                                                                                                                                                                                                                                                         |                                                                                              |

| Paragraph                                                                                                                                                                                                                                                                                                                                                                            | Page                                                                                         |

| GENERAL INFORMATION Stack Element Locations PUSH POP QUP QUP QUP QDWN Reading Microprogram Listings MICROINSTRUCTION DESCRIPTIONS R-Bus Field S-Bus Field Function Field Shift Field Store Field Store Field Store Field MCU Option Field Skip Field MCU Option Field Skip Field MCU Option Field Skip Field MICRODIAGNOSTICS  SECTION VI - MODULE CONTROL UNIT/MAIN MEMORY OVERVIEW | 5-1<br>5-2<br>5-2<br>5-3<br>5-3<br>5-3<br>5-5<br>5-5<br>5-5<br>5-5<br>5-5<br>5-5             |

| Paragraph                                                                                                                                                                                                                                                                                                                                                                            | Page                                                                                         |

| MCU OPERATIONS  Fetch Next Instruction Operations CPU ADDRESS TRANSMIT  MEMORY RECEIVE AND TRANSMIT  CPU RECEIVE  Fetch An Operand Operations CPU ADDRESS TRANSMIT  MEMORY RECEIVE AND TRANSMIT  CPU RECEIVE AND TRANSMIT  CPU RECEIVE                                                                                                                                               | 6-1<br>6-1<br>6-3<br>6-5<br>6-5<br>6-5<br>6-5                                                |

### SECTION VI (CONT)

| Paragraph                           | Page |

|-------------------------------------|------|

| Store An Operand Operations         | 6-6  |

| CPU ADDRESS TRANSMIT                | 6-6  |

| MEMORY RECEIVE                      | 6-6  |

| CPU DATA TRANSMIT                   | 6-6  |

| MEMORY RECEIVE                      | 6-6  |

| Command A Module                    | 6-6  |

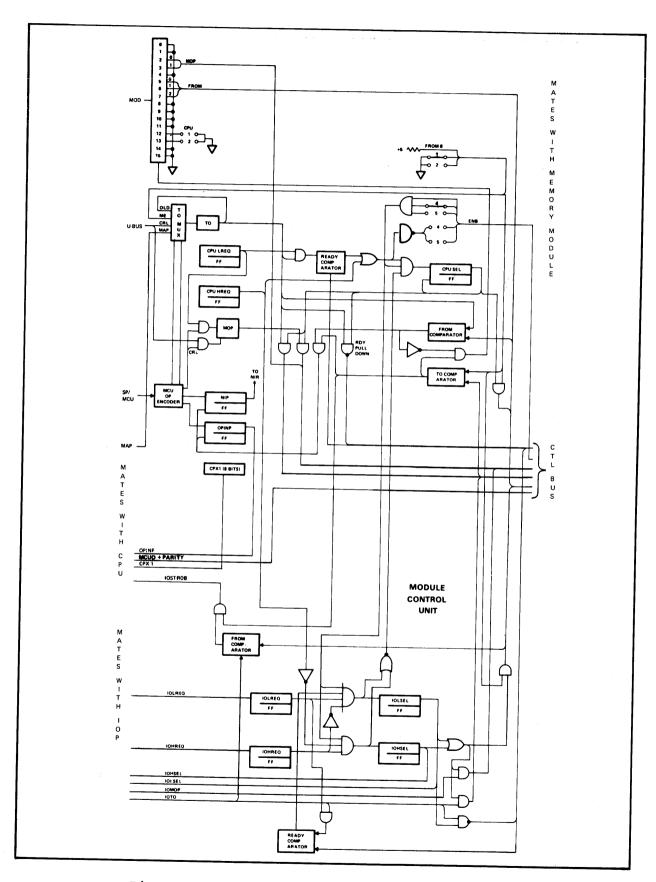

| MCU SERVICING INFORMATION           | 6-8  |

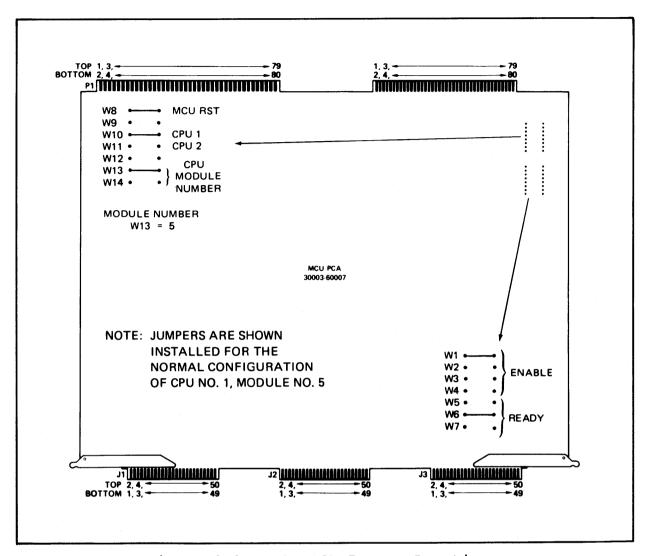

| ENABLE                              | 6-8  |

| READY                               | 6-8  |

| CPU NUMBER                          | 6-8  |

| CPU MODULE NUMBER                   | 6-9  |

| MCU RESET                           | 6-9  |

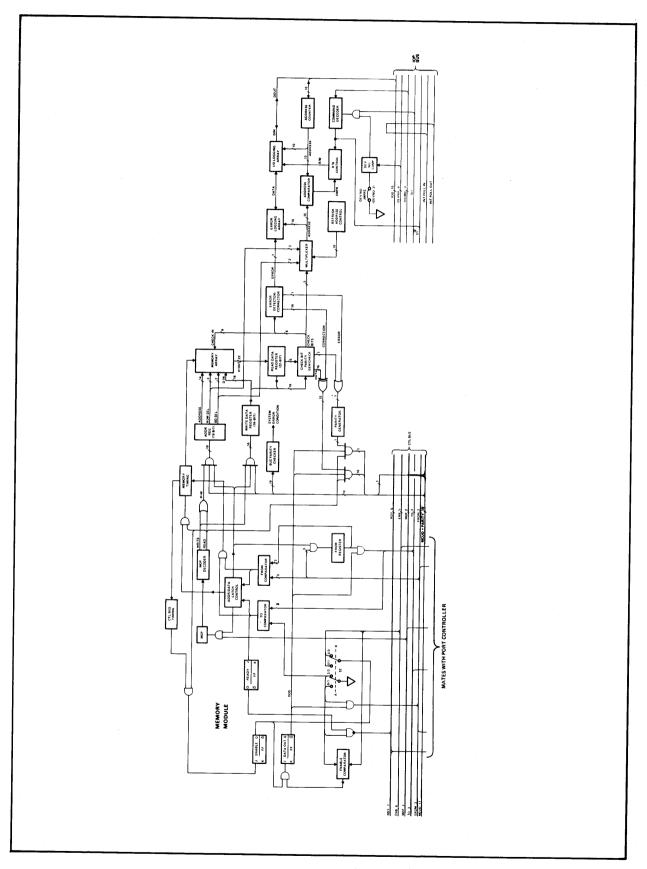

| MAIN MEMORY                         | 6-9  |

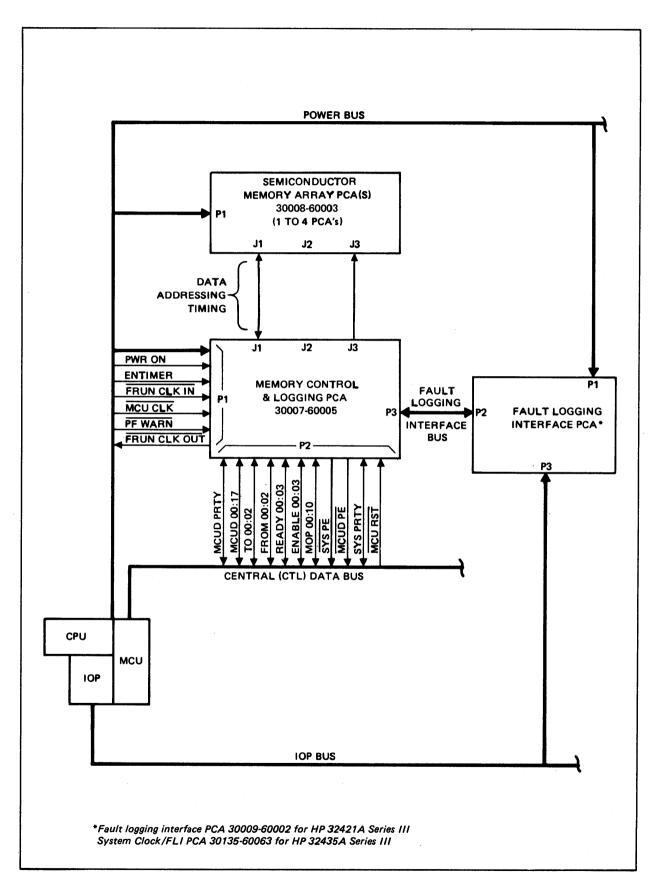

| Memory PCA Interfacing              | 6-9  |

| CTL BUS                             | 6-9  |

|                                     | 6-11 |

| IOP BUS FAULT LOGGING INTERFACE BUS | 6-11 |

|                                     | 6-11 |

| POWER BUS                           | 6-12 |

| Memory PCA Descriptions             | 6-12 |

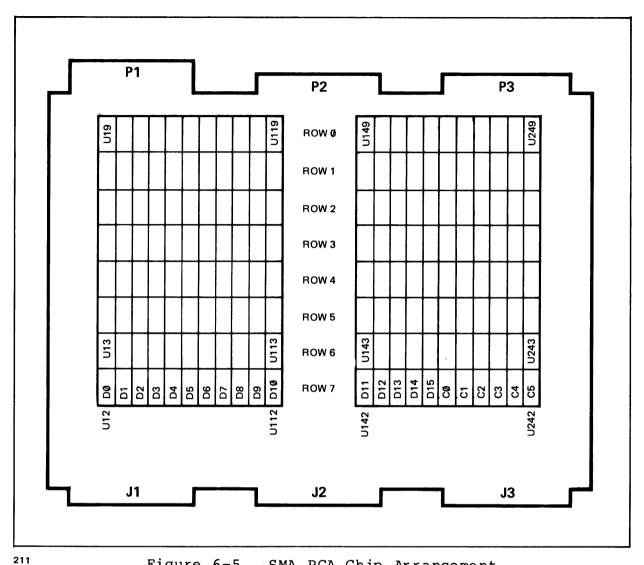

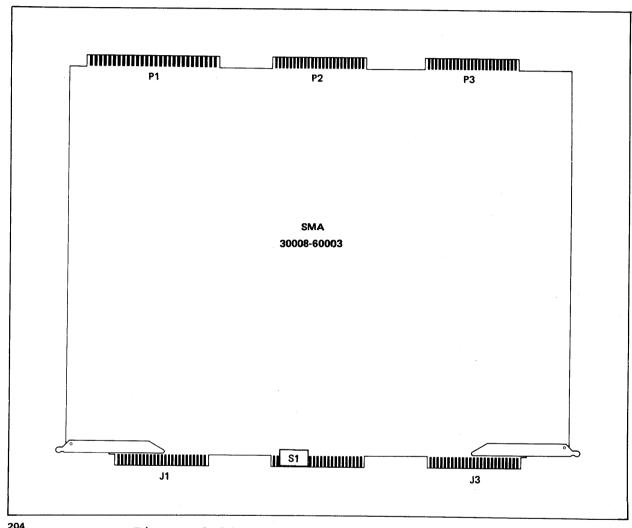

| SMA PCA                             | 6-12 |

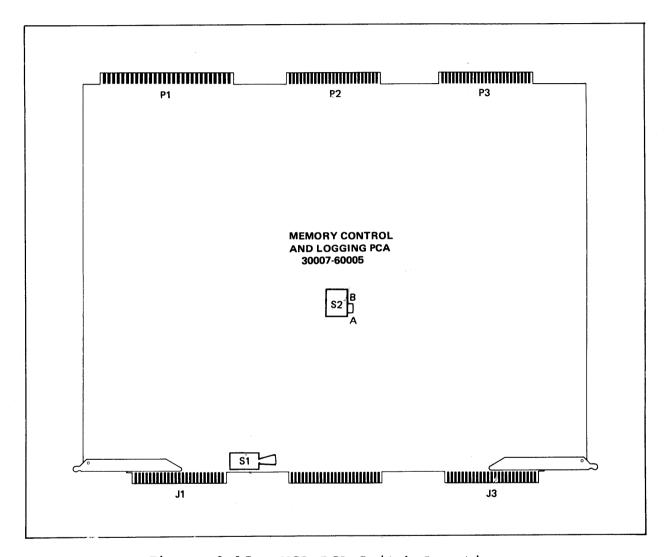

| MCL PCA                             | 6-12 |

| FLI PCA                             | -    |

| Memory Operations                   | 6-12 |

| READ                                | 6-13 |

| WRITE                               | 6-13 |

| NOP                                 | 6-14 |

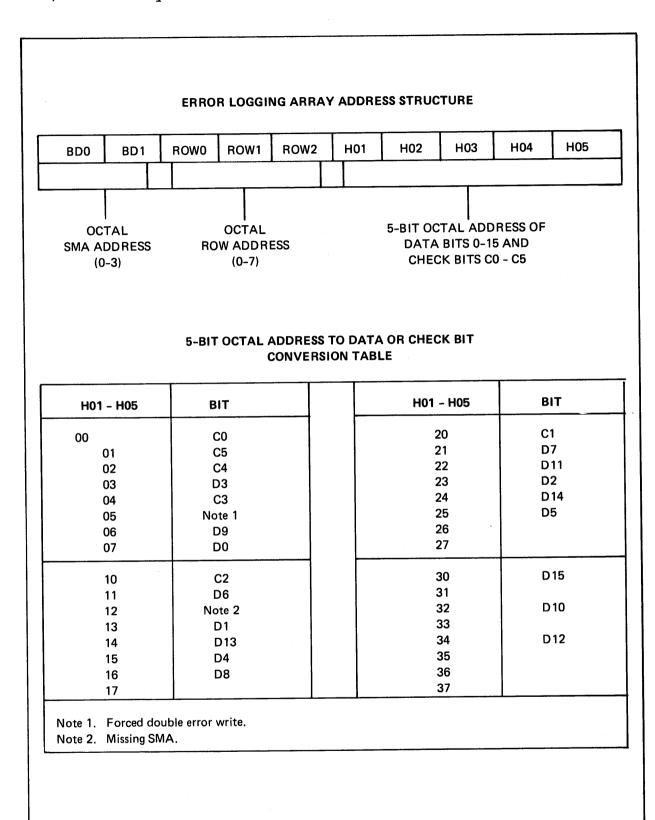

| FAULT CORRECTION AND ERROR LOGGING  | 6-14 |

| Memory Servicing Information        | 6-14 |

| FAULT CORRECTION                    | 6-14 |

| MEMORY ERROR LOGGING FACILITY       | 6-17 |

| Output                              | 6-21 |

| Errors                              | 6-21 |

| Obtaining Memory Errors Copy        | 6-21 |

| FLI PCA PROGRAMMING                 | 6-21 |

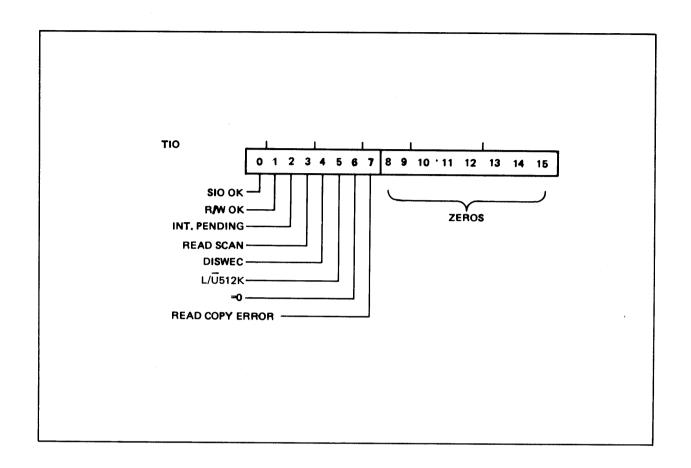

| TIO Command ,                       | 6-23 |

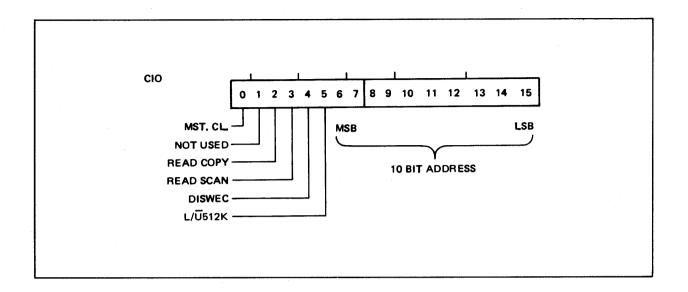

| CIO Command                         | 6-24 |

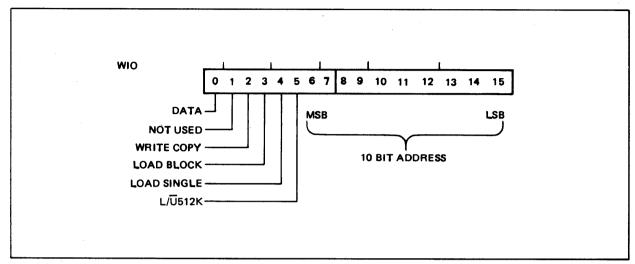

| WIO Command                         | 6-26 |

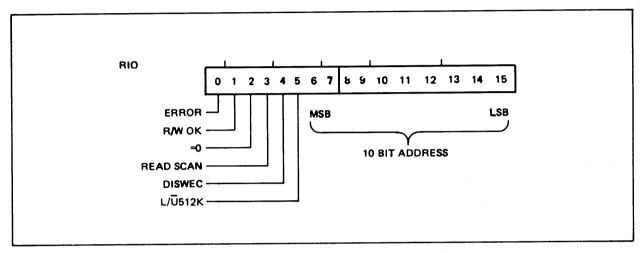

| RIO Command                         | 6-27 |

| SMA PCA SERVICING                   | 6-27 |

| MCL PCA SERVICING                   | 6-28 |

| FLI PCA SERVICING                   | 6-29 |

|                                     |      |

|                                     |      |

| SECTION VII - I/O SYSTEM            |      |

| Paragraph                           | Page |

|                                     | _    |

| INTRODUCTION                        | 7-1  |

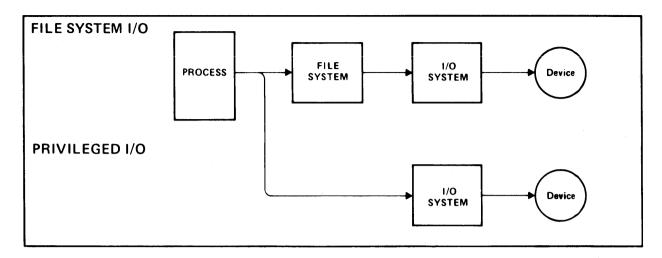

| FILE SYSTEM OPERATION               | 7-2  |

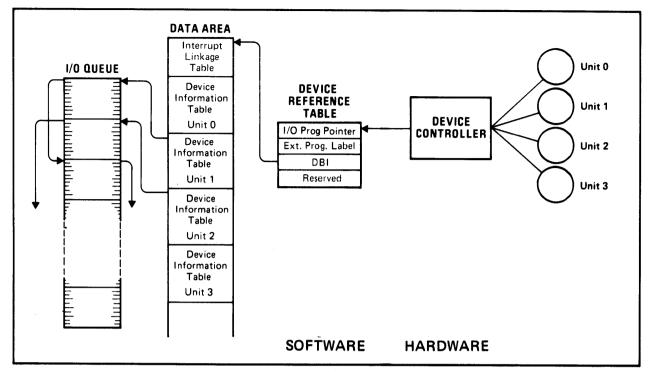

| DEFINITION OF TERMS                 | 7-3  |

| I/O INSTRUCTIONS                    | 7-6  |

SECTION VII (CONT)

| Paragraph                                       | Page         |

|-------------------------------------------------|--------------|

| GENERAL I/O OPERATION                           | 7-7<br>7-9   |

| Direct Read                                     | 7-12         |

| Direct Write                                    | 7-13         |

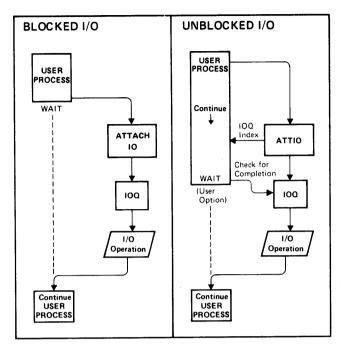

| BLOCKED/UNBLOCKED I/O                           | 7-14         |

| Blocked I/O                                     | 7-14         |

| Unblocked I/O                                   | 7-14         |

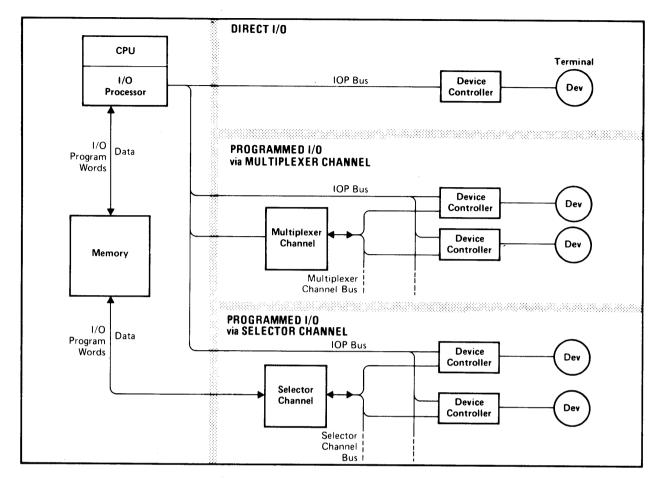

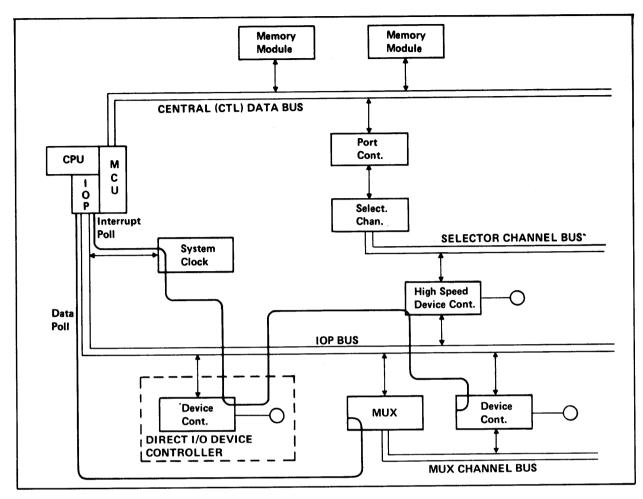

| I/O HARDWARE ELEMENTS                           | 7-15         |

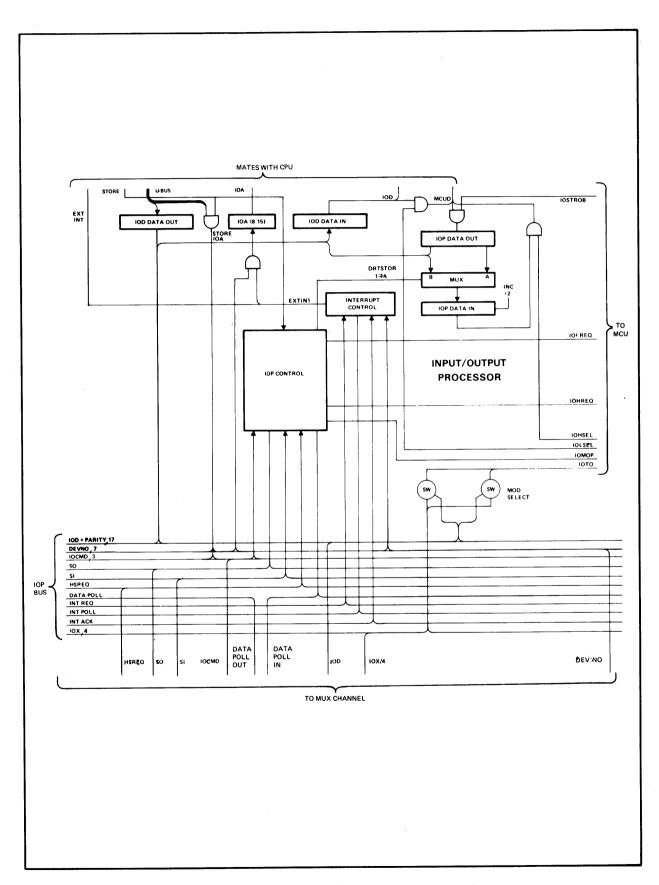

| I/O Processor                                   | 7-15         |

| I/O COMMAND                                     | 7-16         |

| IOP CONTROL                                     | 7-18         |

| INTERRUPT CONTROL                               | 7-18         |

| INT DEVNO                                       | 7-18         |

| DATA OUTPUT REGISTERS                           | 7-18         |

| DATA INPUT REGISTERS                            | 7-18         |

| Module Control Unit                             | 7-18<br>7-19 |

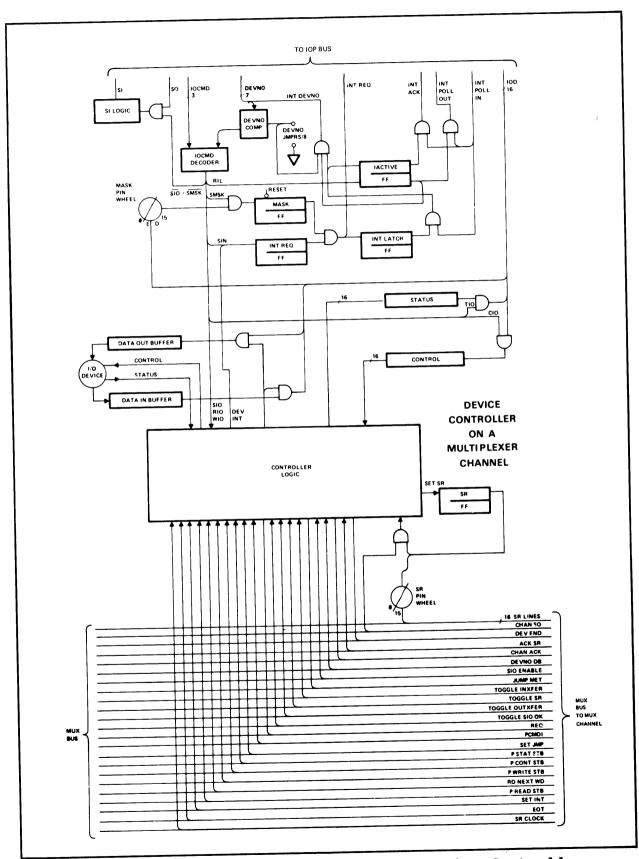

| Multiplexer Channel                             | 7-19         |

| I/O SYSTEM FUNCTIONAL OPERATION                 | 7-19         |

| I/O Priorities                                  | 7-20         |

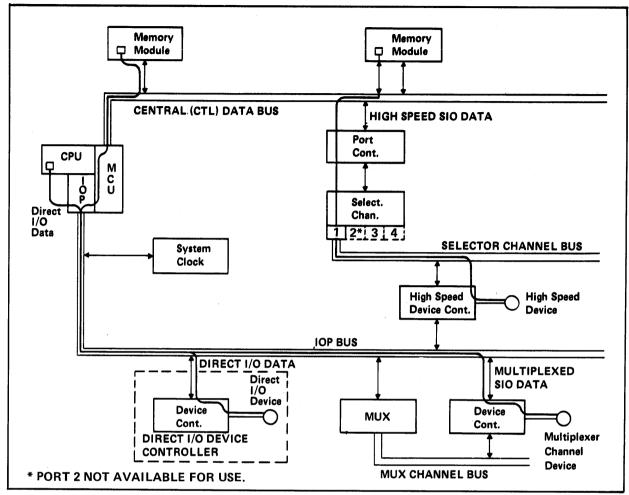

| I/O Data Routes                                 | 7-22         |

| I/O Transfer Modes                              | 7-23         |

| DIRECT I/O                                      | 7-23         |

| PROGRAMMED I/O                                  | 7-24         |

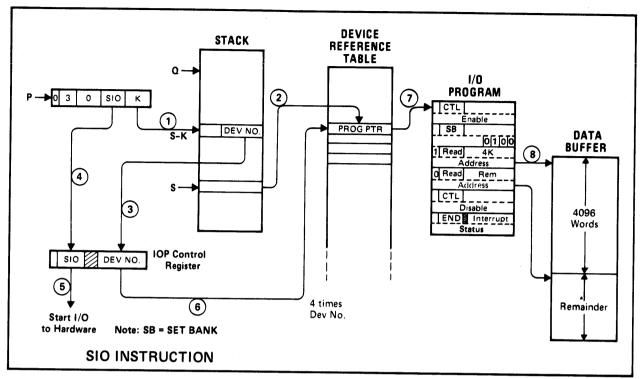

| I/O Program Word                                | 7-24         |

| Typical I/O Program Operation                   | 7-25         |

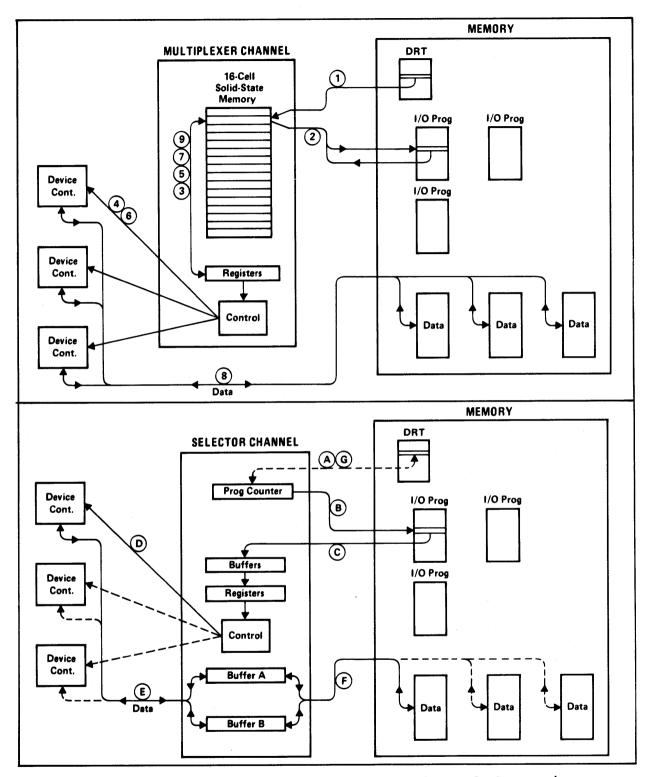

| Multiplexer Channel Transfers                   | 7-26         |

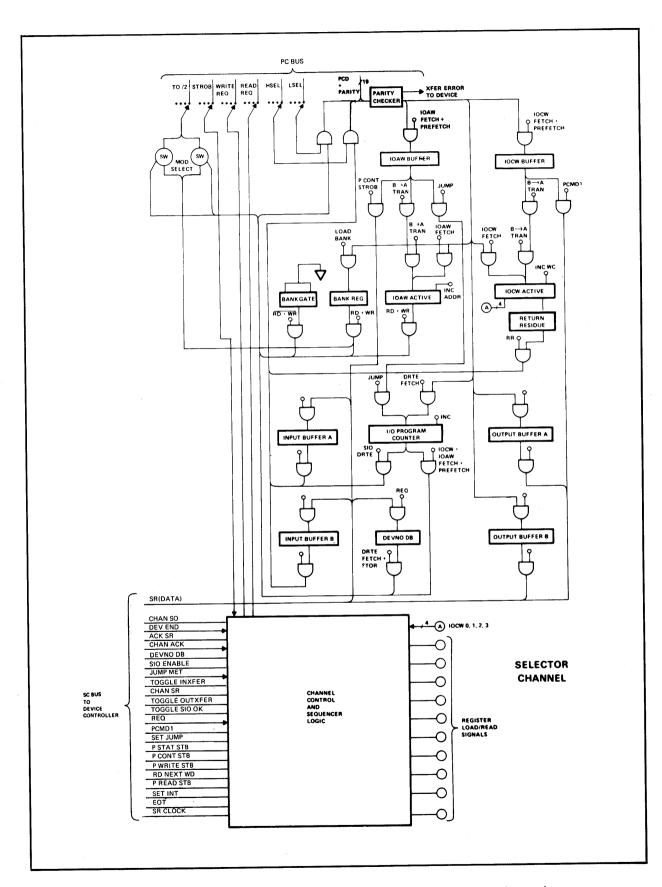

| Selector Channel Transfers                      | 7-28         |

| Multiplexer Channel Operations                  | 7-28         |

| INITIALIZE                                      | 7-28         |

| DRT FETCH                                       | 7-30<br>7-32 |

| I/O PROGRAM WORD TRANSFERS                      | 7-32         |

| IOAW Fetch                                      | 7-33         |

| IOAW Store                                      | 7-33         |

| Next Operation                                  | 7-34         |

| DATA TRANSFERS                                  | 7-34         |

| Address Transfer                                | 7-34         |

| Output Transfer                                 | 7-35         |

| Input Transfer                                  | 7-35         |

| End Of Transfer By Word Count                   | 7-35         |

| End Of Transfer By Device                       | 7-35         |

| Selector Channel and Port Controller Operations | 7-36         |

| PORT CONTROLLER                                 | 7-36         |

| INITIATOR SEQUENCE                              | 7-38         |

| FETCH SEQUENCE                                  | 7-40<br>7-42 |

| EXECUTE SEQUENCES                               | 7-42         |

| Interrupt                                       | 7-42         |

| Jump                                            | 7-43         |

| Control                                         | 7-43         |

SECTION VII (CONT)

| Paragraph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Page                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Set Bank Read Return Residue Write End I/O SYSTEM SERVICING INFORMATION IOP PCA Servicing ENABLE/DISABLE MEMORY SIZE MEMORY INTERLEAVING Selector Channel Maintenance Board PCA Multiplexer Channel PCA Servicing Port Controller PCA Servicing Selector Channel Servicing Selector Channel REGISTER PCA Port Controller Channel Number Memory Size Memory Interleaving SELECTOR CHANNEL CONTROL PCA SELECTOR CHANNEL SEQUENCER PCA                                                           | 7-43<br>7-43<br>7-44<br>7-45<br>7-46<br>7-46<br>7-46<br>7-46<br>7-46<br>7-48<br>7-48<br>7-48<br>7-48<br>7-48<br>7-48 |

| SECTION VIII - INTERRUPT SYSTEM                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                      |

| SECTION VIII INTERROLL SIGIBM                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                      |

| Paragraph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Page                                                                                                                 |

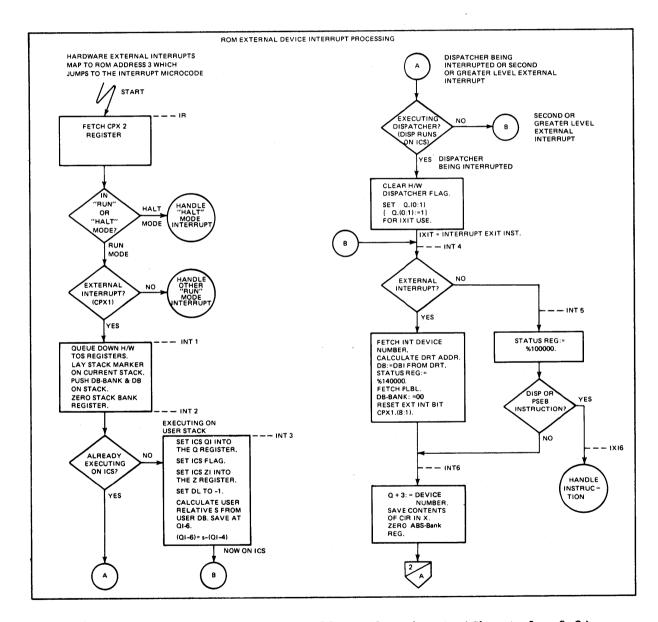

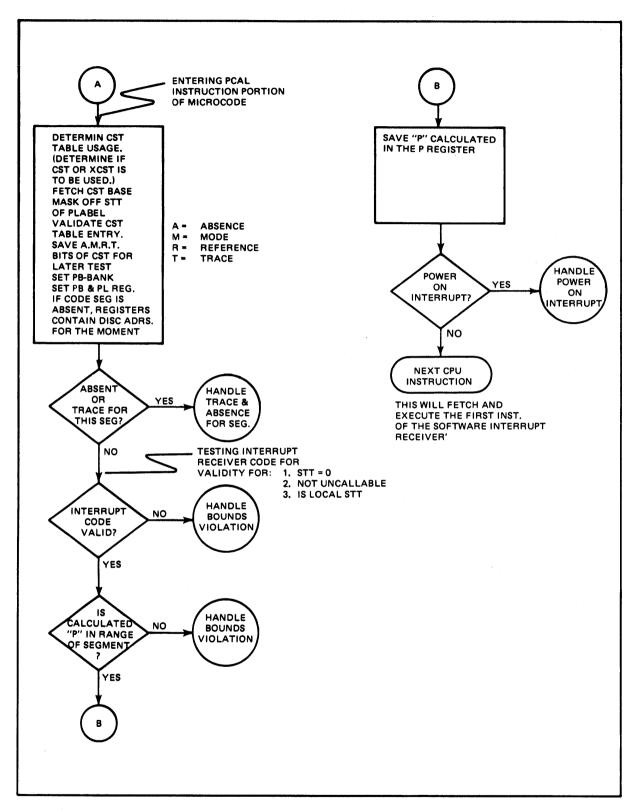

| INTRODUCTION INTERRUPT SYSTEM OVERVIEW INTERRUPT CONTROL STACK INTERRUPT TYPES  External Interrupts ICS Internal Interrupts Non-ICS Internal Interrupts EXTERNAL INTERRUPT PROCESSING Interrupt Priorities Interrupt Program Pointer Sequence Of Operations INTERNAL INTERRUPT PROCESSING General Descriptions BOUNDS VIOLATION ILLEGAL MEMORY ADDRESS NON-RESPONDING MODULE SYSTEM PARITY ERROR ADDRESS PARITY ERROR DATA PARITY ERROR MODULE INTERRUPT POWER FAIL UNIMPLEMENTED INSTRUCTION | 8-1<br>8-3<br>8-5<br>8-6<br>8-7<br>8-8<br>8-8<br>8-8<br>8-13<br>8-14<br>8-14<br>8-14<br>8-14<br>8-15<br>8-15         |

| STT VIOLATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8-15<br>8-15<br>8-15                                                                                                 |

| DDI ATOHUTTON ********************************                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0 10                                                                                                                 |

SECTION VIII (CONT)

| Paragraph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Page                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

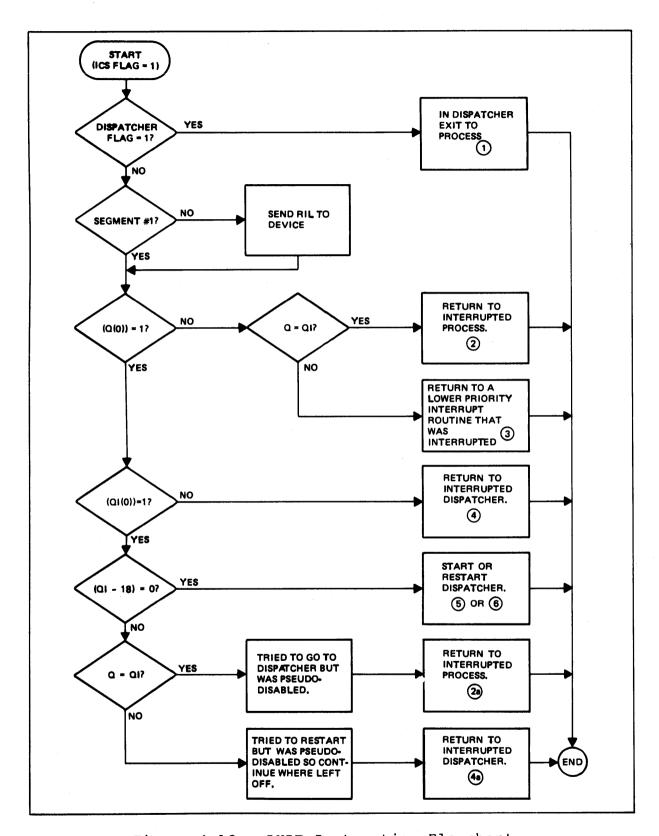

| STACK UNDERFLOW PRIVILEGED MODE VIOLATION STACK OVERFLOW INTEGER OVERFLOW FLOATING-POINT OVERFLOW FLOATING-POINT UNDERFLOW INTEGER DIVIDE BY ZERO FLOATING-POINT DIVIDE BY ZERO EXTENDED PRECISION FLOATING-POINT UNDERFLOW EXTENDED PRECISION FLOATING-POINT UNDERFLOW EXTENDED PRECISION FLOATING-POINT DIVIDE BY ZERO DECIMAL OVERFLOW INVALID ASCII DIGIT INVALID ASCII DIGIT INVALID WORD COUNT RESULT WORD COUNT OVERFLOW DECIMAL DIVIDE BY ZERO ABSENT CODE SEGMENT TRACE STT ENTRY UNCALLABLE ABSENT DATA SEGMENT POWER ON COLD LOAD Sequence For ICS-Type Interrupts Sequence For Non-ICS Type Interrupts INTERRUPT HANDLER DISP Instruction Pseudo Enabling/Disabling The Dispatcher IXIT Instruction INTERRUPT SYSTEM SERVICING INFORMATION | 8-17<br>8-18<br>8-18<br>8-18<br>8-18<br>8-19<br>8-21<br>8-23<br>8-23<br>8-23 |

| SECTION IX - HP 32421A SERIES III POWER SUPPLIES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                              |

| Paragraph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Page                                                                         |

| INTRODUCTION  HP 30 310A OPERATION  Primary Power Circuit  Preregulator A9  Preregulator Control Al  Inverter A7  Inverter Driver A2  Full-Wave Rectifiers and Filters  20-Volt Regulators  Current Limiter A4  Voltage Protection and Control A5  HP 30310A SERVICING INFORMATION  Preventive Maintenance  HP 30310A Adjustments  PREREGULATOR ADJUSTMENT                                                                                                                                                                                                                                                                                                                                                                                             | 9-1<br>9-4<br>9-4<br>9-4<br>9-4<br>9-4<br>9-5<br>9-5<br>9-6<br>9-8           |

SECTION IX (CONT)

| Pa | aragraph                                                                                                                                                                                                                                                                                                                                                                   | Page                                                                                                                                 |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

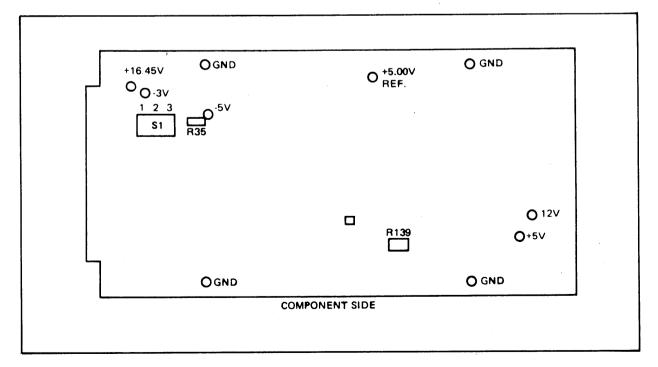

| н  | P 30311A SERVICING INFORMATION Preventive Maintenance     VOLATGE CHECKS     BATTERY TEST  HP 30311A Adjustments     BATTERY (FLOAT) VOLTAGE ADJUSTMENT     +12 VOLT ADJUSTMENT     +5.00 VOLT INTERNAL REFERENCE ADJUSTMENT  Replacement Procedures     POWER SUPPLY REPLACEMENT     BATTERY PACK REPLACEMENT     CONTROL PCA REPLACEMENT     MOTHERBOARD PCA REPLACEMENT | 9-10<br>9-10<br>9-11<br>9-11<br>9-14<br>9-15<br>9-16<br>9-16<br>9-16<br>9-19<br>9-20<br>9-20<br>9-20<br>9-21<br>9-22<br>9-22<br>9-24 |

| S  | ECTION X - HP 32435A SERIES III POWER SUPPLIES                                                                                                                                                                                                                                                                                                                             |                                                                                                                                      |

| P  | Paragraph                                                                                                                                                                                                                                                                                                                                                                  | Page                                                                                                                                 |

| P  | NTRODUCTION                                                                                                                                                                                                                                                                                                                                                                | 10-1<br>10-3                                                                                                                         |

| S  | SECTION XI - SYSTEM INSTALLATION                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                      |

| P  | Paragraph                                                                                                                                                                                                                                                                                                                                                                  | Page                                                                                                                                 |

|    | PART 1 HP 32421A SERIES III COMPUTER SYSTEM INSTALLATION                                                                                                                                                                                                                                                                                                                   |                                                                                                                                      |

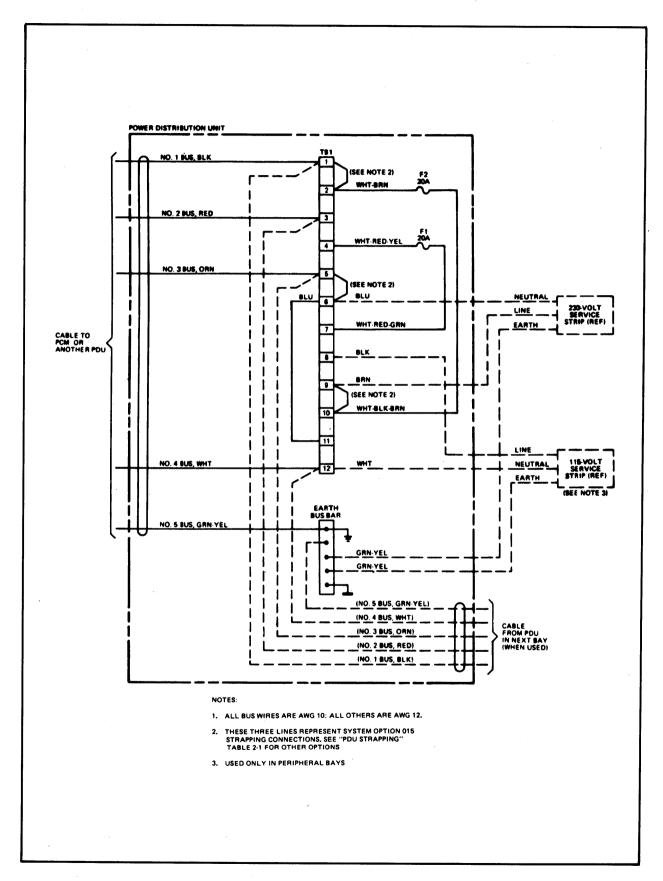

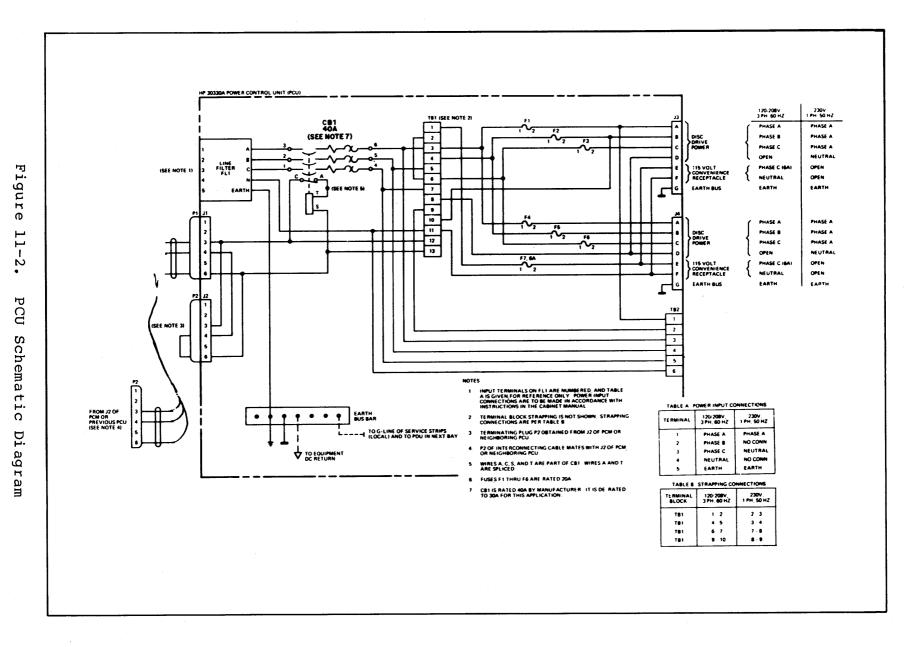

| I  | Power Distribution Unit Power Control Unit Power Control Module Bus Cable Connections Interrupt Poll, Data Poll, and MCU Clock Connections PERIPHERAL DEVICE INSTALLATION NEW INSTALLATION TURN-ON SYSTEM VOLTAGE ADJUSTMENTS                                                                                                                                              | 11-2<br>11-5<br>11-8<br>11-9<br>11-11                                                                                                |

| SECTION XI (CONT)                                       |                                                    |

|---------------------------------------------------------|----------------------------------------------------|

| Paragraph                                               | Page                                               |

| SYSTEM VERIFICATION                                     | 11-14                                              |

| PART 2 HP32435A SERIES III COMPUTER SYSTEM INSTALLATION |                                                    |

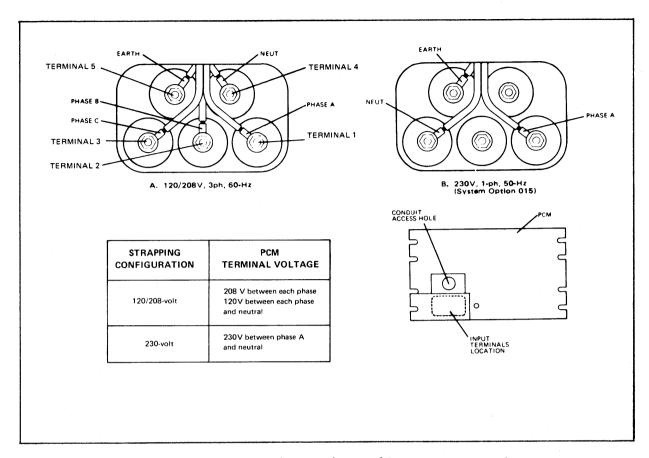

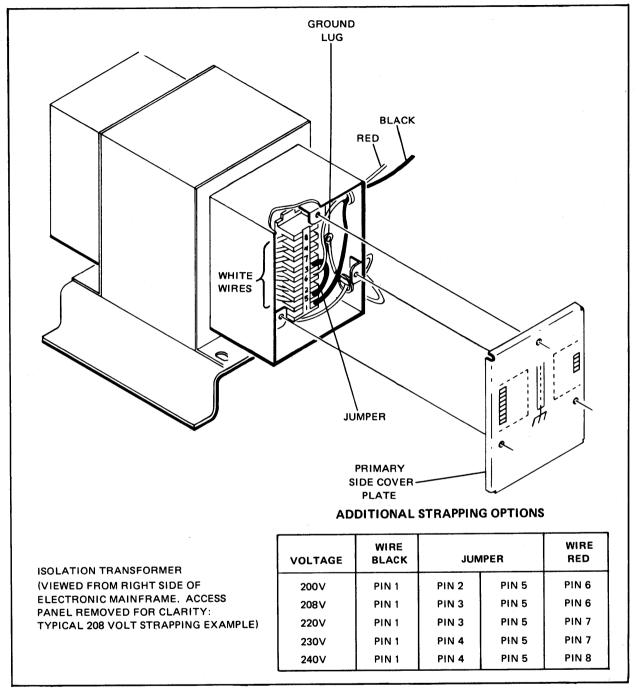

| Isolation Transformer Strapping                         | 11-15<br>11-18<br>11-18<br>11-18<br>11-19<br>11-19 |

## **ILLUSTRATIONS**

## **ILLUSTRATIONS** (continued)

| Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Page                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

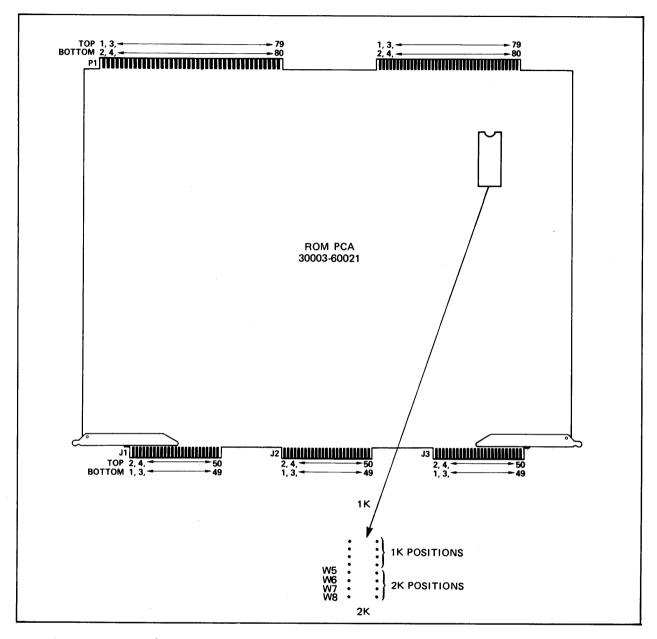

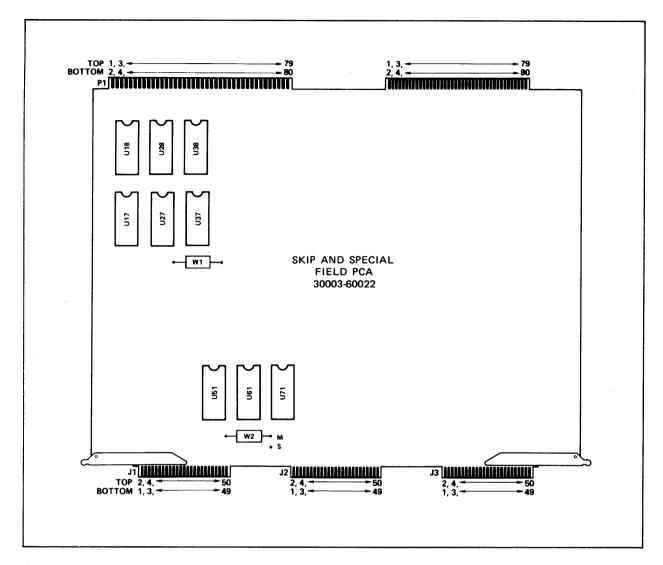

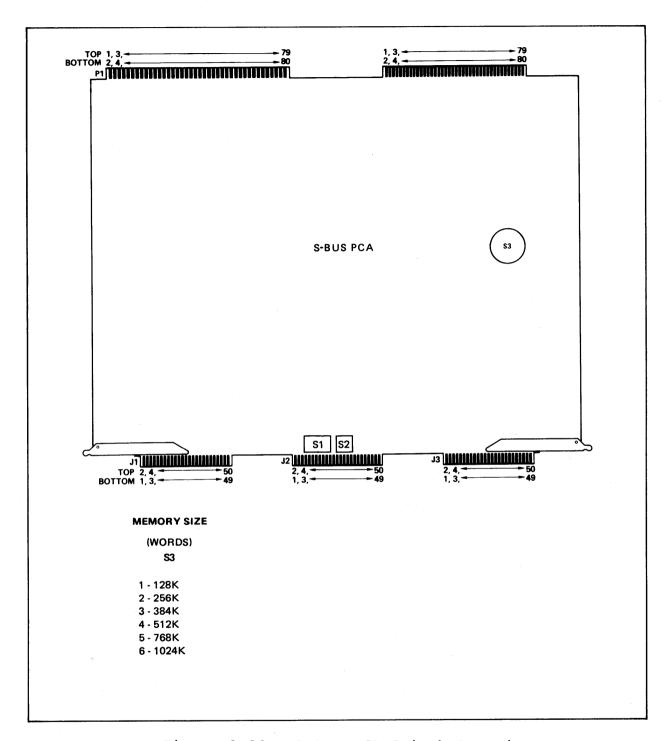

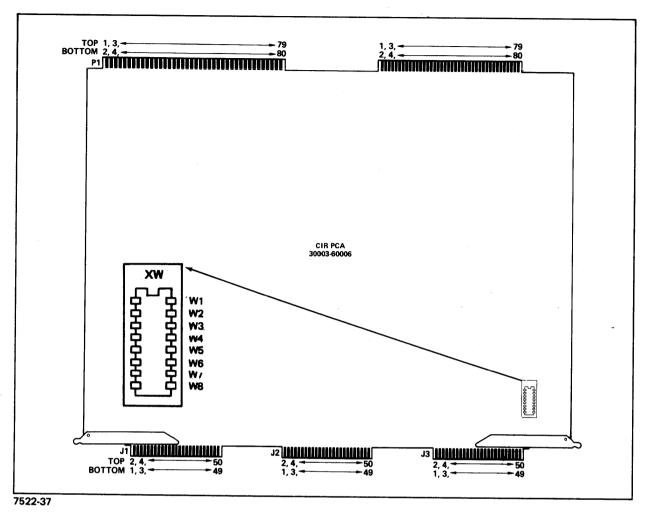

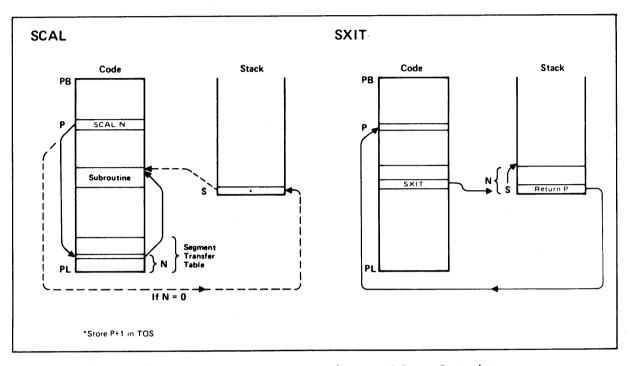

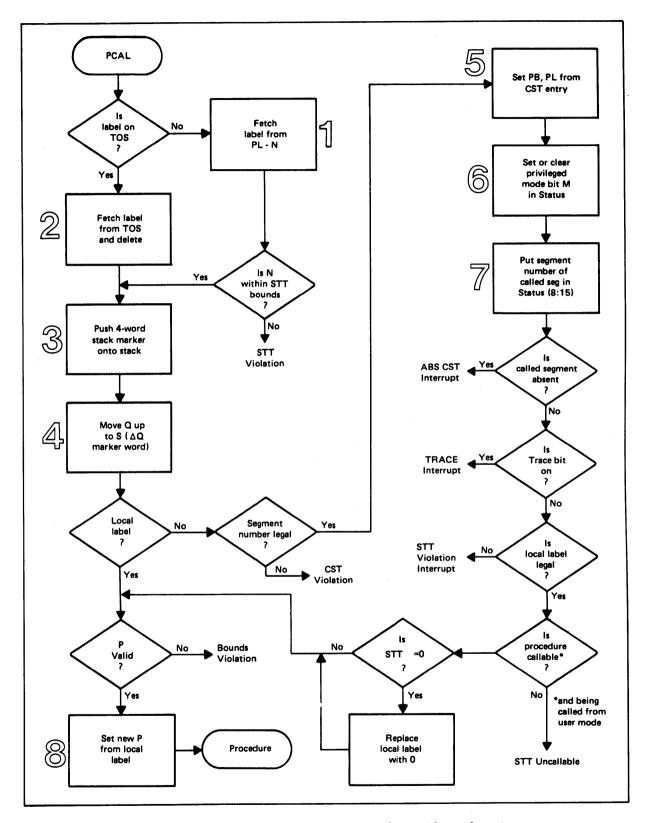

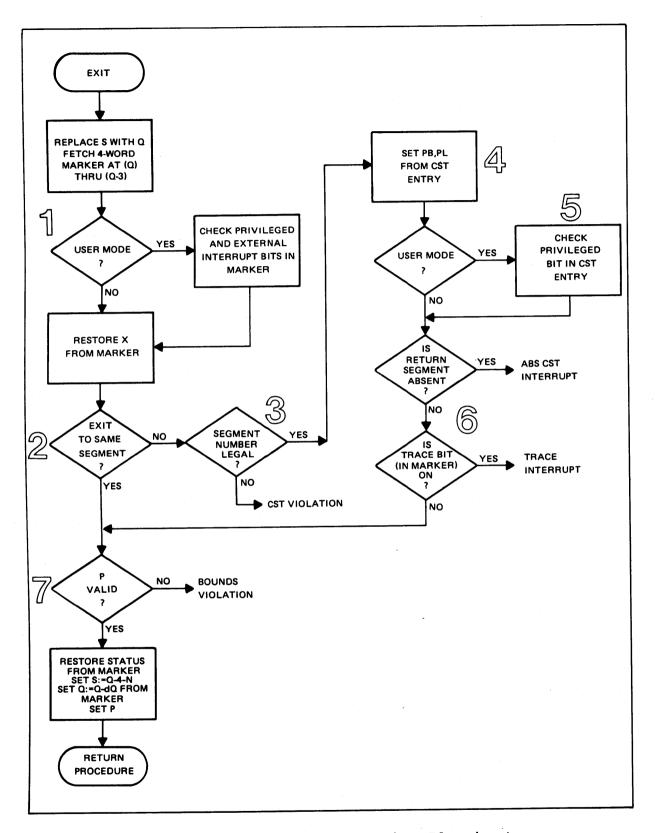

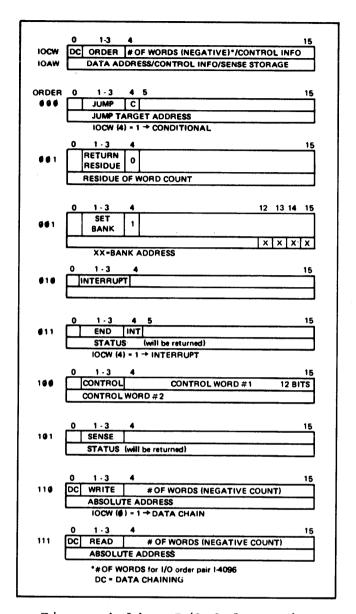

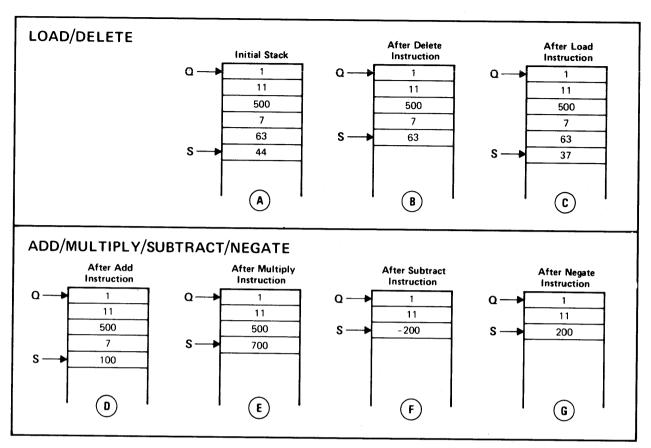

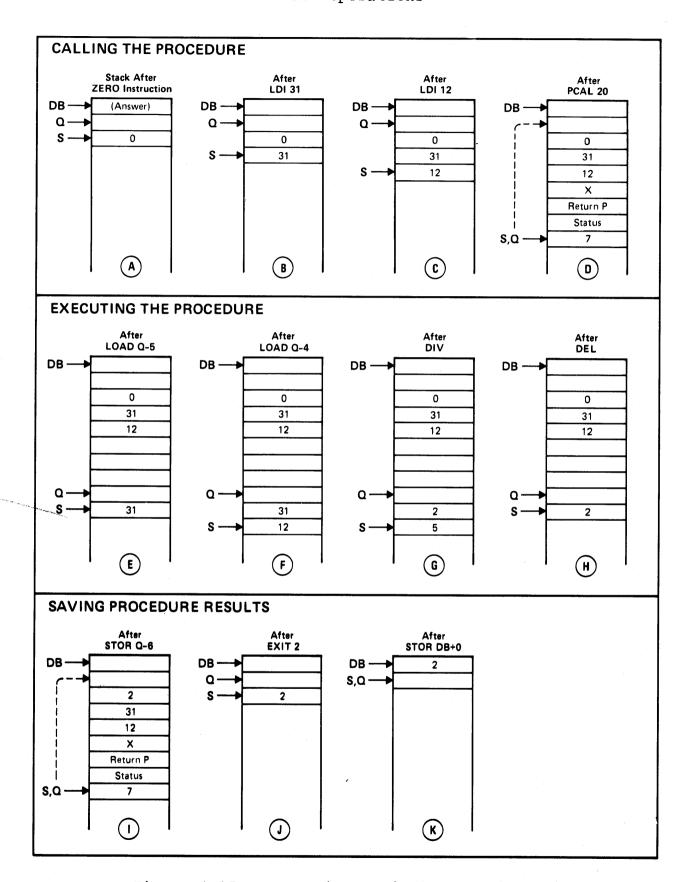

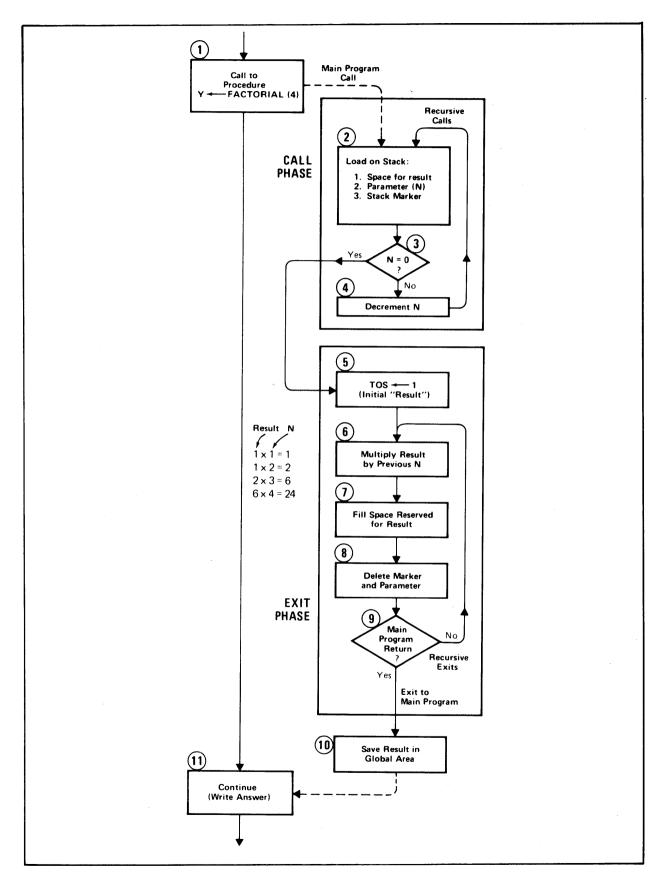

| IXIT Instruction Flowchart  I/O Order Pairs  Basic Arithmetic Stack Operations  Declaring and Calling A Procedure  Executing A Simple Procedure  Recursive Program  Recursive Procedure Flowchart  Stack Operations During Recursive Calls  Stack Operations During Recursive Exits  Microinstruction Summary  MCU Simplified Logic Diagram  Memory Module Simplified Logic Diagram  MCU PCA Jumper Locations  Memory Module Interface Diagram  SMA PCA Chip Arrangement | 4-34<br>4-36<br>4-38<br>4-40<br>4-42<br>4-44<br>4-45<br>4-47<br>4-49<br>5-4<br>6-2<br>6-10<br>6-13 |

| Error Correction Codes                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6-15                                                                                               |

| Decode of H01 through H05                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6-16                                                                                               |

| MEMLCGAN Table                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6-22                                                                                               |

| Typical MEMLOGAN Printout                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6-23<br>6-24                                                                                       |

| TIO Word Format CIO Word Format                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6-25                                                                                               |

| WIO Word Format                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6-26                                                                                               |

| RIO Word Format                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6-27                                                                                               |

| SMA PCA Switch Location                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6-28                                                                                               |

| MCL PCA Switch Locations                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6-29                                                                                               |

| Basic I/O Access Methods                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7-2                                                                                                |

| File System Basic Operation                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7-3                                                                                                |

| I/O System Fundamental Elements                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7-4                                                                                                |

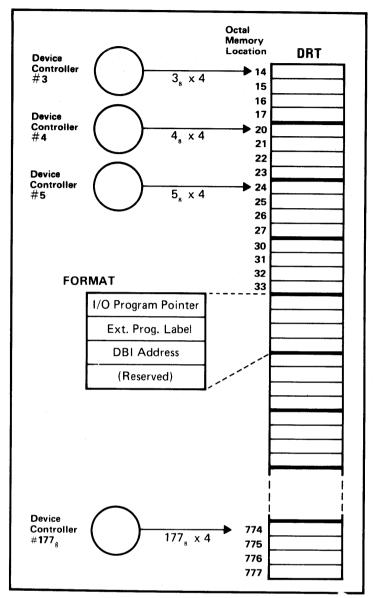

| Device Reference Table                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7-6                                                                                                |

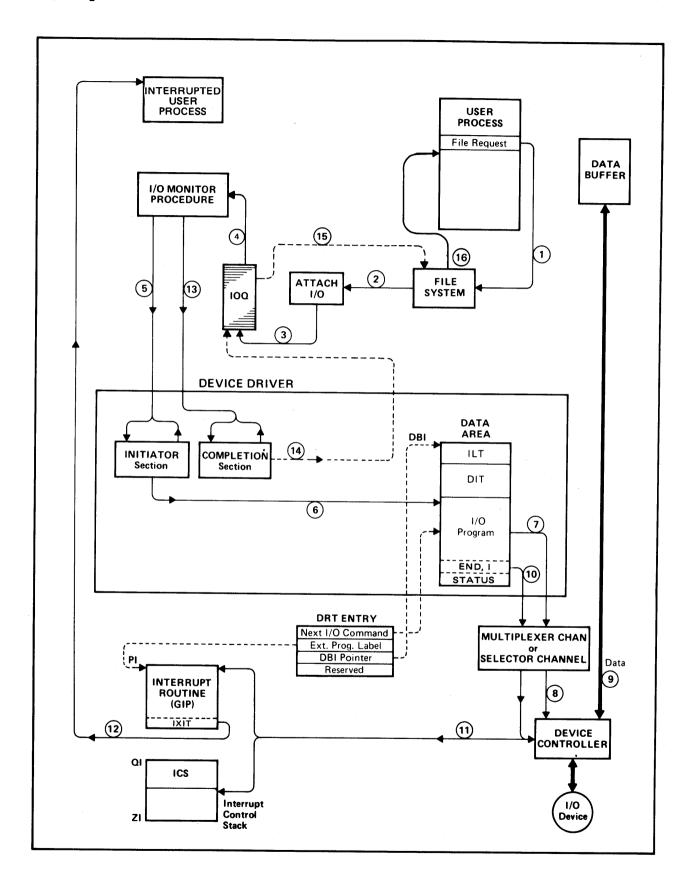

| I/O System Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7-8                                                                                                |

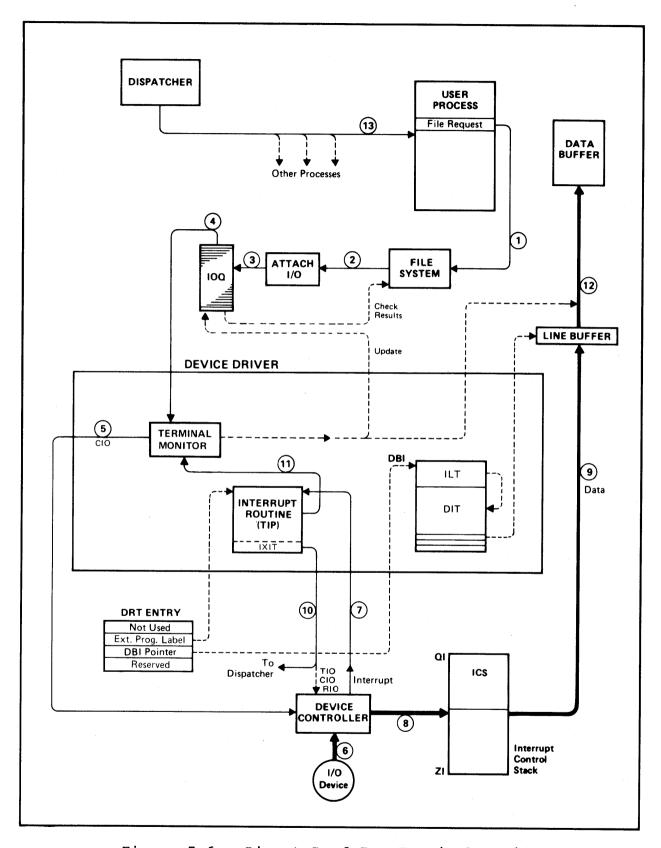

| Direct Read For Terminal Devices                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7-10                                                                                               |

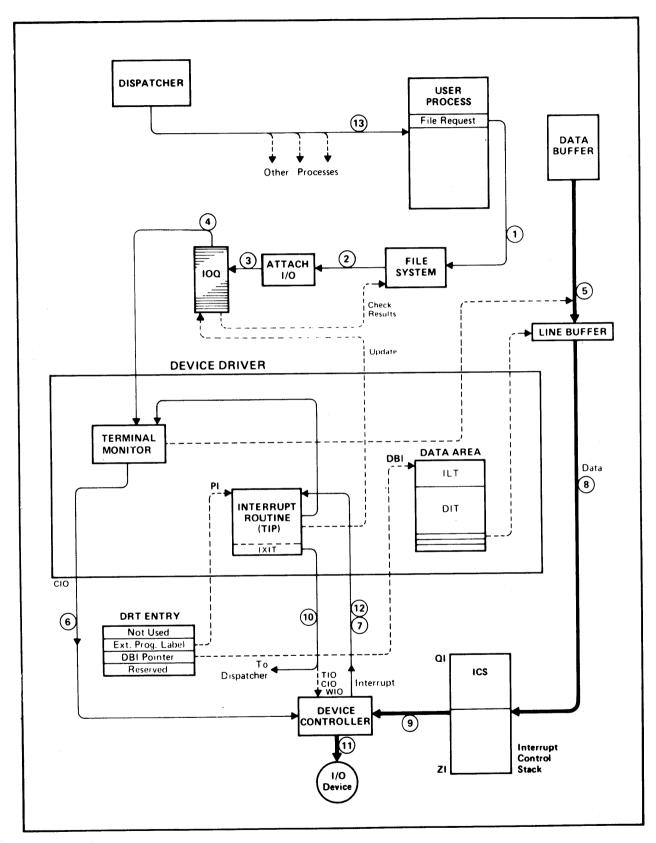

| Direct Write For Terminal Devices                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7-11<br>7-15                                                                                       |

| I/O Hardware Elements                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7-16                                                                                               |

| IOP Simplified Logic Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7-17                                                                                               |

| Interrupt Poll and Data Poll                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7-21                                                                                               |

| I/O Data Routes                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7-22                                                                                               |

| I/O Program Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7-26                                                                                               |

| Multiplexer and Selector Channel Comparisons                                                                                                                                                                                                                                                                                                                                                                                                                             | 7-27                                                                                               |

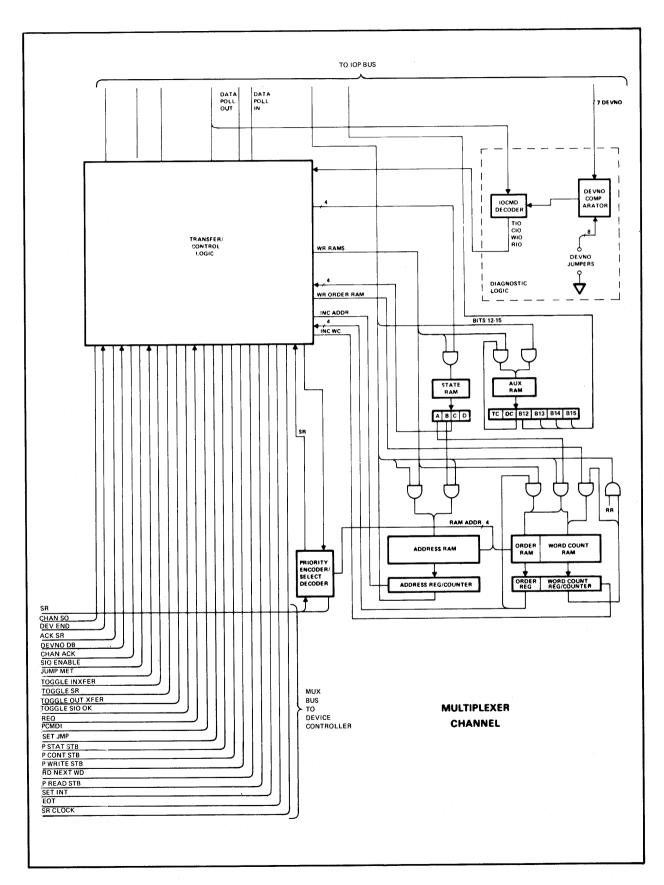

| Multiplexer Channel and Device Controller Simplified                                                                                                                                                                                                                                                                                                                                                                                                                     | <b></b>                                                                                            |

| Logic Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7-29                                                                                               |

| Multiplexer Channel Simplified Logic Diagram                                                                                                                                                                                                                                                                                                                                                                                                                             | 7-31                                                                                               |

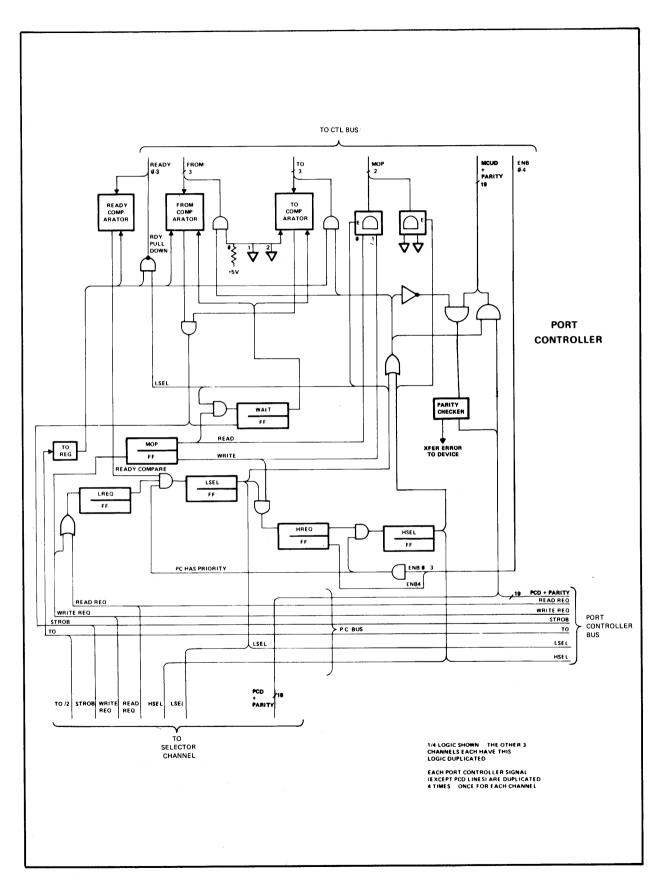

| Port Controller Simplified Logic Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7-37                                                                                               |

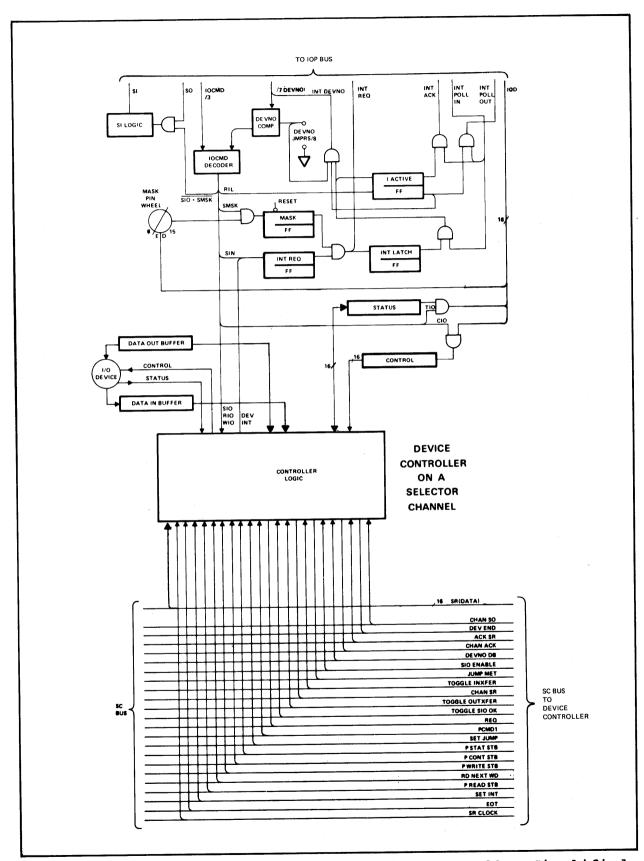

| Selector Channel and Device Controller Simplified                                                                                                                                                                                                                                                                                                                                                                                                                        | 7-39                                                                                               |

| Logic Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7-39                                                                                               |

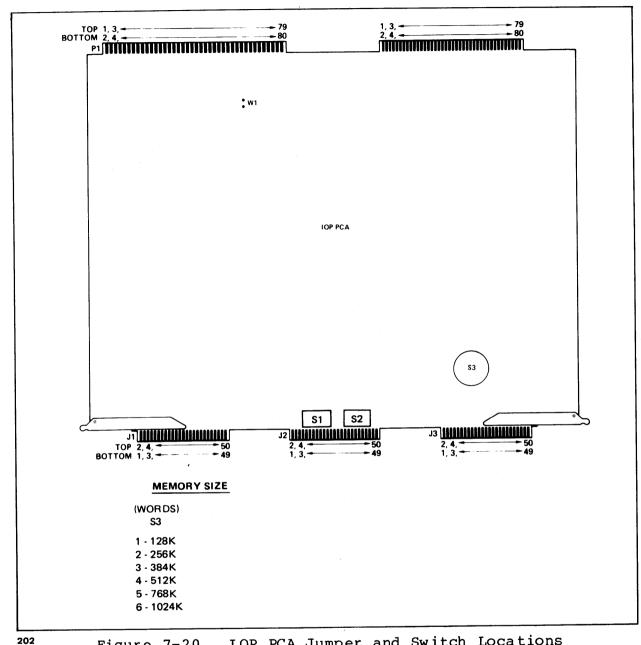

| IOP PCA Jumper and Switch Locations                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7-41                                                                                               |

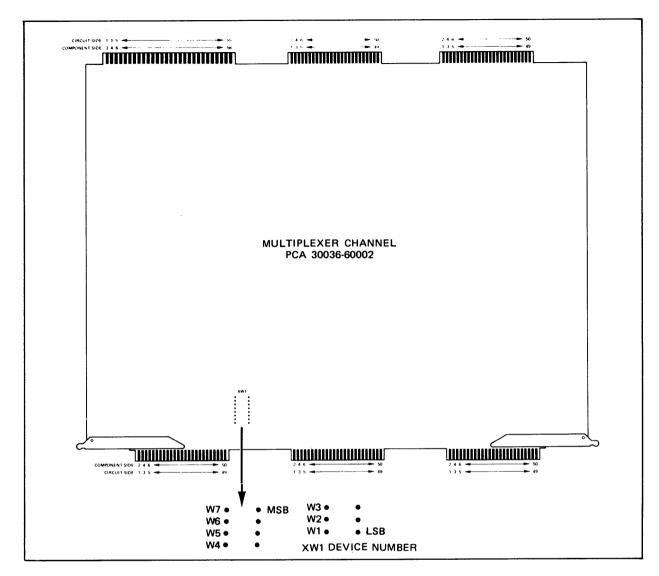

| Multiplexer Channel PCA Jumper Locations                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7-49                                                                                               |

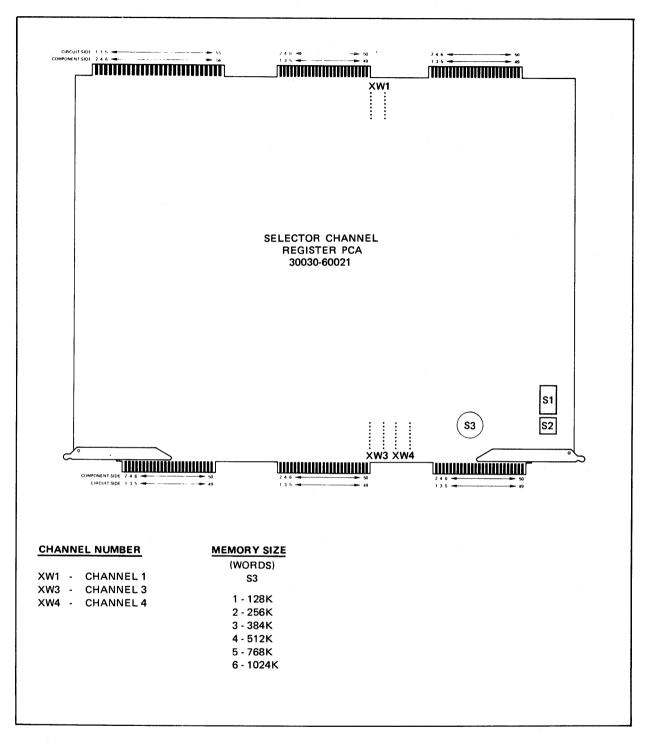

| Selector Channel Register PCA Jumper/Switch Locations                                                                                                                                                                                                                                                                                                                                                                                                                    | 7-50                                                                                               |

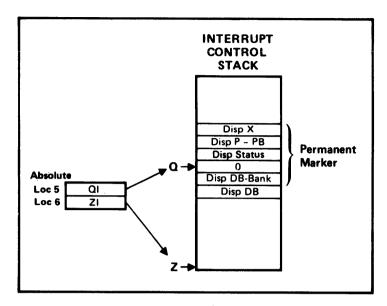

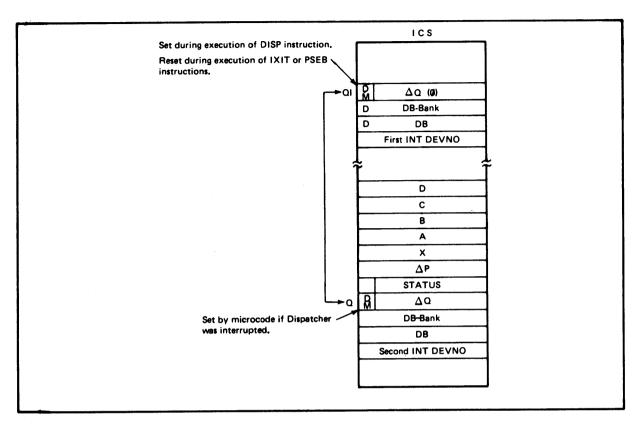

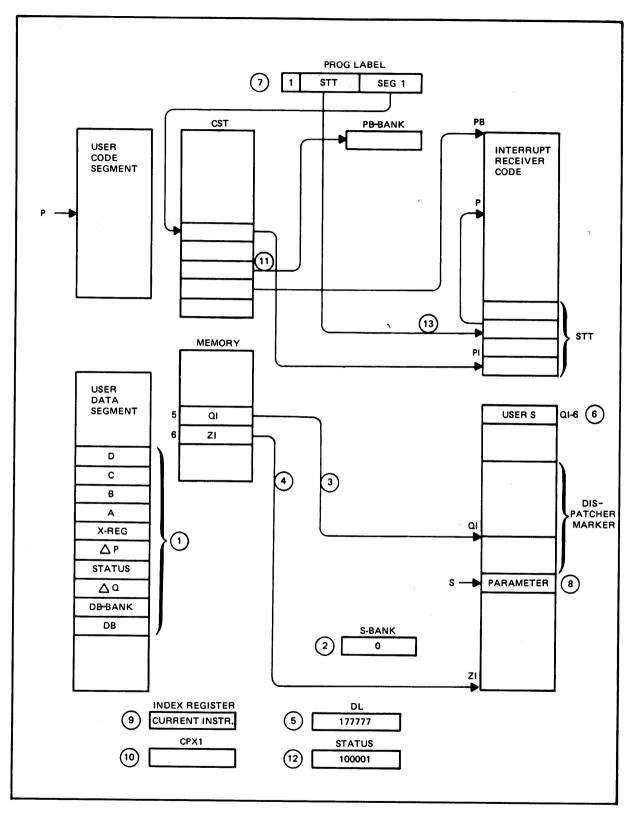

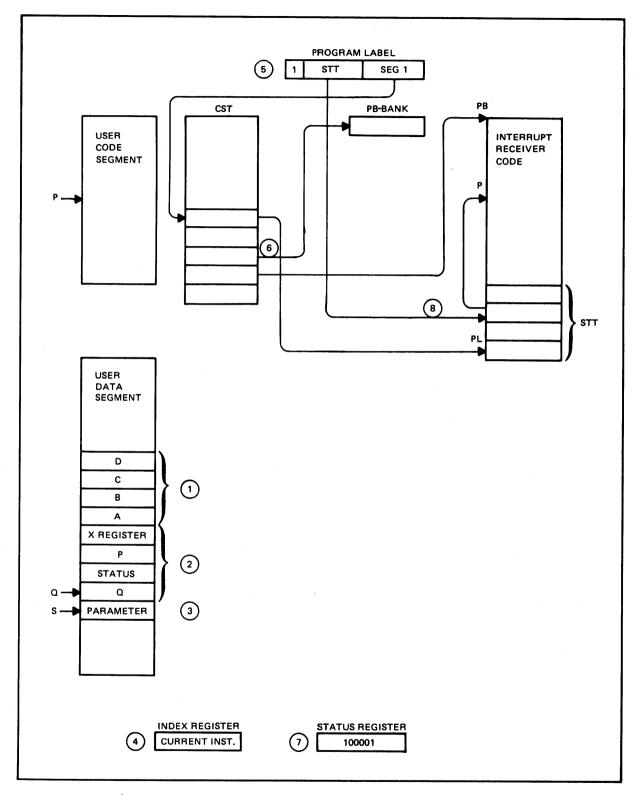

| ICS Dispatcher Marker                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8-4                                                                                                |

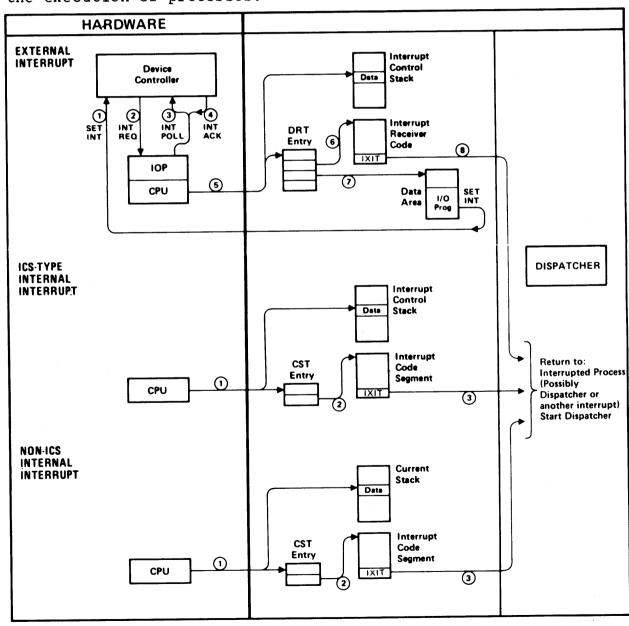

| Interrupt System Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8-5                                                                                                |

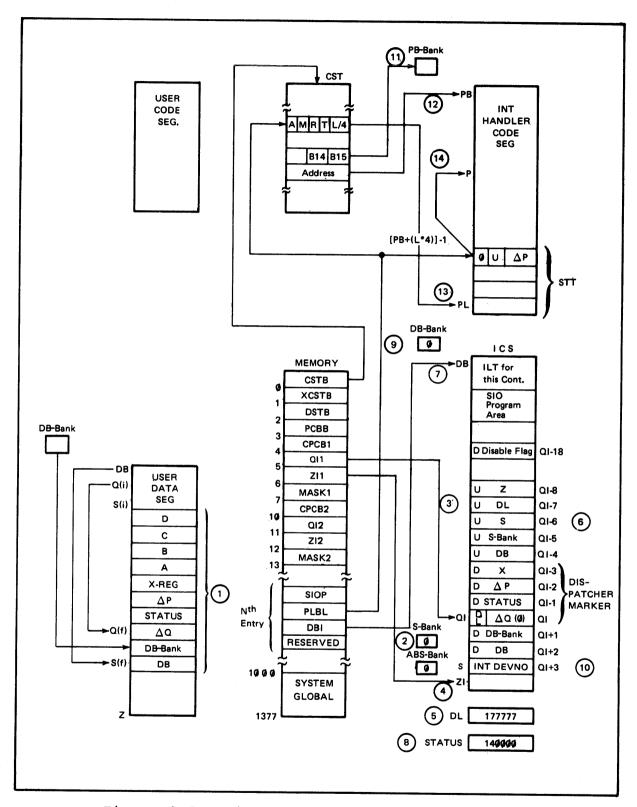

| First Level External Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8-10                                                                                               |

| Second Level Interrupt or Dispatcher Interrupted                                                                                                                                                                                                                                                                                                                                                                                                                         | 8-11                                                                                               |

## **ILLUSTRATIONS** (continued)

| Title                                                                                                                                                                                                                                                                                                                                       | Page                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

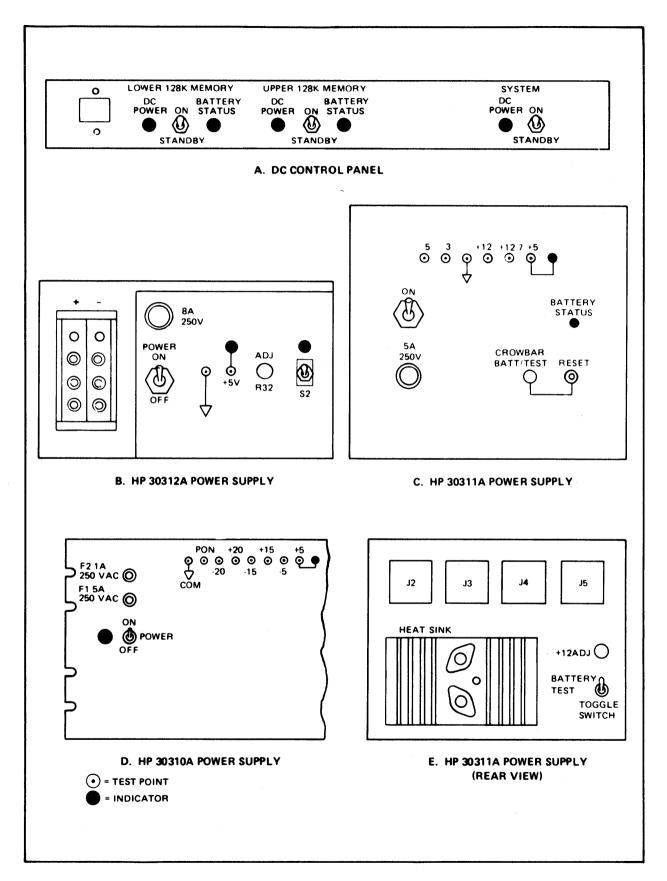

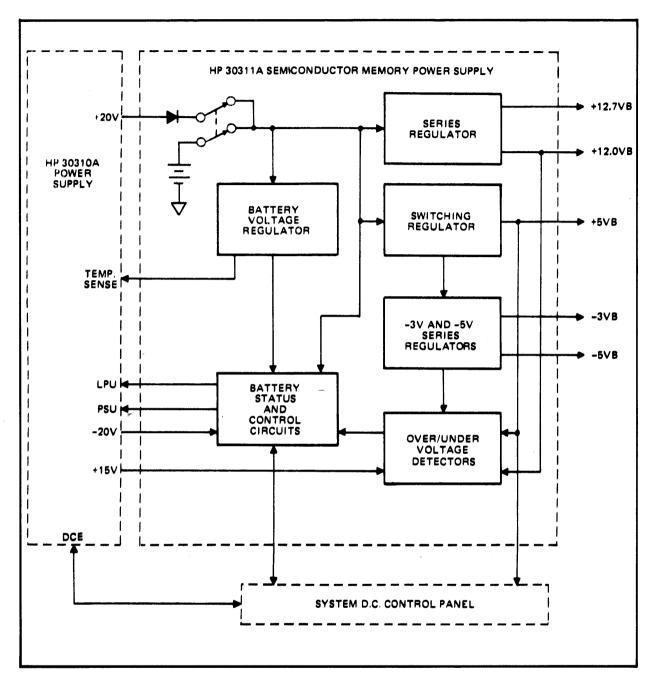

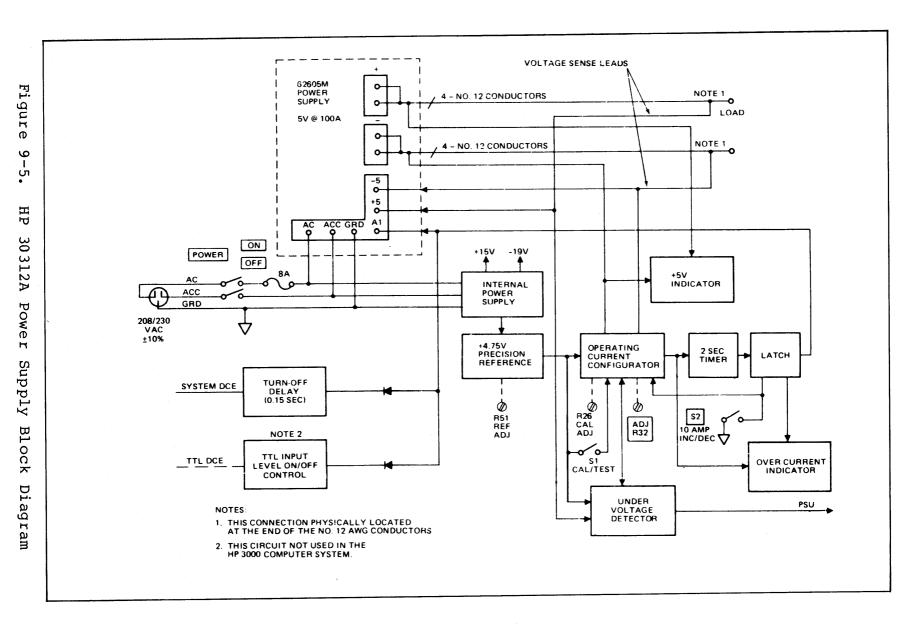

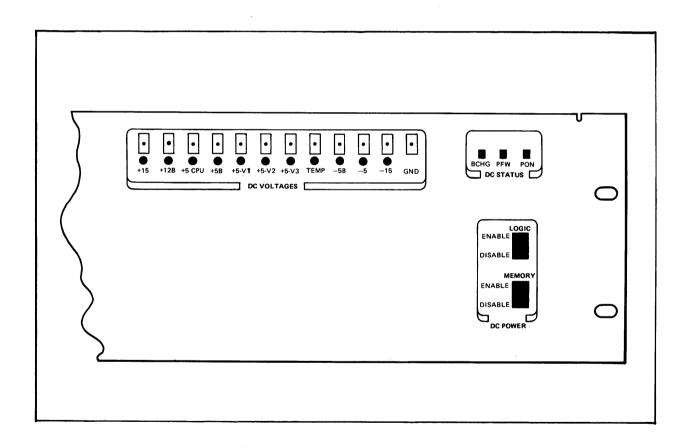

| ICS-Type Internal Interrupt Non-ICS Type Internal Interrupts Interrupt Handler Flowchart Power Controls and Indicators HP 30 310A Power Supply Block Diagram HP 30 311A Power Supply Block Diagram Control Board Adjustment Locations HP 30 312A Power Supply Block Diagram Power Supply Control and Display Assembly PDU Schematic Diagram | 8-20<br>8-22<br>8-25<br>9-2<br>9-3<br>9-13<br>9-17<br>9-23<br>10-2<br>11-4<br>11-6<br>11-7 |

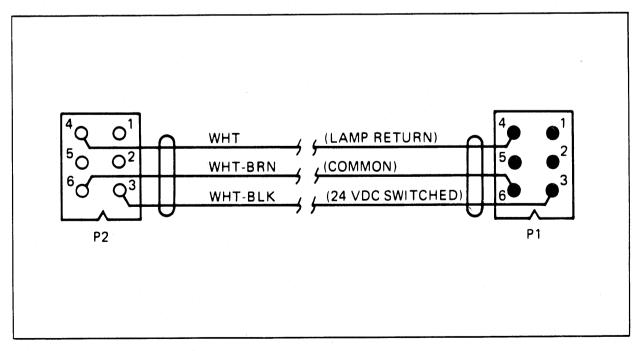

| PCU to PCU/PCM Interconnecting Cable                                                                                                                                                                                                                                                                                                        | 11-10                                                                                      |

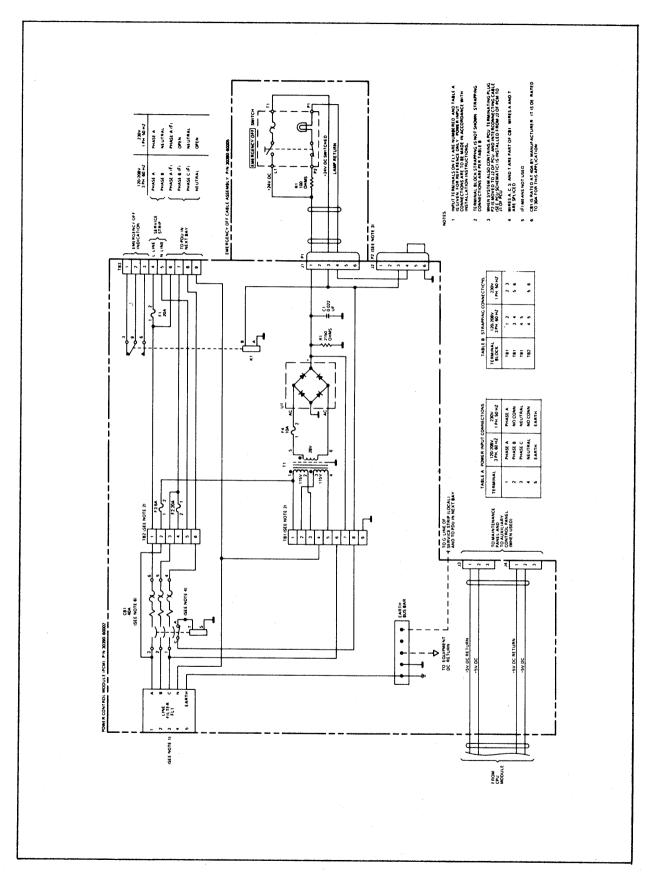

| PCM Schematic Diagram                                                                                                                                                                                                                                                                                                                       | TT_TO                                                                                      |

| Isolation Transformer Strapping Options                                                                                                                                                                                                                                                                                                     | TT-T/                                                                                      |

### **TABLES**

| Fitle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Page                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

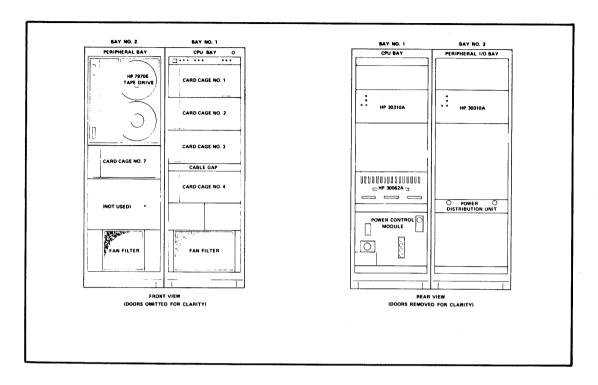

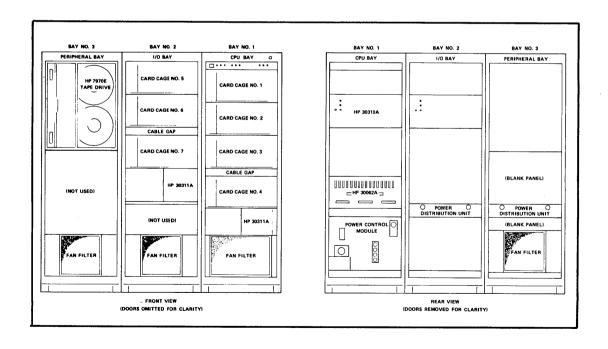

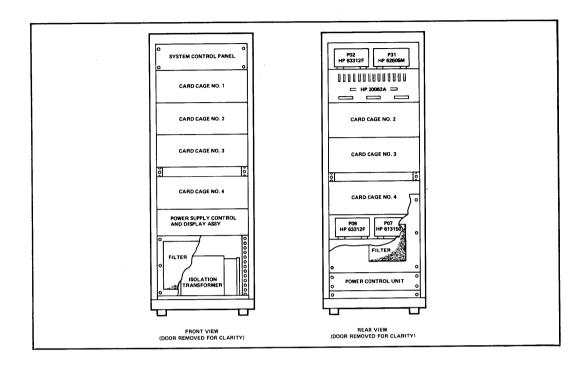

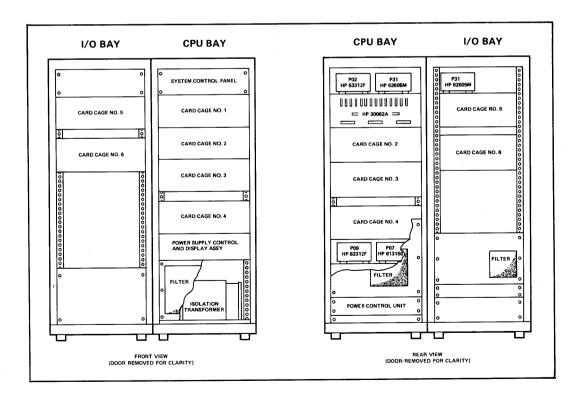

| HP 32421A Series III 2-Bay Model PCA Slot Assignments HP 32421A Series III 3-Bay Model PCA Slot Assignments HP 32435A Series III PCA Slot Assignments Central Processor Module Features Main Memory Configurations Machine Registers Reserved Low Main Memory Locations Condition Codes Bounds Checks Summary TOS Namer Relationships Memory Interleaving Switch Configurations System Control Panel Switches and Lamps MPI PCA J3 Pin Connections Stack Element Locations S-Bus Field Code Definitions S-Bus Field Code Definitions Shift Field Code Definitions Shift Field Code Definitions Store Field Code Definitions Store Field Code Definitions MCU Option Field Code Definitions Skip Field Code Definitions Interrupt Types HP 30 310A Dc Output Voltages HP 30 311A Power Supply Controls and Indicators DC Output Voltages Float Voltage Versus Temperature DC Power Supply Spcifications DC STATUS/POWER Indicators and Switches PDU Strap Connections at TB1 | Page 1-8 1-9 1-10 2-5 2-6 2-12 2-16 2-33 2-46 2-56 2-64 3-7 5-2 5-6 5-9 5-24 5-25 5-34 5-29 9-14 9-15 8-2 9-14 11-3 |

| PDU Strap Connections at TB1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11-3<br>11-5                                                                                                        |

| PDU Ac Service Strip Wiring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 11-5<br>11-14<br>11-16                                                                                              |

| System DC Voltage Tolerances                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                     |

### **INTRODUCTION**

I