# PROCESS COMPUTER

GENERAL 🍪 ELECTRIC

UTILITY AND PROCESS AUTOMATION

PRODUCTS DEPARTMENT

PHOENIX, ARIZONA

GE-NPGCD CAROLINA I (AZNA)

REQN: 282-L3285

The

# Process Computer System

**VOLUME II**

PROCESS I/O

This instruction book is provided as a basic source of technical information on this system. If problems arise in installation, operation, or maintenance that are not covered in these instructions, the matter should be referred to General Electric Company, Process Computer Products Department, Phoenix, Arizona, U.S.A. Attn: Technical Publications.

General Electric reserves the right to make changes in the equipment or software, and its characteristics or functions, at any time without notice.

# 1400A/B PROCESS DIGITAL I/O SUBSYSTEM

## **TABLE OF CONTENTS**

| INTRODUCTION INT                                                                                                                                                                                                                                                                                              | DIGITAL INPUTS DIN                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| MODEL NUMBER/OPTIONS                                                                                                                                                                                                                                                                                          | INPUT SELECTION                     |

| Process Digital Controller                                                                                                                                                                                                                                                                                    | INPUT TERMINATIONS                  |

| Digital I/O Cabinets (Typical):                                                                                                                                                                                                                                                                               | CSU DATA FLOW                       |

| Termination Boards (Typical):                                                                                                                                                                                                                                                                                 | DIGITAL OUTPUTS DOUT                |

| Jumper Pin                                                                                                                                                                                                                                                                                                    | OUTPUT SEQUENCING AND CONTROL       |

| REFERENCE DOCUMENTS                                                                                                                                                                                                                                                                                           | OUTPUT SELECTION                    |

| INSTRUCTIONS INS                                                                                                                                                                                                                                                                                              | OUTPUT TERMINATIONS                 |

| ABT - Abort PDC                                                                                                                                                                                                                                                                                               | Decimal Displays                    |

| ABT - Abort Pulse Source Initiator                                                                                                                                                                                                                                                                            | Analog Outputs                      |

| ACT - Activate                                                                                                                                                                                                                                                                                                | OUTPUT FAULT CHECKING               |

| IN - Input                                                                                                                                                                                                                                                                                                    |                                     |

| JNE - Jump No Error                                                                                                                                                                                                                                                                                           | PULSE SOURCE INITIATOR (OPTION) PSI |

| ord sump no Error                                                                                                                                                                                                                                                                                             |                                     |

| JNR - Jump Not Ready                                                                                                                                                                                                                                                                                          | SEQUENCING AND CONTROL              |

|                                                                                                                                                                                                                                                                                                               | ·                                   |

| JNR - Jump Not Ready                                                                                                                                                                                                                                                                                          | SEQUENCING AND CONTROL              |

| JNR - Jump Not Ready OUT - Output (Normal)                                                                                                                                                                                                                                                                    | SEQUENCING AND CONTROL  TEST MODE   |

| JNR - Jump Not Ready OUT - Output (Normal) OUT - Data Switch Open Detector Check (Test Mode) OUT - Data Switch Short Detector Check (Test Mode) OUT - More Than One Group Driver On Detector                                                                                                                  | SEQUENCING AND CONTROL  TEST MODE   |

| JNR - Jump Not Ready OUT - Output (Normal) OUT - Data Switch Open Detector Check (Test Mode) OUT - Data Switch Short Detector Check (Test Mode) OUT - More Than One Group Driver On Detector Check (Test Mode)                                                                                                | SEQUENCING AND CONTROL  TEST MODE   |

| JNR - Jump Not Ready OUT - Output (Normal) OUT - Data Switch Open Detector Check (Test Mode) OUT - Data Switch Short Detector Check (Test Mode) OUT - More Than One Group Driver On Detector                                                                                                                  | SEQUENCING AND CONTROL  TEST MODE   |

| JNR - Jump Not Ready OUT - Output (Normal) OUT - Data Switch Open Detector Check (Test Mode) OUT - Data Switch Short Detector Check (Test Mode) OUT - More Than One Group Driver On Detector Check (Test Mode) OUT - No Group Driver On Detector Check                                                        | SEQUENCING AND CONTROL  TEST MODE   |

| JNR - Jump Not Ready OUT - Output (Normal) OUT - Data Switch Open Detector Check (Test Mode) OUT - Data Switch Short Detector Check (Test Mode) OUT - More Than One Group Driver On Detector Check (Test Mode) OUT - No Group Driver On Detector Check (Test Mode)                                            | SEQUENCING AND CONTROL  TEST MODE   |

| JNR - Jump Not Ready OUT - Output (Normal) OUT - Data Switch Open Detector Check (Test Mode) OUT - Data Switch Short Detector Check (Test Mode) OUT - More Than One Group Driver On Detector Check (Test Mode) OUT - No Group Driver On Detector Check (Test Mode) OUT - Group Driver Fault Check (Test Mode) | SEQUENCING AND CONTROL  TEST MODE   |

## INTRODUCTION

The Process Digital Input/Output Subsystem provides a means of monitoring and controlling process functions and operator consoles. The input function reads the status of logic variables (yes/no, true/false, set/reset, open/closed, on/off) from various process system devices such as switches, valves, relays, and motors. The output function provides program controlled contact closures, and optional analog signals and stepping motor pulses for controlling the process.

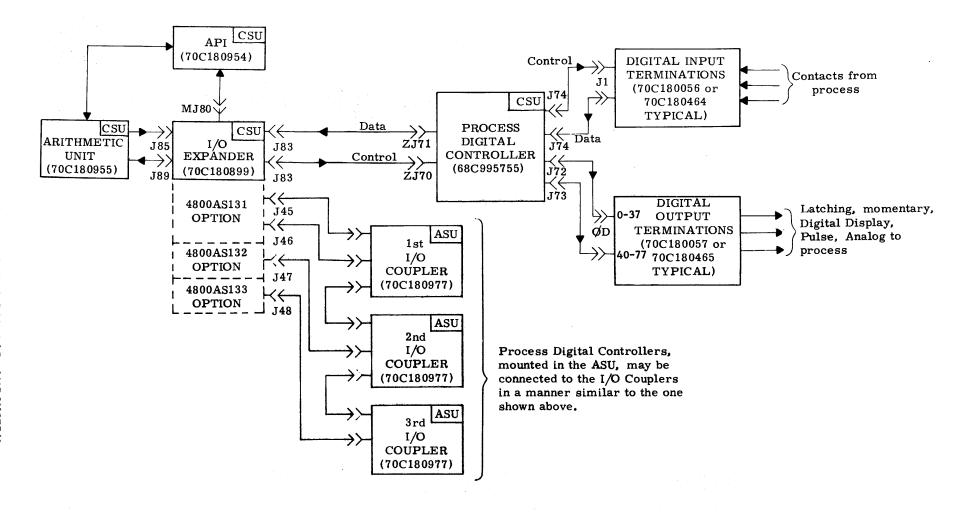

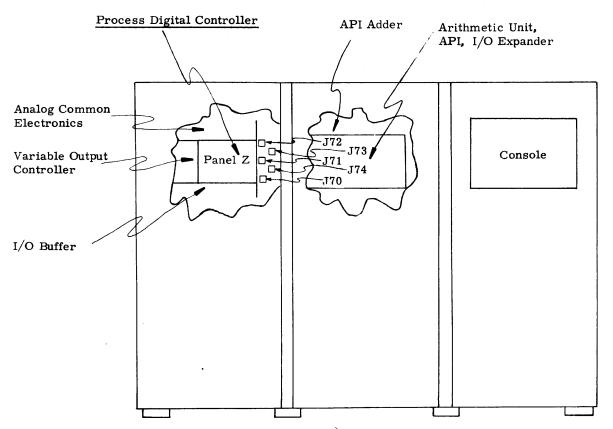

The Process Digital I/O Subsystem described in this publication may be used in a GE-PAC¹ 4010 and future Process Computer Systems. Fig. INT.1 illustrates the basic signal flow and functional modules associated with the digital inputs/outputs in a GE-PAC 4010 System. The signal flow in future systems will be similar and illustrated in the System Logic drawing supplied with the system. The location of the functional modules within the GE-PAC 4010 Central Systems Unit is shown in Fig. INT.2. The location of these modules in the Auxiliary Systems Unit (ASU) is shown on the System Configuration diagram supplied with each system.

Input/output connections with the process and operator consoles are made through termination cabinets. The termination cabinets contain termination points, signal conditioning, and selection gates for digital inputs, and termination points and output relays for digital outputs. Digital inputs may be either 28 volts or 125 volts and may optionally be connected to change detector circuits. Digital outputs may be latched, momentary, decimal display, or applied through analog generators. For each Process Digital Controller, up to sixty-four groups, each having 24 contacts per group of digital inputs, may be connected to the system. For each Process Digital Controller, up to sixty-four groups, each having 16 contacts per group of digital outputs, may be connected to the system.

Program control of the digital input/output subsystem is via the execution of GEN 2 commands or TIM/TOM. Each OUT command (26.5  $\mu$ sec) controls the status of one digital output group of 16 contacts as specified by a data/control word in the A Register. Upon satisfactory (no fault) completion of each output operation, an automatic program interrupt is generated. Each IN command (26.5  $\mu$ sec) places the status ("1" for closed, "0" for open) of 24 contacts in the A Register corresponding to the input group specified by the K1, 0 bits of the command.

To protect the process and the subsystem hardware, the digital I/O subsystem contains error checking circuits which monitor the digital output portion of the hardware. Detection of an error disables output relay operation and delays the ready interrupt until the error condition has been cleared.

The digital I/O subsystem contains extensive test and maintenance hardware permitting off-line testing to isolate failures using a diagnostic program.

#### 1 Registered Trademark of General Electric Company

## MODEL NUMBER/OPTIONS

The following table lists the model numbers and options associated with the digital I/O subsystem. All model numbers listed may not be available on all process computer systems. Options contained in a particular system are shown on the System Configuration Diagram, Special System Logic drawing, etc. supplied with each system.

#### **Process Digital Controller**

4DP4846\*

A(or B\*\*)S01 -

- Special purpose option containing the S02, S03, and S04 options described below. That is, this option defines a system having 16 digital input groups, 16 digital output groups and the basic common hardware. Other options (adders) may of course be added to expand the system.

- S02 Basic hardware for digital inputs and outputs.

- S03 Adder for input groups 1 16 (Adds the control PWBs and cables for digital input groups 1 thru 16 to the basic hardware specified by the S02 option.)

- S04 Adder for output groups 1 16 (Adds the control PWBs and cables for digital output groups 1 thru 16 to the basic hardware specified by the S02 option.)

- S05 Adder for input groups 17 64 (Adds control PWBs and intra-cabinet cables to expand the digital inputs of a system containing an S01 or S04 option from 16 to 64 groups.)

- S06 Adder for output groups 17 -32

(Adds control PWBs and intra-cabinet cables to expand the digital outputs of a system containing an S01 or S04 option from 16 to 32 groups.)

- S07 Adder for output groups 33 64

(Adds control PWBs and intra-cabinet cables to expand the digital outputs of a system containing an S06 option from 32 to 64 groups.)

- S08 Pulse Source Initiator Adder (Adds Pulse Source Initiator printed wiring board, SPIA5.)

<sup>\*</sup> Instead of 4846, the model number for future systems is 4430. The options are the same as those shown above except that intra-cabinet cables are not included with the 4430 model number.

<sup>\*\*</sup> A is for PDC in CSU cabinet. B is for PDC in ASU cabinet.

Fig. INT. 1 Digital Input/Output Block Diagram

Fig. INT. 2 4010 Central Systems Unit

## Digital I/O Cabinets (Typical):

- 4DP4847AS01 Basic Digital Input Cabinet

- 02 Digital Input Distributor (wiring harness)

- 03 Digital Output Distributor (wiring harness)

- 04 28V (4290A) and 12V (See Theory 4847A-04) Dig. In. Power Supply

- 05 125V Dig. In. Power Supply (4491A)

- 06 28V Dig. (4290A) Out Power Supply

- 07 42V (4396A) Analog Gen. Power Supply

- 08 Dig. In. 28V, 192 Pt. Term.

- 09 Dig. In. 125V, 192 Pt. Term.

- 10 Dig. Out 64 Pt. Termination

- 11 Pulse Source Initiator Interposer Relay Assembly

#### Termination Boards (Typical):

#### Input

PX2000ICFA1 - 28V, 48 pt., 1 Msec, Filter PX2000ICFB1 - 28V, 48 pt., 22 Msec, Filter

- PX2000ICFC5 28V, 48 pt., Thumbwheel Sw. Read-in

- PX2000ICFC2 125V, 48 pt., 15 usec, Filter

- PX2000ICFB2 125V, 48 pt., 22 Msec, Filter

- PX2000ICCA4 125V, 24 pt., Change Detection

- PX2000ICCA2 28V, 24 pt., Change Detection

#### Output

- PX2000IHBA1 100V Latching, 16 pt., 1.25A, 150 VDC

- PX2000IHBA2 100V Latching, 16 pt., 1A 120VRMS

- PX2000IHBB1 5VA Latching, 16 pt., 1A, 50 VDC

- PX2000IHBC1 250VA Latching, 8 pt., 1A, 50VDC

- PX2000IHBC2 250VA Latching, 8 pt., 2A, 120VRMS

- PX2000IHBD1 20VA Latching, 8 pt.,.2A. 100VDC

- PX2000IHSA 1 100VA Momentary, 16 pt., 1.25A, 150VDC

PX2000IHSA 2 - 100VA Momentary, 16 pt., 1A, 120VRMS

PX2000IHSB1 - 5VA Momentary, 16 pt., .1A, 50VDC

PX2000IHSC 1 - 250VA Momentary, 8 pt., 1A, 200VRMS

PX2000IHSO 2 - 250 VA Momentary, 8 pt., 2A. 120 VRMS

PX2000IHSD1 - 20VA Momentary, 8 pt., .2A, 120VRMS

PX2000IDDB1 - Dig. Display Drive (4 Digit, Series 10)

PX2000IDDA1 - Dig. Display Drive (4 Digit, Series 120/220)

PX2000IDAA1 - 8 Bit Analog Generator (2 per PWB)

PX2000IDAB1 - 8 Bit Analog Generator(Biased 20% offset))

#### Jumper Pin

The following options are implemented by changing, adding, or removing printed wiring board jumper pins in the Process Digital Controller.

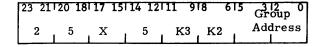

K3, K2 Process Digital Controller Address: The K3, K2 address is determined by the position of jumper pins on the SIOA5 board in A03-FK as shown on sheet 4 of the PDC logic, 68C995755.

Output Relay Energizing Time: The normal output delay time  $(A_7 = 0)$  is 3 Msec. if a jumper pin on the ISSB5 board in A03-FK is in the top black jack or is 8 Msec. if a jumper pin is in the bottom black jack. The long delay  $(A_7 = 1)$  is 8 - 40 Msec. (trimpot adjustable) if a jumper pin is in the top green jack or is 40 to 200 Msec. (trimpot adjustable) if a jumper pin is in the bottom green jack. Sheet 16 of the PDC logic, 68C995755, illustrates these connections.

The 3 (3.3  $\pm$  10%) Msec. energizing time is normally used for 100VA latching relays; the 8 (9.0  $\pm$  10%) Msec. time is normally used for 250VA latching relays or short momentary 100VA relays. The long operate time is normally used for momentary relays.

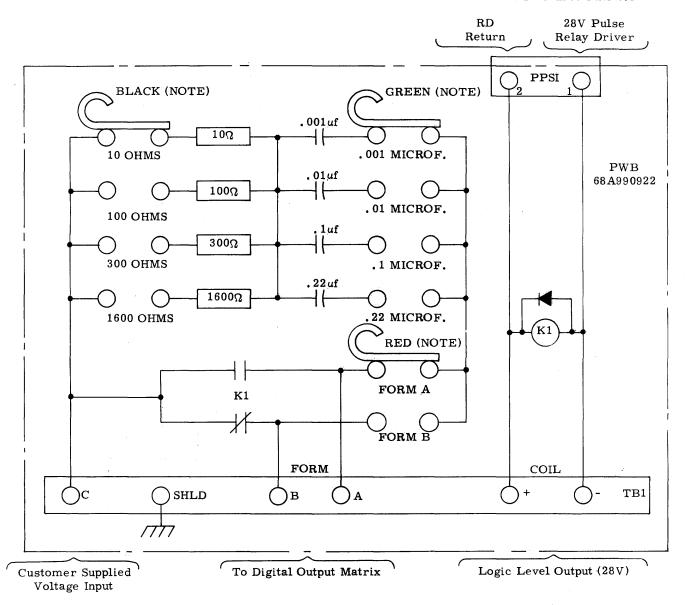

Pulse Source Initiator Operation: Sheet 34 of the PDC logic illustrates these jumper pin connections which are located on the SPIA5 board in A12-AE.

- a. Input Frequency: A jumper pin in the top red jack selects the input signal from the Arithmetic Unit or in the bottom red jack selects an external signal. Further jumper pin selection of the Arithmetic Unit input is provided for either the line frequency input or the adjustable pulse generator (optional) input on the ILDC5 board in B29-FK as shown on sheet 96.2 of the 4022 logic, 70C180955.

- b. Output Frequency: A jumper pin (SPIA5 board) in the top green jack selects the output frequency at one-half the input frequency or in the bottom green jack selects the output frequency equal to the input frequency of the PSI.

- c. Deadman Timer: A jumper pin in a yellow jack selects the duration of the deadman timer at 1 (top), 2 (middle) or 3 (bottom) seconds.

The deadman timer will abort the pulse source initiator if it is left enabled longer than the time interval selected by the jumper pin.

d. Output Signal Type: A jumper pin in the top black jack selects a pulse output signal equal to the output frequency selected or in the bottom black jack selects an output that is enabled for the duration that the PSI is enabled.

Optional Pulse Source Interposer: Sheet 14 of the Digital Outputs logic illustrates these jumper pin connections. These jumper pins determine R/C suppression and contact form. The positions of the jumper pins are specified by the Requisition Engineer.

#### **REFERENCE DOCUMENTS**

#### Logic

68C995755 - Process Digital Controller

70C180056 and 70C180464 - Digital Input Logic (Typical)

70C180057 and 70C180465 - Digital Output Logic (Typical)

#### Interface Module Logic

70C180955 - 4022D Arithmetic Unit

70C180899 - 4078B I/O Expander

70C180954 - 4032D Automatic Program Interrupt

70C180977 - ASU I/O Coupler

#### Maintenance

Computer Maintenance Manual

## **INSTRUCTIONS**

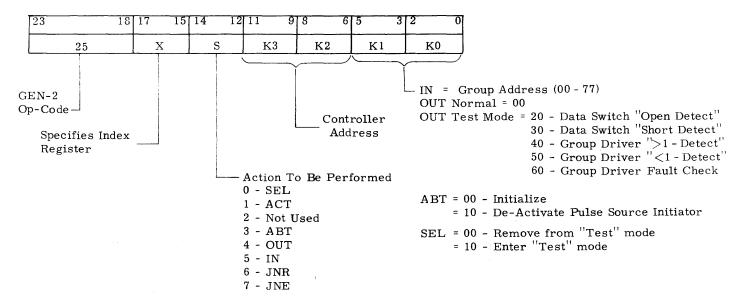

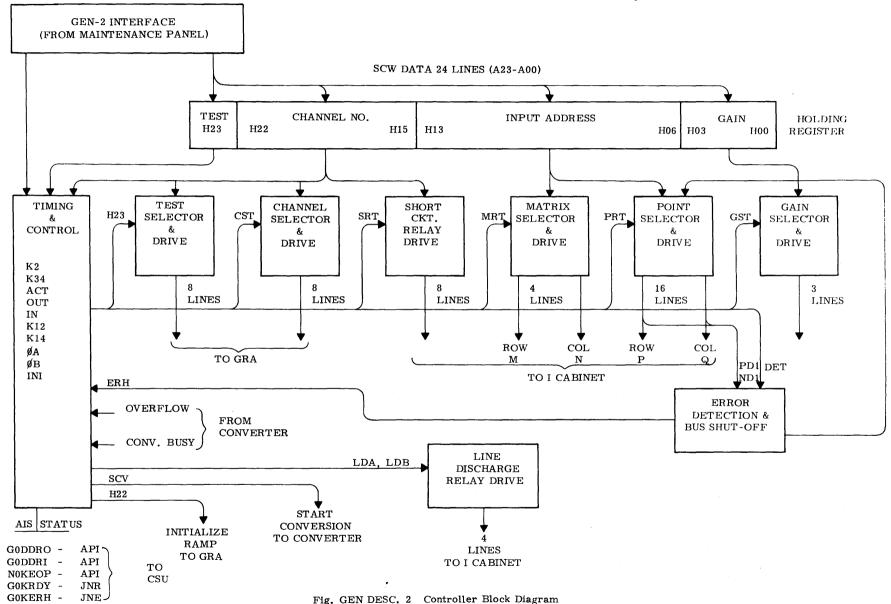

The following GEN 2 instructions, when addressed to the Process Digital Controller (PDC), affect the Process Digital I/O Subsystem as described in the following paragraphs. Fig. INS.1 illustrates the format of the GEN 2 command and the basic Process Digital I/O control.

#### **ABT - Abort PDC**

ABT with K1 = 0 initializes the entire PDC, terminating any operation in progress, and releasing the PDC for a subsequent operation. Pushing the ON/INIT switch on the Programming and Maintenance console when in the MANual mode and the console enabled has the same effect.

#### **ABT - Abort Pulse Source Initiator**

ABT with K1 = 1 deactivates the optional (AS08) Pulse Source Initiator if it is activated. This instruction has no other effect on the PDC and may be used to deactivate the Pulse Source Initiator without affecting any other operation in progress.

#### ACT - Activate

ACT generates a PDC ready interrupt by temporarily moving the ready line from "ready" to "not ready" and back to "ready". If the PDC is "not ready" (busy) when ACT is executed, the instruction has no effect.

#### IN - Input

IN replaces the contents of the Arithmetic Unit A Register with the binary status (1 for closed, 0 for open) of the digital input group specified by the K1,0 bits. Refer to the Digital Inputs section of this publication for further details.

If the PDC is in the Test Mode, the IN instruction replaces the contents of the A Register with the contents of the PDC Output Buffer Register. Refer to the Test Mode description contained later in this section.

#### JNE - Jump No Error

JNE tests the PDC error line to determine if a fault occurred in a previous digital output or test operation. If an error exists, the error indication is cleared permitting further operations and program control is transferred to the first sequential (P+1) instruction. If no error indication exists, program control is transferred to the second (P+2) instruction.

A detailed discussion of error detection is provided in the Output Fault Checking and Test Mode sections of this publication.

#### JNR - Jump Not Ready

JNR tests the busy or ready status of the PDC. If the PDC is ready, program control goes to the next sequential location (P+1). If the PDC is busy, program control goes to the second sequential location (P+2). The PDC is busy during an output operation and held busy if a fault (error) is detected.

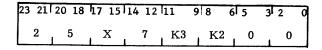

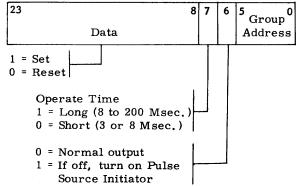

#### **OUT - Output (Normal)**

An OUT command executed when the PDC is in the normal mode (not test mode) and "ready", transfers the contents of the A Register to the PDC and initiates the output operation. The A Register must contain a Control/Data Word corresponding to the format shown below. Refer to the digital Output section for details.

An OUT command with K1 equal to 0 executed when the PDC is in the test mode (following a previous SEL 10 command) is ignored.

#### Control/Data Word (A-Register)

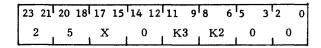

Fig. INS. 1 GEN2 Format

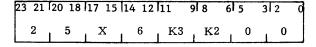

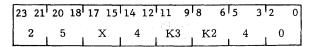

## OUT - Data Switch Open Detector Check (Test Mode)

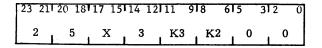

| 23 21 | 20 18 | 17 15 | 14 12 | 11 9 | 8 6 | 5 3 | 2 0 |

|-------|-------|-------|-------|------|-----|-----|-----|

| 2     | 5     | X     | 4     | К3   | K2  | 2   | 0   |

Executing this instruction in the Test Mode with one or more data bits in the A Register control/data word a "0" causes an output fault if the Data Switch Open detector is functioning properly and there are no shorted data switches. Executing this instruction in the Test Mode with all data bits in the control/data word "1" causes no output fault if there are no open data switches. To test all data switches in a system containing more than 378 groups, the command must be executed twice; once with bit 5 a "one" and once with bit 5 a "zero".

Refer to the Test Mode description contained later in this section for further details.

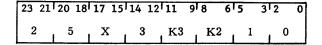

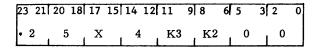

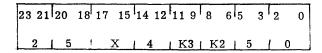

#### OUT - Data Switch Short Detector Check (Test Mode)

| 23 21 20 1 | 8 17 15 | 14 12 | 11 9 | 18 6 | 5 3 | 2 0 |

|------------|---------|-------|------|------|-----|-----|

| 2 5        | X       | 4     | К3   | K2   | 3   | 0   |

Executing this instruction in the Test Mode with one or more data bits in the A Register control/data word a "1" causes an output fault if the Data Switch Short detector is functioning properly and there are no open data switches. To check all data switches in a system with more than 378 groups, this command must be executed twice; once with bit 5 a "one" and once with bit 5 a "zero". Executing this instruction with all control/data word bits "zero" causes no output fault if there are no shorted data switches.

Refer to the Test Mode description contained later in this section for further details.

# OUT - More Than One Group Driver On Detector Check (Test Mode)

Executing this instruction in the Test Mode generates an output fault if the More Than One Group Driver On Detector is functioning properly and there are no open group drivers. The data field is ignored during the execution of this command.

Refer to the Test Mode description contained later in this section for further details.

#### OUT - No Group Driver On Detector Check (Test Mode)

Executing this instruction in the test mode causes an output fault if the No Group Driver On Detector is functioning properly and there are no shorted group drivers.

Refer to the Test Mode description contained later in this section for further details.

# OUT - Group Driver Fault Check (Test Mode)

Executing this instruction in the test mode causes no output fault if there are no faulty group drivers. To check all group drivers it must be executed twice, one with bit 4 = 1 and once with bit 4 = 0. Executing an IN command addressed to the PDC following the execution of the OUT60 commands loads the A Register with the contents of the Output Buffer Register which should correspond to the contents of A when the OUT command was issued. If not, either the data path between the AU and the PDC is faulty, or the Output Buffer Register in the PDC is faulty.

Refer to the Test Mode description contained later in this section for further details.

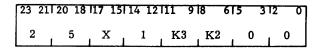

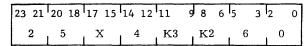

#### SEL - Select Test Mode

| 23 21 | 20 18          | 17 15 | 14 12 | 11 9 | 8 6 | 15 3 | 1 2 | q |

|-------|----------------|-------|-------|------|-----|------|-----|---|

| 2     | 1 <sup>5</sup> | х     | 0     | К3   | K2  | 1    | 0   |   |

Executing SEL with K1 = 1 when the PDC is ready, places the PDC in the test mode. In the test mode, no output relays can be energized (unless a hardware fault exists).

Refer to the Test Mode description contained later in this section for further details.

#### SEL - Select Normal Mode

Executing the SEL command with K1 = 0 when the PDC is ready removes the PDC from the test mode.

Refer to the Test Mode description contained later in this section for further details.

## **DIGITAL INPUTS**

The operation of the digital input portion of the subsystem is controlled by the execution of an IN command addressed to the Process Digital Controller (K3, K2) and to a digital input group (K1, K0). Executing the IN command when the PDC is not in the test mode replaces the contents of the A Register with the status of the 24 digital input signals connected to the addressed input group. Each A Register bit set corresponds to a closed digital input contact or a "true" input logic level.

Executing an IN command when the Process Digital Controller is in the test mode replaces the contents of the A Register with the status of the Process Digital Controller Output Buffer Register. The test mode of operation is described later in this section.

The digital input operation is completed during the execution (26.5  $\mu$ sec.) of the IN command. Therefore, the digital input subsystem is always ready and does not require a ready test function (JNR). There is no hardware error checking associated with the input function. Many systems, however, provide validity checking using software and by connecting one input of each 24 input group to the digital input power supply. This is described in more detail in the Digital Input Terminations section that follows.

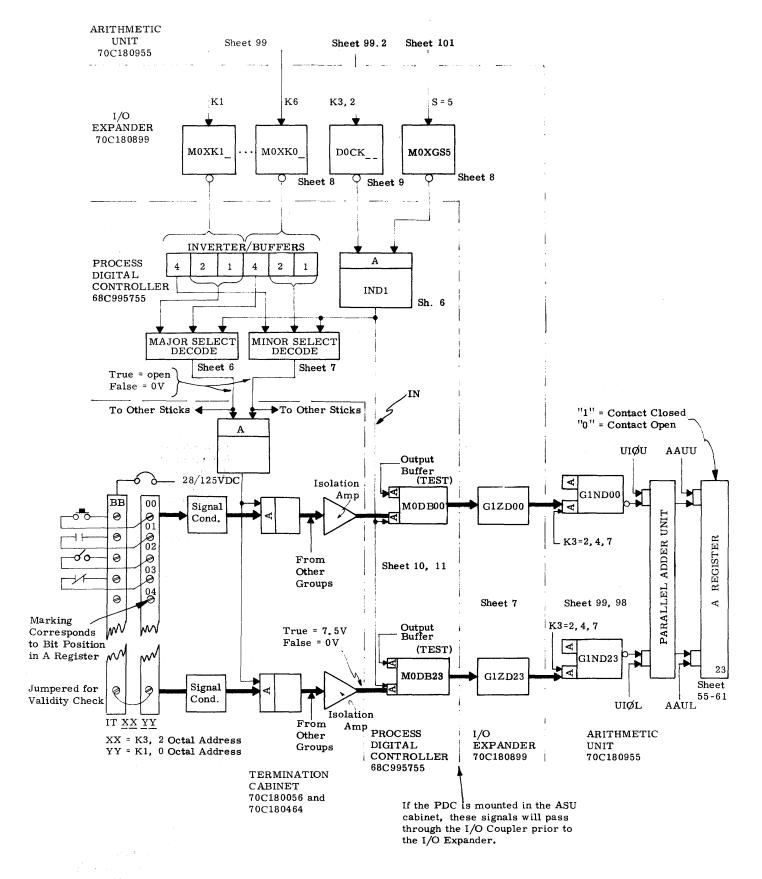

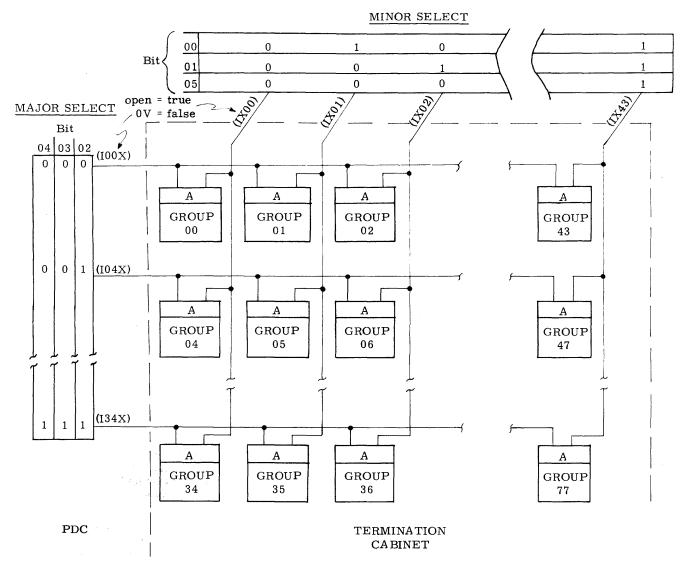

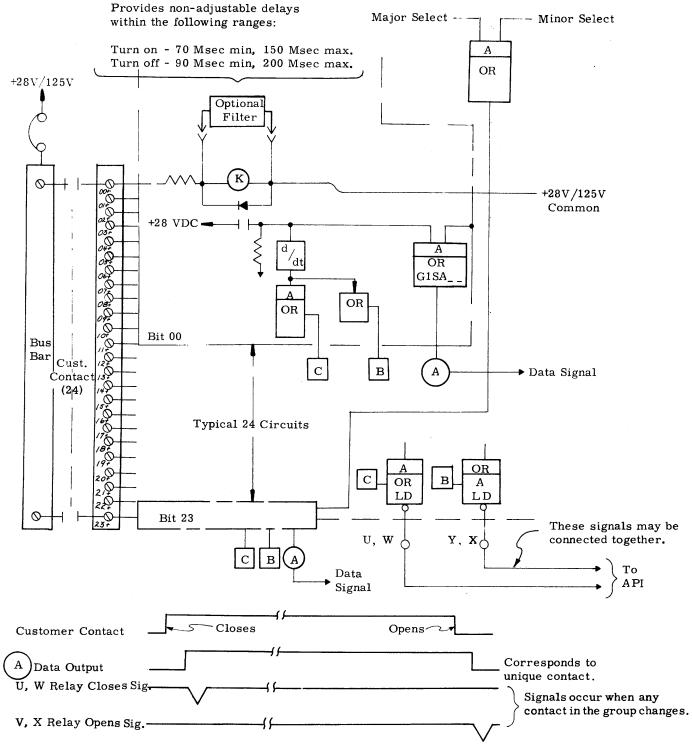

Fig. DIN. 1 contains a detailed block diagram of the digital input portion of the subsystem illustrating the basic data flow and selection logic. As illustrated, the logic levels or contacts from the process are connected to the termination cabinet. These digital input contacts are normally supplied from either a 28VDC or a 125VDC power supply in the termination cabinet. Therefore, when a digital input contact is closed, either 28VDC or 125VDC is connected to the input termination. From the termination, the signal is routed through a signal conditioning circuit and then to a group selection gate. This group selection gate is enabled only when the K1, K0 address portion of the IN command being executed corresponds to the input group of the signal. The K1, K0 bits of the IN command are decoded within the PDC providing the select signal to the group selection gate. From the group selection gate the signal is applied through an isolation amplifier (line driver) to the Process Digital Controller. The S=5 bits and K3, K2 address bits of the IN command, enable the signal through the I/O Expander to the Arithmetic Unit, A Register. Operation of the Arithmetic Unit is the same for all IN commands as described in the Arithmetic Unit Theory publication contained in this book set.

#### INPUT SELECTION

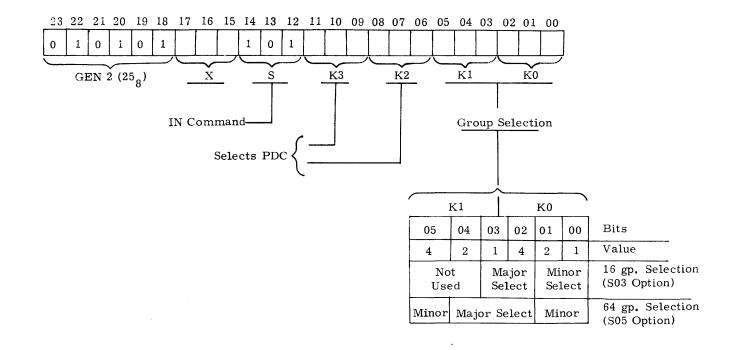

Fig. DIN. 2 illustrates the format of the GEN 2 IN command and the bits associated with enabling and selecting a digital input group. The S and K bits of the GEN 2 command are applied from the Arithmetic Unit, throuth the I/O Expander to the Process Digital Controller. The PDC decodes these bits, selects the input group and enables the digital input function.

The K3, K2 address of the PDC is optional and pin selected on the SIOA5 board in slot A03. The K3, K2 address selected by the jumper pins and the S bits are decoded on sheets 4 and 6 of the PDC logic (68C995755) to enable the Read In Digital Input Driver (D0ING1). The Read In Digital Input Driver enables decoding of the K1, K0 bits for group selection and gates the input data from the termination cabinet through the Line Receivers (M0DB00 - 23, sh. 10 and 11) to the I/O Expander for application to the Arithmetic Unit.

Selection of a digital input group occurs by enabling one minor select line and one major select line corresponding to the K1, K0 bits of the IN command. These minor and major select lines are applied to the termination cabinets where they are ANDed to select a particular group. The group address matrix decode scheme, using the minor and major select lines, is shown by the table on sheet 5 of the PDC logic. This table illustrates both the 4 x 4 matrix required for a 16 group input system (AS03 option) and the 8 x 8 matrix required for a 64 input group system (AS05 option). The mnemonics listed in the matrix scheme table correspond to the mnemonics assigned to the decode logic elements shown on logic sheets 6 thru 9.

Fig. DIN. 3 illustrates the group select matrix scheme in a slightly different form showing the general interconnections and selection within the termination cabinet. This figure also illustrates the bit configuration associated with the mnemonics of the various decode logic elements. The mnemonics are formed as shown in the following examples:

Major Selects: I24X = bit 4, and 2 are both "1"

Value of K0=4 bit

Value of K1=1 and K1-2 bits

Minor Selects: IX41 = bit 5 and bit 0 are both "1"

Value of K0=1 and K0=2 bits

Value of K1=4 bit

The major and minor select lines to the termination cabinet are open for true and 0V for false.

#### INPUT TERMINATIONS

The maximum input capacity of each Process Digital Controller provides for 64 groups of 24 contacts per group or 1536 contact inputs. As described in Model Number/Options section, control for no input groups, 16 input groups, or 64 input groups may be selected for a system.

All digital inputs are connected to a termination cabinet. Although the logic drawing number (70C170056) is subject to change, the general input termination cabinet configuration illustrated in Fig. DIN. 1 should apply. The digital input logic drawing for a particular system will be referenced on the Digital Termination Cabinet Index for the system.

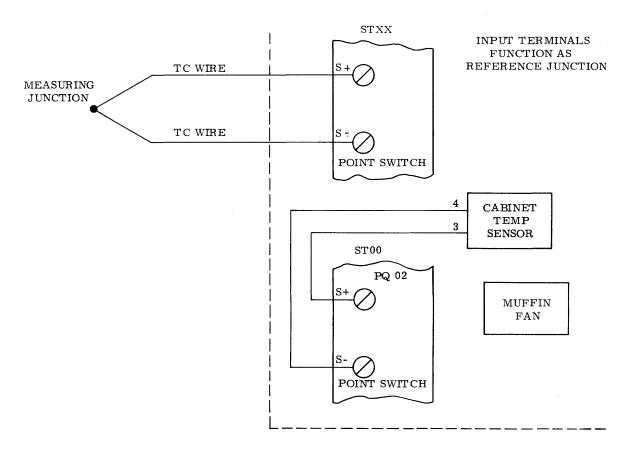

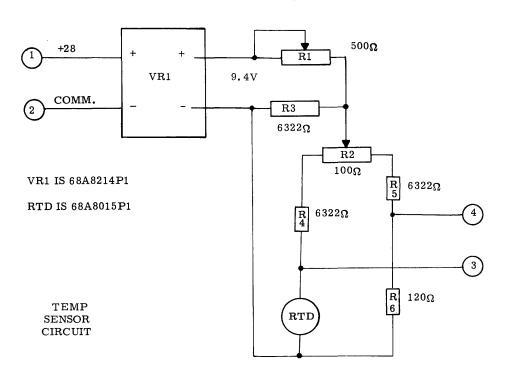

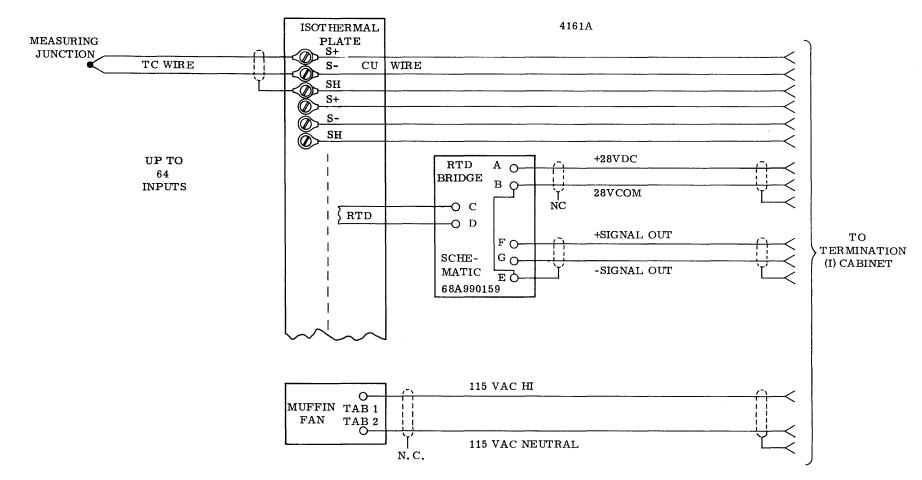

Fig. DIN. 1 Digital Inputs

Fig. DIN. 2 IN Command Format

The digital inputs are terminated on sticks within the termination cabinet. Each stick is divided into digital input termination groups of 24 inputs (points) and labeled:

ITxxyy

Where: xx = K3·K2 octal address

yy = K1·K0 octal address

The System Hardware Address Summary drawing supplied with each system identifies the digital input signals and their termination points.

Power is supplied from a buss bar (BB) in the termination cabinet to the digital input contacts. Normally +28VDC is supplied, however, where the contacts are operated in an environment that may be contaminated easily, +125VDC may be used. The Model Number Option associated with the power supply is described earlier in this section.

In many systems, the power supply voltage on the buss bar is jumpered directly to the data input termination point for bit 23. This serves as a validity bit indicating that the circuit breaker and power supply are providing power to the system contacts when bit 23 is a "one".

From the termination sticks, the digital input signals are applied through signal conditioning circuits. These signal conditioning circuits convert the digital inputs to a form suitable for input to standard logic circuits. From the signal conditioning circuits, the signals are applied to gating circuits which are enabled

according to the group addressed by the IN command. The signal conditioning circuits and gates are contained on a single printed wiring borad which is selected according to the signal input type. A partial list of these signal conditioning boards is provided in the Model Number/Options section.

Optionally, change detection signal conditioning circuit boards may be contained in the system. These signal conditioning boards provide pulse outputs suitable for use as API input signals when: (1) any contact in a group opens, (2) any contact in a group closes, or (3) when any contact in a group changes state (opens or closes).

Fig. DIN. 4 illustrates the basic logic of a Change Detector signal conditioning board. Although it illustrates a Change Detector board connected for +28V/+125V (depending on system option) switching by the digital input contacts, the board may be connected for GND switching.

When a digital input contact changes state, a relay within the Change Detector also changes state. If any relay within the group changes from de-energized to energized, a pulse is coupled from its d/dt circuit resulting in an output at the U and W pins for use as an automatic program interrupt. If the relay changes from energized to de-energized, the d/dt couples a pulse to the V and X output for use as an automatic program interrupt. These outputs may be connected together providing a signal that indicates either change. The status of the group contacts may be read-in to the A Register by addressing the digital input group.

NOTES: (1) The group address corresponds to the K1, K0 octal address.

(2) The input termination groups are marked:

IT XX YY

XX = K3·K2 Octal Address

YY = K1.K0 Octal Address

Fig. DIN. 3 Input Group Selection

The signal conditioning boards with change detection have 24 inputs (on group) per board instead of 48 inputs for other signal conditioning boards. Each group of 24 change detection inputs require two groups of input stick capacity.

From the signal conditioning boards the selected data group is routed through isolation amplifiers which act as buffers and line drivers. The isolation amplifier provides sufficient drive to send data to the PDC in the Central Systems Unit. Twenty-four isolation amplifier circuits are contained by one printed wiring board (PX1000IIAA1orB1). Since only one group (24 inputs) is enabled at any one time, only one board is

required in a system. The data inputs from the selection circuitry are daisy-chained to the isolation amplifier input. The output from the isolation amplifier is at +7.5 volts for a true signal (data bit = 1) and at 0 volts all other times.

#### **CSU DATA FLOW**

The twenty-four data bits of the addressed group are routed from the isolation amplifier in the Termination Cabinet to the Process Digital Controller located in the CSU.

As shown on sheets 10 and 11 of the PDC logic, 68C995755, data from the isolation amplifiers are

Fig. DIN. 4 Change Detectors

applied to line receiver circuits, (M0DB23 - 00). Data are gated through these line receivers by the decoded S and K3, K2 bits of the IN command. Decoding S=5 and the K3, K2 bits equal to the pin selected address enables D0IND1 (sheet 6) and D1DNIN1, 2, 3, 4, to perform the gating function. The output from the line receivers is at 0 volts for a closed or true data bit and at 5 volts for a open or false data bit.

The data from the PDC are routed to drivers and line receivers in the I/O Expander. From the I/O Expander, the data signals at 0 volts for true and 3.5 volts for false are gated through the I/O Input gates and the parallel adder unit to the A Register. The operation of the Arithmetic Unit during the execution of IN commands is described in the Arithmetic Unit Theory description contained in this book set.

## **DIGITAL OUTPUTS**

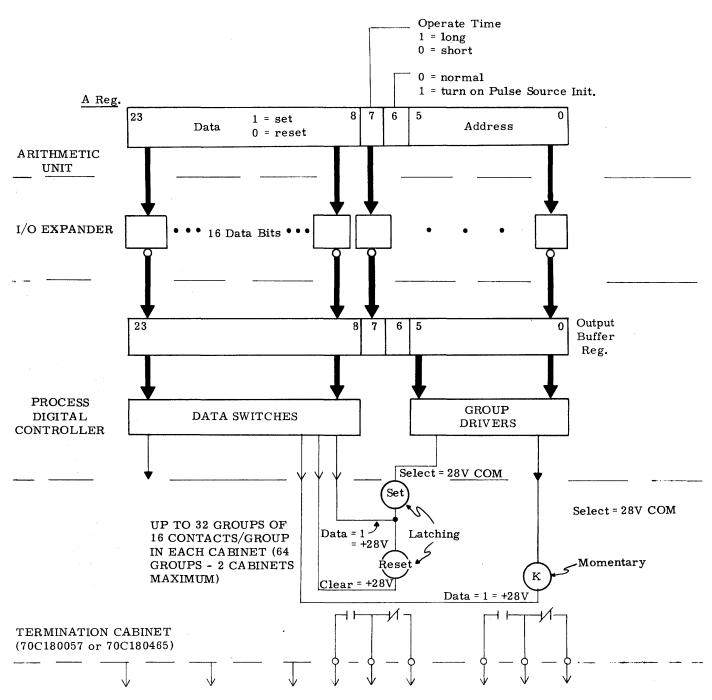

Fig. DOUT. 1 illustrates the basic output control and signal flow within the Digital I/O Subsystem. Operation of the optional Pulse Source Initiator (AS08 option) is described later in this section.

#### NOTE

Logic element mnemonics and sheet numbers contained in paranthesis in the following text refer to the Process Digital Controller (PDC) logic, 68C995755, unless otherwise specified.

The following steps illustrate the general operating sequence of the digital output logic in the normal (non-test) mode.

1. If the PDC is not busy from a previous operation, an OUT command addressed to the PDC (K3, K2) with K1, K0 equal to 00 initiates the digital output operation. The contents of the Arithmetic Unit A Register (Data/Control Word) are transferred to the Output Buffer Register (F10B23-00, sheets 18 - 23).

#### NOTE

A software timer using a clock API may be set at this time. If this time period elapses, an Echo API will indicate an error.

- The PDC is placed in the busy state (F1SMXB, sheet 15) causing the ready line (GOAJNR, sheet 14) for JNR monitoring to go not ready.

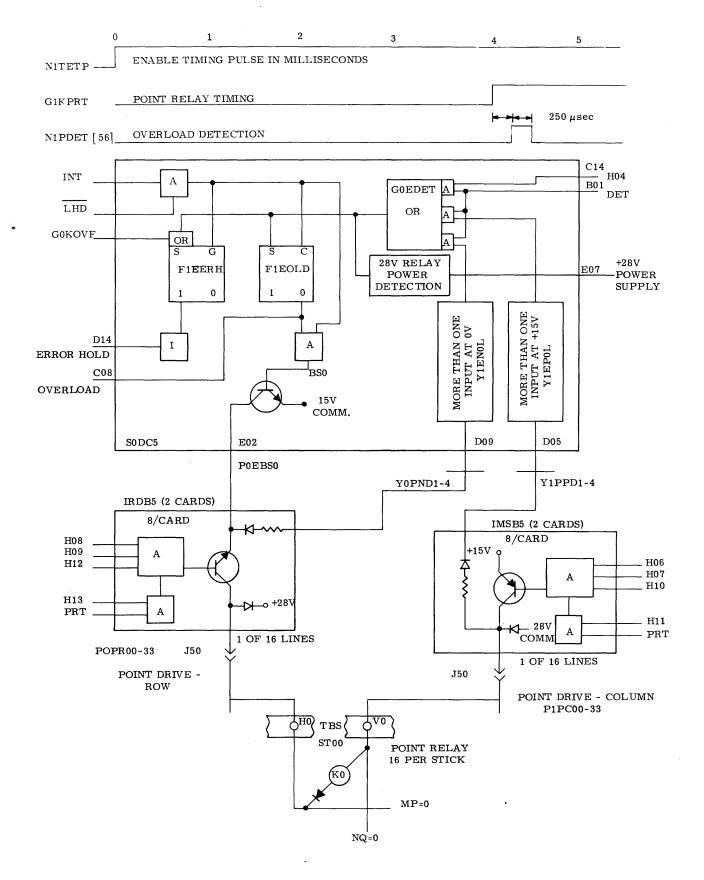

- The following checks are performed to determine if a fault exists in the digital output subsystem.

- All 17 data switches (least or most significant depending on the group being addressed) are enabled (F1SFDS, D0SDSF, sheet 15) and then the data switch outputs are checked (Y1ETO1, G0EDET, sheet 31) to determine if all 17 are on (i.e., no open data switches).

- The Enable 17 data switches signal (D0SDSF) is disabled, and prior to enabling the data bits to the switches, a check (Y1EDSO sheet 31) is made to determine if all data switches are off (i.e., no shorted data switches).

- During the time the output relays are energized, the PDC checks (Y1ETO1, G0EDET, sheet 31) to determine that one and only one group driver is on (i.e., that the addressed group driver is not open and that no other group drivers are shorted).

- After the output relay energization time has elapsed, the data switches are disabled and

then checked (Y1EDSO, sheet 31) to determine that no data switches remain on.

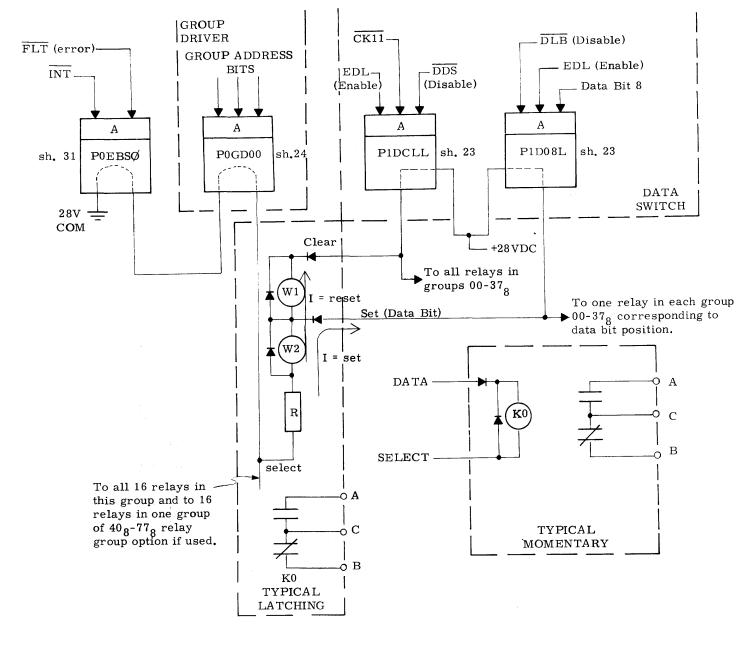

Detection of an output fault places the JNE line (GOAJNE, sheet 14) in the "error" state, disables the output relay current (P0EBSO, sheet 31), holds the ready line (GOAJNR, sheet 14) "not ready", and lights (DOAERR, sheet 14) the FAULT indicator. No output relay energization can occur until the error condition is cleared. The error condition can be cleared by executing a JNE command (N1ES07, sheet 31), or manually by pressing the ALARM CLEAR switch or the ON/INT switch on the Programming and Maintenance Console when the console is enabled and being operated in the manual mode.

Refer to the Output Fault Checking portion of this section for further details.

If no output fault is detected, the group driver corresponding to the address  $(A_{5-0})$  is enabled (28 Volt Common) and the data switches corresponding to the data bits  $(A_{23-8})$  are enabled, (+28V) energizing the corresponding output relays. Current is applied to the relays for the time interval specified by  $A_7$  and the position of a jumper pin. If  $A_7 = 0$ , the short operate time of 3 or 8 milliseconds, depending on the position of a jumper pin (TOSNRM, sheet 16) will occur. If  $A_7 = 1$ , the long operate time of 8 to 40 milliseconds (adjustable) or 40 to 200 milliseconds (adjustable) depending on the position of another jumper pin (TOSALT, sheet 16) will occur.

Latching relays will of course remain in the state dictated by the associated data bits and are normally enabled for the short operate time (A7 = 0). Momentary relays remain in the set state, if dictated by the associated data bits, for the approximate duration of the energizing current and then revert to the reset state. Momentary relays are normally enabled for the long operate time  $(A_7 = 1)$ .

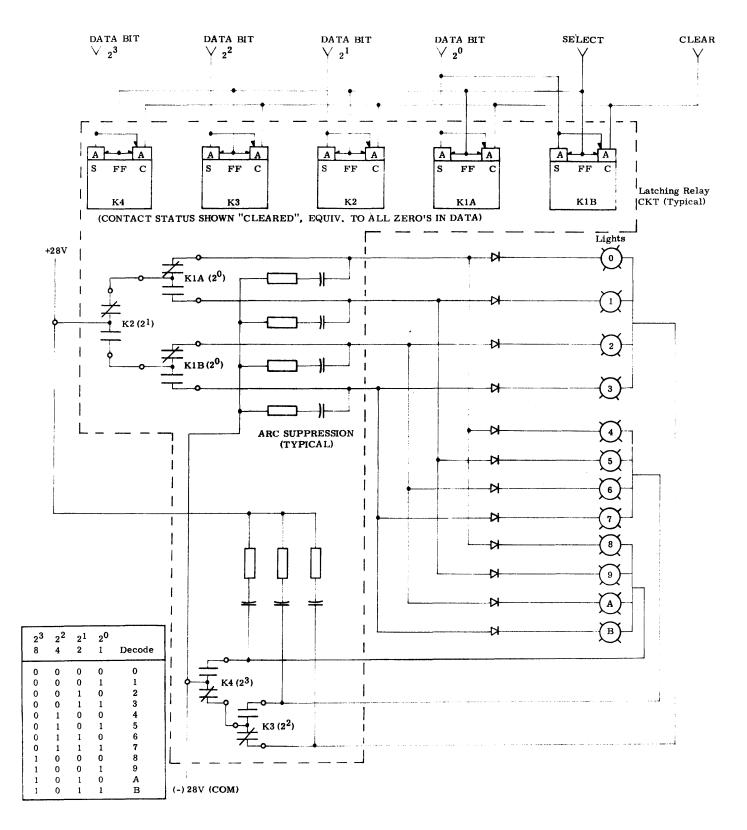

Fig. DOUT. 1 illustrates the connections and operation of both latching and momentary output relays. In addition to the data switch output (+28V = 1) and the group driver output (28 V Com when enabled), a Clear Signal (+28V) is also applied to latching relays during relay energization time. If the data switch output is disabled representing a "zero" data bit, current will flow through the reset relay. If, however, the data bit is a "one", the data switch will be enabled and current will flow through the set relay.

When the operating time specified by bit 7 and the jumper pins has elapsed and if no fault has occurred, the ready line reverts to the ready state for JNR monitoring and generating an Automatic Program Interrupt normally to complete the output operation.

LATCHING, MOMENTARY, DIGITAL DISPLAY, ANALOG OUTPUTS TO PROCESS CONSOLES, OPERATOR CONSOLES, TREND RECORDERS, ETC.

Fig. DOUT. 1 Digital Output Signal Flow

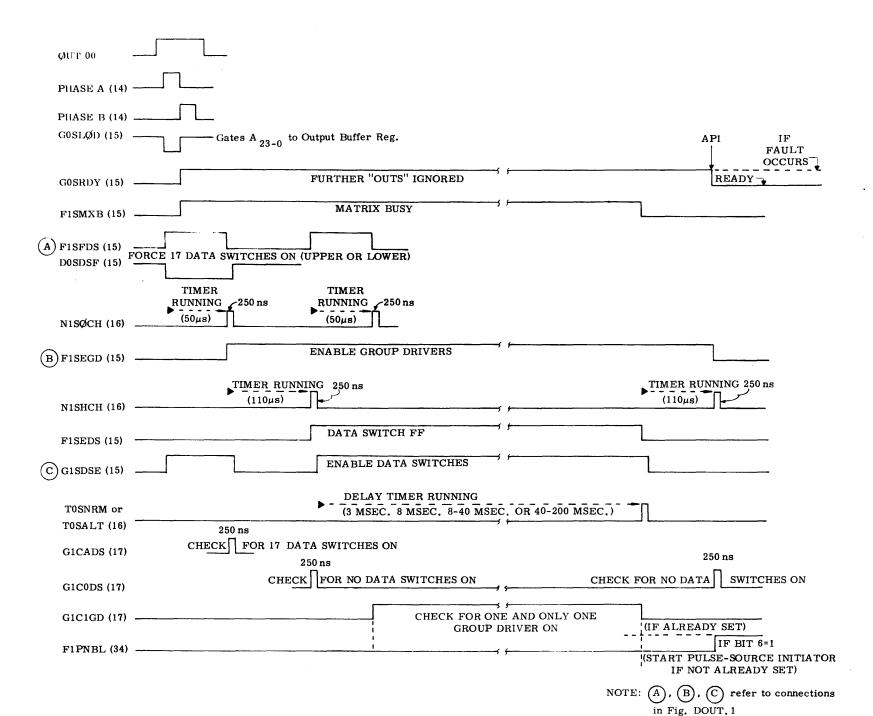

# OUTPUT SEQUENCING AND CONTROL

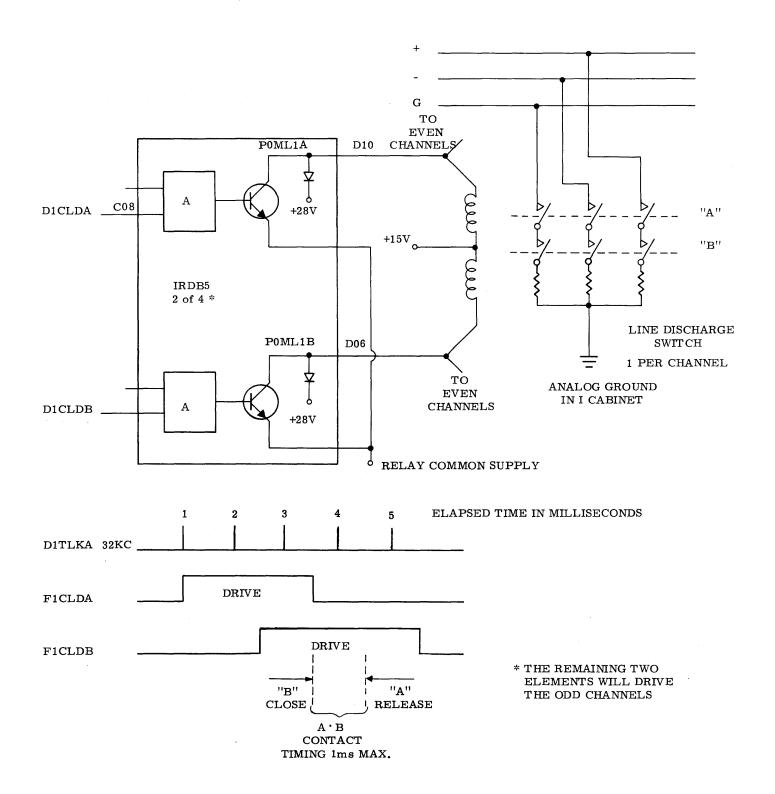

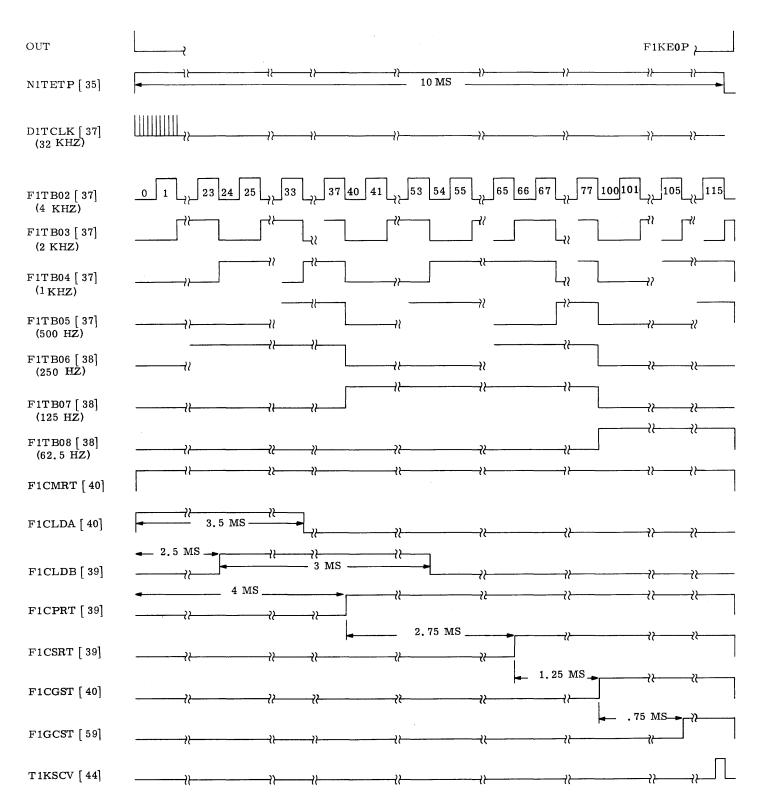

The output sequencing and control portion of the PDC is shown on sheets 15, 16, and 17 of the PDC logic. Fig. DOUT. 2 illustrates some of the control functions performed and Fig. DOUT. 3 contains a timing diagram of the primary control signals.

The normal OUT command addressed to the PDC with K1·K0=00, causes the data from the Arithmetic Unit A Register to be loaded into the Output Buffer Register (F1OB23-00, sh. 18-21). Data is loaded (G0SLOD) into the Output Buffer Register during Phase A time of the OUT command when the PDC is ready.

G0DLOD = AS04 · APHA · SRDY

Enabling GOSLOD sets F1SFDS forcing on all 17 least significant data switches (DCLL, D08L - 16L, sh. 22, 23) or most significant data switches (DCLM, D08M - 16M) depending on the status of address bit 5. If address bit 5 is a "one" the most significant group is enabled and if bit 5 is a "zero" the least significant group is enabled. The least significant data switches control relay groups  $00_8$ -378. The most significant data switches control relay groups  $40_8$ -778 and are only contained in systems with the ASO7 option. The output of the data switches are monitored to determine if 17 are "on". If 17 data switches are not enabled, the Fault (F1EFLT) and Error (F1ERRH) flip-flops are set and no output relays will change state. A detailed discussion of fault detection is described later in this section.

Phase B of the OUT command sets the Matrix Busy (F1SMXB) flip-flop disabling the ready line for JNR monitoring. This signal is also applied to the API module and when the PDC goes ready at the end of the operation, an interrupt will be initiated. At the end of Phase B, the Arithmetic Unit is free to execute other instructions. If another OUT to the PDC is executed it will be ignored until the PDC is ready. A JNR command may be executed for this purpose or an interrupt will occur when the operation is complete.

After the fault check to determine if all 17 data switches can be turned on, the Force Data Switches signal (D0SDSF) is disabled and the Enable Group Drivers flip-flop (F1SEGD) is set. Setting F1SEGD enables the Group Drivers that correspond to the group address ( $\mathbf{A_{4-0}}$ ).

Setting F1SEGD also provides an input to a 110 Microsecond delay circuit, T0SHCH (sheet 16). The output of this delay circuit enables a fault check to determine that no data switches are on. If a data switch is on, a fault exists and operation of the group drivers is inhibited preventing any relays from changing state. A detailed discussion of fault detection is described later in this section.

The timer circuit, TOSHCH, also sets the Enable Data Switches flip-flop (F1SEDS) after expiration of the 110 usec. delay. Setting the Enable Data Switches flip-flop enables the data switches corresponding to address bit 5 and the status of the data bits. Enabling the data switching, in conjunction with the enabled group drivers, will energize the digital output relays.

The Enable Data Switches flip-flop also applies a signal to the time delay circuits, TOSNRM and TOSALT, that determine the time duration that current will be applied to the relays. Time delay circuit TOSNRM establishes this time interval when bit 7 of the control word from the AU is "0". When the time interval determined by bit 7, and the setting of the delay circuit has elapsed, the Matrix Busy flip-flop also applies a signal to a 110 usec. time delay circuit, TOSHCH (sheet 16). TOSHCH, after the 110 µsec. delay, enables G1CODS (sheet 17) to verify that no data switches remain on, and clears the Enable Group Drivers flip-flop, F1SEGD. Clearing the Enable Group Drivers flip-flop turns off the group drivers and enables the ready line, GOSRDY, triggering an automatic program interrupt and providing a ready signal for JNR monitoring. This ready signal, however, cannot be enabled if an error was detected in any of the fault checks. A fault check error enables NOERRH (sheet 31) which inhibits the ready signal, GOSRDY. If no error is detected, the ready signal is enabled completing the digital output operation. A subsequent OUT command may be executed to initiate another digital I/O operation.

#### **OUTPUT SELECTION**

Fig. DOUT. 2 illustrates the basic output selection scheme in the Process Digital I/O Subsystem. Address bits 0 thru 4 of the control/data word from the AU are decoded to enable a unique Group Driver, (GDxx where xx is equal to the octal value of address bits 0 thru 4). Address bit 5 is used in systems with more than 378 output groups to select a particular group of output data switches. When bit 5 is a "zero", the Least Significant Data Switches (DCLL, D08L -16L, sheet 22, 23) are enabled according to the data bits of the control/data word. When bit 5 is a "one", the Most Significant Data Switches (DCLM, D08M -16M sheet 28, 29) are enabled. The Least Significant Data Switches control relay groups 00 thru 37g (bit 5 = 0) and the Most Significant Data Switches control relay groups 40 thru  $77_8$  (bit 5 = 1).

Fig. DOUT. 4 illustrates the control and current flow associated with the selection of a particular relay. POEBSO (sheet 31) is enabled applying 28V Common to the Group Drivers provided no output fault exists. If a fault is detected, 28V Common is removed from the Group Drivers and no relay select current can flow. A detailed discussion of fault detection is described later in this section.

A particular Group Driver is enabled during the output operation according to address bits 0 thru 4. Enabling a Group Driver (POGD00 in Fig. DOUT.4) applies the 28 Volt Common signal to one relay group (16 relays) controlled by the Least Significant Data Switches (Groups 00 thru 37<sub>8</sub>) and one relay group controlled by the Most Significant Data Switches (Groups 50 thru 77<sub>8</sub>) if more than 37<sub>8</sub> groups are contained in the system.

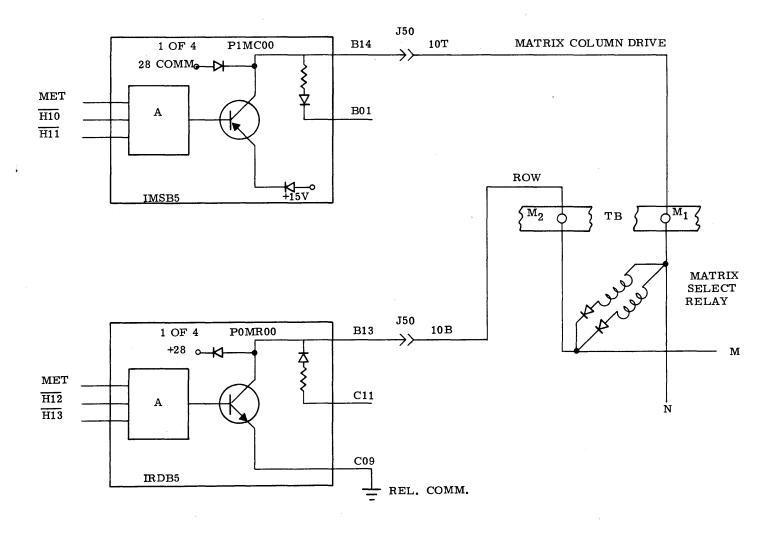

Fig. DOUT. 2 Digital Output Block Diagram

(A), (B),

Refer to Fig. DOUT. 3 For a Timing

Diagram of These Signals.

Fig. DOUT. 3 Digital Output Timing Diagram

Fig. DOUT.4 Output Relay Selection

The Data Switches, which are enabled according to the data bits of the data/control word from the AU, apply +28 volts to the relay in each group that corresponds to the bit position. Therefore, the relay group having the 28 volt common signal enabled to it will be controlled by the data switches.

Control of latching relays and momentary relays is slightly different. As shown in Fig. DOUT. 4, three lines are connected to a latching relay. In addition to the Group Driver output and the Data Switch output, a Clear line is required for latching relays. The Clear line is always enabled during the time the Data Switches are enabled. To understand the operation of

a latching relay, consider the following two conditions while referring to Fig. DOUT. 4. First, consider that the Select line from the Group Driver is enabled applying 28V Common to the bottom of the latching relay and the corresponding data bit (8 in Fig. DOUT. 4) is a "one". Since the corresponding data bit is a "one", +28 volts is enabled to the top of the W2 portion of the latching relay. Therefore, current will flow through the W2 portion setting the relay. Notice that no current will flow through the W1 portion even though the Clear line is enabled applying +28 volts to the top of W1, since the bottom of W1 is at +28 volts from the enabled data line. Second, consider that the corresponding data bit is a "zero". Since the data bit is a "zero", an open will be present on the Data line.

Fig. DOUT. 5 Decimal Display Output

DATA BIT (Most Significant Bit)

LATCHING

RELAY

$(\mathbf{v})$

LATCHING

RELAY

Analog o-Gen. Pwr.

Supply +42V DC (v)

A FF

Typical

LATCHING

RELAY

Adjusted for line impedance, resistor tolerance, etc., (Range of 50 to 475 ohms)

DATA BIT

LATCHING RELAY

LATCHING RELAY DATA BIT

LATCHING RELAY LATCIIING RELAY DATA BIT

LATCIUNG

RELAY

8 Bit

Resolution

Since the Select line is enabled and the Clear line is always enabled, current will flow through both W1 and W2. The current flow through W1 will reset the relay. Therefore, the latching relay is set by a "1" data bit and remains in that state until changed by a "0" data bit.

Momentary relays remain in the set state only during the time (approximate) that current flows through them. Therefore, momentary relays are normally enabled by a long operate time (bit 7 of the control/data word = 1) of 8 to 40 or 40 to 200 milliseconds as selected by a jumper pin and variable adjustment. Since the momentary relays return to the reset state when current is removed, the clear signal is not required for these relays. The select line enables the 28 Volt Common line to the addressed momentary relay group and +28 Volts is enabled to only those relays that have a corresponding data bit equal to "1". Therefore, current will only flow through those relays that correspond to the address and "1" data bits in the data/ control word. These relays will be set, but only for the duration of the output energization current.

#### **OUTPUT TERMINATIONS**

As previously mentioned, the maximum output capacity for each Process Digital Controller is 64 groups having 16 points per group or 1024 digital output points.

The output contact rating may be either 100VA or 250VA depending on the application. Up to 32,100VA output groups or 16,250VA output groups may be installed in a single output termination cabinet. As previously mentioned, the outputs may be momentary or latching.

#### **Decimal Displays**

Digital output groups capable of driving four decimal displays are available. Fig. DOUT.5 illustrates the operation of a typical display output using 4 data bits. Since the relays are latching, the display will remain until changed by a subsequent digital output addressed to the group. The 16 bit data format of the data/control word is capable of controlling four such displays.

#### **Analog Outputs**

Any latched contact output group may be used to control an analog generator providing an analog voltage or current corresponding to the data field. Either 8 or 10 bit analog generators may be used. Two 8-bit analog generators are incorporated in one output group. The output voltage or current range is determined by the application and adjustment of the generators. Fig. DOUT. 6 illustrates the typical operation of an 8-bit analog generator. An analog output requires a stable +42 VDC power supply in the output termination cabinet. The status of the individual relays, and consequently the output, depends on the status of the individual data bits of the data/control word.

The resistor values in the analog generator are in a binary progression from the most significant to the least significant data bit. In an 8-bit analog generator, resolution of 1 part in 255 is provided. In a 10-bit analog generator, resolution of 1 part in 1023 is provided. Enabling a digital output relay parallels the associated resistor with any other resistor that may be enabled between the common power supply and the output point.

#### **OUTPUT FAULT CHECKING**

In order to protect the process and the subsystem hardware, the PDC contains error checking hardware which monitors the digital output portion of the subsystem. During the execution of each digital output operation, the fault check logic determines if any one of the following errors exist:

- Open data switch All 17 data switches (least or most significant if more than 37<sub>8</sub> groups are contained in the system) are enabled and then checked to determine if all 17 are on.

- Shorted data switch Prior to enabling the data switches addressed by the data/control word, the data switches are checked to determine that all of them are off.

- Selected group driver failing to turn on During the time the addressed relay group is to be energized, a check is performed to determine that one group driver is on.

- 4. More than one group driver turning on During the time the addressed relay group is to be energized, a check is performed to determine that only group driver is on.

- 5. A short occurred in the data switch during this operation - After the relay drive current has been disabled, a check is performed to determine if any data switch remains on.

Detection of any of the above errors sets an Output Fault (F1EFST) flip-flop and a Error Hold (F1ERRH) flip-flop. While the Output Fault flip-flop is set, relay energization current is disabled. While the Error Hold flip-flop is set, the PDC ready line is held in the "not ready" (busy) state for JNR monitoring and preventing another digital output operation. The Error Hold flip-flop in the set state also enables the error line for JNE monitoring. The Error Hold flip-flop may be reset by any one of the following means:

- Execution of JNE (after previously initiated operate time has elapsed).

- 2. Execution of an ABT command with K1, 0 = 00.

- Pressing the ON/INIT switch on the Programming and Maintenance Console to initialize the system.

4. Pressing the ALARM CLEAR switch on the Programming and Maintenance console.

F1ERRH = G0ESFF = error detected

F1ERRH = G0ECEH

GOECEH = SO7 · PHB + INT

N1ES07 = JNE command

G1IENT = Initialize + ABT with K1=0 + ALARM CLEAR

The Output Fault flip-flop (F1EFLT, sheet 31), when set, disables output relay energization by disabling F0EBSO (sheet 31) as shown in Fig. DOUT.4. The Output Fault flip-flop is cleared by ABT with K1 = 0, pressing the ALARM CLEAR switch or INIT/ON switch, or by an OUT command that is executed following the clearing of the Error Hold flip-flop by a JNE command.

A1EFLT = G0ESFF = error detected

F1EFLT = G0ECFF

G0ECFF = INT + ELOD

N1ELOD = SLOD = OUT command execution and "ready"

G1IENT = Initialize + ABT with K1=0 + ALARM CLEAR

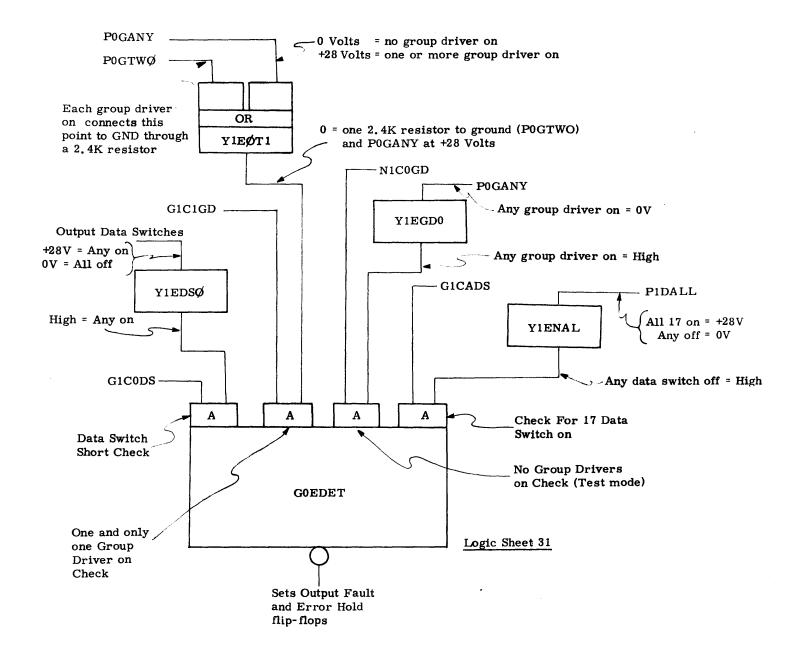

Fig. DOUT. 7 illustrates the operation of the error detection gate, G0EDET, for all error checks. The timing diagram illustrated in Fig. DOUT. 3 shows the timing of the various error control signals (G1CODS, G1CIGD, and G1CADS).

The data switch short check, which checks for no data switches on, is enabled by G1CODS prior to relay energization time. The detector, Y1EDSO, provides a "one" output when any input is at +28 volts. The output data switches are tied to the input (P1DANY) of Y1EDSO. If all output data switches are disabled, P1DANY will be at 0 volts. If any data switches are on, the output of P1DANY will be near 28 volts indicating an error when G1CODS is enabled.

The check to determine that one and only one group driver is on is enabled by G1CIGD during relay energization time when one group driver corresponding to the data/control word should be enabled. The detector, Y1EOT1, provides a "zero" output indicating that only one group driver is enabled when the P0GANY input is at +28 volts and when the P0GTWO input only has one 2.4K ohm resistor connected to ground. Any other condition indicates that no group drivers are enabled (P0GANY = 0) or that more than one group driver is enabled.

Near the beginning of the digital output operation, an open data switch check is performed by forcing (D0SDSF) the upper or lower 17 data switches on for a short period of time (50  $\mu$ sec.) and checking to determine that they are all on. This check is enabled by G1CADS and the status detected by Y1ENAL. The P1DALL input to Y1ENAL, is at approximately +28 volts when all data switches are on or is at approximately 0 volts when any data switches are off. A 0 volt input indicates an error condition, enabling Y1ENAL, which enables G0EDET to set the fault and error hold flip-flops.

Fig. DOUT. 7 Error Detection Block Diagram

# PULSE SOURCE INITIATOR (OPTION)

The optional (4846 A(B)S08) Pulse Source Initiator (PSI) provides drive pulses to control digital set point stations. The PSI may be selected for compatibility with any of the following (or similar) stations:

- General Electric Co.GE-MAC\* 543-16 Control Unit.

- Foxoboro Co. 62HM and 67 CE/CP series controllers.

- Leads and Northrup Co. Sigma "Cyclomone" stepping motor.

- 4. Moore Computer-Set Synchro or Mini-Synchro Controller.

The PSI is started and stopped under program control. It is enabled or started by executing an OUT command with bit 6 of the data/control word in the A Register = 1. It is disabled or stopped by executing an ABT command.

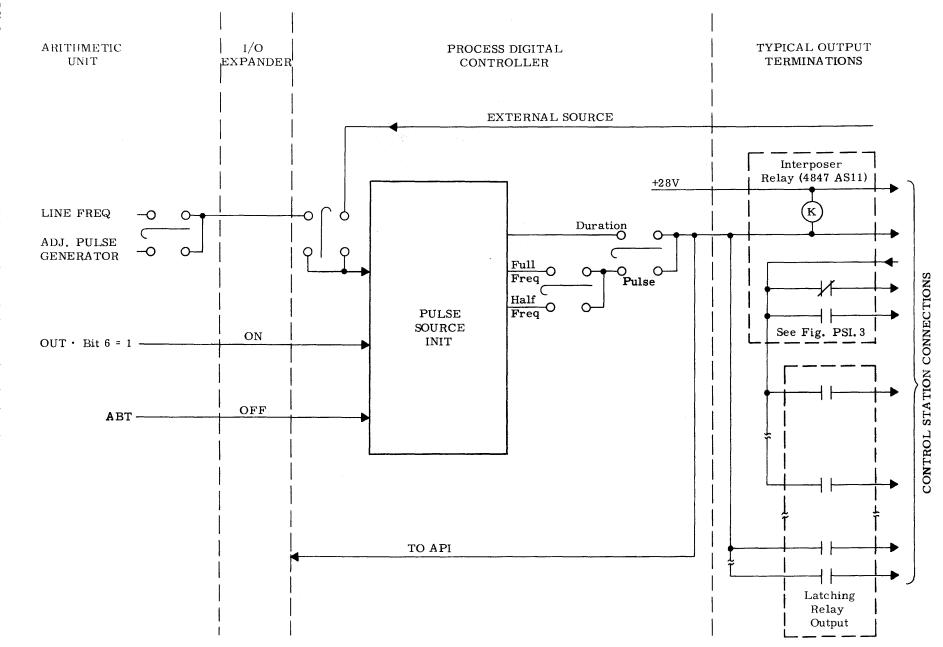

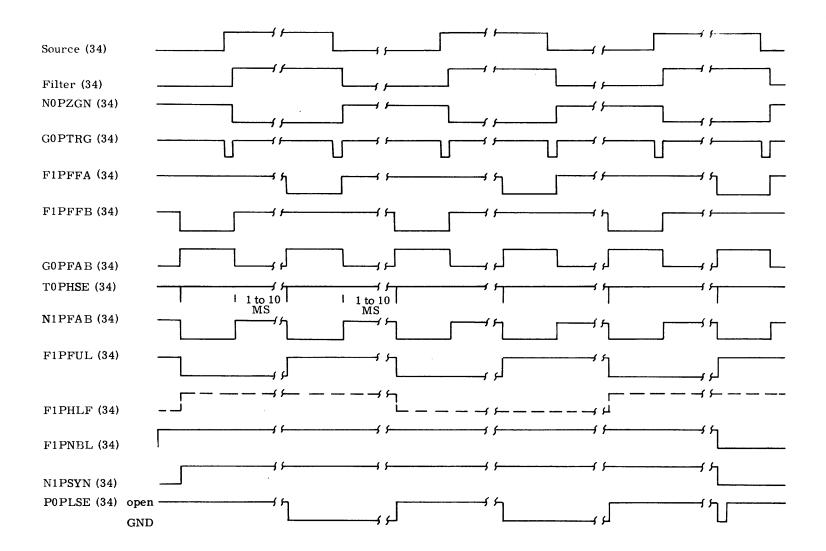

As shown in Fig. PSI.1 the output from the PSI may be either a square wave (pulse) or a single pulse (duration). The frequency of the square wave may be equal to the input frequency or one-half the input frequency. The input frequency may be selected from the line frequency or the adjustable pulse generator in the CSU or from an external system source. Each pulse from the PSI triggers an automatic program interrupt providing automatic program control of the duration of the output signal.

The PSI output may be applied to one or more control stations by latching relays or the output may be used to control an interposing relay (4847AS11 as shown in Fig. PSI.3) to interrupt an AC wavetrain or DC pulse train at the PSI output rate. The PSI output, AC wavetrain or DC pulse train may be directed to one or more control stations by digital output latching relays in the termination cabinet.

Program control of the Pulse Source Initiator normally occurs in the following manner:

- A memory location is loaded with the count, minus one, of the desired number of pulses to be outputted. This location will be decremented by an API generated from each output pulse. When the memory location is decremented from 0 to -1, a non-inhibitable ECHO API is generated which results in an ABT command being executed to disable the pulse source initiator.

- An OUT command addressed to the PDC initiates a normal digital output operation. It performs the normal fault checks and if no faults exist closes the addressed relay(s). With bit 6 of the OUT command a "one" the PSI output operation (pulses) is initiated.

The fall of each output generates an API which contains a DMT command of the memory location loaded in step 1 above.

3. The PSI continues to output pulses until the DMT ECHO occurs signifying that the desired number of output pulses have occurred. This ECHO generates another API which contains an ABT command to deactivate the PSI. The ECHO generates another interrupt which may be used to branch to a subroutine that updates the DMT memory location and data/control word, and initiates the next operation.

#### SEQUENCING AND CONTROL

Executing an OUT command with bit 6 of the control/data word a "one" operates the same as any other digital output operation, as previously described, until the PDC goes ready. That is, executing the OUT command cycles the PDC to not ready, performs the fault check, and if no fault exists, sets the relays to the configuration specified by the data/control word. The output relays associated with the pulse source initiator outputs are normally latching relays.

As shown in Fig. DOUT. 3, the PDC again goes ready, and bit 6 equal to a "one" sets the Pulse Source Initiator Enable flip-flop, F1PNBL. When set, F1PNBL enables the output from the pulse source initiator. Clearing F1PNBL disables the pulse source initiator inhibiting the pulse output. F1PNBL may be cleared by executing an ABT command, the deadman timer timing out, or by manually initializing the system. The deadman timer is used to abort PSI operations if it is enabled for a time longer than the pin selected time interval of 1, 2, or 3 seconds. The ABT command with K1 = 1 only de-activates the PSI while an ABT command with K1 = 0 initializes the entire PDC.

F1PNBL = G0SEND · N0OB06

F1PNBL = G0ACPE + D0AZRO + T0PDMN

GOACPE = ABT with K1 = 1

D0AZRO = Initialize + ABT with K1 = 0

TOPDMN = F1PNBL plus a pin selectable 1, 2, or 3 second delay.

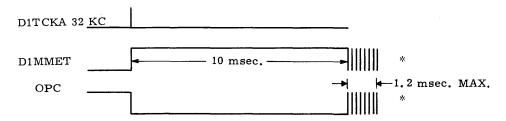

Fig. PSI. 2 illustrates the basic timing of the pulse source initiator. The frequency of the source input is selectable by pin option. As previously mentioned it may be at the power input frequency (50 or 60 Hz), from the adjustable pulse generator option (200 to 2000 Hz), or from an external source. The output from the pulse source initiator may be equal to or one-half the input frequency, or the output may be enabled (duration) until turned off. The pulse output may be phase adjusted (TOPHSE) from 1 to 10 milliseconds by a trimpot.

<sup>\*</sup> Registered Trademark of General Electric Company

Fig. PSI. 1 Pulse Source Initiator, Block Diagram

Fig. PSI. 2 Pulse Source Initiator Timing

NOTE: Position of pins for R/C suppression and contact form determined by requisition engineer. More than one pin can be used in black and green pin jacks to provide added combinations of R/C suppression. (PWB supplied with pins in all resistor and capacitor positions.)

Fig. PSI. 3 Pulse Source Interposer (4847AS11)

# **TEST MODE**

Hardware is included in the PDC to permit off-line testing using a software test program. In the test mode, the relay group drivers, data switches, and fault detectors may be tested using an off-line program.

The following paragraphs describe the operation of the hardware when the test mode commands are executed.

#### **SEL - SELECT**

The Process Digital Controller is placed off-line and in the test mode by executing an SEL (S bits = 0) command with K1 = 1, while the PDC is "ready". While in the off-line test mode, no relays can be energized (unless a hardware fault exists).

Executing an SEL command with K1 = 1 sets the Test Mode flip-flop, F1TEST (sh. 32). F1TEST is reset, removing the PDC from the Test Mode by executing an SEL command with K1 = 0 when the PDC is ready, an ABT command with K1 = 0, or by pressing the ON/INIT switch to initialize the system.

F1TEST = G0TSTF

GOTSTF = K1 = 1.SEL command. "Ready"

F1TEST = G0TCTF + D0AZRO

GOTCTF = K1 = 1. SEL command . "Ready"

D0AZRO = ABT with K1 = 0 + Initialize

The status of the Test Mode flip-flop is displayed by a white indicator on the IDOA5 board slot A09-FK.

A normal OUT command executed with K1 = 0 is ignored when the PDC is in the Test Mode. The OUT with K1 = 0 command is disabled in G1AS04 (sheet 14) by disabling G0AES4.

$$\overline{\text{G0AES4}} = \text{TEST} \cdot \text{C110} + \overline{\text{TEST}} \cdot \overline{\text{CK10}}$$

While in the Test Mode, the program may make several tests by executing OUT commands with the K1 bits encoded to specify the test operation. The following paragraphs describe these tests.

#### OUT - K1-KO = 20

Executing this instruction in the test mode will cause a fault indication if any group driver is on or if less than 17 data switches are on. The group drivers are disabled by the OUT20 instruction and the data switches are controlled by bits 8 thru 23 of the data/control word contained in the A Register. Therefore, if A Register bits 8 thru 23 are all "ones" and there are no shorted group devices, no fault indication should occur. If bits 23 thru 18 of the A Register are not all "ones", a fault indication should occur following the execution of this instruction.

The OUT20 instruction disables all group drivers by enabling G0CNON (sheet 17). Enabling G0CNON enables G1CB00 (sheet 24) and disables G0GB00 (sheet 25). Enabling G1CB00 indicates address bit 0 = 1 which disables all even numbered group drivers (e.g., P0GD00, 2, 4, 6...). Disabling G0GB00 indicates that address bit 0 is a "zero" which disables all odd numbered group drivers (e.g., P0GD01, 3, 5, ...).

$GOCNON = \overline{CK14} \cdot TEST$

G1CB00 = CNON

$\overline{G0GB00}$  = CNON

P0GD00, 2, 4, ... = CB00

$\overline{P0GD01, 3, 5}, \dots = \overline{GB00}$

To Verify No Group Drivers On gate, N1C0GD (sheet 17), is enabled which samples the output of detector Y1EGD0 (sheet 31) to determine if a fault exists. Since the group drivers are disabled by G0CNON, no fault should exist. Fig. DOUT. 7 illustrates the operation of Y1EG00.

$$N1C0GD = CTED \cdot \overline{CK14}$$

The Verify 17 Data Switches On gate, G1CADS (sheet 17), is enabled which samples the output of detector Y1ENAL (sheet 31) to determine if all 17 data switches are on. As previously described, if bits 8 thru 23 of the A Register are all "ones", they should all be "on" and no fault should be detected. If, however, OUT20 was executed with one or more "zeros" in bits 8 thru 23 of the data/control word, a fault should occur. Fig. DOUT. 7 illustrates the operation of Y1ENAL.

G1CADS = CADT

GOCADT = C2+6 · CDEL · CK14 · TEST

#### OUT - K1·KO = 30

Executing this instruction in the test mode will cause a fault indication if any group drivers are "on" or if any data switches are "on". The group drivers are disabled by the OUT30 instruction in the same manner as the OUT20 instruction. The data switches are controlled by bits 8 thru 23 of the data/control word in the A Register. Therefore, if the A Register contains all "zeros", no output fault should occur. If, however, A Register bits 8 thru 23 contain one or more "ones", a fault indication should occur.

The OUT30 instruction disables all group drivers by enabling G0CNON (sheet 17). Enabling G0CNON enables B1CB00 (sheet 24) and disables G0GB00 (sheet 25). Enabling G1CB00 indicates address bit 0 is a "one" which disables all even numbered group drivers (e.g. P0GD00, 2, 4, 6...). Disabling G0GB00 indicates that address bit 0 is a "zero" which disables all odd numbered group drivers (e.g. P0GD01, 3, 5...).

$GOCNON = \overline{CK14} \cdot TEST$

G1CB00 = CNON

$\overline{G0GB00}$  = CNON

$\overline{P0GD00, 2, 4}, \dots = CB00$

$\overline{P0GD01, 3, 5}, \dots = \overline{GB00}$

The Verify No Group Drivers On gate, N1C0GD (sheet 17), is enabled which samples the output of detector Y1EGD0 (sheet 31) to determine if a fault exists. Since the group drivers are disabled by G0CNON, no fault should exist. Fig. DOUT. 7 illustrates the operation of Y1EG00.

$N1C0GD = CTED \cdot \overline{CK14}$

The Verify No Data Switches On gate, G1C0DS (sheet 17), is enabled which samples the output of detector Y1EDSO (sheet 31) to determine if all data switches are off. As previously described, if bits 8 thru 23 in the A Register are all "zeros" no fault should occur. If one or more of these bits are "one", a fault should occur. Fig. DOUT. 7 illustrates the operation of V1EDSO.

G1C0DS = CTED  $\cdot$   $\overline{C2+6}$

The Clear Data Switch drivers (P1DCLL, M) are disabled by N0CK11 (sheet 17).

OUT - K1·KO = 40

Executing this instruction in the test mode should cause a fault indication. Two group drivers are forced "on" and the output of the more than one group driver detector (Y1EOT1) is checked for the error indication. The OUT40 instruction disables all data switches and checks the output of the Data Switch Short Check detector (Y1EDSO) indicating a fault of any data switches are on.

The Disable Data Switches gate, G1CDDS (sheet 17), is enabled disabling all output data switches (P1D23L - 00L, P1D23M-00M). The Verify No Data Switches On gate, G1C0DS (sheet 17) is enabled which samples the output of a detector (Y1EDSO) to determine if any data switches are on. Fig. DOUT.7 illustrates the operation of Y1EDSO.

G1CDDS = CK14

$G1C0DS = CK14 \cdot CTED$

The Force Two Group Drivers gate, G0CTWO (sheet 17), is enabled forcing two group drivers on by disabling D0GB00 and enabling D1GB00. The Verify Only One Group Driver on gate, G1C1GD is enabled to check the output of the One and Only One Group Driver On detector (Y1EOT1) which should provide an output fault. Fig. DOUT.7 illustrates the operation of Y1EOT1.

G0CTWO =  $CK14 \cdot \overline{CK12} \cdot TEST \cdot \overline{CK11}$

G1C1GD = CK14·CTED

#### OUT - $K1 \cdot KO = 50$

Executing this instruction should cause a fault indication. All group drivers are disabled and the output of the One and Only One Group Drive On detector (Y1EOT1) is sampled which should provide the fault indication. Executing OUT50 also disables all data switches and samples the output of the Data Switch Short Check detector (Y1EDSO) providing a fault indication if any data switches are on.

The OUT50 instruction disables all group drivers by enabling G0CNON (sheet 17). Enabling G0CNON enables G1CB00 (sheet 24) and disables G0GB00 (sheet 25). Enabling G1CB00 indicates address bit 0 = 1 which disables all even numbered group drivers (e.g. P0GD00, 2, 4, 6...). Disabling G0GB00 indicates that address bit 0 is a "zero" which disables all odd numbered group drivers (e.g. P0GD01, 3, 5...).

GOCNON = CK14. TEST

G1CB00 = CNON

$\overline{G0GB00}$  = CNON

$P0GD00, 2, 4, \dots = CB00$

$\overline{P0GD01, 3, 5}, \ldots = \overline{GB00}$

The Verify Only One Group Driver On gate, G1C1GD (sheet 17) is enabled to sample the output of the One and Only One Group Driver On detector (Y1EOT1) which should provide an output fault indication since no group drivers are on. Fig. DOUT.7 illustrates the operation Y1EOT1.

G1C1GD = CK14. CTED

The Disable Data Switches gate, G1CDDS (sheet 17), is enabled disabling all output data switches (P1D23L-00L, P1D23M-00M). The Verify No Data Switches On gate, G1C0DS (sheet 17) is enabled which samples the output of a detector (Y1EDSO) to determine if any data switches are on. Fig. DOUT. 7 illustrates the operation of Y1EDSO.

G1CDDS = CK14

$G1C0DS = DK14 \cdot CTED$

OUT - K1-KO = 60

Executing this instruction in the test mode should not cause an output fault. All data switches are disabled and the Verify No Data Switches On detector (Y1EDSO) output is monitored. Operation of the Group Drivers is controlled by the address bits (0 thru 4) of the control/data word in the A Register. The output of the One and Only One Group Driver On detector (Y1EOT1) is sampled to determine if only one is enabled. By selecting address bit configurations, an individual faulty group driver may be found and identified.

The Verify Only One Group Driver On gate, G1C1GD is enabled to sample the output of the One and Only One Group Driver On detector (Y1EOT1). Since the

address should enable one group driver no fault should be detected. Fig. DOUT.7 illustrates the operation of Y1EOT1.

G1C1GD = CK14·CTED

The Disable Data Switches gate, G1CDDS (sheet 17), is enabled disabling all output data switches (P1D23L - 00L, P1D23M-00M). The Verify No Data Switches On gate, G1C0DS (sheet 17) is enabled which samples the output of a detector (Y1EDSO) to determine if any data switches are on. Fig. DOUT.7 illustrates the operation of Y1EDSO.

G1CDDS = CK14 G1C0DS = CK14·CTED

#### IN

An IN command addressed to the PDC, when in the test mode, loads the A Register with the contents of the PDC Output Buffer Register. IN is normally executed following an OUT60 command. This should load the A Register with the same value as it contained prior to execution of OUT60. If not, either the data path between the AU and the PDC is faulty or the Output Buffer Register is faulty.

Executing an IN command in the test mode enables D0INOB (sheet 7). Enabling D0INOB enables the contents of the Output Buffer Register (F10B23-00) thru the Test Output Buffer Gates (G1TB23-00, sheet 12) to the Arithmetic Unit in the same manner as the data from a normal digital input operation.

#### **TEST INDICATORS**

The following indicators are provided in the process digital controller as an aid in testing and isolating component failures. These indicators are located on the edge of the printed wiring boards listed.

- READY This green indicator located on the IDOA5 board in slot A09-FK indicates the status of the ready line used for digital output JNR monitoring and for API generation. It is shown on sheet 14 of the PDC logic.

- FAULT This red indicator located on the IDOA5 board in slot A09-FK is lighted when the PDC detects a fault whether it is operating in the test mode or in the normal digital output mode. It is shown on sheet 14 of the PDC logic.

- TEST MODE This white indicator located on the IDOA5 board in slot A09-FK is lighted following the execution of an SEL 10 command which places the PDC in the off-line or test mode. The light is extinguished following the execution of a SEL 00 or, an ABT 00 command, or when the ON/INIT switch is pressed to initialize the system. It is shown on sheet 32 of the PDC logic.

- GROUP DRIVERS ENABLED This indicator located on the ISSB5 board in slot A08-FK is lighted whenever the output group drivers are enabled. It is shown on sheet 32 of the PDC logic.

- DATA SWITCHES ENABLED This indicator located (top) on the ISSB5 board in slot A08-FK is lighted whenever the output data switches are enabled. It is shown on sheet 32 of the PDC logic.

- OUTPUT BUFFER REGISTER The IDDA/C1 display printed wiring board, used for various test purposes, may be inserted in slot A11-AK to display the status of the PDC Output Buffer Register. The logic is shown on sheet 33 of the PDC logic.

#### **READER COMMENTS**

The General Electric Company solicits your comments on publications covering Process Computer equipment. Please explain any "no" responses in the COMMENTS section. Your comments and suggestions become the property of the General Electric Company.

| How   | is t  | his publication used:                      |                |               |       |

|-------|-------|--------------------------------------------|----------------|---------------|-------|

|       | Fan   | niliarization Refer                        | ence           |               |       |

|       | Tra   | ining Maint                                | tenance        |               |       |

|       | Oth   | er (Explain)                               |                |               |       |

| Doe   | s thi | s publication meet your requirements       | YES            |               | NO    |

| Is th | ie m  | aterial:                                   |                |               |       |

|       | 1)    | Presented in clear text                    |                |               |       |

|       | 2)    | Conveniently organized                     |                |               |       |

|       | 3)    | Adequately detailed                        |                |               |       |

|       | 4)    | Adequately illustrated                     |                |               |       |

|       | 5)    | Presented at appropriate technical level   |                |               |       |

| Plea  | ıse p | provide specific text references (page num | nber, line, et | c.) with your | comme |

|       |       | DATE                                       | ē              |               |       |

|       |       |                                            |                |               |       |

**COMMENTS:**

Cut Along Line

Communications concerning Technical Publications should be directed to:

Manager, Technical Publications

Utility and Process Automation Systems Operation

2255 West Desert Cove Road

Phoenix, Arizona 85029

Fold

Fold

Fold

FIRST CLASS Permit No. 4091 Phoenix, Arizona

#### **BUSINESS REPLY MAIL**

NO POSTAGE NECESSARY IF MAILED IN THE UNITED STATES

POSTAGE WILL BE PAID BY ...

GENERAL ELECTRIC COMPANY

UTILITY and PROCESS AUTOMATION

SYSTEMS OPERATION

2255 West Desert Cove Road

Phoenix, Arizona 85029

**Attention: Technical Publications**

Fold

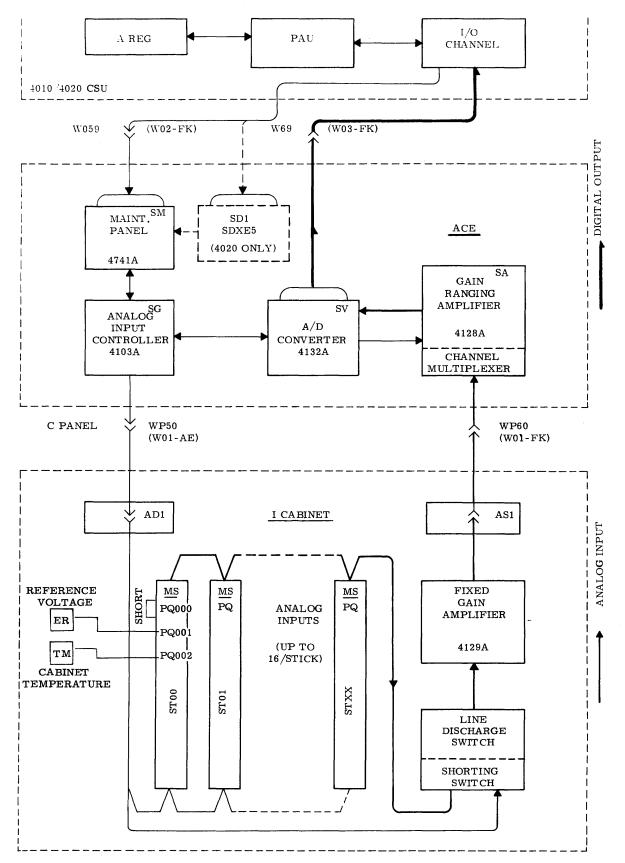

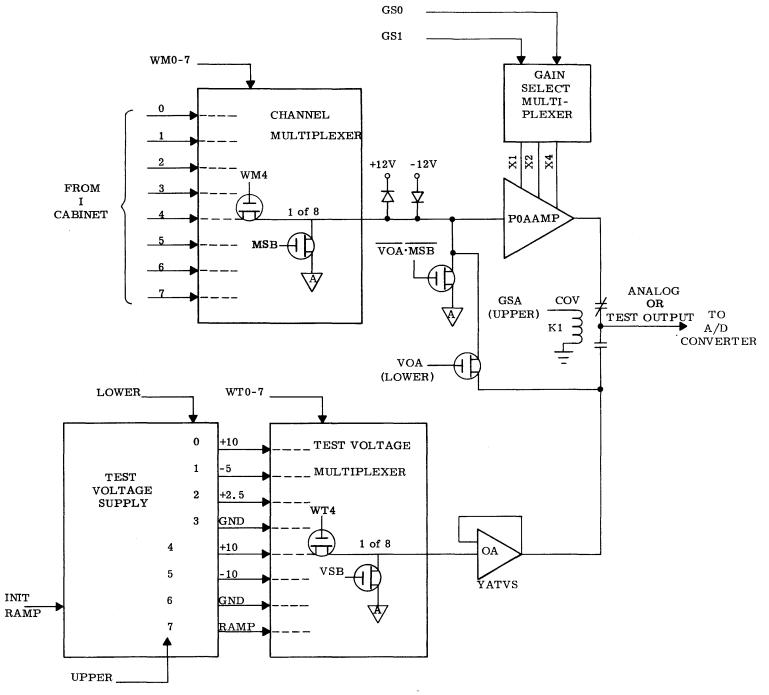

# 1100 A/B ANALOG INPUT SUBSYSTEM

# **TABLE OF CONTENTS**

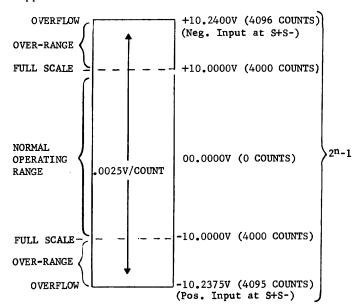

| INTRODUCTION                                 | INT - 1     |

|----------------------------------------------|-------------|

| SPECIFICATION SUMMARY                        | INT - 1     |

| GENERAL DESCRIPTION                          | GEN DESC-1  |

| ANALOG COMMON ELECTRONICS (ACE)              | GEN DESC-1  |

| Controller                                   | GEN DESC-1  |

| Gain Ranging Amplifier (GRA)                 | GEN DESC-1  |

| Analog/Digital Converter (ADC)               | GEN DESC-1  |

| Maintenance Panel                            | GEN DESC-5  |

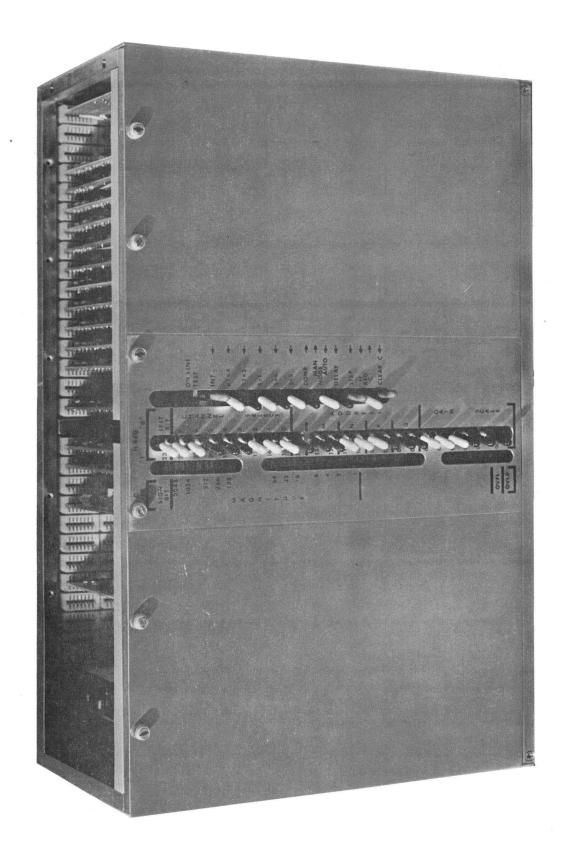

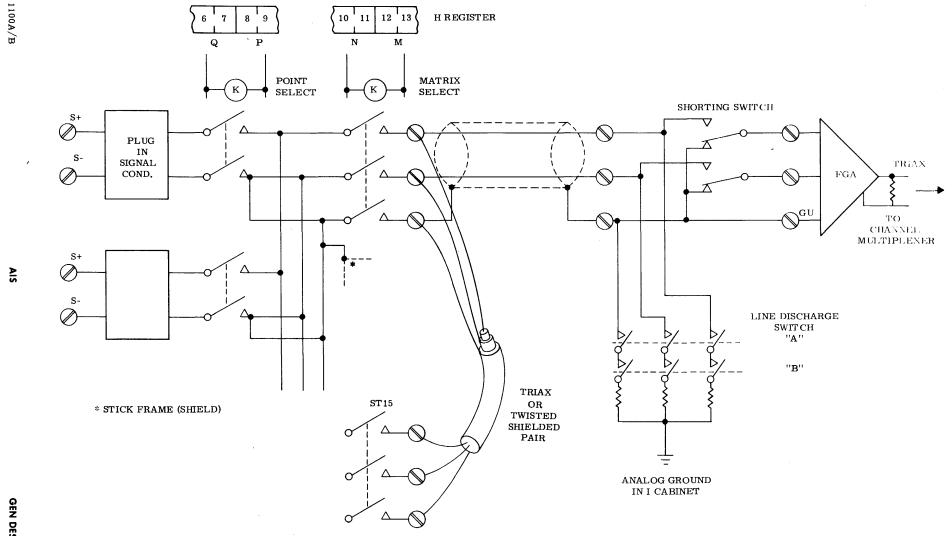

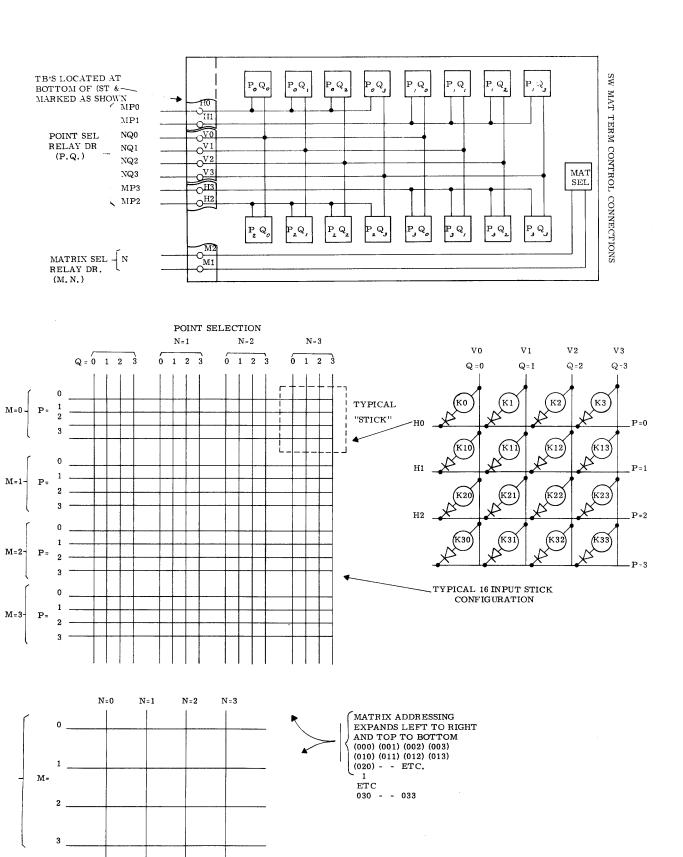

| ANALOG INPUT TERMINATION CABINET (I CABINET) | GEN DESC-8  |

| Relay Multiplexer                            | GEN DESC-8  |