# QD32 DISK CONTROLLER TECHNICAL MANUAL (MSCP COMPATIBLE)

3545 Harbor Boulevard Costa Mesa, California 92626 (714) 662-5600 TWX 910-595-2521

#### WARNING

This equipment generates, uses and can radiate radio frequency energy, and if not installed and used in accordance with the technical manual, may cause interference to radio communications. It has been tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of Federal Communications Commission (FCC) Rules, which are designed to provide reasonable protection against such interference when operating in a commercial environment. Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

Copyright (C) 1985 Emulex Corporation

The information in this manual is for information purposes and is subject to change without notice.

Emulex Corporation assumes no responsibility for any errors which may appear in the manual.

Printed in U.S.A.

| Section                                                                                                                         | Title                                                                                                                                                                                                                                                                                                                                                                                                              | Page                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| ONE GEN                                                                                                                         | MERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                  | ٠                                                                                  |

| 1.1<br>1.2<br>1.2.1<br>1.3<br>1.4<br>1.4.1<br>1.5.1<br>1.5.2<br>1.5.3<br>1.5.4<br>1.5.5<br>1.5.5                                | INTRODUCTION SUBSYSTEM OVERVIEW MASS STORAGE CONTROL PROTOCOL (MSCP) PHYSICAL ORGANIZATION OVERVIEW SUBSYSTEM MODELS and OPTIONS SUBSYSTEM OPTIONS FEATURES MICROPROCESSOR DESIGN CONFIGURATION FLEXIBILITY SELF-TEST ERROR CONTROL SEEK OPTIMIZATION COMMAND BUFFER ADAPTIVE DMA BLOCK-MODE DMA TWENTY-TWO-BIT ADDRESSING                                                                                         | 1-1<br>1-2<br>1-2<br>1-3<br>1-4<br>1-6<br>1-6<br>1-7<br>1-7<br>1-7                 |

| 1.6<br>1.6.1<br>1.6.2<br>1.6.3                                                                                                  | COMPATIBILITY DIAGNOSTICS OPERATING SYSTEMS HARDWARE COMPATIBILITY  WTROLLER SPECIFICATION                                                                                                                                                                                                                                                                                                                         | 1-8<br>1-8<br>1-8                                                                  |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5                                                                                                 | OVERVIEW  GENERAL SPECIFICATION  ENVIRONMENTAL SPECIFICATION  PHYSICAL SPECIFICATION  ELECTRICAL SPECIFICATION                                                                                                                                                                                                                                                                                                     | 2-1<br>2-1<br>2-3<br>2-3<br>2-4                                                    |

| THREE                                                                                                                           | PLANNING THE INSTALLATION                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                    |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.3<br>3.4<br>3.4.1<br>3.4.2<br>3.4.2.1<br>3.4.2.2<br>3.5<br>3.5.1<br>3.5.2<br>3.5.2.1 | OVERVIEW  MSCP SUBSYSTEM CONFIGURATION  ARCHITECTURE  PERIPHERAL NUMBERING  PERIPHERAL CAPACITIES  A DEC MSCP SUBSYSTEM  THE QD32 MSCP SUBSYSTEM  LOGICAL UNIT NUMBERS  QD32 MSCP SUBSYSTEM LOGICAL CONFIGURATION  Logical Devices  Device Numbers  OPERATING SYSTEMS, DEVICE AND VECTOR ADDRESSES  RSTS/E OPERATING SYSTEMS (V8.0)  RT-11 OPERATING SYSTEMS (V5.1 and above)  Installing a Single MSCP Controller | 3-1<br>3-2<br>3-2<br>3-3<br>3-3<br>3-4<br>3-4<br>3-4<br>3-6<br>3-7<br>3-10<br>3-10 |

| 3.5.2.2<br>3.5.2.3                                                                                                              | Installing Multiple MSCP Controllers Disk Partitioning                                                                                                                                                                                                                                                                                                                                                             | 3-12                                                                               |

| Section                                                                                  | Title                                                                                                                                                                                                                                                          | Page                                                        |

|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| 3.5.3<br>3.5.3.1<br>3.5.3.2<br>3.5.4<br>3.5.4.1<br>3.5.4.2<br>3.5.5                      | RSX-llm OPERATING SYSTEMS (V4.0 and above)                                                                                                                                                                                                                     | 3-14<br>3-14<br>3-17<br>3-18<br>3-16<br>3-21                |

| FOUR IN                                                                                  | NSTALLATION                                                                                                                                                                                                                                                    |                                                             |

| 4.1.1<br>4.1.2<br>4.1.3<br>4.2<br>4.2.1<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.3.1<br>4.3.3.2 | OVERVIEW SUBSYSTEM CONFIGURATIONS DIP SWITCH TYPES MAINTAINING FCC CLASS A COMPLIANCE INSPECTION QD32 DISK CONTROLLER INSPECTION DISK CONTROLLER SETUP DISK CONTROLLER BUS ADDRESS INTERRUPT VECTOR ADDRESS OPTIONS Automatic Bootstrapping MSCP Device Number | 4-1<br>4-3<br>4-3<br>4-4<br>4-4<br>4-7<br>4-7<br>4-8<br>4-8 |

| 4.3.3.2.<br>4.3.3.2.                                                                     | Logical Unit to Autoboot From                                                                                                                                                                                                                                  | 4-9<br>4-9                                                  |

| 4.3.3.3<br>4.3.3.4<br>4.3.3.5<br>4.4                                                     | Alternate Address                                                                                                                                                                                                                                              | 4-10<br>4-11<br>4-11<br>4-12                                |

| 4.4.1<br>4.4.2<br>4.4.3<br>4.5                                                           | SYSTEM PREPARATION                                                                                                                                                                                                                                             | 4-12<br>4-12<br>4-13<br>4-13                                |

| 4.5.1<br>4.5.2<br>4.5.3<br>4.5.4<br>4.5.5                                                | DRIVE PLACEMENT                                                                                                                                                                                                                                                | 4-13<br>4-13<br>4-14<br>4-14                                |

| 4.6<br>4.6.1<br>4.6.1.1<br>4.6.1.2                                                       | CABLING                                                                                                                                                                                                                                                        | 4-14<br>4-16<br>4-17<br>4-17<br>4-18                        |

| 4.6.1.3<br>4.6.2<br>4.7<br>4.7.1<br>4.7.2<br>4.7.3                                       | Grounding  SEPARATE CABINETS  INTEGRATION AND OPERATION  DRIVE FORMATTING  TESTING  OPERATION                                                                                                                                                                  | 4-18<br>4-26<br>4-26<br>4-26<br>4-27                        |

| 4.7.3.1                                                                                  | Indicators                                                                                                                                                                                                                                                     | 4-27                                                        |

| Section                                                                                                  | Title                                                                                                                                                                                                                                                          |                                                                      |  |

|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--|

| FIVE T                                                                                                   | ROUBLESHOOTING                                                                                                                                                                                                                                                 |                                                                      |  |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5                                                                          | OVERVIEW  SERVICE  FAULT ISOLATION PROCEDURE  POWER-UP SELF-DIAGNOSTIC  FATAL ERROR CODES.                                                                                                                                                                     | 5-1<br>5-2<br>5-5<br>5-6                                             |  |

| SIX REC                                                                                                  | GISTERS AND PROGRAMMING                                                                                                                                                                                                                                        |                                                                      |  |

| 6.1<br>6.2<br>6.3<br>6.3.1<br>6.3.2<br>6.3.2.1<br>6.3.2.2<br>6.4<br>6.5<br>6.5.1<br>6.5.2<br>6.6         | OVERVIEW OVERVIEW OF MSCP SUBSYSTEM PROGRAMMING EXPANDED COMMANDS UNSUPPORTED COMMANDS Minimal Disk Subset Diagnostic and Utility Protocol (DUP) REGISTERS NOVRAM COMMANDS DRIVE GEOMETRY PARAMETERS LOADING THE NOVRAM BOOTSTRAP COMMAND FORMAT DRIVE COMMAND | 6-1<br>6-2<br>6-2<br>6-3<br>6-3<br>6-3<br>6-5<br>6-1<br>6-13<br>6-13 |  |

| SEVEN I                                                                                                  | FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                         |                                                                      |  |

| 7.1<br>7.2                                                                                               | OVERVIEW QD32 DISK CONTROLLER ARCHITECTURE                                                                                                                                                                                                                     | 7-1<br>7-1                                                           |  |

|                                                                                                          | INTERFACES                                                                                                                                                                                                                                                     |                                                                      |  |

| 8.1<br>8.2<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.3<br>8.3.1<br>8.3.1.1<br>8.3.1.2<br>8.3.1.3<br>8.3.2 | OVERVIEW LSI-11 BUS INTERFACE INTERRUPT PRIORITY LEVEL REGISTER ADDRESS DMA OPERATIONS SCATTER/GATHER QD32 SMD DISK DRIVE INTERFACE I/O CABLES A Cable B Cable Drivers and Receivers I/O SIGNAL PROCESSING Tag/Bus Signals Discrete Signals                    | 8-1<br>8-3<br>8-3<br>8-3<br>8-3<br>8-4<br>8-4<br>8-4<br>8-6<br>8-6   |  |

| Section Title     |                                                                                | Page               |

|-------------------|--------------------------------------------------------------------------------|--------------------|

| APPENDI           | CES                                                                            |                    |

| A                 | AUTOCONFIGURE, CSR, AND VECTOR ADDRESSES                                       |                    |

| A.1               | OVERVIEW                                                                       | A-1                |

| A.2               | AUTOCONFIGURE                                                                  | A-1                |

| A.3               | DETERMINING THE VECTOR ADDRESS FOR USE WITH AUTOCONFIGURE                      | A-3                |

| A.4               | A SYSTEM CONFIGURATION EXAMPLE                                                 | A-6                |

| В                 | PROM REMOVAL AND REPLACEMENT                                                   |                    |

| B.1<br>B.2        | OVERVIEW EXCHANGING PROMS                                                      | B-1<br>B-1         |

| C                 | UTILITIES AND SOFTWARE                                                         |                    |

| c.1               | OVERVIEW                                                                       | C-1                |

| D                 | DISK DRIVE CONFIGURATION PARAMETERS                                            |                    |

| D.1<br>D.2<br>D.3 | OVERVIEW CONFIGURATION TABLES SPECIAL CONSIDERATIONS FOR LARGE CAPACITY DRIVES | D-1<br>D-1<br>D-12 |

# LIST OF FIGURES

| Figure                                                                                                                                          | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Page                                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

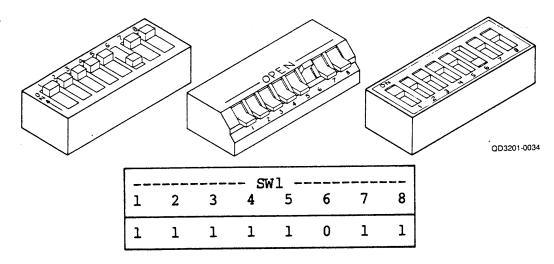

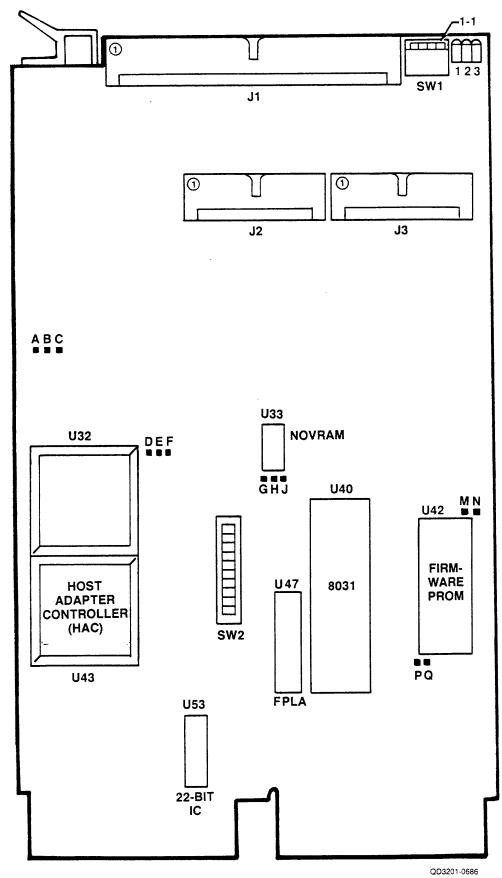

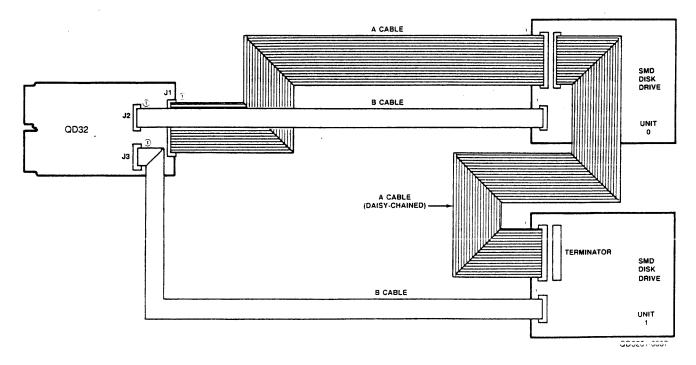

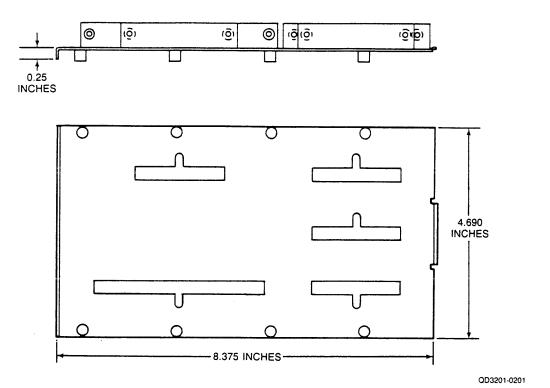

| 1-1<br>1-2<br>1-3<br>2-1<br>3-1<br>3-2<br>3-3<br>3-4<br>4-1<br>4-2<br>4-3<br>4-4<br>4-5<br>4-6<br>4-7<br>4-8<br>5-1<br>6-1<br>6-2<br>7-1        | QD32 Subsystem Configuration.  QD32 Disk Controller Sales Order Example QD32 Disk Controller Dimensions DEC MSCP Subsystem Logical and Physical Configuration. QD32 Subsystem Logical and Physical Configuration. Sample SHOW CONFIGURATION.  CONFIGURE Command Listing QD32 Configuration Reference Sheet Switch Setting Example QD32 Disk Controller Assembly. Drive Cabling Cable I/O Adapter Panel Rack-Mount Panel Rack-Mount Drive Cabling Configuration. Freestanding Drive Cabling Configuration Fault Isolation Chart Drive Configuration Parameter Block Worksheet Bootstrap Command Example QD32 Block Diagram | 1-3<br>1-4<br>1-5<br>2-4<br>3-2<br>3-3<br>3-21<br>3-23<br>4-2<br>4-3<br>4-14<br>4-20<br>4-22<br>4-24<br>5-3<br>6-14<br>7-2 |

|                                                                                                                                                 | LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                            |

| Table                                                                                                                                           | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Page                                                                                                                       |

| 1-1<br>1-2<br>2-1<br>2-2<br>2-3<br>2-4<br>3-1<br>3-2<br>4-1<br>4-2<br>4-3<br>4-4<br>4-5<br>4-6<br>4-7<br>5-1<br>5-2<br>5-3<br>5-4<br>6-1<br>8-2 | Dasic Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1-3<br>1-4<br>2-1<br>2-3<br>2-3<br>2-4<br>3-7<br>3-9<br>4-6<br>4-7<br>4-9<br>4-10<br>4-19<br>5-5<br>5-6<br>8-5             |

# LIST OF TABLES

| Table | Title                                                   | Page |

|-------|---------------------------------------------------------|------|

| 8-3   | A Cable Signal Line Functions                           | 8-7  |

| 8-4   | B Cable Signal Functions                                | 8-11 |

| A-1   | SYSGEN Device Table                                     | A-2  |

| A-2   | Priority Ranking for Floating Vectors Addresses         | A-4  |

| A-3   | CSR and Vector Address Example                          | A-6  |

| Ã-4   | Floating Address Computation                            | A-7  |

| C-1   | Utility and Diagnostic Software                         | C-1  |

| D-1   | CDC LMD 9457 NOVRAM Parameters                          | D-2  |

| D-2   | CDC RSD 9710 NOVRAM Parameters                          | D-3  |

| D-3   | CDC RSD 9710 Sector Setting                             | D-3  |

| D-4   | CDC 9715-515 NOVRAM Parameters                          | D-4  |

| D-5   | CDC 9715-515 Sector Setting                             | D-4  |

| D-6   | CDC 9771 XMD NOVRAM Parameters under MicroVMS           | D-5  |

| D-7   | CDC 9771 XMD Sector Setting                             | D-5  |

| D-8   | CDC 9771 XMD NOVRAM Parameters under RSX and RSTS/E     | D-6  |

| D-9   | CDC 9771 XMD Sector Setting                             | D-6  |

| D-10  | CDS 315 NOVRAM Parameters                               | D-7  |

| D-11  | CDS 315 Sector Setting                                  | D-7  |

| D-12  | Fujitsu M2351A NOVRAM Parameters                        | D-8  |

| D-13  | Fujitsu M2351A Sector Setting                           | D-8  |

| D-14  | Fujitsu M2361A NOVRAM Parameters under MicroVMS         | D-9  |

| D-15  | Fujitsu M2361A Sector Setting                           | D-9  |

| D-16  | Fujitsu M2361A NOVRAM Parameters under RSX and RSTS/E . | D-10 |

| D-17  | Fujitsu M2361A Sector Setting                           | D-10 |

| D-18  | Fujitsu M2333 NOVRAM Parameters                         | D-11 |

| D-19  | Fujitsu M2333 Sector Setting                            | D-11 |

#### EMULEX PRODUCT WARRANTY

CONTROLLER WARRANTY: Emulex warrants for a period of twelve (12) months from the date of shipment that each Emulex controller product supplied shall be free from defects in material and workmanship.

CABLE WARRANTY: All Emulex provided cables are warranted for ninety (90) days from the time of shipment.

The above warranties shall not apply to expendable components such as fuses, bulbs, and the like, nor to connectors, adaptors, and other items not a part of the basic product. Emulex shall have no obligation to make repairs or to cause replacement required through normal wear and tear or necessitated in whole or in part by catastrophe, fault or negligence of the user, improper or unauthorized use of the product, or use of the product is such a manner for which it was not designed, or by causes external to the product, such as but not limited to, power failure or air conditioning. Emulex's sole obligation hereunder shall be to repair or replace any defective product, and, unless otherwise stated, pay return transportation cost for such replacement.

Purchaser shall provide labor for removal of the defective product, shipping charges for return to Emulex and installation of its replacement. THE EXPRESSED WARRANTIES SET FORTH IN THIS AGREEMENT ARE IN LIEU OF ALL OTHER WARRANTIES, EXPRESSED OR IMPLIED, INCLUDING WITHOUT LIMITATION, ANY WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, AND ALL OTHER WARRANTIES ARE HEREBY DISCLAIMED AND EXCLUDED BY EMULEX. THE STATED EXPRESS WARRANTIES ARE IN LIEU OF ALL OBLIGATIONS OR LIABILITIES ON THE PART OF EMULEX FOR DAMAGES, INCLUDING BUT NOT LIMITED TO SPECIAL, INDIRECT, OR CONSEQUENTIAL DAMAGES ARISING OUT OF, OR IN CONNECTION WITH THE USE OR PERFORMANCE OF THE PRODUCT.

RETURNED MATERIAL: Warranty claims must be received by Emulex within the applicable warranty period. A replaced product, or part thereof, shall become the property of Emulex and shall be returned to Emulex

Purchaser's expense. All returned material must be accompanied by a RETURN MATERIALS AUTHORIZATION (RMA) number assigned by Emulex.

**BLANK**

#### 1.1 INTRODUCTION

The QD32 Disk Controller, designed and manufactured by Emulex Corporation, is a MSCP-compatible controller that interfaces with SMD disk drives. This manual is designed to help you install and use your QD32 Disk Controller. The contents of the eight sections and four appendices are described as follows:

- Section 1 General Description: This section contains an overview of the QD32 Disk Controller.

- Section 2 Controller Specification: This section contains the specification for the QD32 Disk Controller.

- Section 3 Planning the Installation: This section contains the information necessary to plan your installation, including MSCP subsystem and operating system considerations.

- Section 4 Installation: This section contains the information needed to set up and physically install the controller, including switch settings and cabling.

- Section 5 **Troubleshooting:** This section describes fault isolation procedures that can be used to pinpoint trouble spots.

- Section 6 Registers and Programming: This section describes the QD32's LSI-ll bus registers and presents an overview of the Mass Storage Control Protocol (MSCP).

- Section 7 Functional Description: This section describes the controller architecture.

- Section 8 Interfaces: This section describes the controller LSI-ll bus and SMD interfaces.

- Appendix A Autoconfigure: This appendix describes the DEC algorithm for the assignment of CSR addresses and vector addresses.

- Appendix B PROM Removal and Replacement: This appendix contains instructions to remove and replace the firmware so that the user can upgrade the QD32 Disk Controller in the field.

- Appendix C Utilities and Diagnostics: This appendix lists the utilities and diagnostics for the QD32.

- Appendix D Disk Drive Configuration Parameters: This appendix contains configuration parameters for supported SMD disk drives.

#### 1.2 SUBSYSTEM OVERVIEW

The QD32 Disk Controller connects high-capacity mass storage peripherals to the LSI-ll bus on computers manufactured by Digital Equipment Corporation (DEC). The QD32 implements DEC's Mass Storage Control Protocol (MSCP) to provide a software-transparent interface for the host DEC computer. To provide traditional Emulex flexibility in peripheral selection, the QD32 uses the industry standard SMD interface as its peripheral interface. The QD32 supports the extended cylinder addressing functions of the SMD-E (extended) interface. SMD-E and SMD-0 interfaces are electrically and logically compatible. For more information on the QD32's SMD interface, see subsection 8.3.

#### 1.2.1 MASS STORAGE CONTROL PROTOCOL (MSCP)

MSCP is a software interface designed to lower the host computer's mass storage overhead by offloading much of the work associated with file management into an intelligent mass storage subsystem. In concert with SMD compatible peripherals, the QD32 provides just such a subsystem. The QD32 relieves the host CPU of many file maintenance tasks. The QD32 Disk Controller performs these MSCP functions: error checking and correction, bad block replacement, seek optimization, command prioritizing and ordering, and data mapping.

This last feature is, perhaps, the most important. This feature allows the host computer's operating system software to store data in logical blocks that are identified by simple logical block numbers Thus, the host does not need to have detailed knowledge of the peripheral's geometry (cylinders, tracks, sectors, etc.). This feature also makes autoconfiguration a simple matter. During system start-up, the host operating system queries the subsystem to find its capacity (the number of logical blocks that the subsystem can store).

Because the host operating system does not need to have detailed knowledge of its mass storage subsystem, the complexity of the operating system itself has been reduced. This reduction comes about because only one or two software modules are required to allow many different subsystems to be connected to a host.

#### 1.3 PHYSICAL ORGANIZATION OVERVIEW

The QD32 Disk Controller is a modular, microprocessor-based disk controller that connects directly to the host computer's LSI-11 bus backplane. The microprocessor architecture ensures excellent reliability and compactness.

The QD32 is contained on a single dual-wide printed circuit board assembly (PCBA) that plugs directly into an LSI-ll bus backplane slot.

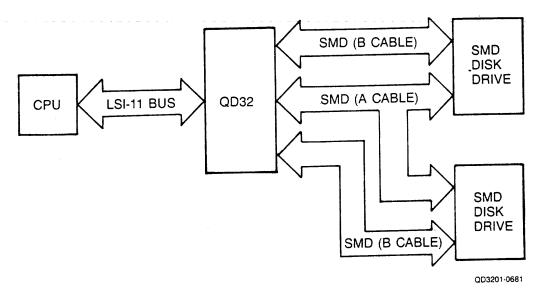

The QD32 supports up to two physical or four logical disk drives. Aggregate data storage capacities are limited only by the capacities of the peripherals. Figure 1-1 shows one possible SMD configuration.

Figure 1-1. QD32 Subsystem Configuration

# 1.4 SUBSYSTEM MODELS and OPTIONS

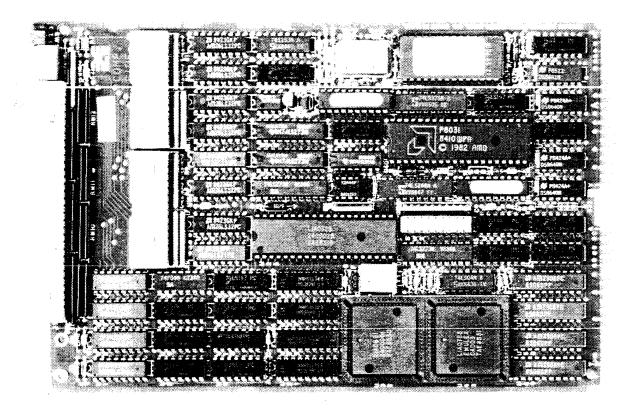

The QD32 Disk Controller, with appropriate peripherals, provides a DEC MSCP-compatible mass storage subsystem. The QD32 is pictured in Figure 1-2. The QD32 is identified by a top level assembly tag that is glued to the 8031 microprocessor chip on the PWB. The QD32 top level assembly number is given in Table 1-1 along with the part numbers of the items that are delivered with the QD32.

| Itm | Qty | Description                                   | Part Number            |

|-----|-----|-----------------------------------------------|------------------------|

| 1 2 | 1   | QD32 Disk Controller<br>22-Bit Addressing Kit | QD3210201<br>QD0113002 |

| 3   | li  | QD32 Technical Manual                         | QD3251001              |

Table 1-1. Basic Contents

QD3201-0823

Figure 1-2. QD32 Disk Controller

#### 1.4.1 SUBSYSTEM OPTIONS

Table 1-2 lists the options that can be ordered to tailor your QD32 to your particular application. Software programs are offered in distribution kits that include media and documentation.

| Table $1-2$ . QD3 | 32 Options |

|-------------------|------------|

|-------------------|------------|

| Option                                                                                                  | Description                                                                                                                                                           |

|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PX995180n-0n1                                                                                           | Includes the Emulex LSI/PDP MSCP Formatter Program (SXMX8B). Distribution kit is per customer order.                                                                  |

| VX9951804                                                                                               | Includes the Emulex MicroVAX MSCP Disk Formatter Program (FQD01M).                                                                                                    |

| QD3113003                                                                                               | QD32 Cabling Kit for MICRO/PDP-11 and MicroVAX I and II Tower. Includes cables, panels, and instructions.                                                             |

| SU7811212-0n2<br>SU7811219-0n2<br>SU7811213-0n2<br>SU7811218-0n2<br>SU1110201<br>CU2220301<br>SU7813104 | SMD A-Cable, shielded SMD A-Cable, extension SMD B-Cable, shielded SMD-B Cable, extension Cable I/O Adapter Panel Rack-Mount Panel Peripheral Cable Adapter Panel Kit |

<sup>1</sup> See Appendix C for distribution kit part numbers.

Options are specified as separate line items on a sales order. An example of an actual sales order is shown in Figure 1-3.

| Item | Qty | Model Number | Comment/Description                                                |

|------|-----|--------------|--------------------------------------------------------------------|

| 1.   | 1   | QD32         | Disk Controller implementing DEC MSCP with SMD drives.             |

| 2.   | 1   | VX9951804    | Includes the Emulex MicroVAX MSCP Disk Formatter Program (FQD01M). |

Figure 1-3. Sales Order Example

<sup>2</sup> See Table 4-7 for part numbers for specific cable lengths.

#### 1.5 FEATURES

The following features enhance the usefulness of the QD32 Disk Controller.

#### 1.5.1 MICROPROCESSOR DESIGN

The QD32 design incorporates an eight-bit, high-performance CMOS microprocessor to perform all controller functions. The microprocessor approach provides a reduced component count, high reliability, easy maintainability, and the microprogramming flexibility that allows MSCP to be implemented without expensive, dedicated hardware.

#### 1.5.2 CONFIGURATION FLEXIBILITY

The QD32 Disk Controller can support many different SMD drive configurations by using the QD32's Nonvolatile Random Access Memory (NOVRAM). The QD32's NOVRAM can be programmed for two physical drive configurations. In addition, the user can change these stored drive configurations by altering the NOVRAM using Emulex software or the QD32's extended command set. The flexibility of the QD32 configuration NOVRAM eliminates the need for special configuration PROMs and field upgrade kits.

#### 1.5.3 SELF-TEST

The QD32 incorporates an internal self-test routine which exercises all parts of the microprocessor, the on-board memory, the buffer controller, and the Host Adapter Controller (HAC). Although this test does not completely test all circuitry, successful execution indicates a very high probability that the disk controller is operational. If the QD32 fails the self-test, it leaves three lightemitting diodes (LEDs) ON and sets an error bit in the Status and Address (SA) register (base address plus two).

#### 1.5.4 ERROR CONTROL

The disk controller presents error-free media to the operating system by correcting soft errors and retrying operations without intervention by the host.

#### 1.5.5 SEEK OPTIMIZATION

The QD32 is able to pool the various seeks that need to be performed and determine the most efficient order in which to do them. This is an especially important feature in heavily loaded systems. The disk controller's ability to arrange seeks in the optimum order saves a great deal of time and makes the entire system more efficient.

#### 1.5.6 COMMAND BUFFER

The QD32 contains a buffer that is able to store 13 MSCP commands. This large buffer allows the subsystem to achieve a higher throughput and to operate at a very efficient level.

#### 1.5.7 ADAPTIVE DMA

During each DMA data transfer burst, the QD32 monitors the LSI-ll bus for other pending DMA requests and suspends its own DMA activity to permit other DMA transfers to occur. The host processor programs the DMA burst length during the MSCP initialization sequence or the QD32 defaults to 16 words per burst. In addition, the QD32 firmware design includes a switch selectable DMA burst delay to avoid data late conditions. Because of these adaptive DMA techniques, the QD32 ensures that CPU functions, including interrupt servicing, are not locked out for excessive periods of time by high-speed disk transfers.

#### 1.5.8 BLOCK-MODE DMA

The QD32 supports block-mode DMA for accessing memory. In this mode, the initial address of the data is transmitted, followed by a burst of up to 16 words of data. The memory address is automatically incremented to accommodate this burst. Block mode transfers considerably reduce the overhead associated with DMA operations.

#### 1.5.9 TWENTY-TWO-BIT ADDRESSING

The QD32 supports the 22-bit addressing capability of the extended LSI-ll bus.

#### 1.6 COMPATIBILITY

#### 1.6.1 DIAGNOSTICS

Emulex offers two diagnostic programs to support the use and maintenance of the QD32:

- Emulex PDP/LSI MSCP Formatter Program (SXMX8B)

- Emulex MicroVAX MSCP Disk Formatter Program (FQD01M)

#### 1.6.2 OPERATING SYSTEMS

The QD32 implements MSCP. Emulex supports its implementation of MSCP beginning with the indicated version of the following DEC operating systems:

| Operating<br>System | Version |

|---------------------|---------|

| Micro/VMS           | 4.0     |

| RSTS/E              | 8.0     |

| RSX-11M             | 4.1     |

| RSX-11M-PLUS        | 2.1     |

| RT-11               | 5.1     |

#### 1.6.3 HARDWARE COMPATIBILITY

The QD32 Disk Controller complies with DEC LSI-11 bus protocol, and it directly supports 22-bit addressing and block-mode DMA. The QD32 also supports scatter-write and gather-read operations on the MicroVAX I.

The disk drives supported by the QD32 are not media compatible with comparable DEC MSCP products.

The QD32 Disk Controller supports hard-sectored disk drives that use the SMD interface. The QD32 also supports the extended cylinder addressing functions of the SMD-E interface (see subsection 8.3). The QD32 supports disk transfer rates up to 2.5M byte per second. Emulex has certified the following disk drives for full support:

- Control Data Corporation (CDC) 9457 LMD

- CDC 9710-80

- CDC 9715-515

- CDC 9771 XMD

- Century Data Systems (CDS) 315

- Fujitsu M2351A

- Fujitsu M2361A

- Fujitsu M2333

#### 2.1 OVERVIEW

This section contains the general, environmental, physical, electrical, and port specifications for the QD32 Disk Controller.

| Subsection | Title                       |

|------------|-----------------------------|

| 2.2        | General Specification       |

| 2.3        | Environmental Specification |

| 2.4        | Physical Specification      |

| 2.5        | Electrical Specification    |

#### 2.2 GENERAL SPECIFICATION

Table 2-1 contains a general specification for the QD32 Disk Controller.

Table 2-1. QD32 General Specifications

| Parameter                         | Description                                                                                                            |  |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------|--|

| PUNCTION                          | Providing mass data storage to<br>Digital Equipment Corporation<br>(DEC) computers that use the<br>LSI-11 bus          |  |

| Logical CPU Interface             | Emulates DEC's Mass Storage<br>Control Protocol (MSCP)                                                                 |  |

| Diagnostic<br>Software            | Emulex PDP/LSI MSCP Disk<br>Formatter Program (SXMX8B) and<br>MicroVAX MSCP Disk Formatter<br>Program (FQD01M)         |  |

| Operating System<br>Compatibility | Micro/VMS V4.0 and above RSTE/S V8.0 and above RSX-11M V4.1 and above RSX-11M PLUS V2.1 and above RT-11 V5.1 and above |  |

(continued on next page)

# **General Specification**

Table 2-1. QD32 General Specifications (continued)

| Parameter                              | Description                                                                                                                                   |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| CPU I/O Technique                      | Direct Memory Access (DMA), including adaptive techniques and block mode; supports scatter-write and gather-read operations on the MicroVAX I |

| INTERFACE                              |                                                                                                                                               |

| CPU Interface                          | Extended LSI-ll bus interface                                                                                                                 |

| Device Base Address                    |                                                                                                                                               |

| Standard<br>Alternates                 | 177721508<br>177721548<br>177603348<br>177603408<br>177603448<br>177603508<br>177603548                                                       |

| Vector Address                         | Programmable                                                                                                                                  |

| Priority Level                         | BR4 and BR5                                                                                                                                   |

| Bus Loading                            | 1 DC Load, 2.5 AC Loads                                                                                                                       |

| Peripheral Interface                   | SMD-E (Extended) up to 20 MHz<br>SMD-0                                                                                                        |

| Disk Transfer Rate                     | Up to 2.5M bytes per second                                                                                                                   |

| Number of Physical<br>Drives Supported | 2                                                                                                                                             |

| Drive Sectoring                        | Hard Sectored                                                                                                                                 |

| Maximum Cable Lengths                  |                                                                                                                                               |

| A Cable (daisy-chain)                  | 100 ft (30 m) cumulative                                                                                                                      |

| B Cable (radial)                       | 50 ft (15 m)                                                                                                                                  |

# 2.3 ENVIRONMENTAL SPECIFICATION

Table 2-2 contains the environmental specifications for the QD32 Disk Controller.

Table 2-2. QD32 Environmental Specifications

| Parameter             | Description                                                                                                          |

|-----------------------|----------------------------------------------------------------------------------------------------------------------|

| OPERATING TEMPERATURE | 10°C (50°F) to 40°C (104°F), where maximum temperature is reduced 1.8°C per 1000 meters (1°F per 1000 feet) altitude |

| RELATIVE HUMIDITY     | 10% to 90% with a maximum wet bulb of 28°C (82°F) and a minimum dewpoint of 2°C (3.6°F)                              |

| COOLING               | 6 cubic feet per minute                                                                                              |

| HEAT DISSIPATION      | 82 BTU per hour                                                                                                      |

#### 2.4 PHYSICAL SPECIFICATION

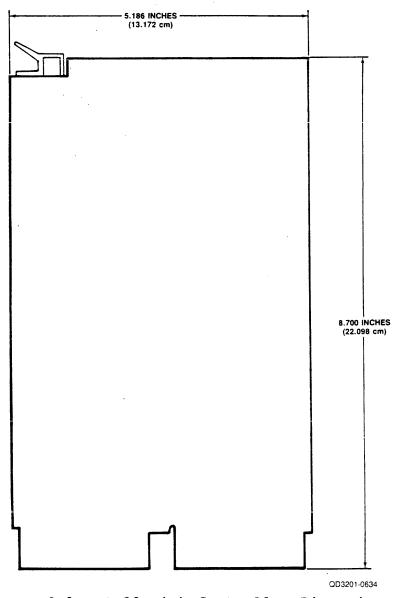

Table 2-3 contains the physical specifications for the QD32 Disk Controller.

Table 2-3. QD32 Physical Specifications

| Parameter       | Description                                                             |  |

|-----------------|-------------------------------------------------------------------------|--|

| PACKAGING       | Single, dual-wide, four-layer<br>PCBA                                   |  |

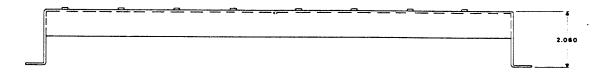

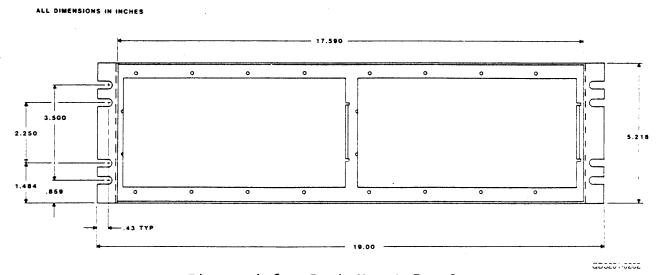

| Dimensions      | 5.186 by 8.70 inches<br>13.172 by 22.09 centimeters<br>(see Figure 2-1) |  |

| Shipping Weight | 3 pounds                                                                |  |

# 2.5 ELECTRICAL SPECIFICATION

Table 2-4 lists and describes the electrical specification for the QD32 Disk Controller.

Table 2-4. QD32 Electrical Specifications

| Parameter | Description                        |  |

|-----------|------------------------------------|--|

| POWER     | 5 VDC <u>+</u> 5%, 2.6 amperes (A) |  |

Figure 2-1. QD32 Disk Controller Dimensions

#### 3.1 OVERVIEW

This section is designed to help you plan the installation of your QD32 Disk Controller. Taking a few minutes and planning the configuration of your subsystem before beginning its installation should result in a smoother installation with less system down time. This section contains QD32 application examples and configuration procedures. The subsections are listed in the following table:

| Subsection               | Title                                                                                                                    |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------|

| 3.2<br>3.3<br>3.4<br>3.5 | MSCP Subsystem Configuration A DEC MSCP Subsystem The QD32 MSCP Subsystem Operating Systems, Device and Vector Addresses |

#### 3.2 MSCP SUBSYSTEM CONFIGURATION

The following paragraphs describe MSCP Subsystem concepts, including architecture, unit numbering, capacities, and related concepts.

#### 3.2.1 ARCHITECTURE

MSCP is a protocol designed by DEC for mass storage subsystems using Digital Storage Architecture (DSA). In a MSCP mass storage subsystem, DSA comprises three functional and physical layers:

- Host Layer. An MSCP class-driver in the host system receives requests from the operating system and then relays data and commands to the controller in MSCP message packets.

- Controller Layer. The MSCP controller communicates with both the host layer and the mass storage layer. controller transmits MSCP message packets to and from the host MSCP class-driver and performs data-handling functions for the mass storage devices. The QD32 functions as the controller layer.

- Mass Storage Layer. The mass storage peripheral devices communicate with the MSCP controller and send or receive data as specified by the MSCP controller.

MSCP defines the form of the message packets that are exchanged by the host and the MSCP controller. The QD32 implements MSCP in mass storage subsystems using SMD as the peripheral interface.

#### 3.2.2 PERIPHERAL NUMBERING

Each MSCP peripheral on the system is identified to the operating system by an MSCP device name. An MSCP device name consists of a device class identifier and a unit number. The device class is indicated by a two-letter prefix; MSCP disk devices are indicated by the prefix DU.

With the exception of MicroVMS systems, DEC operating systems require that all MSCP peripherals on a system have different MSCP device numbers, even if they are managed by separate MSCP controllers at separate LSI-ll bus device addresses. For example, under RSX-llM-PLUS, if there are three peripherals on the first MSCP controller (at 7721508), then the first peripheral on the second MSCP controller (in floating CSR address space) is numbered DU3.

#### 3.2.3 PERIPHERAL CAPACITIES

The capacity of peripherals in an MSCP subsystem is measured in logical blocks. Each logical block contains 512 bytes of data. The MSCP controller can report the capacity of a peripheral to the operating system. For example, a Fujitsu M2361A (689M byte) disk drive supported by the QD32 is able to store 1,139,136 logical blocks.

#### 3.3 A DEC MSCP SUBSYSTEM

Figure 3-1 shows the organization of a typical DEC MSCP subsystem for the LSI-11 bus. The MSCP host and controller functions (see section 3.2.1) are combined in a single piece of hardware, in this example the DEC KDA50. The KDA50 plugs directly into the LSI-11 bus and is attached to RA81 disk drives via a disk-drive-native interface.

Figure 3-1. DEC MSCP Subsystem Logical and Physical Configuration

3-2 Planning the Installation

# 3.4 THE QD32 MSCP SUBSYSTEM

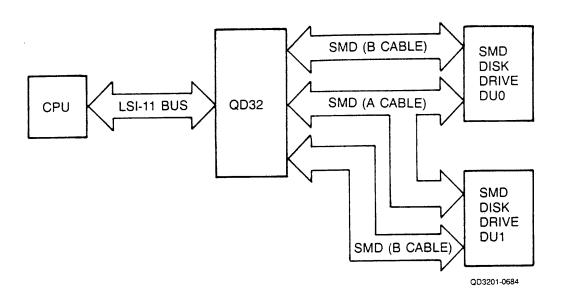

Figure 3-2 illustrates a typical QD32 MSCP subsystem. As with the DEC implementation, the QD32 is connected directly to the LSI-ll bus. However, the QD32 uses the SMD peripheral interface to communicate with one or two disk drives.

Figure 3-2. QD32 Subsystem Logical and Physical Configuration

The MSCP subsystem provided by the QD32 is essentially analogous to the DEC MSCP subsystem. As in the DEC subsystem, the QD32 MSCP controller connects directly to the LSI-11 bus and performs many of the same functions as the KDA50. As an MSCP controller, the QD32 receives requests from the host, optimizes the requests, generates SMD commands to perform the operations, transfers data to and from the host, transfers data to and from the device, and buffers data as necessary. When the command is complete, the controller sends a response to the host.

The QD32 also performs all of the functions of the peripheral controller, including serialization and deserialization of data. The QD32 connects to the peripherals it supports via the SMD interface.

# MSCP Subsystem Logical and Physical Configuration

#### 3.4.1 LOGICAL UNIT NUMBERS

As noted in subsection 3.2.2, most DEC operating systems do not allow any MSCP disk devices on one system to have the same unit number, even though they may be controlled by separate MSCP controllers at different base addresses.

DEC MSCP-type drives can accept unit identification plugs that define addresses from 0 to 255. Disk drives controlled by the QD32 do not have this flexibility; the QD32 can detect only two unique drive addresses at its SMD interface - 0 and 1. To prevent a unit-number conflict between the QD32's drives and another MSCP controller's drives, the QD32 employs switches to change the drive logical unit number that is reported to the operating system.

Example 3-1 An MSCP controller at a standard base address supports four disk drives; a QD32 at an alternate base address supports two disk drives. An offset of 4 is specified for the QD32. This causes the QD32 disk with address 0 to be reported to the operating system as logical unit number (LUN) 4. The QD32 disk 1 is reported as LUN 5.

The offset for the logical unit number is specified by using switches SW1-2 through SW1-4 on the QD32. See subsection 4.3.3.2.2 for switch setting information.

#### 3.4.2 QD32 MSCP SUBSYSTEM LOGICAL CONFIGURATION

This subsection explains the algorithm used by the QD32 to map logical MSCP peripherals onto the physical disk drives provided by the QD32 subsystem.

# 3.4.2.1 Logical Devices

The phrase "logical MSCP disk drive" refers to the disk drive as it appears to the operating system. That is, the operating system associates a disk drive of known type (in this case, an MSCP disk drive) with a unit number and a capacity. The QD32 MSCP controller presents that information to the operating system after initialization on command.

Because the MSCP controller is responsible for establishing the relationship between unit number and capacity, it is possible for the controller to divide its physical disk drives into more than one logical unit. For example, if a physical disk drive has a capacity of 1,402,832 blocks, the MSCP controller can divide that capacity into two parts of 701,416 blocks each. (Each part may have a different capacity.) Each part is then assigned a separate unit number, and the the unit number and capacity of each part is presented to the operating system.

The operating system then sees the two parts as separate disk drives, even though the data is actually stored on the same physical drive. The two parts are called logical disk drives, and the numbers that identify them are called MSCP unit numbers.

A drive configuration that supports multiple logical units is specified by the data that is stored in the configuration Nonvolatile Random Access Memory (NOVRAM). Information for programming the configuration NOVRAM is given in Section 6, Registers and The field that causes a drive to be divided into Programming. multiple logical units is called the Split Code (word 11). There are four types of split codes: no split, cylinder split, head split, and reverse head split:

- When no split is specified, the entire physical drive is one logical drive.

- Cylinder split codes divide a physical drive by cylinders. A Starting Cylinder Offset field in the NOVRAM specifies the first cylinder of the second logical drive. Alternate cylinders are divided evenly between drives. For example, a Fujitsu M2351A, which has 842 cylinders, might be divided so that Drive 0 is assigned cylinders 0 through 420 and Drive 1 assigned cylinders 421 through 842. In this example, the Starting Cylinder Offset has a value of 421.

- Head split codes divide the drive by data heads. A Starting Head Offset field in the NOVRAM specifies the first head of the second logical drive. When the drive is split by data heads, each logical drive has its own platter(s); consequently, the lower blocks of one logical drive are in the same physical cylinder as the lower blocks of the other logical drive. For example, a CDC 9457 LMD might be divided so that Drive 0 is assigned heads 0 and 1 and Drive 1 is assigned heads 2 and 3. The Starting Head Offset has a value of 2. In this example, the CDC 9457 removable media is assigned logical unit number (LUN) 0 and the fixed media assigned LUN 1.

Reverse head split codes also divide the drive by data heads, but assign the lower numbered heads to drive 1 and the higher numbered heads to drive 0. If you entered a reverse split code for the previous CDC 9457 example, Drive O is assigned heads 2 and 3 and Drive 1 is assigned heads 0 and 1. The Starting Head Offset has a value of 2. One advantage of the reverse head split codes is that you may use a fixed media unit as your system disk without modifications to the operating system.

# MSCP Subsystem Logical and Physical Configuration

The head splitting technique has a performance advantage over the cylinder method. Typically, most disk accesses are made in the lower cylinders of a disk because many system-oriented files are located there, including the drive's directory. Because the low (and high) cylinders are vertically aligned between the two logical drives when the head splitting technique is used, switching between head-split logical drives requires less head movement than switching between cylinder-split drives.

#### 3.4.2.2 Device Numbers

The drives supported by the QD32 are assigned MSCP device names by the operating system. As described in subsection 3.2.2, an MSCP device name consists of a device class prefix and a device unit number. Drives are assigned MSCP device numbers beginning with zero (0). The conventions for numbering multiple MSCP drives vary by operating system.

Under RSX-11M, RSX-11M-PLUS and RT-11, DUO is assigned to the first drive on the first MSCP controller, where "first" means the controller located at the standard base address. Unit number 1 would be the second drive on the first controller, etc. If there are two MSCP controllers on the system, the units installed on the second begin numbering at n+1, where n equals the highest unit number of the first MSCP controller.

RSTS/E requires that drives supported by a standard MSCP controller be numbered starting at 0 and drives supported by an alternate MSCP controller be numbered starting at 4.

Because MSCP device names under MicroVMS designate the supporting MSCP controller, the unit numbering is less restricted. For example, two drives which are supported by a standard MSCP controller might be DUAO and DUAL and a third drive supported by an alternate MSCP controller might be DUBO.

Table 3-1 is an MSCP unit numbering example under the RSX-11M operating system which shows the MSCP number versus the actual physical addresses assigned to all the components. The physical disk drive (unit number 0) of the second controller is split into two logical units. Note that two device names are associated with that drive.

Table 3-1. Subsystem Configuration Example

| QD32<br>Address      | Device Description        | Drive<br>Unit<br>Number | Device<br>Name |

|----------------------|---------------------------|-------------------------|----------------|

| 772150               | Fujitsu M2361A            | 0                       | DU 0           |

|                      | Fujitsu M2361A            | 1                       | DUl            |

| 760334<br>(Floating) | CDC 9457 LMD (head split) | 0                       | DU2<br>DU3     |

|                      | Fujitsu M2351A            | 1                       | DU4            |

#### NOTE

All of the MSCP peripherals supported by the QD32 use the same device identifier - RA81. Unique device identifiers are not available to the host because of the nature of the NOVRAM.

#### 3.5 OPERATING SYSTEMS, DEVICE AND VECTOR ADDRESSES

Before the installation of any peripheral device can be considered complete, the computer's operating system must be made aware of the new resource. The information provided in this section is intended to supplement your DEC operating system resources and to be used as an aid in planning the installation of your QD32.

An operating system can be made aware of a new resource in three ways:

- The operating system can poll the computer's I/O device address space.

- The device can be manually connected using CONNECT or CONFIGURE statements.

- The user can tell the operating system about a device during an interactive SYSGEN procedure.

The first technique is referred to as autoconfigure, and it is essentially automatic. The second technique requires that CONNECT statements be placed in a special command file that is executed each time the computer is bootstrapped. The third technique, interactive SYSGEN, creates a configuration file that the operating system references when the system is bootstrapped. All techniques accomplish the same result: they associate a specific device type with a bus address and interrupt vector.

Most recent versions of DEC operating systems use autoconfigure to some extent, and try to follow the same rules. The RT-11 operating system does not use autoconfigure, but can locate devices that reside at a standard address. There are some differences among operating systems, however, especially with regard to MSCP controllers at alternate LSI-11 bus addresses. The following paragraphs address these differences for each supported operating system. This discussion includes information on choosing appropriate LSI-11 bus device addresses and interrupt vectors for the subsystem.

The following operating system discussions give procedures for choosing LSI-11 bus addresses for the first MSCP controller and any subsequent controllers in the host configuration. No instructions are provided for programming the chosen address into the QD32. See subsection 4.5.1 for detailed switch setting information.

MSCP-type controllers contain two registers that are visible to the LSI-11 bus I/O page. They are the Initialization and Polling (IP) register (base address) and the Status and Address (SA) register (base address plus 2). The IP register, the CSR address, LSI-11 bus address and the base address all refer to the same register. All of the operating systems described in the following subsections use the standard LSI-11 bus address of 17721508 for the first controller on the host system.

Vector addresses for MSCP controllers are not selected by using switches on the controller, but are programmed into the controller during the Initialization process. Many operating systems select the vector address automatically. If an operating system requires manual input of the vector, the procedure notes that fact.

Again, although DEC has attempted to standardize treatment of peripherals by operating systems, some differences do exist. Table 3-2 lists and describes the device names assigned to MSCP devices under five operating systems. Two controller names and two drive names are given to indicate the numbering scheme.

Table 3-2. Device Names

| Operating System                                       | Controller<br>First, Second             | Drives Supported<br>by First Controller                    |

|--------------------------------------------------------|-----------------------------------------|------------------------------------------------------------|

| RSTS/E<br>RSX-11M<br>RSX-11M-PLUS<br>RT-11<br>MicroVMS | RUO, RU1 DUA, DUB PortO, Port1 PUA, PUB | DUO, DU1<br>DUO, DU1<br>DUO, DU1<br>DUO, DU1<br>DUAO, DUA1 |

The information regarding operating systems in these subsections is subject to change. The following discussions are based on three assumptions:

- This is the first pass that is being made through SYSGEN; therefore, no saved answer file exists. Answer N (no) to questions such as "Use as input saved answer file?"

- Your host system configuration conforms to the standard LSI-11 device configuration algorithm (otherwise autoconfigure results are not reliable).

- You are generating a mapped version of the operating system on the appropriate hardware (unless you are using RT-11).

#### 3.5.1 RSTS/E OPERATING SYSTEMS (V8.0 and above)

RSTS/E scans the hardware to determine configuration each time the system is bootstrapped. The scanning program is called INIT.SYS and it relies on the same hardware configuration conventions as do the other DEC operating systems.

The RSTS/E operating system can support two MSCP controllers. first MSCP controller must be located at the standard LSI-ll bus address, 772150g. According to DEC documentation, the second unit should be located in floating address space. For an alternate QD32, Emulex suggests specifying a LSI-11 bus address of 760334g using the HARDWARE option of the INIT.SYS program.

The INIT.SYS program uses a user-specified table, located in the currently installed monitor, to make exceptions to the autoconfigure algorithm. This table is modified by the HARDWARE option of the INIT.SYS program. Use of this table allows an MSCP controller to be placed at virtually any address on the I/O page. Note that this table must be reset any time a new monitor is installed. Emulex suggests using an LSI-Il bus address of 7603348 for an alternate QD32. An MSCP controller must be located at the standard address to be a bootstrap device.

Interrupt vector addresses are assigned to the MSCP controllers by INIT.SYS and programmed into the devices during initialization.

#### 3.5.1.1 Adding MSCP Support

Support for an MSCP controller must be included in a monitor at SYSGEN time. To include support for an MSCP controller in a RSTS/E monitor, respond to the SYSGEN question "number of MSCP controllers" with the number of MSCP controllers on the system.

Units connected to MSCP controllers will be accessible to an on-line RSTS/E system only after the monitor is successfully SYSGENed and installed with the INSTALL sub-option of the INIT.SYS program, and the units have been successfully initialized with the DSKINT sub-option of INIT.SYS.

#### 3.5.2 RT-11 OPERATING SYSTEMS (V5.1 and above)

The RT-11 Operating System supports up to four MSCP controllers with up to 256 devices (total) on the four controllers. The following paragraphs discuss the LSI-11 bus and vector addresses for MSCP controllers under RT-11 in host systems with only one MSCP controller and in those with more than one controller. Disk partitioning, a unique feature of RT-11 that is applicable regardless of the number of controllers, is also discussed.

#### 3.5.2.1 Installing a Single MSCP Controller

If your host system includes only one MSCP controller, install it with a LSI-11 bus address of 772150g. RT-11 will find and install the handler (driver) for that controller. In single MSCP controller configurations, it is not necessary to run SYSGEN. You may use one of the pregenerated monitors that are provided with the RT-11 Distribution. Emulex recommends that you modify the system start-up command file, STARTx.COM, to properly partition the disk drives. See subsection 3.5.2.3.

# 3.5.2.2 <u>Installing Multiple MSCP Controllers</u>

If your host system includes more than one MSCP controller, you may either modify the MSCP handler as described in the RT-11 Software Support Manual or perform a SYSGEN. The following procedure describes the SYSGEN technique (user input is in boldface print):

1. Initiate SYSGEN:

#### IND SYSGEN<return>

Answer the next group of questions appropriately.

Indicate that you want the system to use the start-up 2. command file when booting:

> Do you want the start-up indirect file (Y)? Y<return>

The start-up command file is required to allow additional MSCP controller LSI-11 bus addresses to be specified and to partition the disks consistently when the system is bootstrapped. Answer the next set of questions appropriately.

3. Indicate that you want MSCP support when the Disk Options question appears:

> Enter the device name you want support for [dd]: DU<return>

4. Indicate the number of MSCP controllers on your system in response to this question:

> How many ports are to be supported (1)? 2<return>

RT-11 refers to individual MSCP controllers or controllers as ports. Each port has its own LSI-ll bus and vector addresses.

5. Specify support for all other devices in your host system configuration as well. Indicate that there are no more devices by entering a period:

> Enter the device name you want support for [dd]: .<return>

6. You must specify the addresses of all MSCP controllers (ports) using the SET CSR keyboard command. To ensure that this is done consistently and automatically on power-up, you must add the commands to the system start-up command file, STARTx.COM. The x stands for the monitor that is being used, where x is S, F, or X for single-job, foreground/background, or extended memory, respectively. Edit the command file to include the following statements:

SET DU CSR=772150 (Default)

SET DU CSR2=7603348 (Floating)

SET DU VECTOR=154 (Default)

SET DU VEC2=300

The LSI-ll bus for the second device can be any unused address in the I/O page which is supported by QD32 address switch settings; the vector address can be any unused address in the vector page. Default statements are not required.

7. Complete SYSGEN according to the DEC documentation.

# 3.5.2.3 Disk Partitioning

RT-11 is unable to handle drives with a capacity of more than 65,535 blocks (33.5M bytes). To allow drives with larger capacities to be used, RT-11 allows individual physical drives to be partitioned into multiple logical drives. This is done by assigning as many logical drive names (DUO, DU1, etc.) to a physical drive as that drive can support. The statements that make that assignment should be placed in the system start-up command file. This ensures that the drives are automatically partitioned every time the system is bootstrapped and that the partitions are always the same. Use the following procedure to determine the total number of logical drives to be assigned to each physical drive.

1. Determine the drive configuration(s) that you intend to use. You need to know the LUN of each logical drive and the data storage capacity (in logical blocks) of each logical unit. Refer to Appendix D for the logical block capacity of supported SMD drives. If the QD32 is at an alternate LSI-ll bus address (not 7721508), then you must specify an MSCP device number by using switches SW1-2 through SW1-4 (see subsection 4.3.3.2.2).

- 2. Divide the capacity for each MSCP Unit by 65,535. If the result is a number greater than 1, then that MSCP Unit should be partitioned into multiple logical units. (The last partition on a disk may be smaller that 65,535 blocks.) Round the result up to the nearest whole number. That whole number equals the number of logical disks into which that MSCP unit should be partitioned.

- 3. You must then include a series of statements in the system start-up command file, STARTx.COM, that assigns logical names to each partition. Each statement has the following format:

SET DUn UNIT=y PART=x PORT=z

where  $\bf n$  is the logical device name,  $\bf y$  is the physical MSCP unit number,  $\bf x$  is the partition number, and  $\bf z$  is the controller number. You must do this for each partition on each drive, including drives that can hold only one partition.

Example: You have selected a Fujitsu M2351A drive that has a capacity of 787,156 blocks.

Dividing the unit capacities by 65,535 and rounding the result up to the nearest whole number gives the number of logical units into which each should be partitioned.

You begin assigning logical names to the partitions beginning with DUO. For the previous example, the assignments are made as follows:

```

SET DUO UNIT=0 PART=0 PORT=0

SET DU1 UNIT=0 PART=1 PORT=0

SET DU2 UNIT=0 PART=2 PORT=0

SET DU3 UNIT=0 PART=3 PORT=0

SET DU4 UNIT=0 PART=4 PORT=0

SET DU5 UNIT=0 PART=5 PORT=0

SET DU6 UNIT=0 PART=6 PORT=0

SET DU7 UNIT=0 PART=7 PORT=0

SET DU8 UNIT=0 PART=8 PORT=0

SET DU9 UNIT=0 PART=9 PORT=0

SET DU10 UNIT=0 PART=10 PORT=0

SET DU11 UNIT=0 PART=11 PORT=0

SET DU12 UNIT=0 PART=12 PORT=0

```

Modify the system start-up command file to include the disk partitioning statements.

#### 3.5.3 RSX-llm OPERATING SYSTEMS (V4.0 and above)

RSX-llM SYSGEN is an interrogative program that allows a complete, running RSX-llM system to be configured for a particular hardware environment. SYSGEN is well documented in the RSX-llM System Generation and Installation Guide, and you are expected to rely primarily on that manual. This explanation is provided only to remove some ambiguities that the installation of the QD32 may present.

SYSGEN supports autoconfigure, and MSCP controllers are detected by autoconfigure. However, autoconfigure detects only the MSCP controller that is located at the standard LSI-11 bus address. Additional MSCP controllers at alternate addresses must be attached to the operating system manually.

#### NOTE

If the QD32 controls the system disk, you must select 22-bit addressing (SW2-6 ON) even if your system has only 256K bytes of memory.

#### 3.5.3.1 <u>Installing a Single MSCP Controller</u>

If you have only one QD32, install it at the standard address (7721508) and use autoconfigure to connect your peripherals. The procedure given in the RSX-llM System Generation and Configuration Guide is adequate for this purpose.

#### 3.5.3.2 Installing Multiple MSCP Controllers

If you have two MSCP controllers, say a DEC MSCP controller and a QD32, you must perform a complete manual initialization. We recommend that the DEC MSCP controller be installed at the standard LSI-ll bus address. Locating the QD32 at the alternate LSI-ll bus address does not prevent its being used as the system device. Both MSCP controllers are connected to the operating system by using the following procedure.

- 1. Invoke SYSGEN.

- > SET /UIC=[200,200] < return >

- > @SYSGEN<return>

- 2. To indicate that you want to use autoconfigure, answer Y (yes) to the following question:

- \* Autoconfigure the host system hardware?

[Y/N]: Y<return>

- 3. To indicate that you do not want to override autoconfigure results, answer N (no) to this question:

- \* Do you want to override Autoconfigure

results? [Y/N]: N<return>

Answer the rest of the questions in the SETUP section appropriately, and continue to the next section, TARGET CONFIGURATION. In TARGET CONFIGURATION, the defaults presented for the first group of questions should be accurate for your system because autoconfigure was requested.

- 4. In response to the question regarding devices, indicate that you have two MSCP-type controllers:

- \* Devices: DU=2<return>

Devices: .<return>

This entry supersedes the value of 1 that autoconfigure has determined. Typing a period (.) terminates device input.

Continue through the next four sections, HOST CONFIGURATION, EXECUTIVE OPTIONS, TERMINAL DRIVER OPTIONS, and SYSTEM OPTIONS, answering questions appropriately.

5. When you reach the PERIPHERAL OPTIONS section, SYSGEN asks you questions that pertain only to the MSCP devices on your system. (Unless you indicated that you wished to override other autoconfigure results when you responded to the Devices question, SYSGEN asks questions on those devices.)

The first question requests information about the controller's interrupt vector address, LSI-ll bus address, the number of DU-type disk drives (there is no default value for this parameter), the number of command rings, and the number of response rings. The question is asked twice, once for controller 0 and once for controller 1, because we have specified two DU-type controllers. The dialog uses the abbreviation contr to indicate controller.

\* DU contr 0 [D:154,172150,,4,4] 154,172150,3,4,4<return>

The standard vector address for MSCP controllers is 1548. The vector for a second unit should be allocated from floating vector address space. Any unused vector between 3008 and 7748 can be allocated. See Appendix A for a description of DEC's algorithm for assigning floating vectors.

The standard LSI-11 bus address for MSCP controllers is 7721508. Emulex recommends that second unit be located at in floating LSI-11 bus address space. See Appendix A for a description of the DEC algorithm for assigning floating addresses.

The number of DU-type disk drives depends on the configuration that you have selected for the QD32, or on the number of drives that are attached to a DEC MSCP controller.

When you select a configuration for the QD32, you are taking into account the number of physical disk drives that you are attaching to the QD32's SMD interface. When you select a configuration, you are also specifying a logical arrangement for the QD32 MSCP subsystem. Some configurations split one physical drive into two logical drives to make file management easier. You determine the configuration of each SMD disk drive when you program the QD32's NOVRAM; see Section 6.

The following types of disk drives can be attached to DEC MSCP controllers:

- RX50

- RD51

- RD52

- RD53

- RC25

- RA60

- RA80

- RA81

The RX50 drive contains two 5.25-inch floppy diskettes; count an RX50 as two drives. The RC25 has both fixed and removable hard media; count an RC25 as two drives.

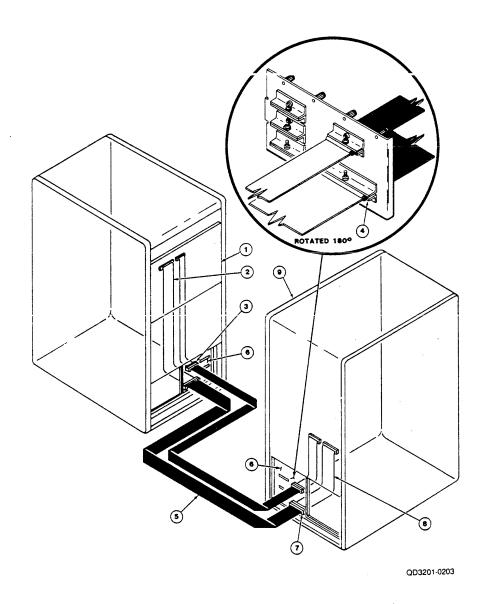

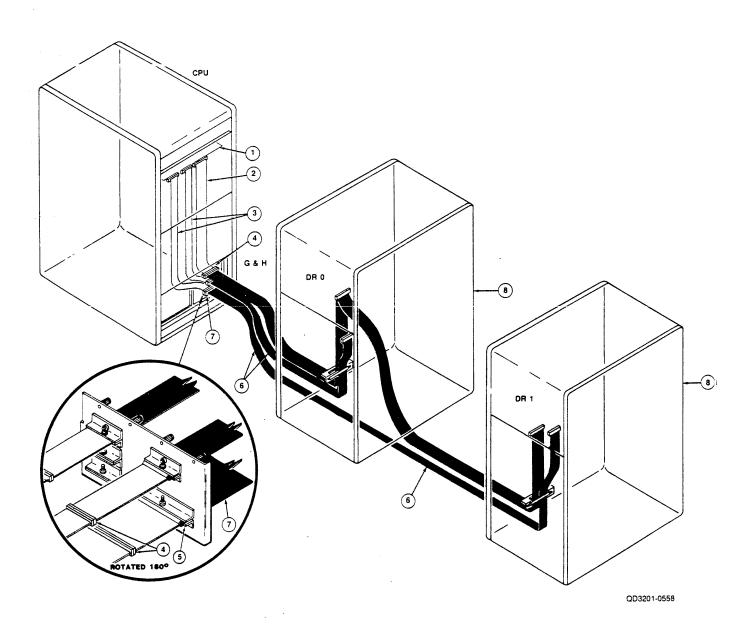

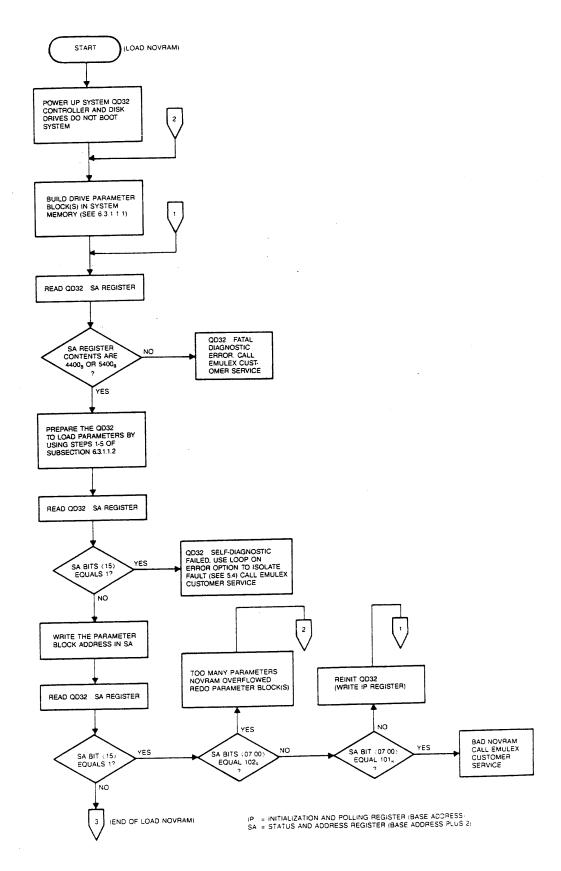

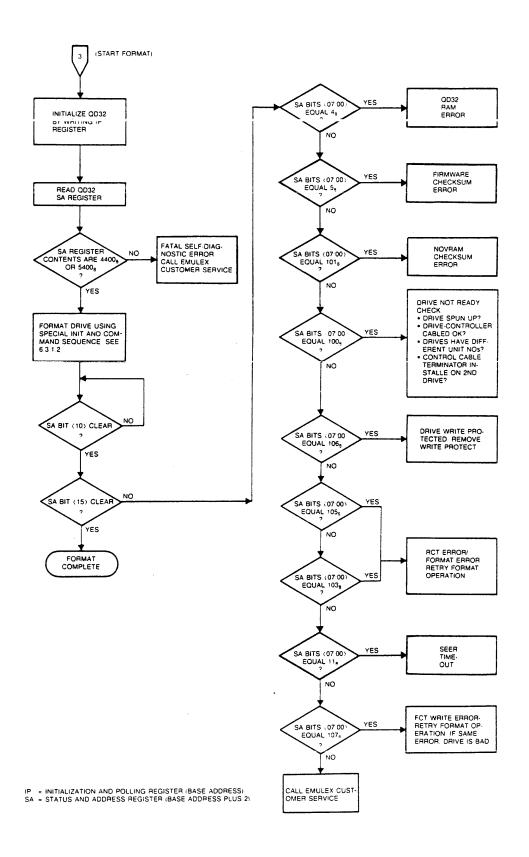

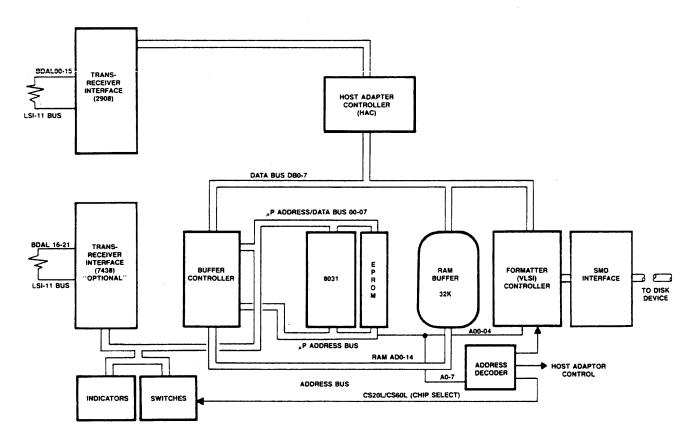

RSX-llM supports up to eight command and eight response rings; the number of command and response rings that you specify depends on your application. Four command and four response rings are reasonable and adequate for most applications. For further information about command and response rings, refer to the MSCP documentation listed in subsection 6.3 of this manual. In most instances, further information is not required to install the QD32.