# PDP-8/A MINIPROCESSOR USERS MANUAL

Copyright © 1976 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

This document was set on DIGITAL'S DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DECDECtapePDPDECCOMMDECUSRSTSDECsystem-10DIGITALTYPESET-8DECSYSTEM-20MASSBUSTYPESET-11

UNIBUS

## CONTENTS

| CHAPTER 1         INTRODUCTION AND DESCRIPTION           1.1         SYSTEM DESCRIPTION         1.4           1.1.1         Central Processor Unit (CPU)         1.8           1.1.2         KGS-AA Programmer's Console         1.8           1.1.3         Limited Function Panel         1.8           1.1.4         Memory         1.8           1.1.5         MM8-A Core Memory         1.8           1.1.6         MSB-A Read/Write Semiconductor Memory (RAM)         1.8           1.1.7         MR8-A Read Memory (ROM)         1.9           1.1.8         MRB-FB Reprogrammable Read Only Memory (PROM)         1.9           1.1.9         G8016 Power Supply Regulator Module         1.9           1.1.10         G8018 Power Supply Regulator Module         1.9           1.1.11         Interfacing         1.9           1.1.12         Option Modules         1.10           1.1.13         DKCB-AD I/O Option Board (M8316)         1.10           1.1.14         KIME-A Extended Option Board (M8317)         1.10           1.1.15         Peripheral Options         1.10           1.2         CONSOLE OPERATION         1.10           1.2.1         Limited Function Panel         1.10           1.2.2 |           |                                       | Page   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------------------------------|--------|

| 1.1.1       Central Processor Unit (CPU)       1.8         1.1.2       KCB-AA Programmer's Console       1.8         1.1.3       Limited Function Panel       1.8         1.1.4       Memory       1.8         1.1.5       MM8-A Core Memory       1.8         1.1.6       MSB-A Read/Write Semiconductor Memory (RAM)       1.8         1.1.7       MR8-A Read Memory (ROM)       1.9         1.1.8       MRB-FB Reprogrammable Read Only Memory (PROM)       1.9         1.1.9       G8018 Power Supply Regulator Module       1.9         1.1.10       G8018 Power Supply Regulator Module       1.9         1.1.11       Interfacing       1.9         1.1.12       Option Modules       1.10         1.1.13       DKCS-AA I/O Option Board (M8316)       1.10         1.1.14       KM8-A Extended Option Board (M8317)       1.10         1.1.1       KM8-A Extended Option Board (M8317)       1.10         1.2       CONSOLE OPERATION       1.10         1.2.1       Limited Function Panel       1.10         1.2.2       Programmer's Console       1.10         1.2.3       Entering Data in Memory       1.21         CHAPTER 2       INSTALLATION AND ACCEPTANCE TEST                                                | CHAPTER 1 | INTRODUCTION AND DESCRIPTION          |        |

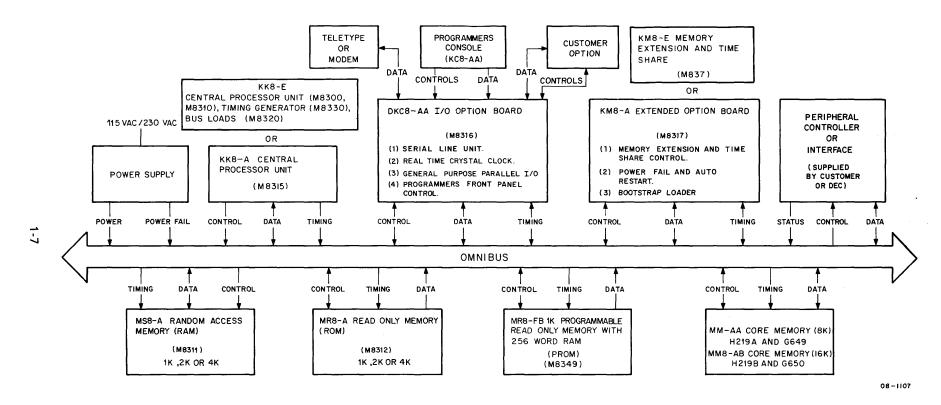

| 1.1.1       Central Processor Unit (CPU)       1.8         1.1.2       KC8-AA Programmer's Console       1.8         1.1.3       Limited Function Panel       1.8         1.1.4       Memory       1.8         1.1.5       MM8-A Core Memory       1.8         1.1.6       MS8-A Read/Write Semiconductor Memory (RAM)       1.8         1.1.7       MR8-A Read Memory (ROM)       1.9         1.1.8       MR8-FB Reprogrammable Read Only Memory (PROM)       1.9         1.1.9       G8016 Power Supply Regulator Module       1.9         1.1.10       G8018 Power Supply Regulator Module       1.9         1.1.11       Interfacing       1.9         1.1.12       Option Modules       1-10         1.1.13       DKCS-AA I/O Option Board (M8316)       1-10         1.1.14       KM8-A Extended Option Board (M8317)       1-10         1.1.15       Peripheral Options       1-10         1.2       CONSOLE OPERATION       1-10         1.2.1       Limited Function Panel       1-10         1.2.2       Programmer's Console       1-10         1.2.3       Entering Data in Memory       1-10         1.2.4       Examining Memory Locations       1-11         1.2                                                   | 1.1       | SYSTEM DESCRIPTION                    | . 1-4  |

| 1.1.2       KCB-AA Programmer's Console       1.8         1.1.3       Limited Function Panel       1.8         1.1.4       Memory       1.8         1.1.5       MM8-A Core Memory       1.8         1.1.6       MS8-A Read-Write Semiconductor Memory (RAM)       1.9         1.1.7       MR8-A Read Memory (ROM)       1.9         1.1.8       MR8-FB Reprogrammable Read Only Memory (PROM)       1.9         1.1.9       G8016 Power Supply Regulator Module       1.9         1.1.10       G8018 Power Supply Regulator Module       1.9         1.1.11       Interfacing       1.9         1.1.12       Option Modules       1-10         1.1.13       DKCB-AA I/O Option Board (M8316)       1-10         1.1.14       KM8-A Extended Option Board (M8317)       1-10         1.1.1       KM8-A Extended Option Board (M8317)       1-10         1.2       CONSOLE OPERATION       1-10         1.2.1       Limited Function Panel       1-10         1.2.2       Programmer's Console       1-10         1.2.3       Entering Data From the Programmer's Console       1-10         1.2.4       Examining Memory       1-11         1.2.5       Entering Data in Memory       2-1                                          | 1.1.1     |                                       |        |

| 1.1.3       Limited Function Panel       1.8         1.1.4       Memory       1.8         1.1.5       MM8-A Core Memory       1.8         1.1.6       MS9-A Read/Write Semiconductor Memory (RAM)       1.8         1.1.7       MR8-A Read Memory (ROM)       1.9         1.1.8       MR8-FB Reprogrammable Read Only Memory (PROM)       1.9         1.1.9       G8016 Power Supply Regulator Module       1.9         1.1.10       G8018 Power Supply Regulator Module       1.9         1.1.11       Interfacing       1.9         1.1.12       Option Modules       1.9         1.1.13       DKCB-AA I/O Option Board (M8316)       1-10         1.1.14       KM8-A Extended Option Board (M8317)       1-10         1.1.15       Peripheral Options       1-10         1.2       CONSOLE OPERATION       1-10         1.2.1       Limited Function Panel       1-10         1.2.2       Programmer's Console       1-10         1.2.3       Entering Data From the Programmer's Console       1-10         1.2.4       Examining Memory Locations       1-11         1.2.5       Entering Data in Memory       2-1         2.1       Lintering Data in Memory       2-1                                                      | 1.1.2     |                                       |        |

| 1.1.4       Memory       1.8         1.1.5       MMB-A Core Memory       1.8         1.1.6       MS8-A Read/Write Semiconductor Memory (RAM)       1.8         1.1.7       MR8-A Read Memory (ROM)       1.9         1.1.8       MR8-FB Reprogrammable Read Only Memory (PROM)       1.9         1.1.9       G8016 Power Supply Regulator Module       1.9         1.1.10       G8018 Power Supply Regulator Module       1.9         1.1.11       Interfacing       1.9         1.1.12       Option Modules       1.10         1.1.13       DKCB-AA I/O Option Board (M8316)       1.10         1.1.14       KM8-A Extended Option Board (M8317)       1.10         1.1.15       Peripheral Options       1.10         1.2       CONSOLE OPERATION       1.10         1.2.1       Limited Function Panel       1.10         1.2.2       Programmer's Console       1.10         1.2.2       Programmer's Console       1.10         1.2.2       Programmer's Console       1.11         1.2.4       Examining Memory Locations       1.11         1.2.5       Entering Data From the Programmer's Console       1.11         1.2.1       Intried Function Panel       2.2                                                        | 1.1.3     |                                       |        |

| 1.1.5       MM8-A Core Memory       1.8         1.1.6       MSS-A Read/Write Semiconductor Memory (RAM)       1.8         1.1.7       MRS-A Read Memory (ROM)       1.9         1.1.8       MR8-FB Reprogrammable Read Only Memory (PROM)       1.9         1.1.9       G8016 Power Supply Regulator Module       1.9         1.1.10       G8018 Power Supply Regulator Module       1.9         1.1.11       Interfacing       1.9         1.1.12       Option Modules       1-10         1.1.13       DKCB-AA I/O Option Board (M8316)       1-10         1.1.14       KMB-A Extended Option Board (M8317)       1-10         1.1.15       Peripheral Options       1-10         1.2       CONSOLE OPERATION       1-10         1.2.1       Limited Function Panel       1-10         1.2.2       Programmer's Console       1-10         1.2.3       Entering Data From the Programmer's Console       1-10         1.2.4       Examining Memory Locations       1-11         1.2.5       Entering Data in Memory       1-11         1.2.5       Entering Data in Memory       2-1         2.1       Power Source       2-2         2.1.1       Power Source       2-2         <                                               |           |                                       |        |

| 1.1.6       MS8-A Read/Memory (ROM)       1.9         1.1.7       MR8-A Read Memory (ROM)       1.9         1.1.8       MR8-FB Reprogrammable Read Only Memory (PROM)       1.9         1.1.9       G8016 Power Supply Regulator Module       1.9         1.1.10       G8018 Power Supply Regulator Module       1.9         1.1.11       Interfacing       1.9         1.1.12       Option Modules       1-10         1.1.13       DKC8-AA I/O Option Board (M8316)       1-10         1.1.14       KM8-A Extended Option Board (M8317)       1-10         1.1.15       Peripheral Options       1-10         1.2       CONSOLE OPERATION       1-10         1.2.1       Limited Function Panel       1-10         1.2.2       Programmer's Console       1-10         1.2.2       Programmer's Console       1-10         1.2.2       Programmer's Console       1-10         1.2.4       Examining Memory Locations       1-11         1.2.5       Entering Data From the Programmer's Console       1-11         1.2.5       Entering Data in Memory       1-11         1.2.1       Instraction And Acceptance       2-2         2.1       SITE CONSIDERATIONS       2-2                                                      |           | ·                                     |        |

| 1.1.7       MR8-A Read Memory (ROM)       1.9         1.1.8       MR8-FB Reprogrammable Read Only Memory (PROM)       1.9         1.1.9       G8016 Power Supply Regulator Module       1.9         1.1.10       G8018 Power Supply Regulator Module       1.9         1.1.11       Interfacing       1.9         1.1.12       Option Modules       1.10         1.1.13       DKC8-AA I/O Option Board (M8316)       1.10         1.1.14       KM8-A Extended Option Board (M8317)       1-10         1.1.15       Peripheral Options       1-10         1.2       CONSOLE OPERATION       1-10         1.2.1       Limited Function Panel       1-10         1.2.2       Programmer's Console       1-10         1.2.3       Entering Data From the Programmer's Console       1-10         1.2.4       Examining Memory Locations       1-11         1.2.5       Entering Data in Memory       1-11         CHAPTER 2         INSTALLATION AND ACCEPTANCE TEST         2.1       SITE CONSIDERATIONS       2.1         2.1.2       I/O Cabling Requirements       2.2         2.1.2       I/O Cabling Requirements       2.2         2.1.3       Fire and Safety Precautions <td></td> <td></td> <td></td>                      |           |                                       |        |

| 1.1.8       MR8-FB Reprogrammable Read Only Memory (PROM)       1.9         1.1.9       G8016 Power Supply Regulator Module       1.9         1.1.10       G8018 Power Supply Regulator Module       1.9         1.1.11       Interfacing       1.9         1.1.12       Option Modules       1-10         1.1.13       DKCB-AA I/O Option Board (M8316)       1-10         1.1.14       KM8-A Extended Option Board (M8317)       1-10         1.1.15       Peripheral Options       1-10         1.2       CONSOLE OPERATION       1-10         1.2.1       Limited Function Panel       1-10         1.2.2       Programmer's Console       1-10         1.2.3       Entering Data From the Programmer's Console       1-10         1.2.4       Examining Memory Locations       1-11         1.2.5       Entering Data in Memory       1-11         CHAPTER 2       INSTALLATION AND ACCEPTANCE TEST         2.1       2.1       Power Source       2.2         2.1.1       Power Source       2.2         2.1.2       I/O Cabling Requirements       2.2         2.1.1       Power Source       2.2         2.1.2       I/O Cabling Requirements       2.2         2.1.3 </td <td></td> <td></td> <td></td>                  |           |                                       |        |

| 1.1.9       G8016 Power Supply Regulator Module       1.9         1.1.10       G8018 Power Supply Regulator Module       1.9         1.1.11       Interfacing       1.9         1.1.12       Option Modules       1.10         1.1.13       DKC8-AA I/O Option Board (M8316)       1.10         1.1.14       KM8-A Extended Option Board (M8317)       1.10         1.1.15       Peripheral Options       1.10         1.2       CONSOLE OPERATION       1.10         1.2.1       Limited Function Panel       1.10         1.2.2       Programmer's Console       1.10         1.2.3       Entering Data From the Programmer's Console       1.10         1.2.4       Examining Memory Locations       1.11         1.2.5       Entering Data in Memory       1.11         1.2.5       Entering Data in Memory       1.11         1.2.1       POWER Source       2.2         2.1.2       I/O Cabling Requirements       2.2         2.1.3       Fire and Safety Precautions       2.2         2.2.1       PACKING INSTRUCTIONS       2.2         2.3.1       BAB-C Chassis Assembly       2.3         2.3.2       Other PDP-8/A Chassis Assemblies       2.3         2.4.3 <td></td> <td></td> <td></td>                         |           |                                       |        |

| 1.1.10       G8018 Power Supply Regulator Module       1.9         1.1.11       Interfacing       1.9         1.1.12       Option Modules       1-10         1.1.13       DKC8-AA I/O Option Board (M8316)       1-10         1.1.14       KM8-A Extended Option Board (M8317)       1-10         1.1.15       Peripheral Options       1-10         1.2       CONSOLE OPERATION       1-10         1.2.1       Limited Function Panel       1-10         1.2.2       Programmer's Console       1-10         1.2.3       Entering Data From the Programmer's Console       1-10         1.2.4       Examining Memory Locations       1-11         1.2.5       Entering Data in Memory       1-11         1.2.4       Examining Memory Locations       1-11         1.2.5       Entering Data in Memory       1-11         1.2.4       Examining Memory Locations       2-1         2.1       INSTALLATION AND ACCEPTANCE TEST         2.1       Prower Source       2-2         2.1       SITE CONSIDERATIONS       2-1         2.1.1       Power Source       2-2         2.1.2       I/O Cabling Requirements       2-2         2.1.3       Fire and Safety Precautions                                                        |           |                                       |        |

| 1.1.11       Interfacing       1-9         1.1.12       Option Modules       1-10         1.1.13       DKC8-AA I/O Option Board (M8316)       1-10         1.1.14       KM8-A Extended Option Board (M8317)       1-10         1.1.15       Peripheral Options       1-10         1.2       CONSOLE OPERATION       1-10         1.2.1       Limited Function Panel       1-10         1.2.2       Programmer's Console       1-10         1.2.3       Entering Data From the Programmer's Console       1-10         1.2.4       Examining Memory Locations       1-11         1.2.5       Entering Data in Memory       1-11         1.2.5       Entering Data in Memory       1-11         1.2.1       Power Source       2-2         2.1       SITE CONSIDERATIONS       2-1         2.1.1       Power Source       2-2         2.1.2       I/O Cabling Requirements       2-2         2.1.3       Fire and Safety Precautions       2-2         2.2       UNPACKING INSTRUCTIONS       2-2         2.3       PACKING INSTRUCTIONS       2-3         2.3.1       BA8-C Chassis Assembly       2-3         2.3.2       Other PDP-8/A Chassis Assembly <t< td=""><td></td><td></td><td></td></t<>                               |           |                                       |        |

| 1.1.12       Option Modules       1-10         1.1.13       DKC8-AA I/O Option Board (M8316)       1-10         1.1.14       KM8-A Extended Option Board (M8317)       1-10         1.1.15       Peripheral Options       1-10         1.2       CONSOLE OPERATION       1-10         1.2.1       Limited Function Panel       1-10         1.2.2       Programmer's Console       1-10         1.2.3       Entering Data From the Programmer's Console       1-10         1.2.4       Examining Memory Locations       1-11         1.2.5       Entering Data in Memory       1-11         1.2.5       Entering Data in Memory       1-11         1.2.1       Entering Data in Memory       1-11         1.2.2       INSTALLATION AND ACCEPTANCE TEST         2.1       SITE CONSIDERATIONS       2-1         2.1.2       I/O Cabling Requirements       2-2         2.1.3       Fire and Safety Precautions       2-2         2.2       UNPACKING INSTRUCTIONS       2-2         2.3       PACKING INSTRUCTIONS       2-2         2.3.1       BA8-C Chassis Assembly       2-3         2.3.2       Other PDP-B/A Chassis Assembly       2-3         2.3.1       Chassis Descr                                                   |           |                                       |        |

| 1.1.13       DKC8-AA I/O Option Board (M8316)       1-10         1.1.14       KM8-A Extended Option Board (M8317)       1-10         1.1.15       Peripheral Options       1-10         1.2       CONSOLE OPERATION       1-10         1.2.1       Limited Function Panel       1-10         1.2.2       Programmer's Console       1-10         1.2.2       Examining Data From the Programmer's Console       1-10         1.2.3       Entering Data From the Programmer's Console       1-10         1.2.4       Examining Memory Locations       1-11         1.2.5       Entering Data in Memory       1-11         1.2.5       Entering Data in Memory       1-11         CHAPTER 2         INSTALLATION AND ACCEPTANCE TEST         2.1       SITE CONSIDERATIONS       2-1         2.1       Power Source       2-2         2.1.2       I/O Cabling Requirements       2-2         2.1.3       Fire and Safety Precautions       2-2         2.2       2.1/O Cabling Requirements       2-2         2.1.3       Fire and Safety Precautions       2-2         2.2       UNPACKING INSTRUCTIONS       2-2         2.3       PACKING INSTRUCTIONS       2-3                                                                 |           |                                       |        |

| 1.1.14       KM8-A Extended Option Board (M8317)       1-10         1.1.15       Peripheral Options       1-10         1.2       CONSOLE OPERATION       1-10         1.2.1       Limited Function Panel       1-10         1.2.2       Programmer's Console       1-10         1.2.3       Entering Data From the Programmer's Console       1-10         1.2.4       Examining Memory Locations       1-11         1.2.5       Entering Data in Memory       1-11         CHAPTER 2         INSTALLATION AND ACCEPTANCE TEST         2.1         SITE CONSIDERATIONS       2-1         2.1.1       Power Source       2-2         2.1.2       I/O Cabling Requirements       2-2         2.1.3       Fire and Safety Precautions       2-2         2.2       UNPACKING INSTRUCTIONS       2-2         2.3       PACKING INSTRUCTIONS       2-2         2.3.1       BA8-C Chassis Assembly       2-3         2.3.2       Other PDP-8/A Chassis Assemblies       2-3         2.4.4       PDP-8/A BASIC SYSTEM COMPONENTS       2-7         2.4.1       Chassis Descriptions       2-14         2.4.2       Expansion Techniques                                                                                                   |           | ·                                     |        |

| 1.1.15       Peripheral Options       1.10         1.2       CONSOLE OPERATION       1.10         1.2.1       Limited Function Panel       1.10         1.2.2       Programmer's Console       1.10         1.2.3       Entering Data From the Programmer's Console       1.10         1.2.4       Examining Memory Locations       1.11         1.2.5       Entering Data in Memory       1.11         CHAPTER 2         UNSTALLATION AND ACCEPTANCE TEST         2.1       SITE CONSIDERATIONS       2.1         2.1.1       Power Source       2.2         2.1.2       I/O Cabling Requirements       2.2         2.1.3       Fire and Safety Precautions       2.2         2.1.3       Fire and Safety Precautions       2.2         2.2       UNPACKING INSTRUCTIONS       2.2         2.3       PACKING INSTRUCTIONS       2.3         2.3.1       BAB-C Chassis Assembly       2.3         2.3.2       Other PDP-8/A Chassis Assembles       2.3         2.4       PDP-8/A BASIC SYSTEM COMPONENTS       2.7         2.4.1       Chassis Descriptions       2.14         2.4.2       Expansion Techniques       2.14         2.4.3                                                                                         |           |                                       |        |

| 1.2       CONSOLE OPERATION       1-10         1.2.1       Limited Function Panel       1-10         1.2.2       Programmer's Console       1-10         1.2.3       Entering Data From the Programmer's Console       1-10         1.2.4       Examining Memory Locations       1-11         1.2.5       Entering Data in Memory       1-11         CHAPTER 2         INSTALLATION AND ACCEPTANCE TEST         2.1       SITE CONSIDERATIONS       2-1         2.1.1       Power Source       2-2         2.1.2       I/O Cabling Requirements       2-2         2.1.3       Fire and Safety Precautions       2-2         2.2       2.1.3       Fire and Safety Precautions       2-2         2.2       2.1.3       PACKING INSTRUCTIONS       2-2         2.3       PACKING INSTRUCTIONS       2-3         2.3.1       BA8-C Chassis Assembly       2-3         2.3.2       Other PDP-8/A Chassis Assemblies       2-3         2.4       PDP-8/A BASIC SYSTEM COMPONENTS       2-7         2.4.1       Chassis Descriptions       2-8         2.4.2       Expansion Techniques       2-14         2.4.3       PDP-8/A Module Descriptions       2-14                                                                           |           |                                       |        |

| 1.2.1       Limited Function Panel       1.10         1.2.2       Programmer's Console       1.10         1.2.3       Entering Data From the Programmer's Console       1.10         1.2.4       Examining Memory Locations       1.11         1.2.5       Entering Data in Memory       1.11         CHAPTER 2         INSTALLATION AND ACCEPTANCE TEST         2.1       SITE CONSIDERATIONS       2.1         2.1.1       Power Source       2.2         2.1.2       I/O Cabling Requirements       2.2         2.1.3       Fire and Safety Precautions       2.2         2.2       UNPACKING INSTRUCTIONS       2.2         2.3       PACKING INSTRUCTIONS       2.3         2.3.1       BAB-C Chassis Assembly       2.3         2.3.2       Other PDP-8/A Chassis Assemblies       2.3         2.4       PDP-8/A BASIC SYSTEM COMPONENTS       2.7         2.4.1       Chassis Descriptions       2.8         2.4.2       Expansion Techniques       2.14         2.4.3       PDP-8/A Module Descriptions       2.14         2.4.3.1       KK8-A Central Processor Unit (CPU)       2.14         2.4.3.2       MS8-A Read/Write Random Access Memory (ROM)       2.                                                         |           |                                       |        |

| 1.2.2       Programmer's Console       1-10         1.2.3       Entering Data From the Programmer's Console       1-10         1.2.4       Examining Memory Locations       1-11         1.2.5       Entering Data in Memory       1-11         CHAPTER 2         INSTALLATION AND ACCEPTANCE TEST         2.1       SITE CONSIDERATIONS       2-1         2.1.1       Power Source       2-2         2.1.2       I/O Cabling Requirements       2-2         2.1.3       Fire and Safety Precautions       2-2         2.1       2.1       Pire and Safety Precautions       2-2         2.2       UNPACKING INSTRUCTIONS       2-2         2.3       PACKING INSTRUCTIONS       2-3         2.3.1       BA8-C Chassis Assembly       2-3         2.3.2       Other PDP-8/A Chassis Assembles       2-3         2.4       PDP-8/A BASIC SYSTEM COMPONENTS       2-7         2.4.1       Chassis Descriptions       2-8         2.4.2       Expansion Techniques       2-14         2.4.3       PDP-8/A Module Descriptions       2-14         2.4.3       PDP-8/A Module Descriptions       2-14         2.4.3.1       KK8-A Central Processor Unit (CPU)                                                                         |           |                                       |        |

| 1.2.3       Entering Data From the Programmer's Console       110         1.2.4       Examining Memory Locations       111         1.2.5       Entering Data in Memory       111         CHAPTER 2       INSTALLATION AND ACCEPTANCE TEST         2.1       SITE CONSIDERATIONS       2.1         2.1.1       Power Source       2.2         2.1.2       I/O Cabling Requirements       2.2         2.1.3       Fire and Safety Precautions       2.2         2.2       UNPACKING INSTRUCTIONS       2.2         2.3       PACKING INSTRUCTIONS       2.2         2.3.1       BA8-C Chassis Assembly       2.3         2.3.2       Other PDP-8/A Chassis Assemblies       2.3         2.3.1       BAB-C Chassis Assemblies       2.3         2.4.1       Chassis Descriptions       2.3         2.4.2       Expansion Techniques       2.3         2.4.1       Chassis Descriptions       2.14         2.4.2       Expansion Techniques       2.14         2.4.3       PDP-8/A Module Descriptions       2.14         2.4.3.1       KK8-A Central Processor Unit (CPU)       2.14         2.4.3.2       MSB-A Read/Write Random Access Memory (RAM)       2.16 <td< td=""><td></td><td></td><td></td></td<>                       |           |                                       |        |

| 1.2.4       Examining Memory Locations       111         1.2.5       Entering Data in Memory       111         CHAPTER 2       INSTALLATION AND ACCEPTANCE TEST         2.1       SITE CONSIDERATIONS       2-1         2.1.1       Power Source       2-2         2.1.2       I/O Cabling Requirements       2-2         2.1.3       Fire and Safety Precautions       2-2         2.2       UNPACKING INSTRUCTIONS       2-2         2.3       PACKING INSTRUCTIONS       2-3         2.3.1       BA8-C Chassis Assembly       2-3         2.3.2       Other PDP-8/A Chassis Assemblies       2-3         2.3.2       Other PDP-8/A Chassis Assemblies       2-3         2.4       PDP-8/A BASIC SYSTEM COMPONENTS       2-7         2.4.1       Chassis Descriptions       2-8         2.4.2       Expansion Techniques       2-14         2.4.2       Expansion Techniques       2-14         2.4.3       PDP-8/A Module Descriptions       2-14         2.4.3       PDP-8/A Module Descriptions       2-14         2.4.3.1       KK8-A Central Processor Unit (CPU)       2-14         2.4.3.2       MS8-A Read/Write Random Access Memory (RAM)       2-16 <td< td=""><td></td><td></td><td></td></td<>                     |           |                                       |        |

| 1.11         CHAPTER 2       INSTALLATION AND ACCEPTANCE TEST         2.1       SITE CONSIDERATIONS       2-1         2.1.1       Power Source       2-2         2.1.2       I/O Cabling Requirements       2-2         2.1.3       Fire and Safety Precautions       2-2         2.2       UNPACKING INSTRUCTIONS       2-2         2.3       PACKING INSTRUCTIONS       2-3         2.3.1       BA8-C Chassis Assembly       2-3         2.3.2       Other PDP-8/A Chassis Assemblies       2-3         2.4       PDP-8/A BASIC SYSTEM COMPONENTS       2-7         2.4.1       Chassis Descriptions       2-8         2.4.2       Expansion Techniques       2-14         2.4.3       PDP-8/A Module Descriptions       2-14         2.4.3       PDP-8/A Module Descriptions       2-14         2.4.3.1       KK8-A Central Processor Unit (CPU)       2-14         2.4.3.2       MS8-A Read/Write Random Access Memory (RAM)       2-16         2.4.3.3       MR8-A Read Only Random Access Memory (ROM)       2-16         2.4.3.4       MM8-AA 8K Core Memory       2-21         2.4.3.5       MM8-AB 16K Core Memory       2-21         2.4.3.6                                                                            |           |                                       |        |

| CHAPTER 2       INSTALLATION AND ACCEPTANCE TEST         2.1       SITE CONSIDERATIONS       2-1         2.1.1       Power Source       2-2         2.1.2       I/O Cabling Requirements       2-2         2.1.3       Fire and Safety Precautions       2-2         2.2       UNPACKING INSTRUCTIONS       2-2         2.3       PACKING INSTRUCTIONS       2-3         2.3.1       BA8-C Chassis Assembly       2-3         2.3.2       Other PDP-8/A Chassis Assemblies       2-3         2.4       PDP-8/A BASIC SYSTEM COMPONENTS       2-7         2.4.1       Chassis Descriptions       2-8         2.4.2       Expansion Techniques       2-14         2.4.3       PDP-8/A Module Descriptions       2-14         2.4.3       PDP-8/A Module Descriptions       2-14         2.4.3.1       KK8-A Central Processor Unit (CPU)       2-14         2.4.3.2       MS8-A Read/Write Random Access Memory (RAM)       2-16         2.4.3.3       MR8-A Read Only Random Access Memory (ROM)       2-16         2.4.3.4       MM8-A B 16K Core Memory       2-21         2.4.3.5       MM8-A B 16K Core Memory       2-21         2.4.3.6       D KC8-AA I/O Option Board       2-24 <td></td> <td></td> <td></td>             |           |                                       |        |

| 2.1       SITE CONSIDERATIONS       2-1         2.1.1       Power Source       2-2         2.1.2       I/O Cabling Requirements       2-2         2.1.3       Fire and Safety Precautions       2-2         2.2       UNPACKING INSTRUCTIONS       2-2         2.3       PACKING INSTRUCTIONS       2-3         2.3.1       BA8-C Chassis Assembly       2-3         2.3.2       Other PDP-8/A Chassis Assemblies       2-3         2.4       PDP-8/A BASIC SYSTEM COMPONENTS       2-7         2.4.1       Chassis Descriptions       2-8         2.4.2       Expansion Techniques       2-14         2.4.3       PDP-8/A Module Descriptions       2-14         2.4.3.1       KK8-A Central Processor Unit (CPU)       2-14         2.4.3.2       MS8-A Read/Write Random Access Memory (RAM)       2-16         2.4.3.3       MR8-A Read Only Random Access Memory (ROM)       2-16         2.4.3.5       MM8-AA 8K Core Memory       2-21         2.4.3.6       DKC8-AA I/O Option Board       2-24         2.4.3.7       KM8-A Extended Option Board       2-24         2.4.3.8       Semiconductor Memory Power Supply       2-30         2.4.3.9       Core Memory Power Supply Regulator       2-                         | 1.2.5     | Entering Data in Memory               | . 1-11 |

| 2.1.1       Power Source       2-2         2.1.2       I/O Cabling Requirements       2-2         2.1.3       Fire and Safety Precautions       2-2         2.2       UNPACKING INSTRUCTIONS       2-2         2.3       PACKING INSTRUCTIONS       2-3         2.3.1       BA8-C Chassis Assembly       2-3         2.3.2       Other PDP-8/A Chassis Assemblies       2-3         2.4       PDP-8/A BASIC SYSTEM COMPONENTS       2-7         2.4.1       Chassis Descriptions       2-8         2.4.2       Expansion Techniques       2-14         2.4.3       PDP-8/A Module Descriptions       2-14         2.4.3.1       KK8-A Central Processor Unit (CPU)       2-14         2.4.3.2       MS8-A Read/Write Random Access Memory (RAM)       2-16         2.4.3.3       MR8-A Read Only Random Access Memory (ROM)       2-16         2.4.3.4       MM8-AA 8K Core Memory       2-21         2.4.3.5       MM8-AB 16K Core Memory       2-21         2.4.3.6       DKC8-AA I/O Option Board       2-24         2.4.3.7       KM8-A Extended Option Board       2-24         2.4.3.8       Semiconductor Memory Power Supply       2-30         2.4.3.9       Core Memory Power Supply Regulator                          | CHAPTER 2 | INSTALLATION AND ACCEPTANCE TEST      |        |

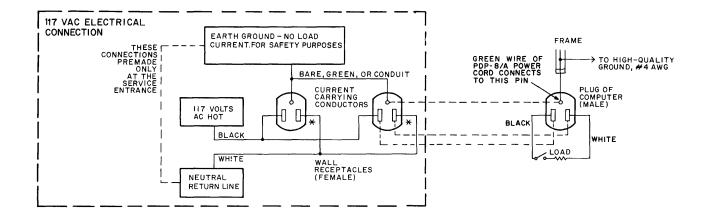

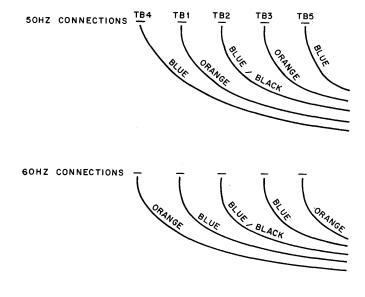

| 2.1.2       I/O Cabling Requirements       2-2         2.1.3       Fire and Safety Precautions       2-2         2.2       UNPACKING INSTRUCTIONS       2-2         2.3       PACKING INSTRUCTIONS       2-3         2.3.1       BA8-C Chassis Assembly       2-3         2.3.2       Other PDP-8/A Chassis Assemblies       2-3         2.4       PDP-8/A BASIC SYSTEM COMPONENTS       2-7         2.4.1       Chassis Descriptions       2-8         2.4.2       Expansion Techniques       2-14         2.4.3       PDP-8/A Module Descriptions       2-14         2.4.3       PDP-8/A Module Descriptions       2-14         2.4.3       KK8-A Central Processor Unit (CPU)       2-14         2.4.3.1       KK8-A Central Processor Unit (CPU)       2-14         2.4.3.2       MS8-A Read/Write Random Access Memory (RAM)       2-16         2.4.3.3       MR8-A Read Only Random Access Memory (ROM)       2-16         2.4.3.4       MM8-AA 8K Core Memory       2-21         2.4.3.5       MM8-AB 16K Core Memory       2-21         2.4.3.6       DKC8-AA I/O Option Board       2-24         2.4.3.7       KM8-A Extended Option Board       2-28         2.4.3.8       Semiconductor Memory Power Su                | 2.1       | SITE CONSIDERATIONS                   | . 2-1  |

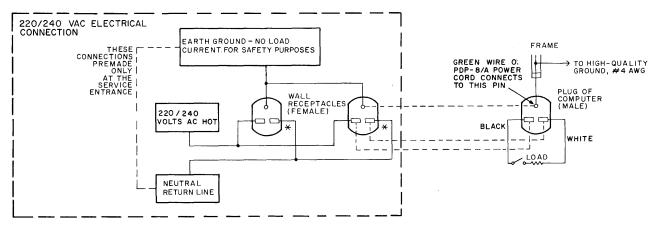

| 2.1.3       Fire and Safety Precautions       2-2         2.2       UNPACKING INSTRUCTIONS       2-2         2.3       PACKING INSTRUCTIONS       2-3         2.3.1       BA8-C Chassis Assembly       2-3         2.3.2       Other PDP-8/A Chassis Assemblies       2-3         2.4       PDP-8/A BASIC SYSTEM COMPONENTS       2-7         2.4.1       Chassis Descriptions       2-8         2.4.2       Expansion Techniques       2-14         2.4.3       PDP-8/A Module Descriptions       2-14         2.4.3       PDP-8/A Module Descriptions       2-14         2.4.3       KK8-A Central Processor Unit (CPU)       2-14         2.4.3.1       KK8-A Central Processor Unit (CPU)       2-14         2.4.3.2       MS8-A Read/Write Random Access Memory (RAM)       2-16         2.4.3.3       MR8-A Read Only Random Access Memory (ROM)       2-16         2.4.3.4       MM8-AA 8K Core Memory       2-21         2.4.3.5       MM8-AB 16K Core Memory       2-21         2.4.3.6       DKC8-AA I/O Option Board       2-24         2.4.3.7       KM8-A Extended Option Board       2-28         2.4.3.8       Semiconductor Memory Power Supply       2-30         2.4.3.9       Core Memory Power                | 2.1.1     | Power Source                          | . 2-2  |

| 2.2       UNPACKING INSTRUCTIONS       2-2         2.3       PACKING INSTRUCTIONS       2-3         2.3.1       BA8-C Chassis Assembly       2-3         2.3.2       Other PDP-8/A Chassis Assemblies       2-3         2.4       PDP-8/A BASIC SYSTEM COMPONENTS       2-7         2.4.1       Chassis Descriptions       2-8         2.4.2       Expansion Techniques       2-14         2.4.3       PDP-8/A Module Descriptions       2-14         2.4.3.1       KK8-A Central Processor Unit (CPU)       2-14         2.4.3.2       MS8-A Read/Write Random Access Memory (RAM)       2-16         2.4.3.3       MR8-A Read Only Random Access Memory (ROM)       2-16         2.4.3.4       MM8-AA 8K Core Memory       2-21         2.4.3.5       MM8-AB 16K Core Memory       2-21         2.4.3.6       DKC8-AA I/O Option Board       2-24         2.4.3.7       KM8-A Extended Option Board       2-28         2.4.3.8       Semiconductor Memory Power Supply       2-30         2.4.3.9       Core Memory Power Supply Regulator       2-32         2.4.3.10       Limited Function Panel       2-34                                                                                                                  | 2.1.2     | I/O Cabling Requirements              | . 2-2  |

| 2.3       PACKING INSTRUCTIONS       2-3         2.3.1       BA8-C Chassis Assembly       2-3         2.3.2       Other PDP-8/A Chassis Assemblies       2-3         2.4       PDP-8/A BASIC SYSTEM COMPONENTS       2-7         2.4.1       Chassis Descriptions       2-8         2.4.2       Expansion Techniques       2-14         2.4.3       PDP-8/A Module Descriptions       2-14         2.4.3.1       KK8-A Central Processor Unit (CPU)       2-14         2.4.3.2       MS8-A Read/Write Random Access Memory (RAM)       2-16         2.4.3.3       MR8-A Read Only Random Access Memory (ROM)       2-16         2.4.3.4       MM8-AA 8K Core Memory       2-21         2.4.3.5       MM8-AB 16K Core Memory       2-21         2.4.3.6       DKC8-AA I/O Option Board       2-24         2.4.3.7       KM8-A Extended Option Board       2-28         2.4.3.8       Semiconductor Memory Power Supply       2-30         2.4.3.9       Core Memory Power Supply Regulator       2-32         2.4.3.10       Limited Function Panel       2-34                                                                                                                                                                     | 2.1.3     | Fire and Safety Precautions           | . 2-2  |

| 2.3.1       BA8-C Chassis Assembly       2-3         2.3.2       Other PDP-8/A Chassis Assemblies       2-3         2.4       PDP-8/A BASIC SYSTEM COMPONENTS       2-7         2.4.1       Chassis Descriptions       2-8         2.4.2       Expansion Techniques       2-14         2.4.3       PDP-8/A Module Descriptions       2-14         2.4.3.1       KK8-A Central Processor Unit (CPU)       2-14         2.4.3.2       MS8-A Read/Write Random Access Memory (RAM)       2-16         2.4.3.3       MR8-A Read Only Random Access Memory (ROM)       2-16         2.4.3.4       MM8-AA 8K Core Memory       2-21         2.4.3.5       MM8-AB 16K Core Memory       2-21         2.4.3.6       DKC8-AA I/O Option Board       2-24         2.4.3.7       KM8-A Extended Option Board       2-28         2.4.3.8       Semiconductor Memory Power Supply       2-30         2.4.3.9       Core Memory Power Supply Regulator       2-32         2.4.3.10       Limited Function Panel       2-34                                                                                                                                                                                                                      | 2.2       | UNPACKING INSTRUCTIONS                | . 2-2  |

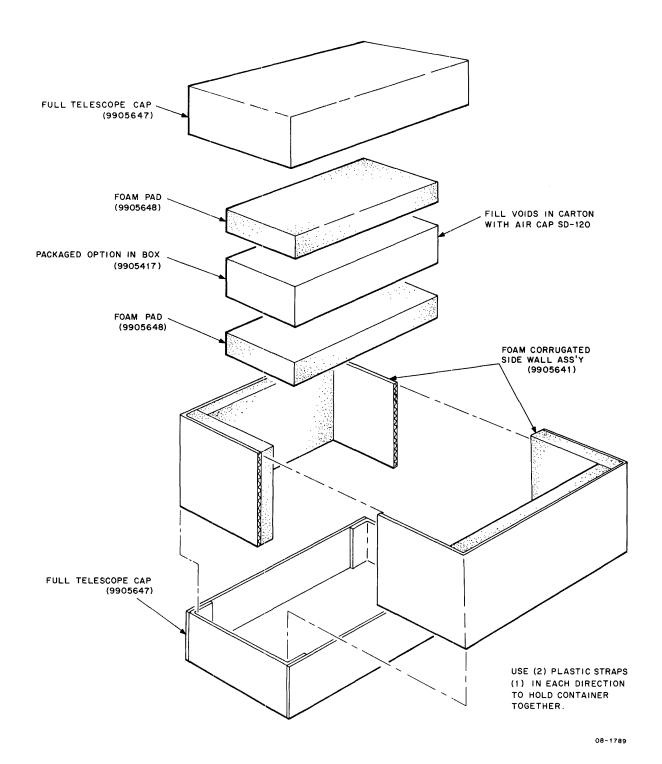

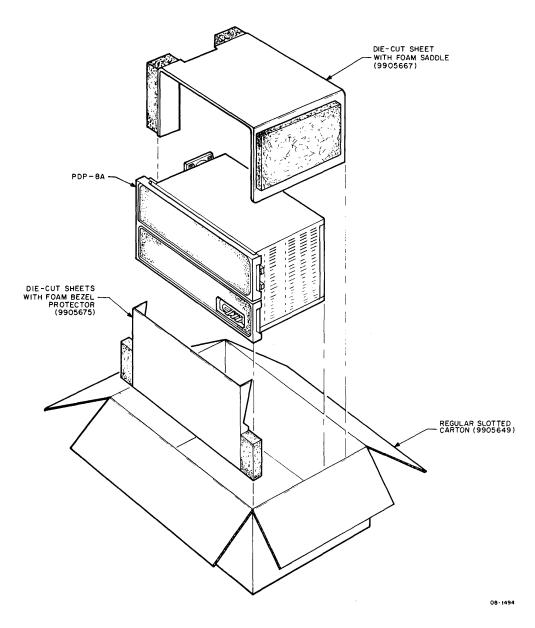

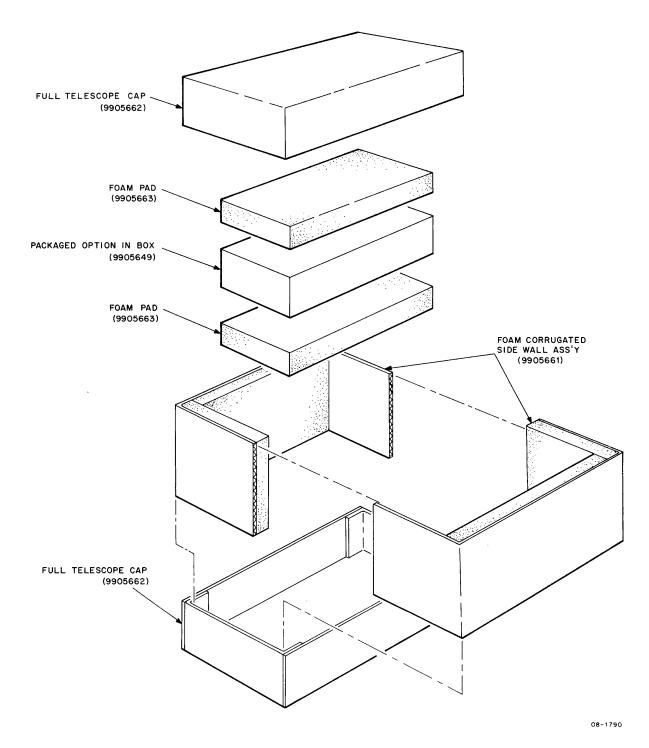

| 2.3.1       BA8-C Chassis Assembly       2-3         2.3.2       Other PDP-8/A Chassis Assemblies       2-3         2.4       PDP-8/A BASIC SYSTEM COMPONENTS       2-7         2.4.1       Chassis Descriptions       2-8         2.4.2       Expansion Techniques       2-14         2.4.3       PDP-8/A Module Descriptions       2-14         2.4.3.1       KK8-A Central Processor Unit (CPU)       2-14         2.4.3.2       MS8-A Read/Write Random Access Memory (RAM)       2-16         2.4.3.3       MR8-A Read Only Random Access Memory (ROM)       2-16         2.4.3.4       MM8-AA 8K Core Memory       2-21         2.4.3.5       MM8-AB 16K Core Memory       2-21         2.4.3.6       DKC8-AA I/O Option Board       2-24         2.4.3.7       KM8-A Extended Option Board       2-28         2.4.3.8       Semiconductor Memory Power Supply       2-30         2.4.3.9       Core Memory Power Supply Regulator       2-32         2.4.3.10       Limited Function Panel       2-34                                                                                                                                                                                                                      | 2.3       | PACKING INSTRUCTIONS                  | . 2-3  |

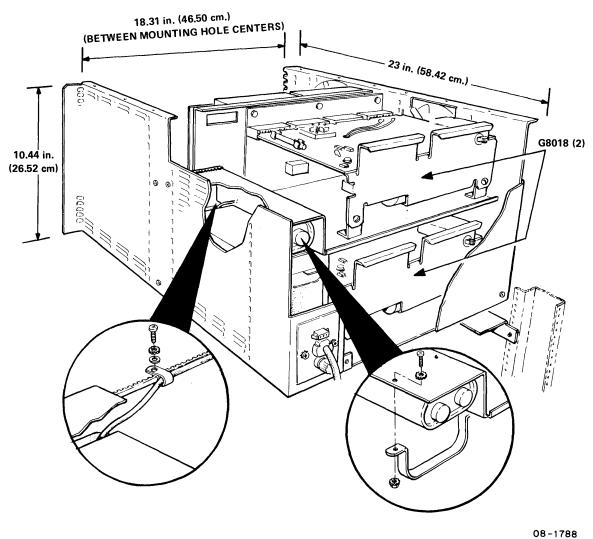

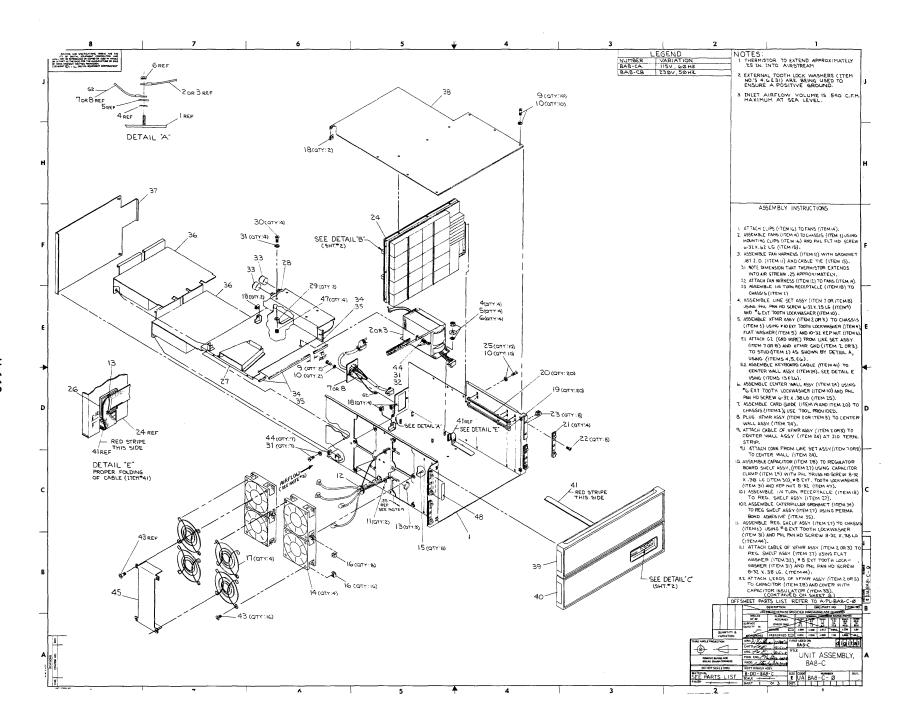

| 2.3.2       Other PDP-8/A Chassis Assemblies       2-3         2.4       PDP-8/A BASIC SYSTEM COMPONENTS       2-7         2.4.1       Chassis Descriptions       2-8         2.4.2       Expansion Techniques       2-14         2.4.3       PDP-8/A Module Descriptions       2-14         2.4.3.1       KK8-A Central Processor Unit (CPU)       2-14         2.4.3.2       MS8-A Read/Write Random Access Memory (RAM)       2-16         2.4.3.3       MR8-A Read Only Random Access Memory (ROM)       2-16         2.4.3.4       MM8-AA 8K Core Memory       2-21         2.4.3.5       MM8-AB 16K Core Memory       2-21         2.4.3.6       DKC8-AA I/O Option Board       2-24         2.4.3.7       KM8-A Extended Option Board       2-28         2.4.3.8       Semiconductor Memory Power Supply       2-30         2.4.3.9       Core Memory Power Supply Regulator       2-32         2.4.3.10       Limited Function Panel       2-34                                                                                                                                                                                                                                                                           | 2.3.1     | BA8-C Chassis Assembly                | . 2-3  |

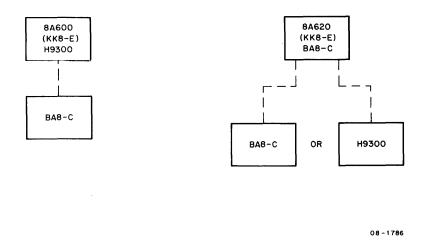

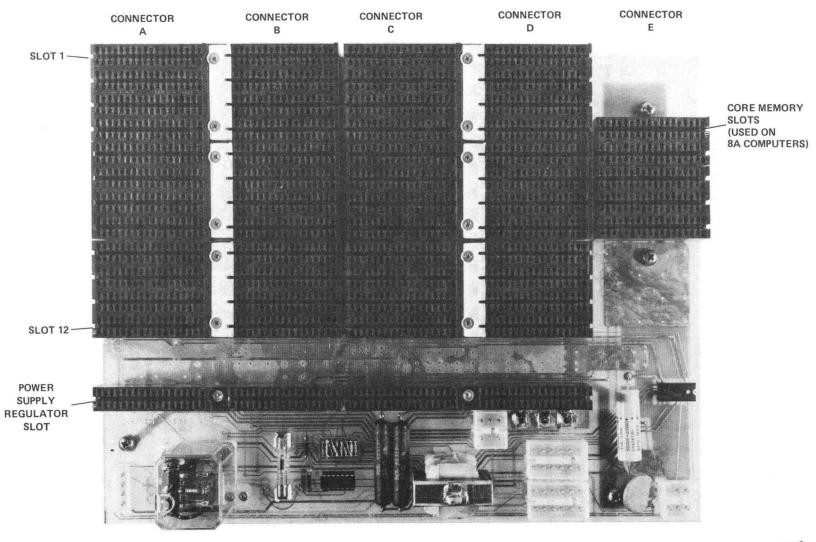

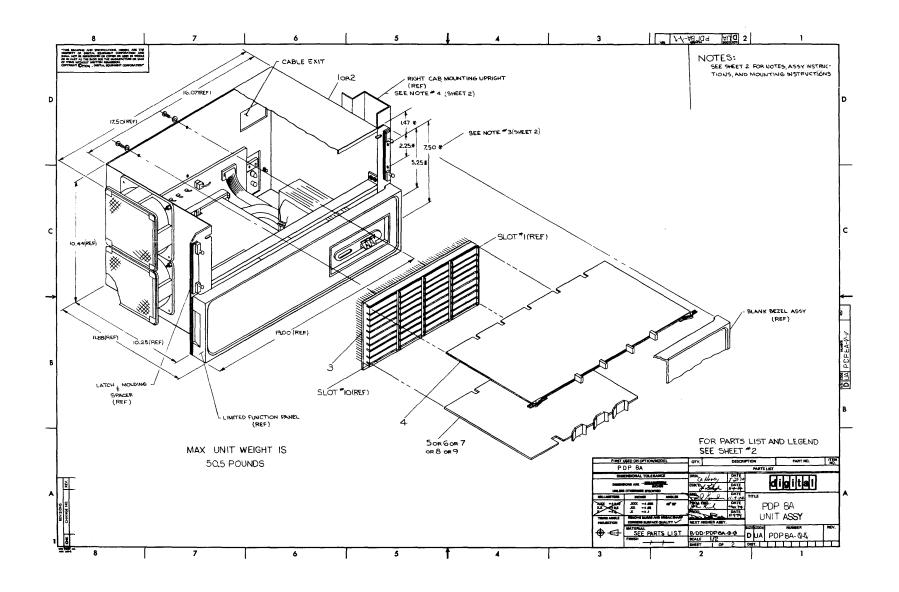

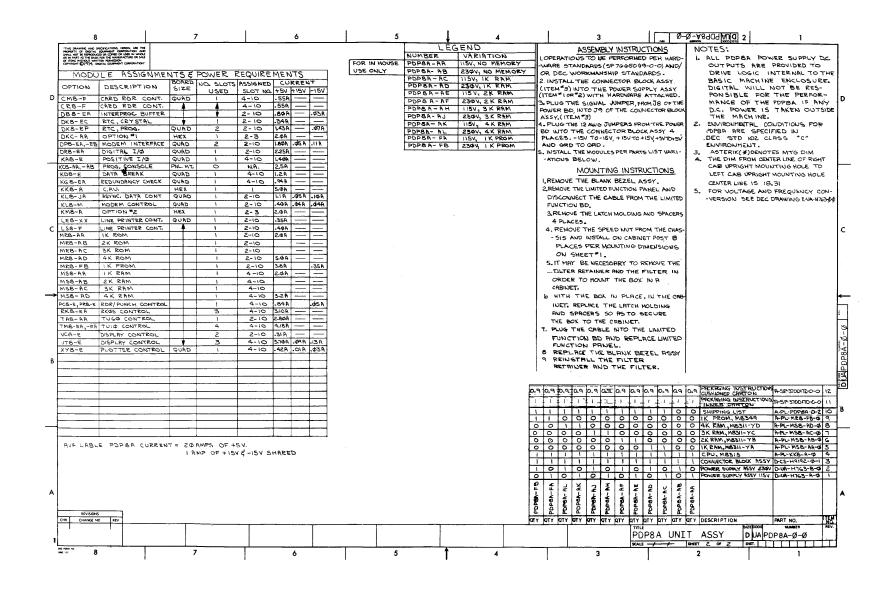

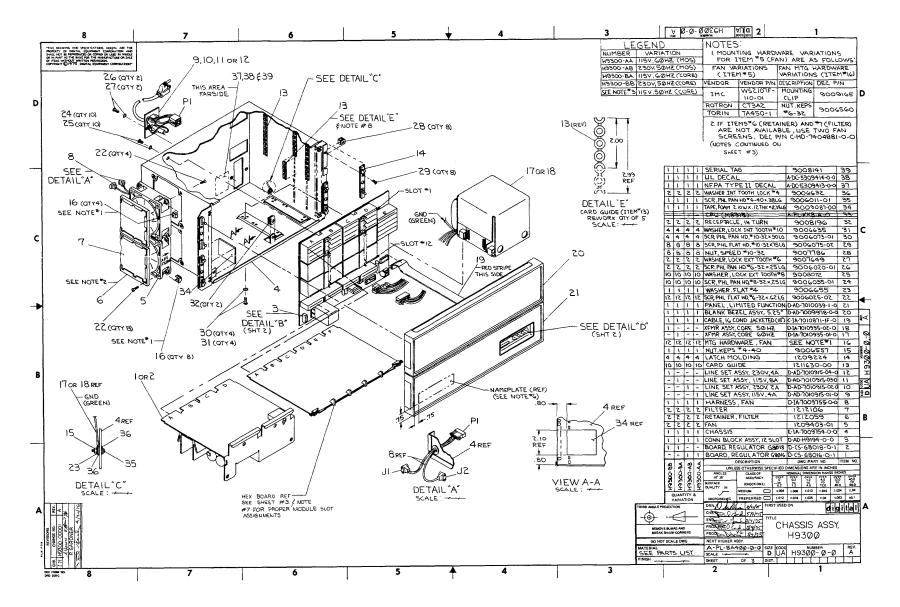

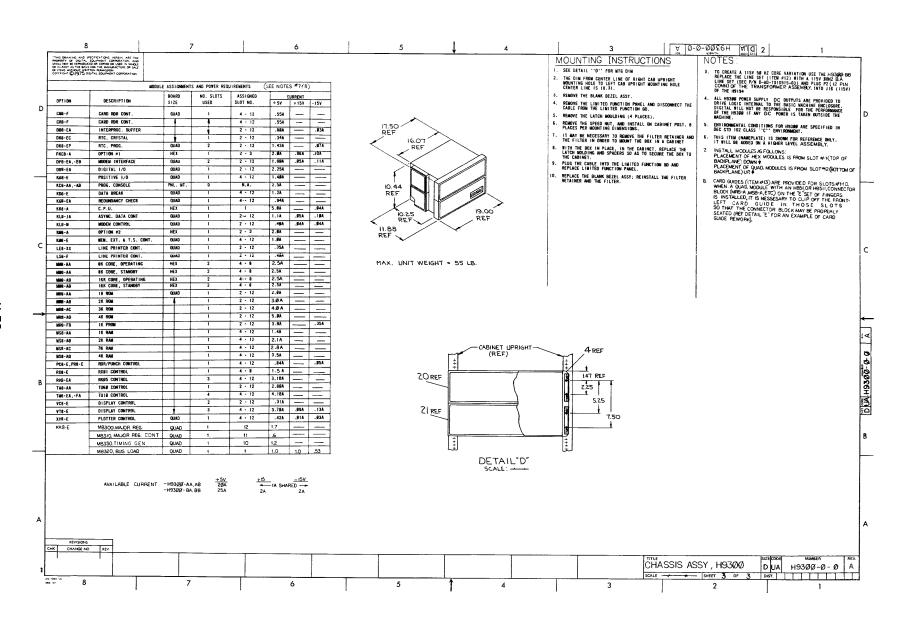

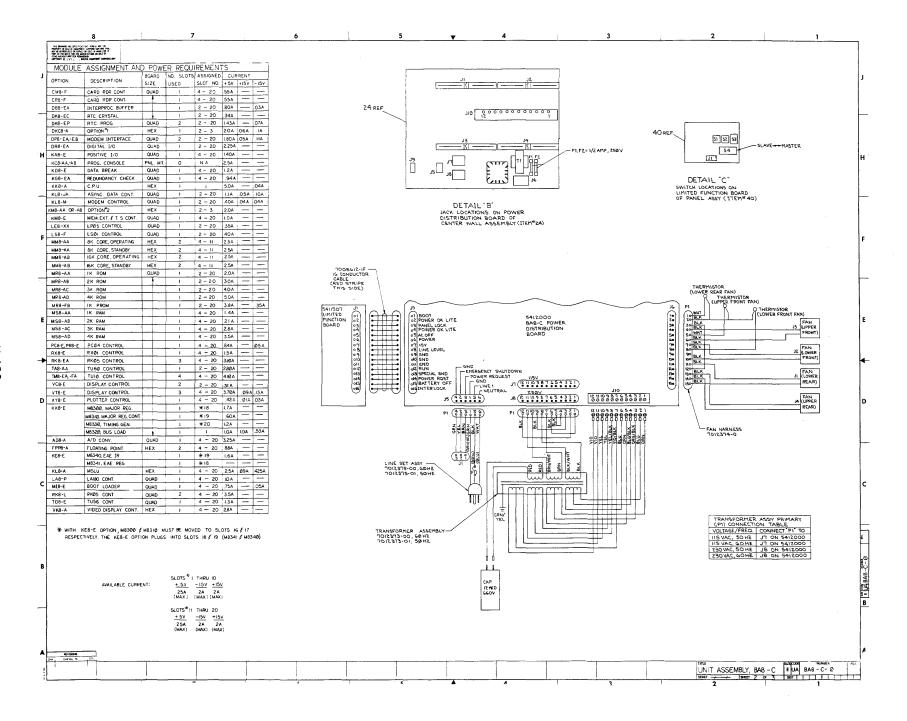

| 2.4       PDP-8/A BASIC SYSTEM COMPONENTS       2-7         2.4.1       Chassis Descriptions       2-8         2.4.2       Expansion Techniques       2-14         2.4.3       PDP-8/A Module Descriptions       2-14         2.4.3.1       KK8-A Central Processor Unit (CPU)       2-14         2.4.3.2       MS8-A Read/Write Random Access Memory (RAM)       2-16         2.4.3.3       MR8-A Read Only Random Access Memory (ROM)       2-16         2.4.3.4       MM8-AA 8K Core Memory       2-21         2.4.3.5       MM8-AB 16K Core Memory       2-21         2.4.3.6       DKC8-AA I/O Option Board       2-24         2.4.3.7       KM8-A Extended Option Board       2-28         2.4.3.8       Semiconductor Memory Power Supply       2-30         2.4.3.9       Core Memory Power Supply Regulator       2-32         2.4.3.10       Limited Function Panel       2-34                                                                                                                                                                                                                                                                                                                                          | 2.3.2     | ·                                     |        |

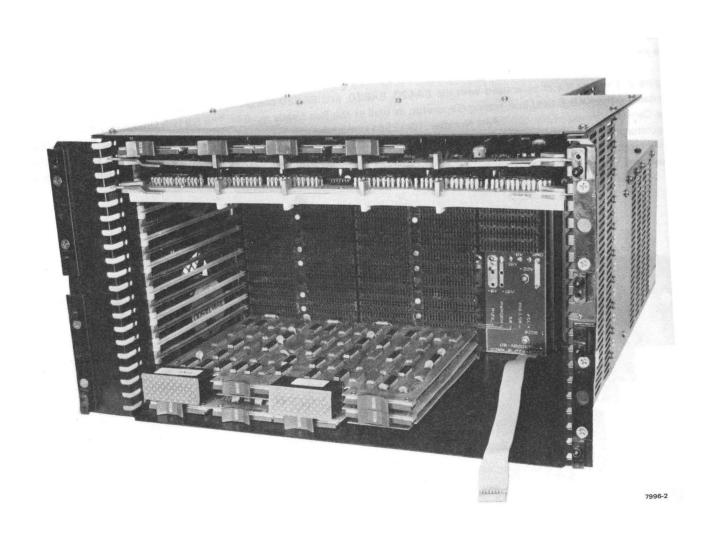

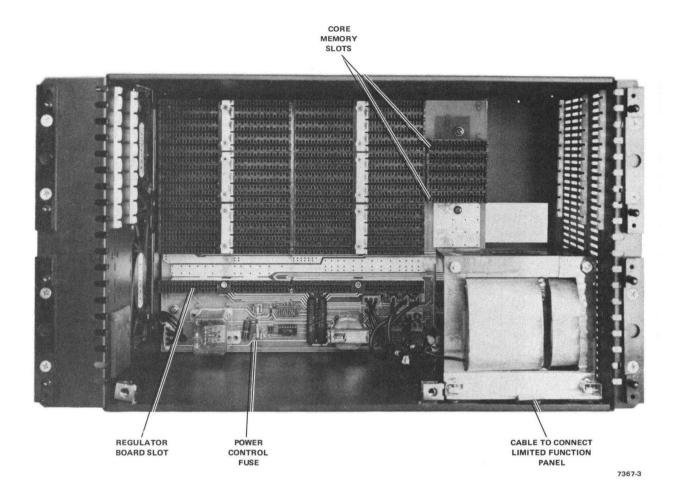

| 2.4.1       Chassis Descriptions       2-8         2.4.2       Expansion Techniques       2-14         2.4.3       PDP-8/A Module Descriptions       2-14         2.4.3.1       KK8-A Central Processor Unit (CPU)       2-14         2.4.3.2       MS8-A Read/Write Random Access Memory (RAM)       2-16         2.4.3.3       MR8-A Read Only Random Access Memory (ROM)       2-16         2.4.3.4       MM8-AA 8K Core Memory       2-21         2.4.3.5       MM8-AB 16K Core Memory       2-21         2.4.3.6       DKC8-AA I/O Option Board       2-24         2.4.3.7       KM8-A Extended Option Board       2-24         2.4.3.8       Semiconductor Memory Power Supply       2-30         2.4.3.9       Core Memory Power Supply Regulator       2-32         2.4.3.10       Limited Function Panel       2-34                                                                                                                                                                                                                                                                                                                                                                                                      | 2.4       |                                       |        |

| 2.4.2       Expansion Techniques       2-14         2.4.3       PDP-8/A Module Descriptions       2-14         2.4.3.1       KK8-A Central Processor Unit (CPU)       2-14         2.4.3.2       MS8-A Read/Write Random Access Memory (RAM)       2-16         2.4.3.3       MR8-A Read Only Random Access Memory (ROM)       2-16         2.4.3.4       MM8-AA 8K Core Memory       2-21         2.4.3.5       MM8-AB 16K Core Memory       2-21         2.4.3.6       DKC8-AA I/O Option Board       2-24         2.4.3.7       KM8-A Extended Option Board       2-28         2.4.3.8       Semiconductor Memory Power Supply       2-30         2.4.3.9       Core Memory Power Supply Regulator       2-32         2.4.3.10       Limited Function Panel       2-34                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2.4.1     |                                       |        |

| 2.4.3       PDP-8/A Module Descriptions       2-14         2.4.3.1       KK8-A Central Processor Unit (CPU)       2-14         2.4.3.2       MS8-A Read/Write Random Access Memory (RAM)       2-16         2.4.3.3       MR8-A Read Only Random Access Memory (ROM)       2-16         2.4.3.4       MM8-AA 8K Core Memory       2-21         2.4.3.5       MM8-AB 16K Core Memory       2-21         2.4.3.6       DKC8-AA I/O Option Board       2-24         2.4.3.7       KM8-A Extended Option Board       2-28         2.4.3.8       Semiconductor Memory Power Supply       2-30         2.4.3.9       Core Memory Power Supply Regulator       2-32         2.4.3.10       Limited Function Panel       2-34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2.4.2     | ·                                     |        |

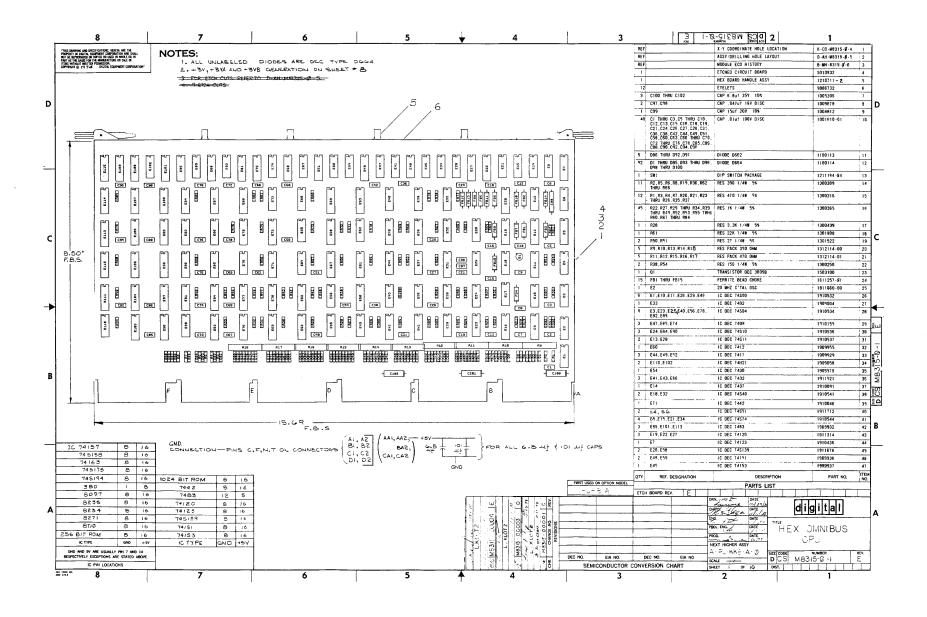

| 2.4.3.1       KK8-A Central Processor Unit (CPU)       2-14         2.4.3.2       MS8-A Read/Write Random Access Memory (RAM)       2-16         2.4.3.3       MR8-A Read Only Random Access Memory (ROM)       2-16         2.4.3.4       MM8-AA 8K Core Memory       2-21         2.4.3.5       MM8-AB 16K Core Memory       2-21         2.4.3.6       DKC8-AA I/O Option Board       2-24         2.4.3.7       KM8-A Extended Option Board       2-28         2.4.3.8       Semiconductor Memory Power Supply       2-30         2.4.3.9       Core Memory Power Supply Regulator       2-32         2.4.3.10       Limited Function Panel       2-34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |                                       |        |

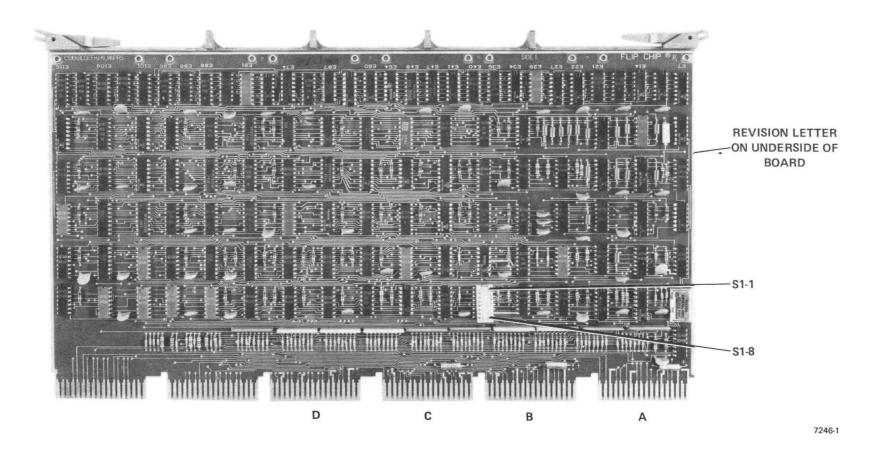

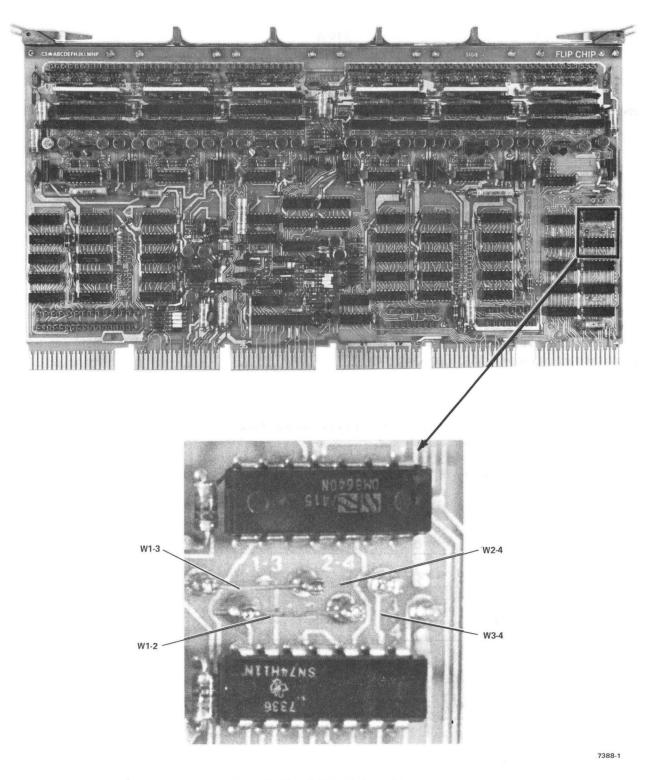

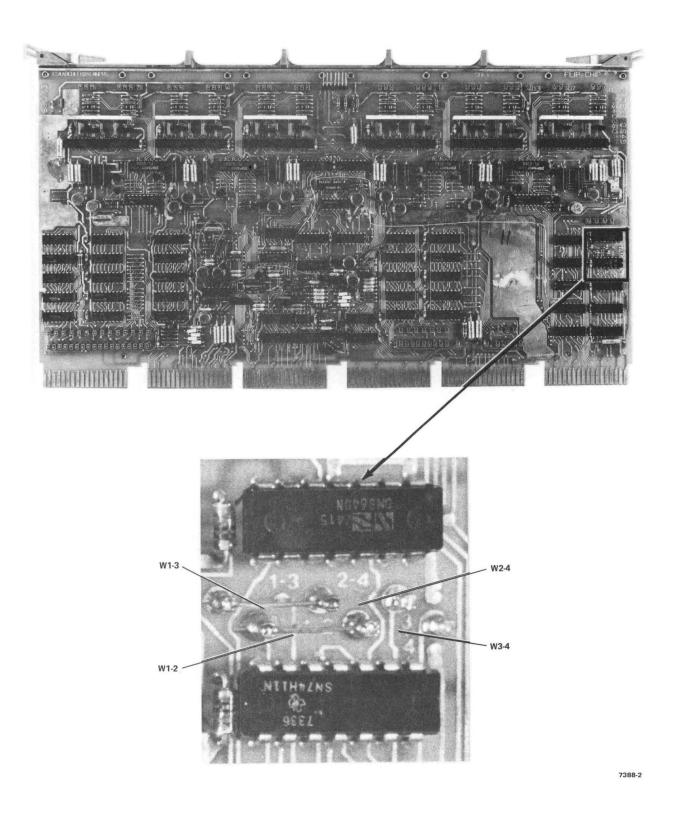

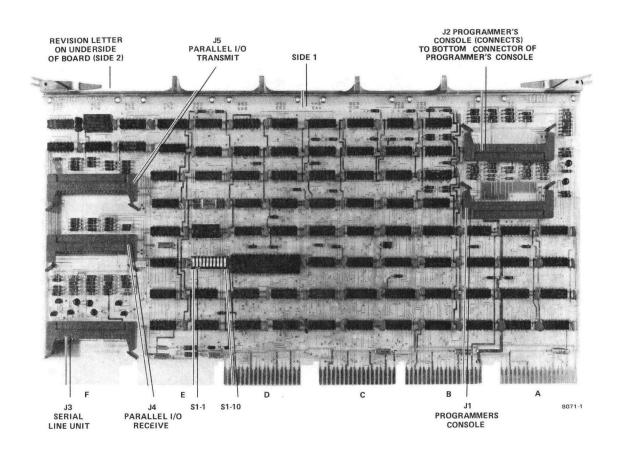

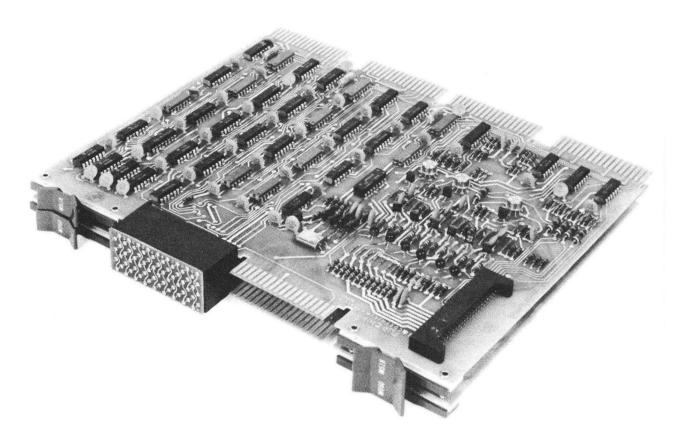

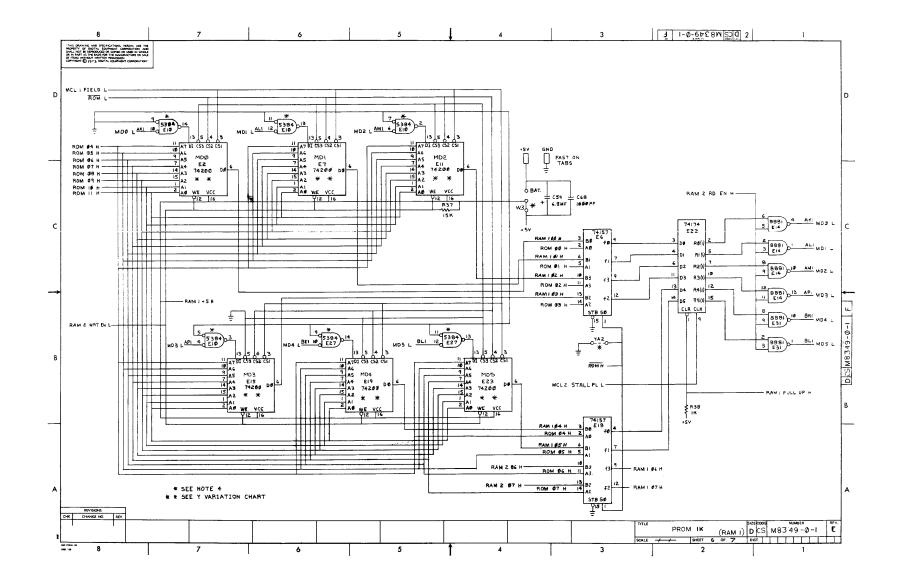

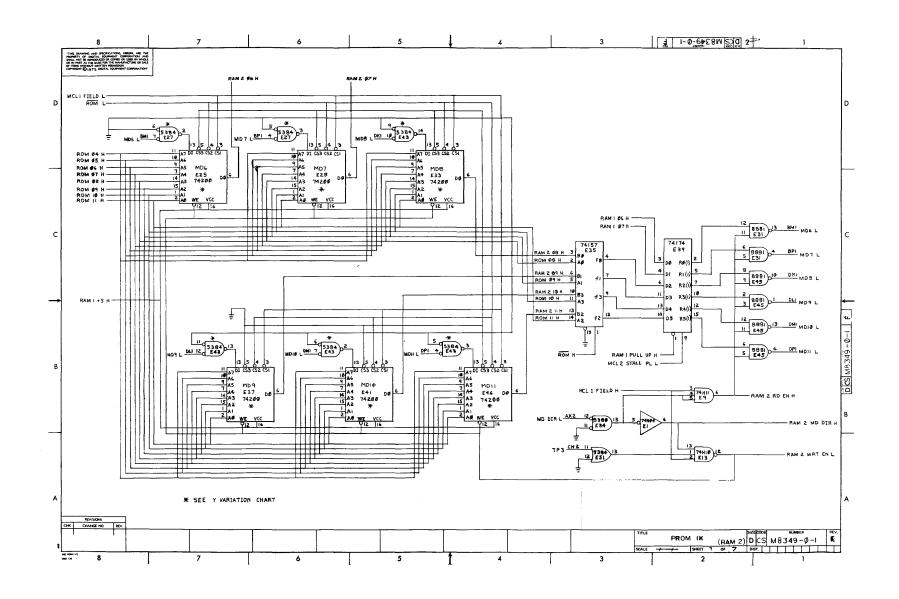

| 2.4.3.2       MS8-A Read/Write Random Access Memory (RAM)       2-16         2.4.3.3       MR8-A Read Only Random Access Memory (ROM)       2-16         2.4.3.4       MM8-AA 8K Core Memory       2-21         2.4.3.5       MM8-AB 16K Core Memory       2-21         2.4.3.6       DKC8-AA I/O Option Board       2-24         2.4.3.7       KM8-A Extended Option Board       2-28         2.4.3.8       Semiconductor Memory Power Supply       2-30         2.4.3.9       Core Memory Power Supply Regulator       2-32         2.4.3.10       Limited Function Panel       2-34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2.4.3.1   |                                       |        |

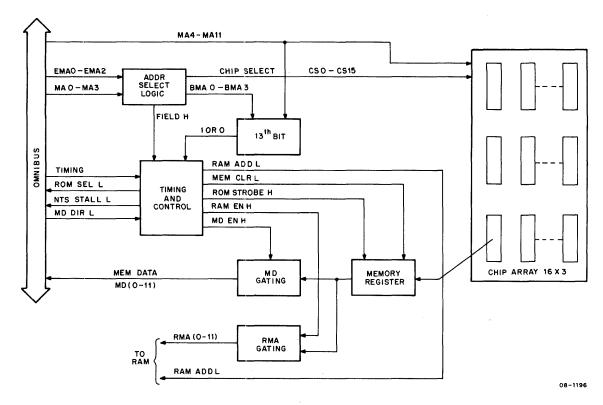

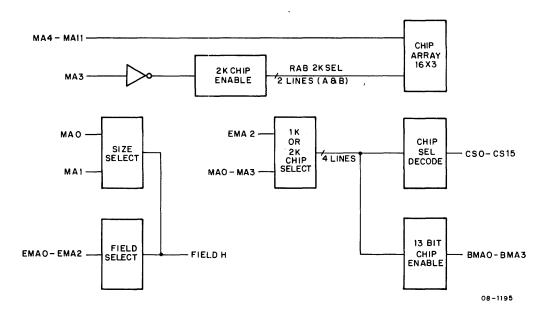

| 2.4.3.3       MR8-A Read Only Random Access Memory (ROM)       2-16         2.4.3.4       MM8-AA 8K Core Memory       2-21         2.4.3.5       MM8-AB 16K Core Memory       2-21         2.4.3.6       DKC8-AA I/O Option Board       2-24         2.4.3.7       KM8-A Extended Option Board       2-28         2.4.3.8       Semiconductor Memory Power Supply       2-30         2.4.3.9       Core Memory Power Supply Regulator       2-32         2.4.3.10       Limited Function Panel       2-34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           | ·                                     |        |

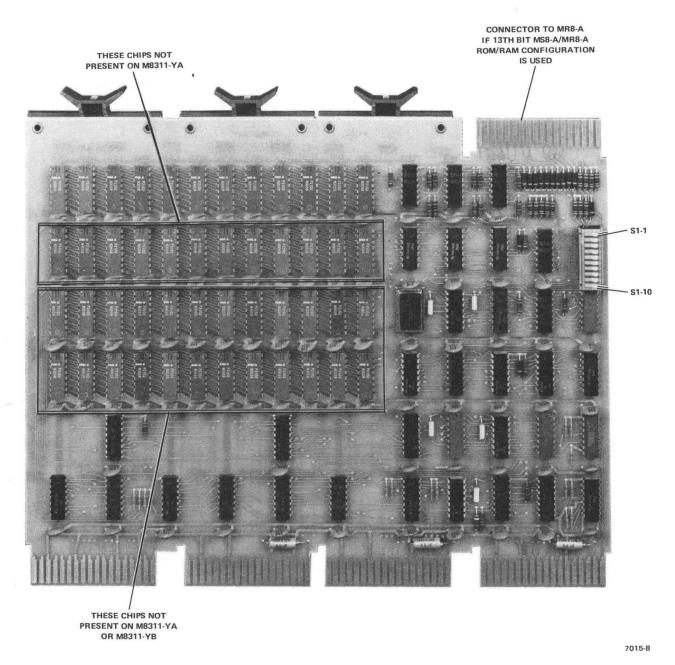

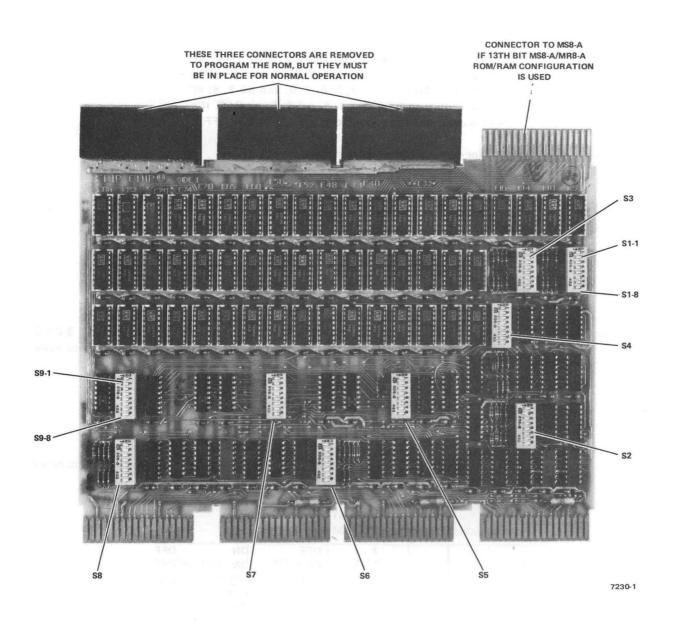

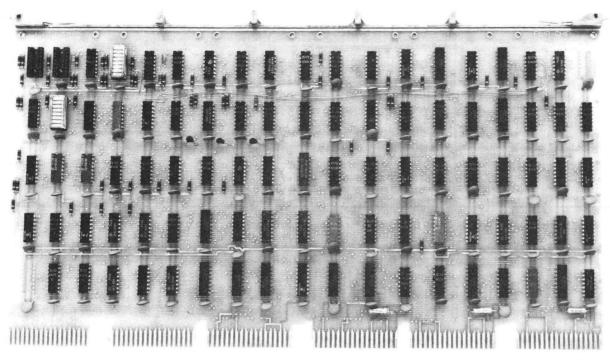

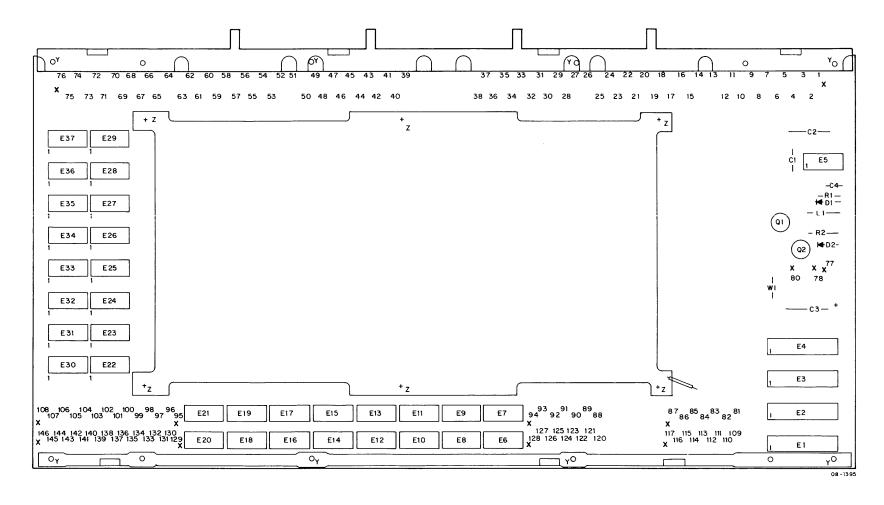

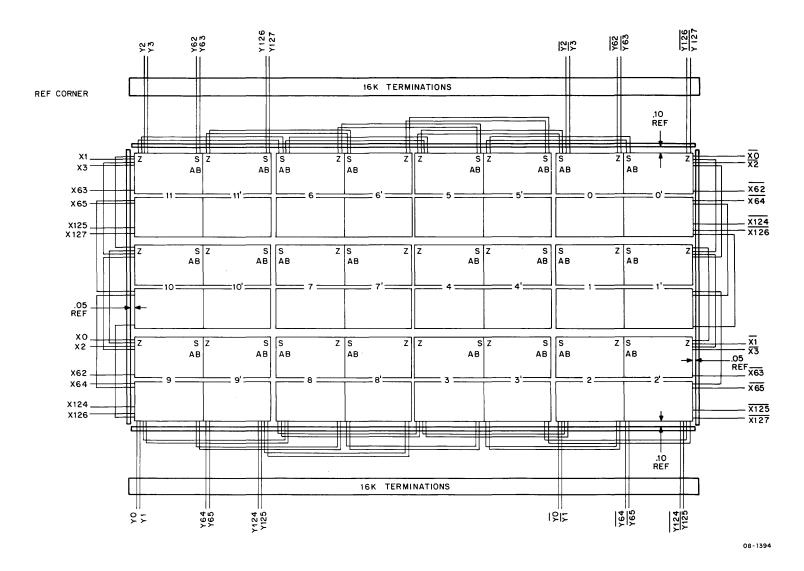

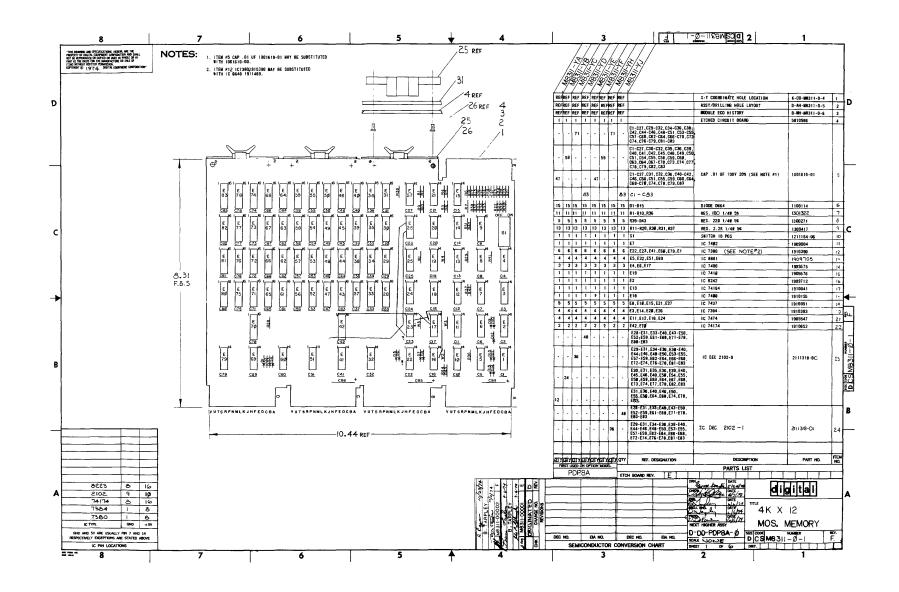

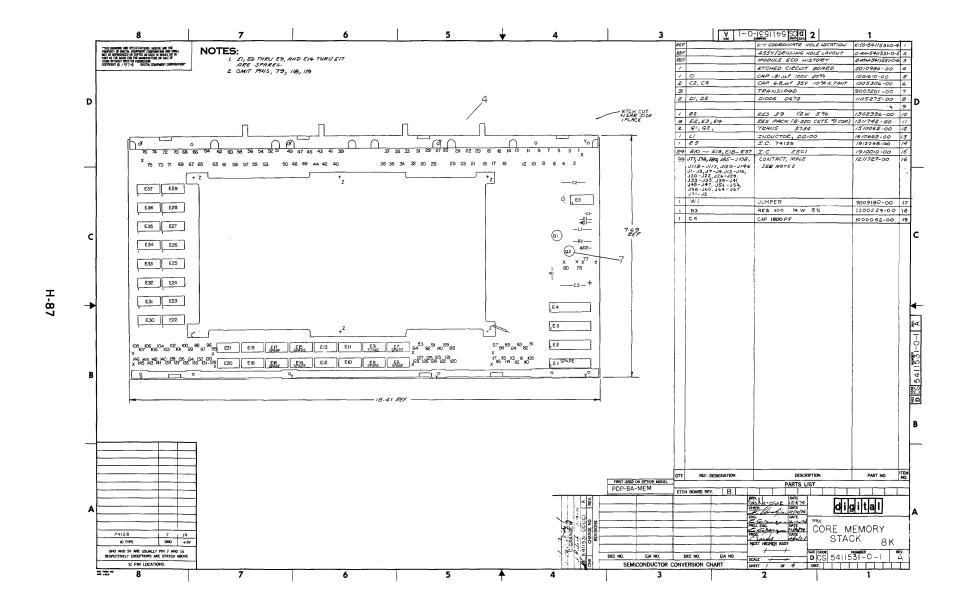

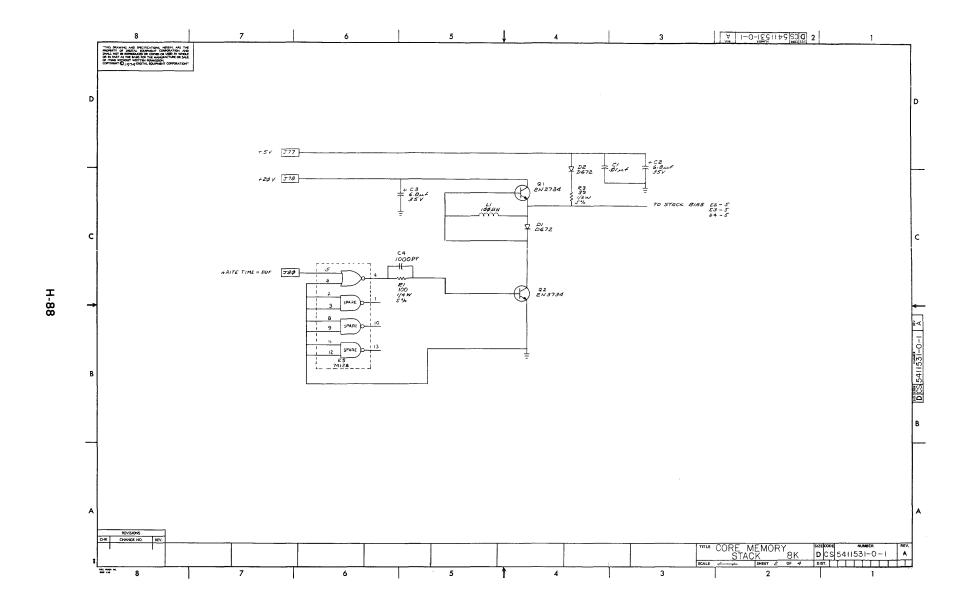

| 2.4.3.4       MM8-AA 8K Core Memory       2-21         2.4.3.5       MM8-AB 16K Core Memory       2-21         2.4.3.6       DKC8-AA I/O Option Board       2-24         2.4.3.7       KM8-A Extended Option Board       2-28         2.4.3.8       Semiconductor Memory Power Supply       2-30         2.4.3.9       Core Memory Power Supply Regulator       2-32         2.4.3.10       Limited Function Panel       2-34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           | •                                     |        |

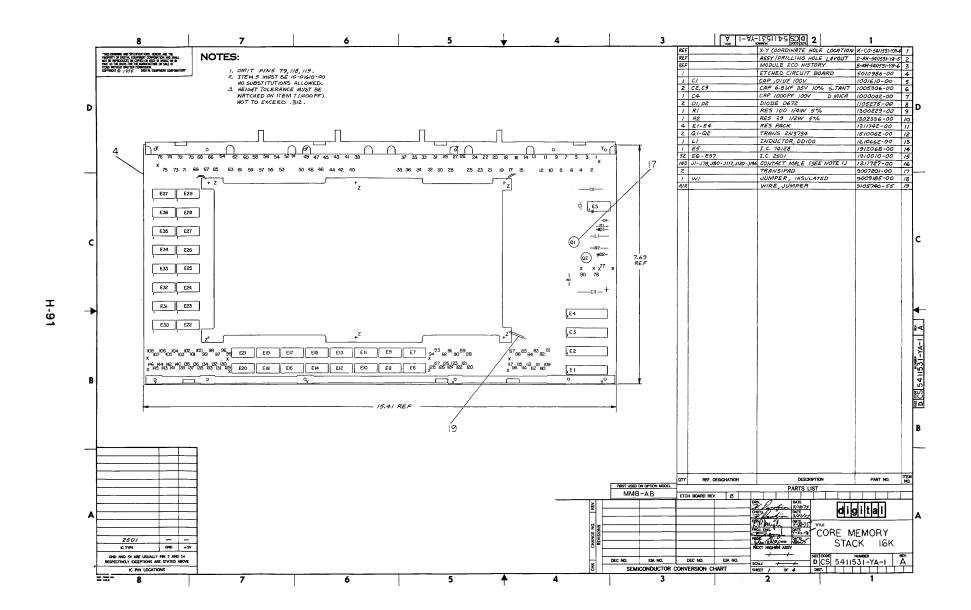

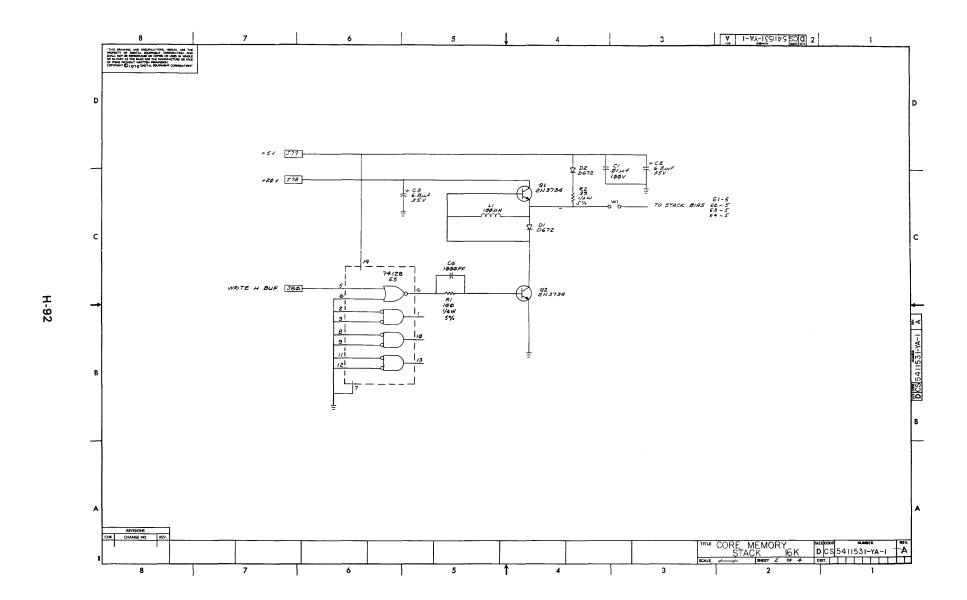

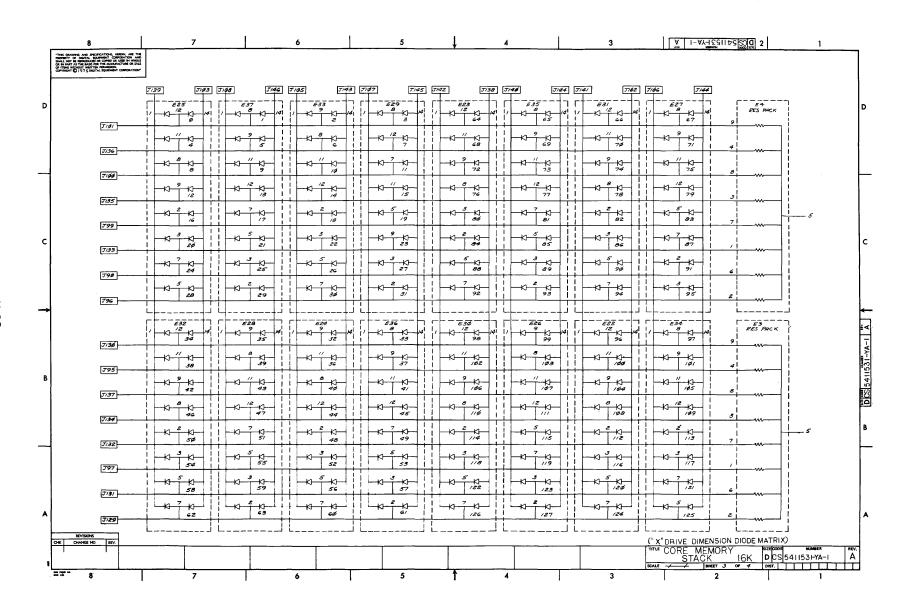

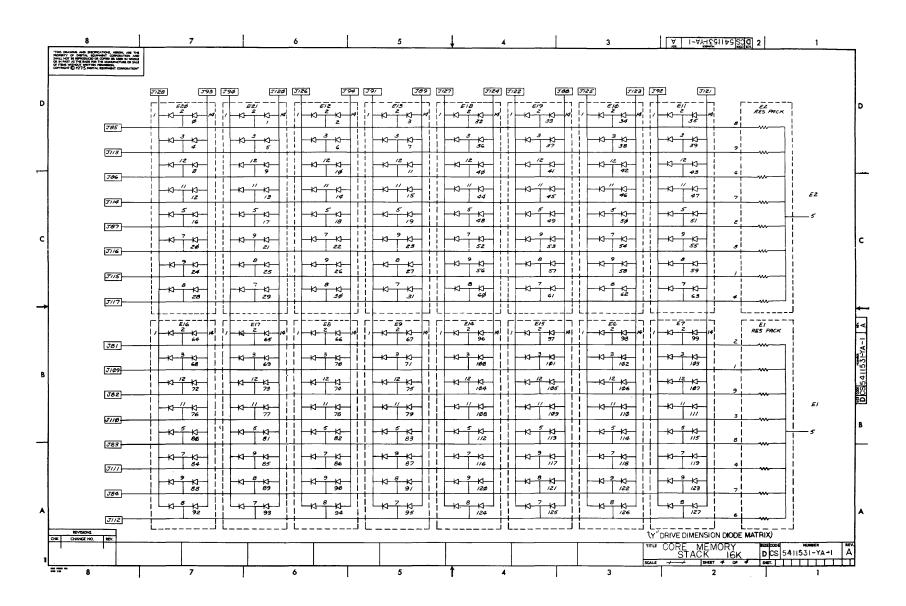

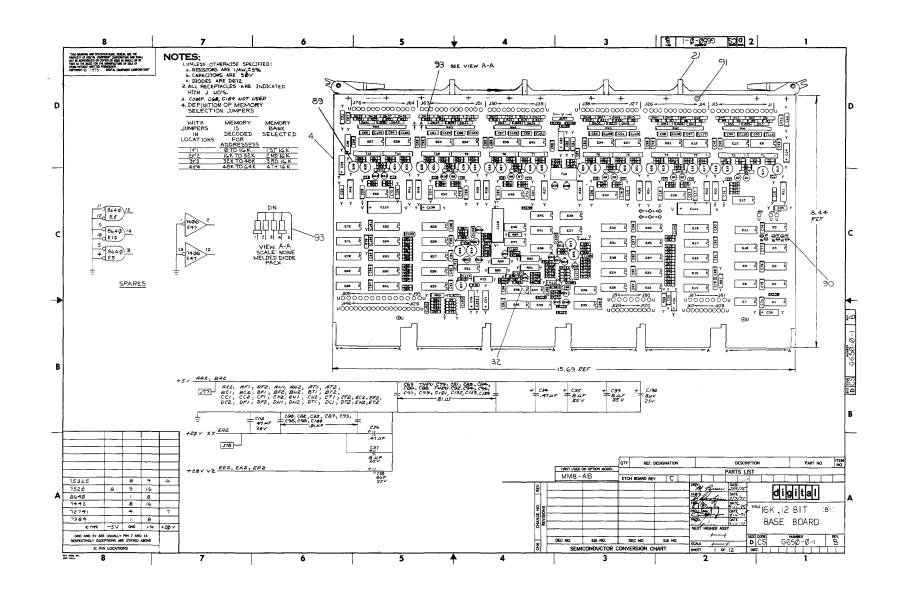

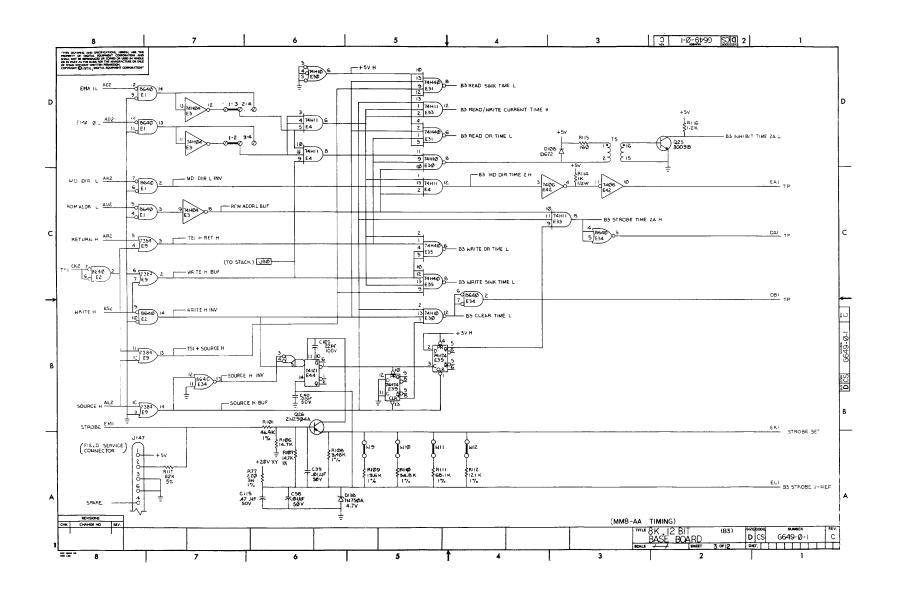

| 2.4.3.5       MM8-AB 16K Core Memory       2-21         2.4.3.6       DKC8-AA I/O Option Board       2-24         2.4.3.7       KM8-A Extended Option Board       2-28         2.4.3.8       Semiconductor Memory Power Supply       2-30         2.4.3.9       Core Memory Power Supply Regulator       2-32         2.4.3.10       Limited Function Panel       2-34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           | · · · · · · · · · · · · · · · · · · · |        |

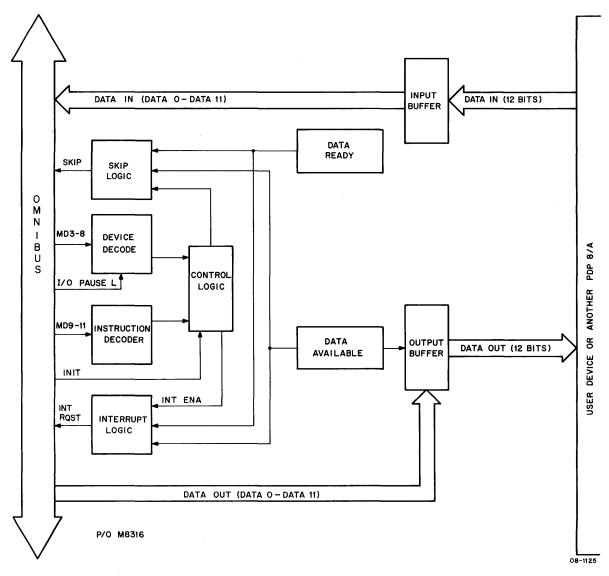

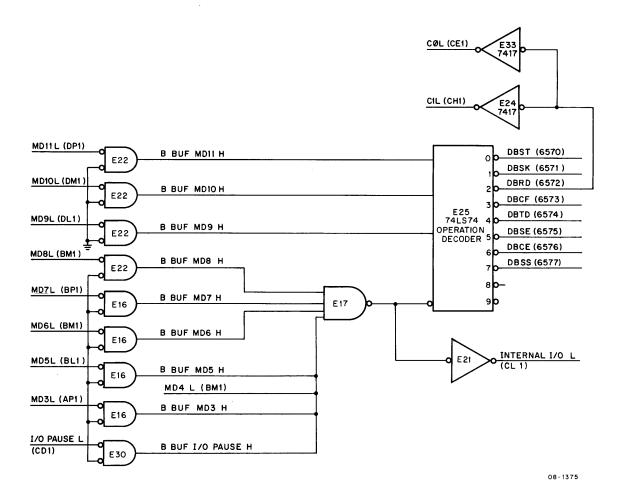

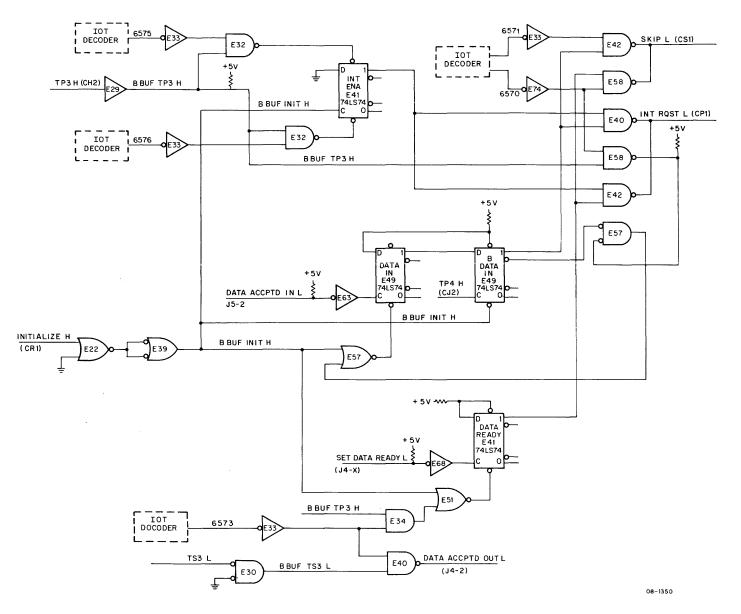

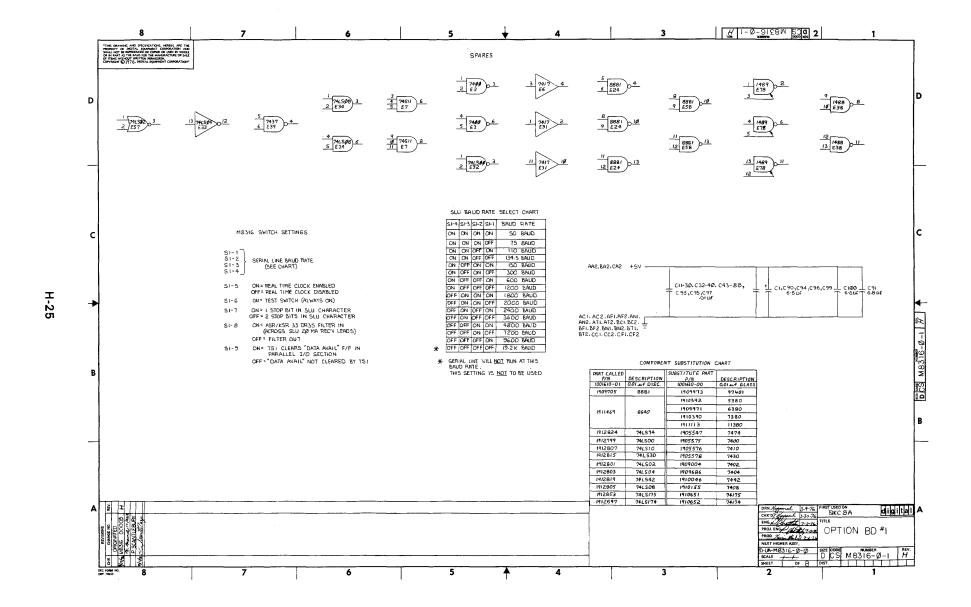

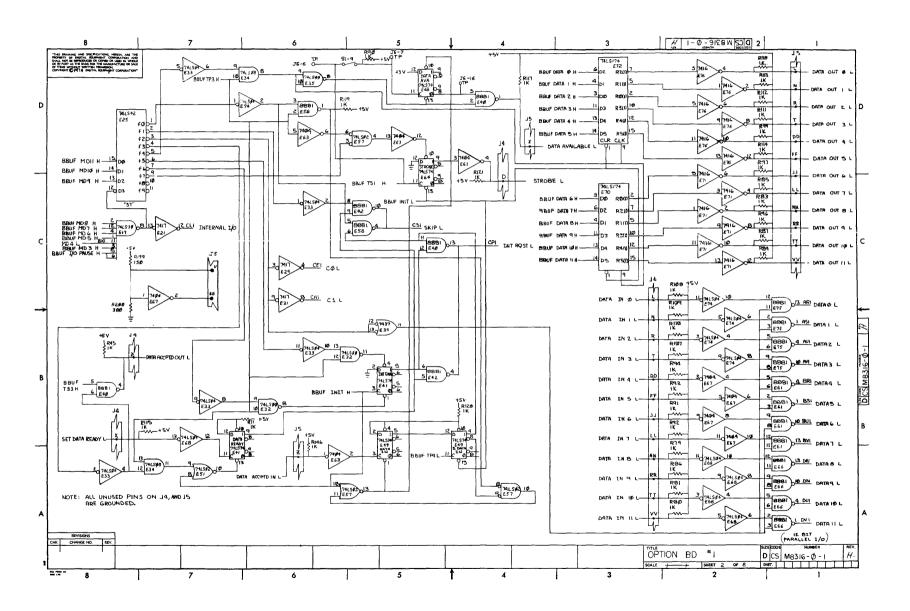

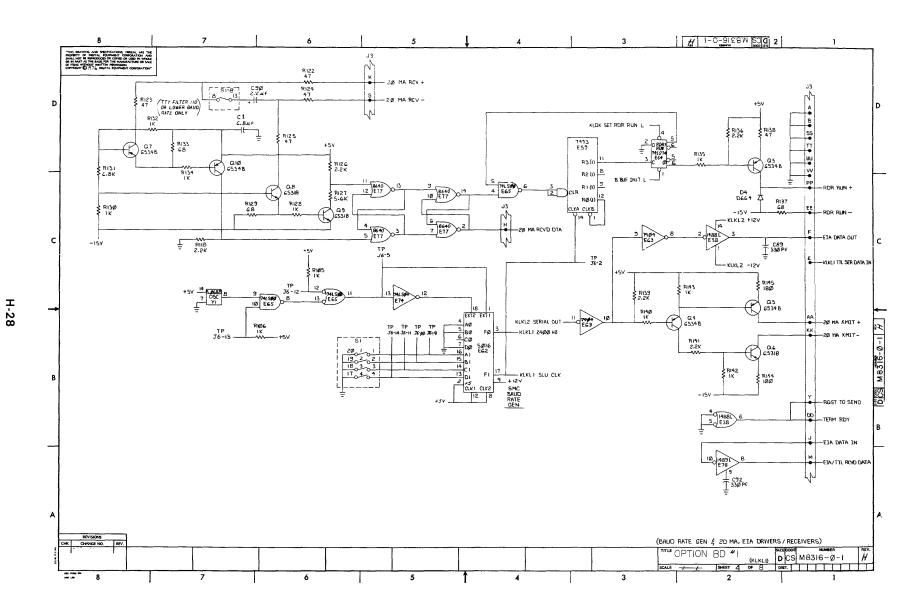

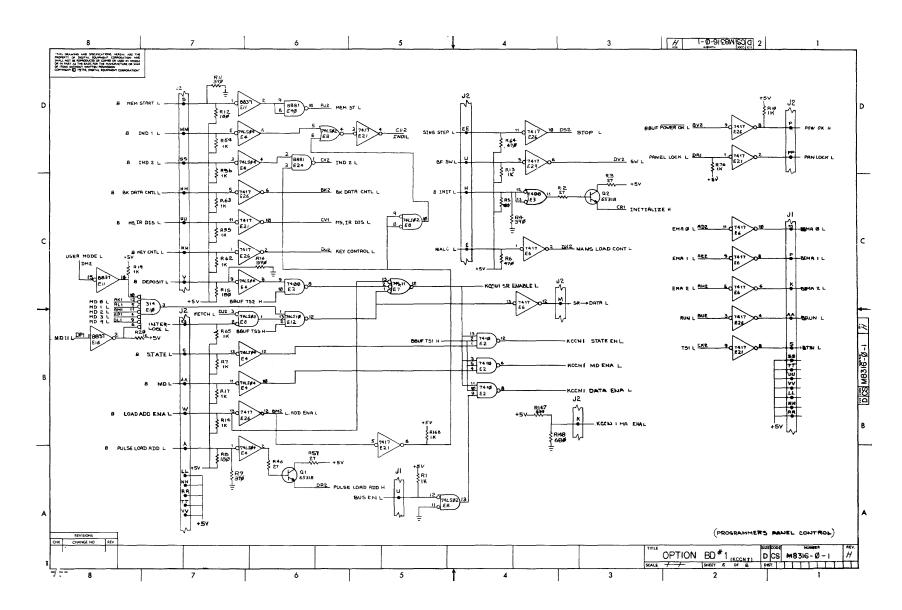

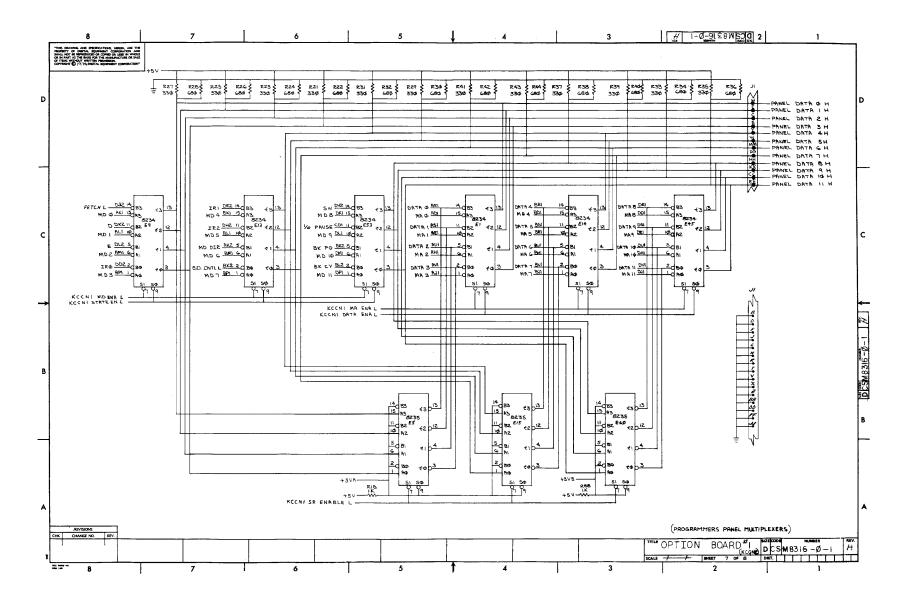

| 2.4.3.6       DKC8-AA I/O Option Board       2-24         2.4.3.7       KM8-A Extended Option Board       2-28         2.4.3.8       Semiconductor Memory Power Supply       2-30         2.4.3.9       Core Memory Power Supply Regulator       2-32         2.4.3.10       Limited Function Panel       2-34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           | ·                                     |        |

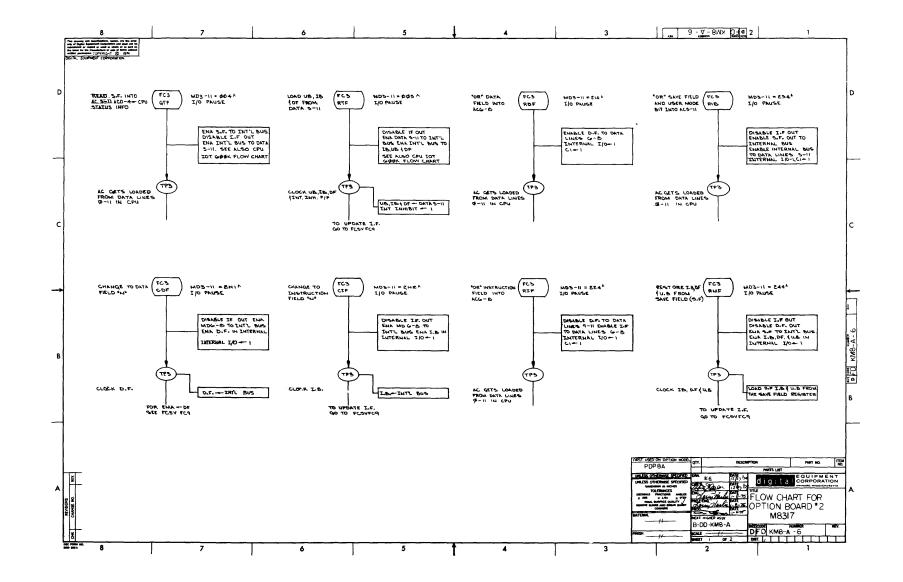

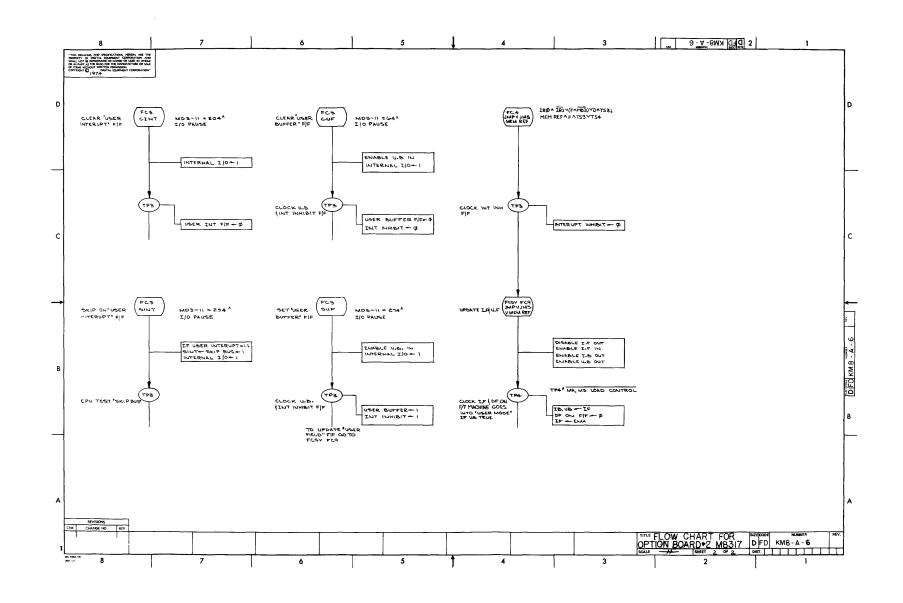

| 2.4.3.7KM8-A Extended Option Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           | · ·                                   |        |

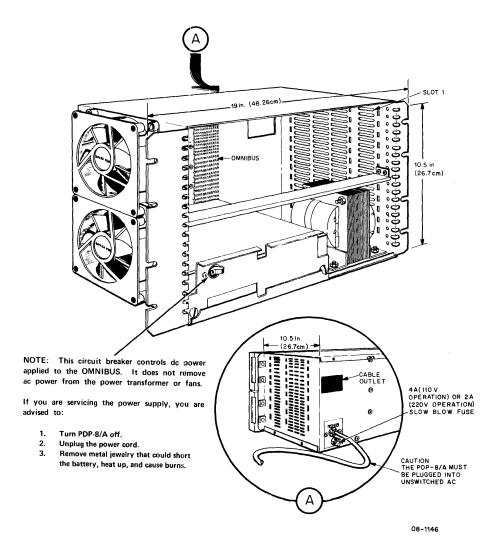

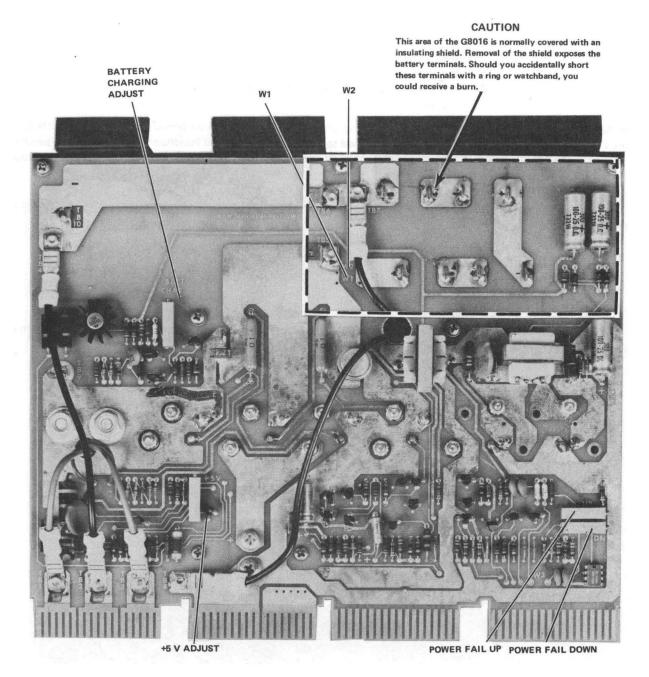

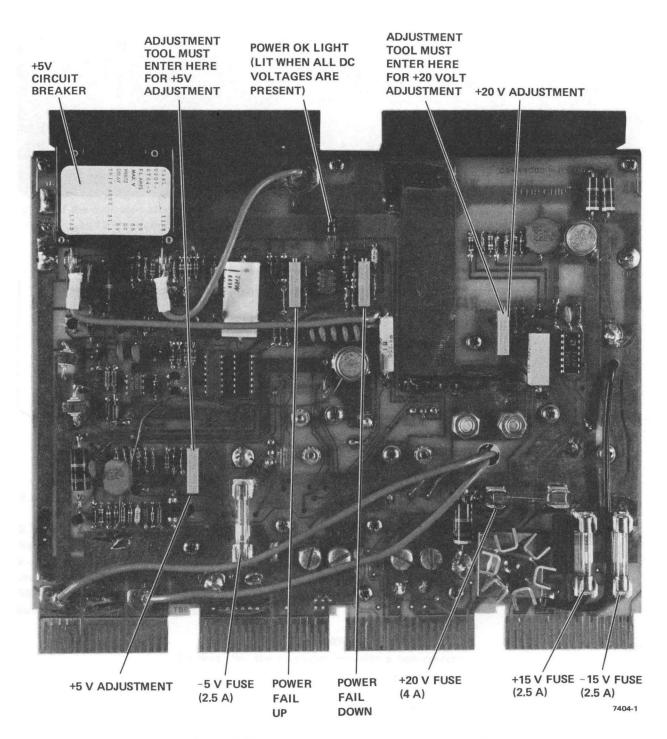

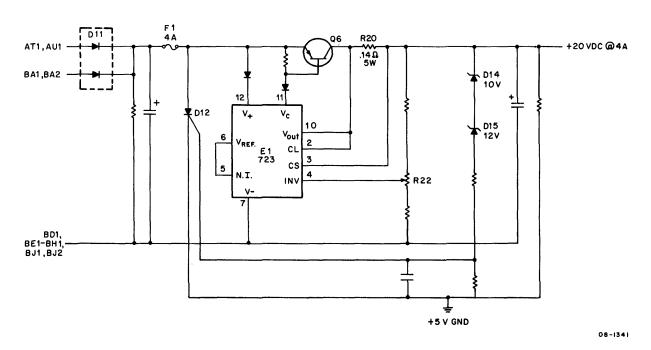

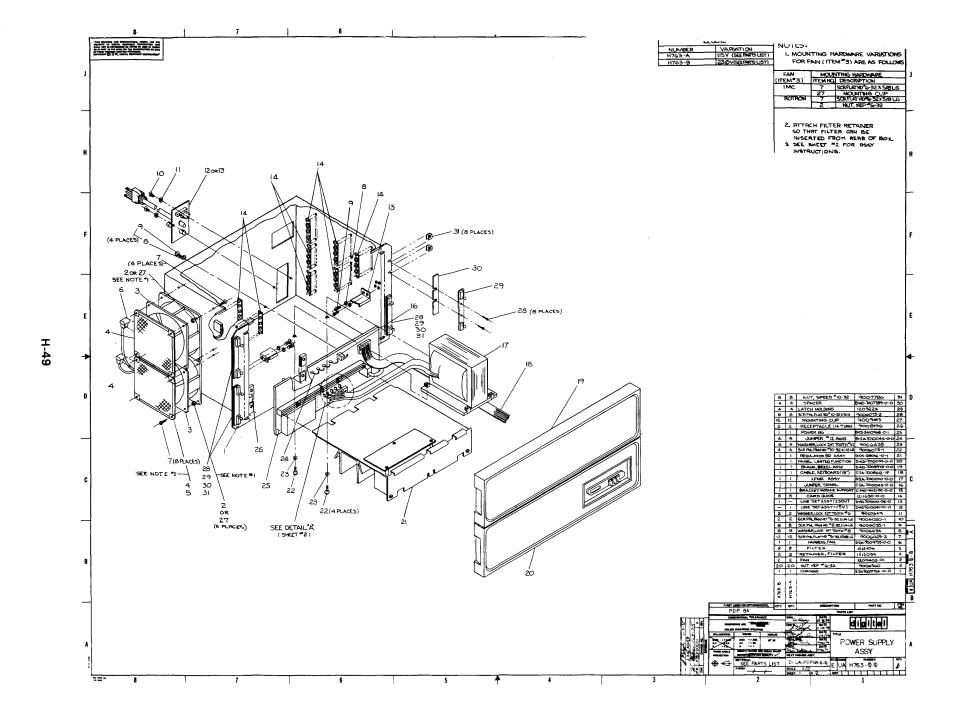

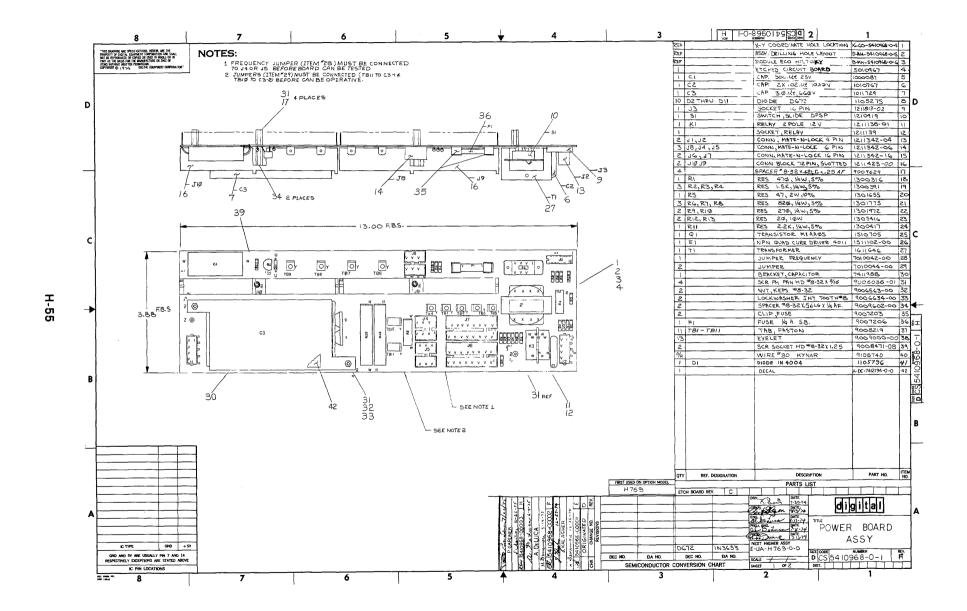

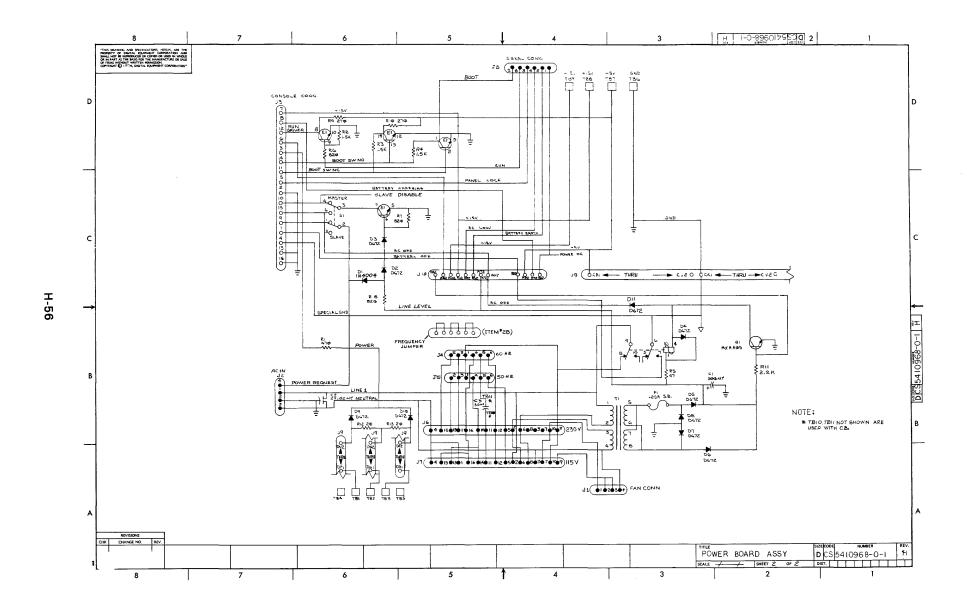

| 2.4.3.8Semiconductor Memory Power Supply2-302.4.3.9Core Memory Power Supply Regulator2.4.3.10Limited Function Panel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |                                       |        |

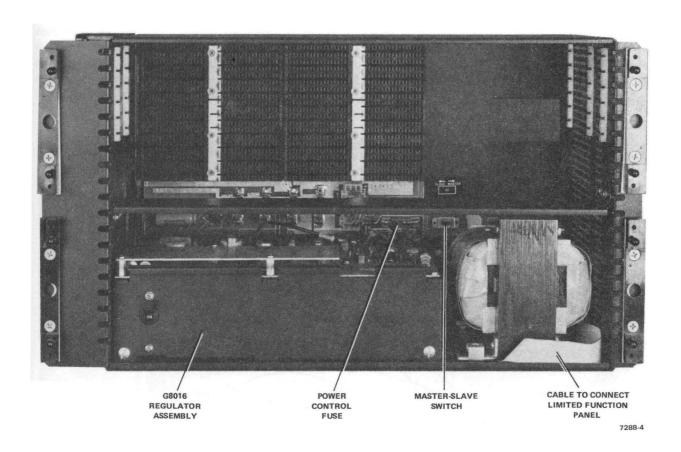

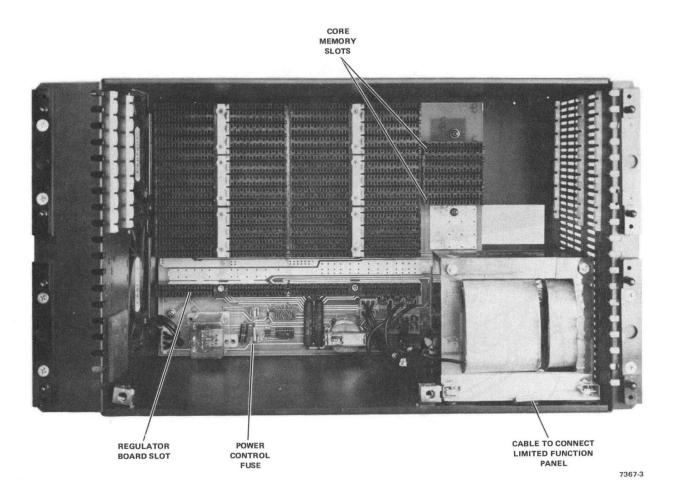

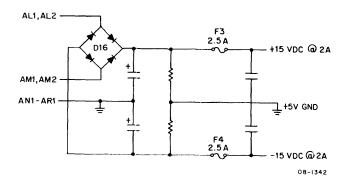

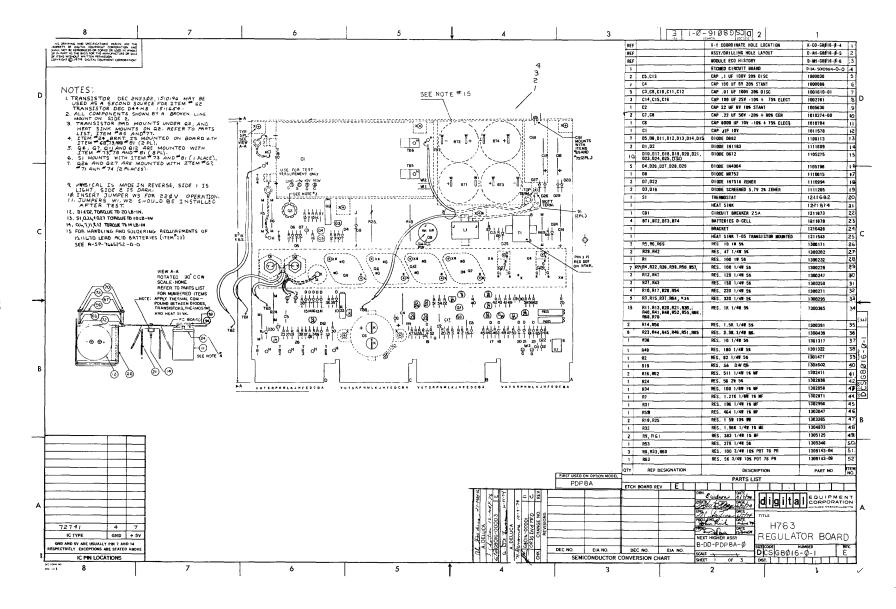

| 2.4.3.9       Core Memory Power Supply Regulator       2.4.3.10         Limited Function Panel       2.34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           | ·                                     |        |

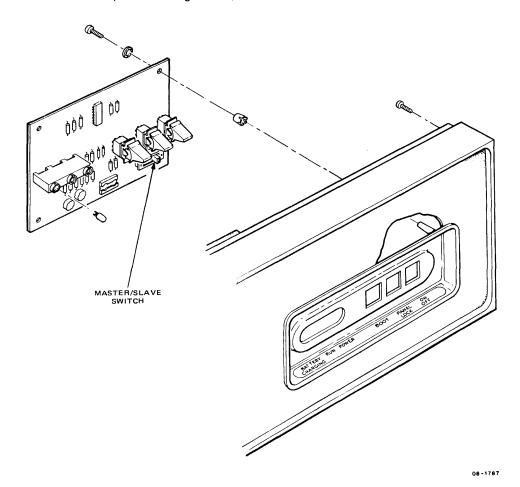

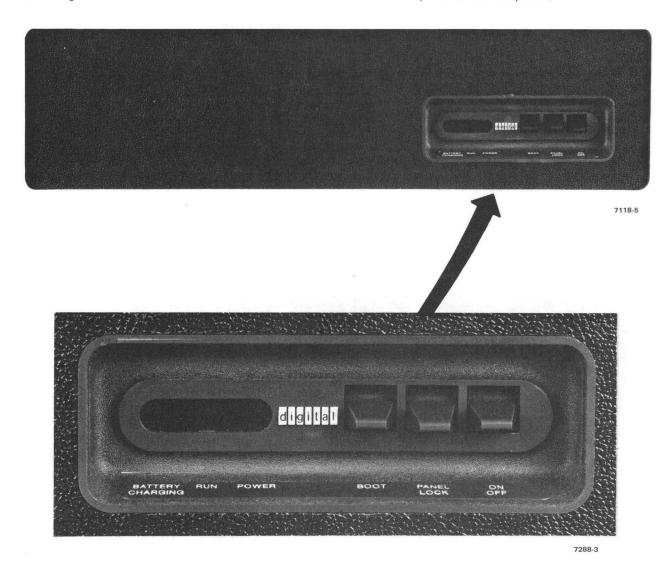

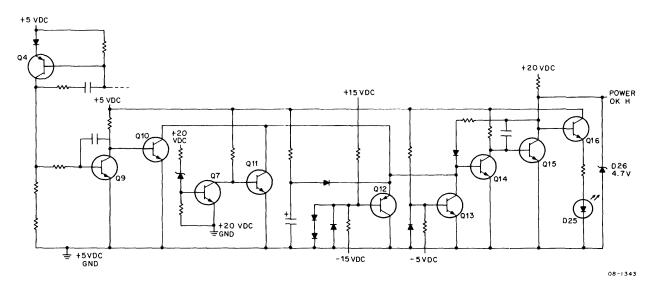

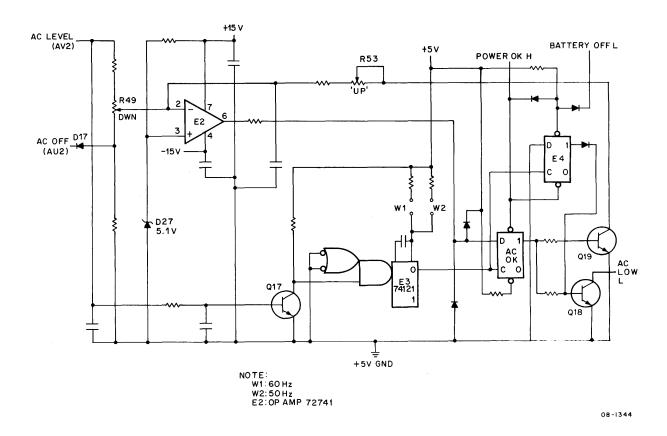

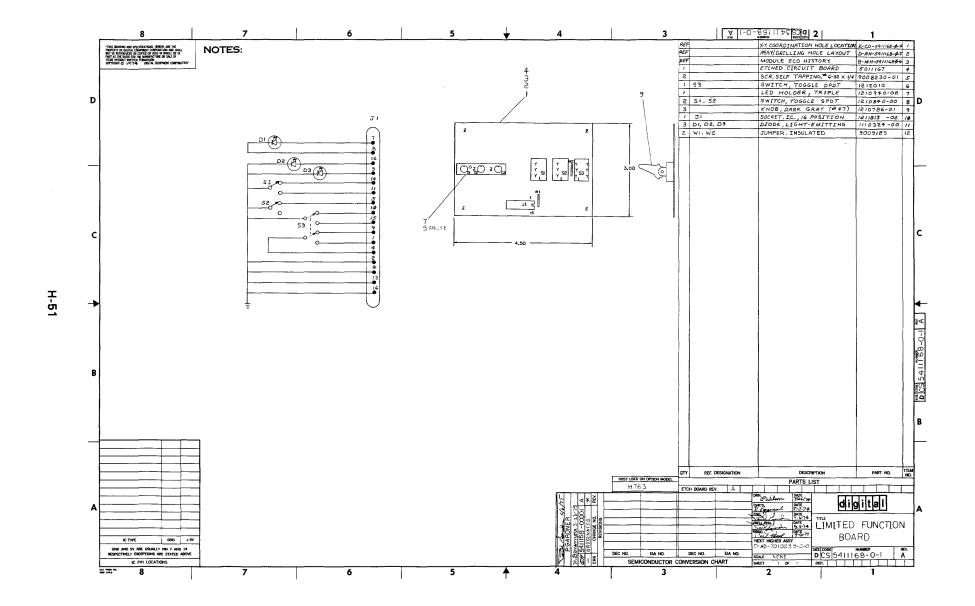

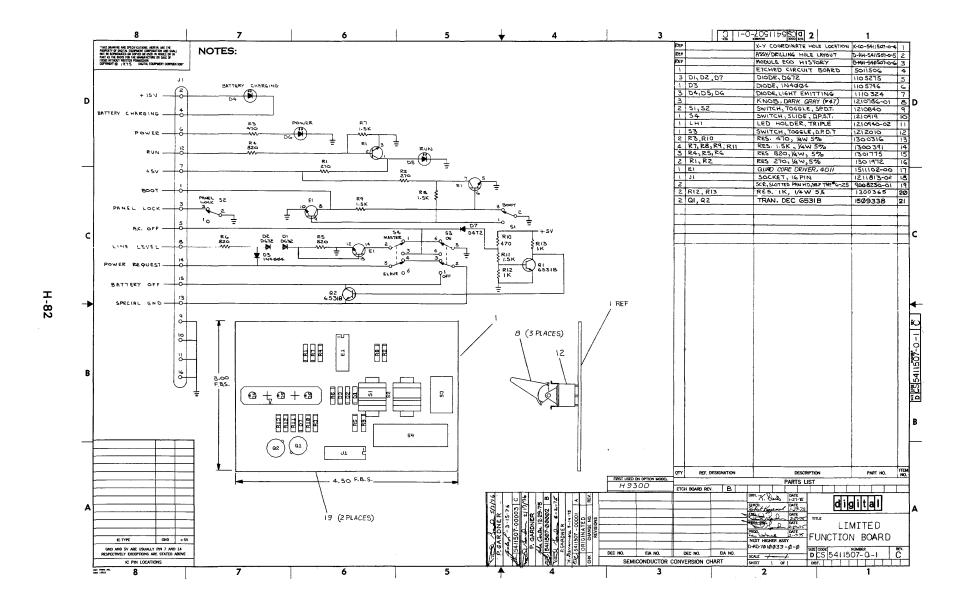

| 2.4.3.10 Limited Function Panel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |                                       |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           | · · · · · · · · · · · · · · · · · · · |        |

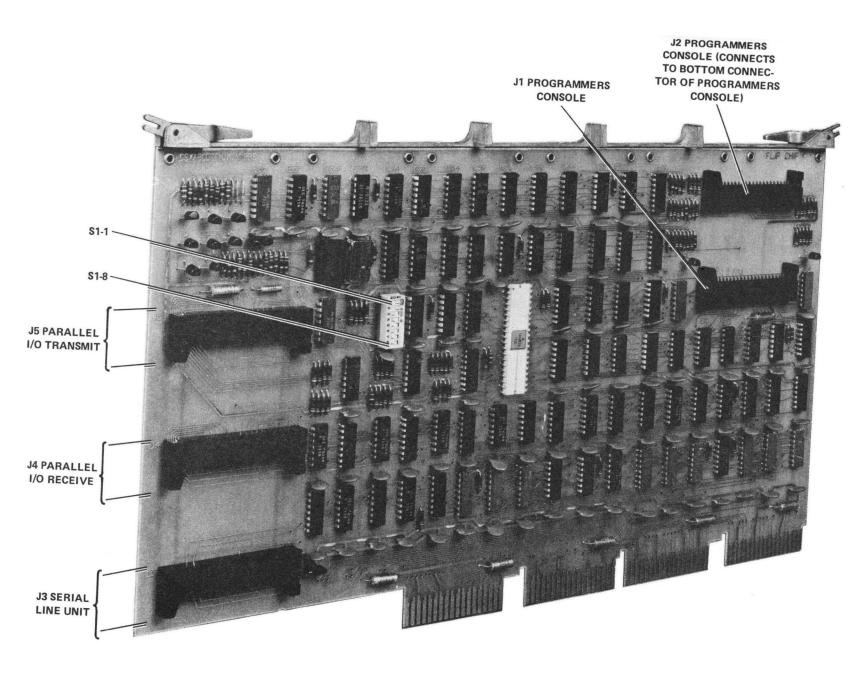

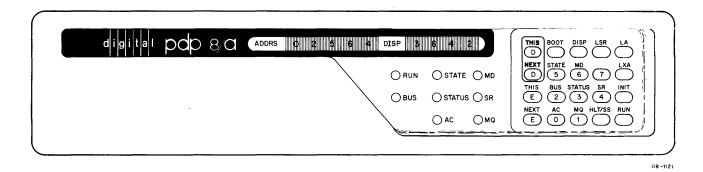

| 2.4.3.11 KC8-AA Programmer's Console 2-35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2.4.3.11  | KC8-AA Programmer's Console           |        |

|           |                                                                | Page   |

|-----------|----------------------------------------------------------------|--------|

| 2.5       | INSTALLING THE PDP-8/A AND TURNING POWER ON FOR THE FIRST TIME | . 2-35 |

| 2.5.1     | Environmental and Power Requirements                           | . 2-35 |

| 2.5.2     | Turning on the Computer for the First Time                     | . 2-35 |

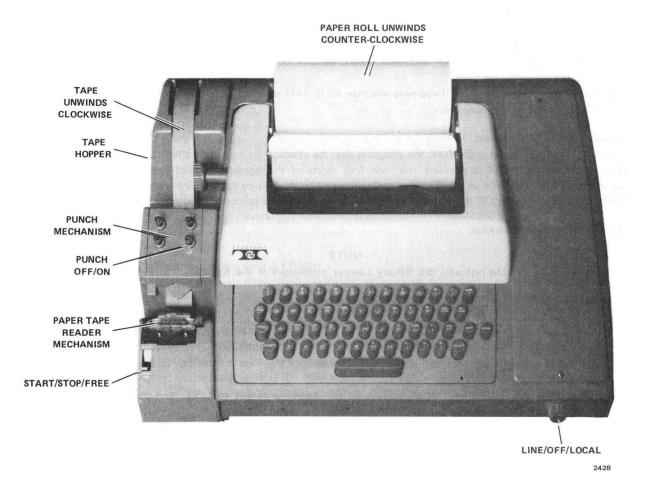

| 2.6       | TESTING PDP-8/A WITHOUT PAPER TAPE DIAGNOSTICS                 |        |

| 2.6.1     | Programmer's Console                                           | . 2-37 |

| 2.6.2     | Central Processor Test Routines                                |        |

| 2.6.3     | Entering Test Routines from the Programmer's Console           | . 2-38 |

| 2.6.4     | Central Processor Test Routines                                |        |

| 2.7       | LOADING THE RIM AND BINARY LOADERS                             |        |

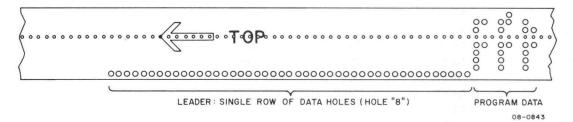

| 2.7.1     | Loading the RIM Loader                                         |        |

| 2.7.2     | Checking the RIM Loader                                        |        |

| 2.7.3     | Loading the Binary Loader                                      |        |

| 2.7.4     | Loading Binary Formatted Paper Tapes                           |        |

| 2.8       | TESTING THE PDP-8/A USING MAINDEC DIAGNOSTIC PROGRAMS          |        |

| 2.8.1     | Central Processor Unit (CPU) Test                              |        |

| 2.9       | ADDITIONAL DIAGNOSTIC TESTS                                    |        |

| 2.9.1     | Memory Test                                                    |        |

| 2.9.2     | DKC8-AA Test                                                   |        |

| 2.9.3     | KM8-A Extended Option Board Test                               |        |

|           |                                                                |        |

| 2.9.4     | Testing Extended Memories                                      |        |

| 2.10      | BASIC PDP-8/A MAINTENANCE                                      | . 2-55 |

| CHAPTER 3 | INTERFACING TO THE OMNIBUS                                     |        |

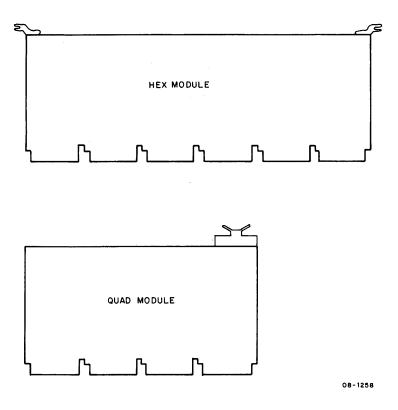

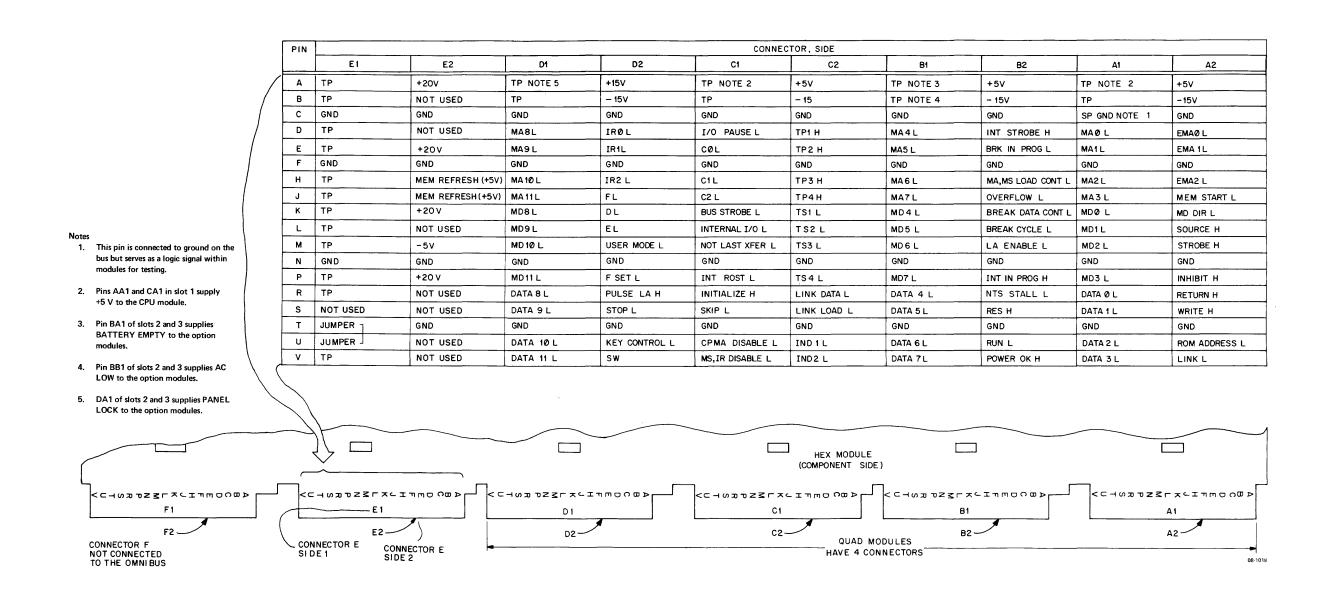

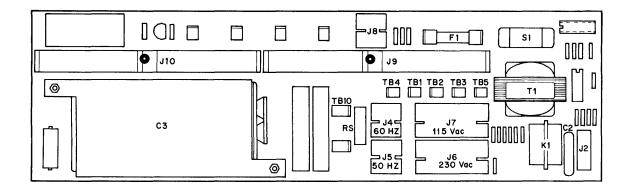

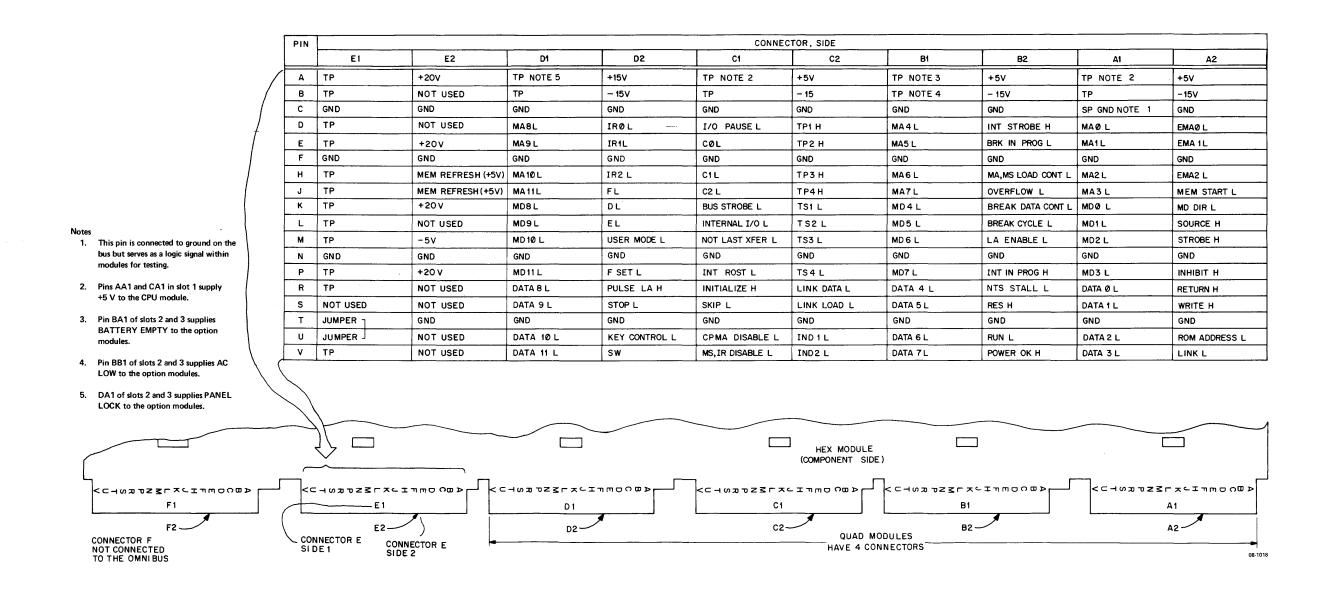

| 3.1       | OMNIBUS PHYSICAL DESCRIPTION                                   | . 3-1  |

| 3.2       | BUS SPECIFICATIONS                                             | . 3-3  |

| 3.3       | METHODS OF DATA TRANSFER                                       | . 3-3  |

| 3.3.1     | Programmed I/O Transfer                                        | . 3-3  |

| 3.3.2     | Interrupt Facility                                             |        |

| 3.3.3     | Data Break Transfer                                            |        |

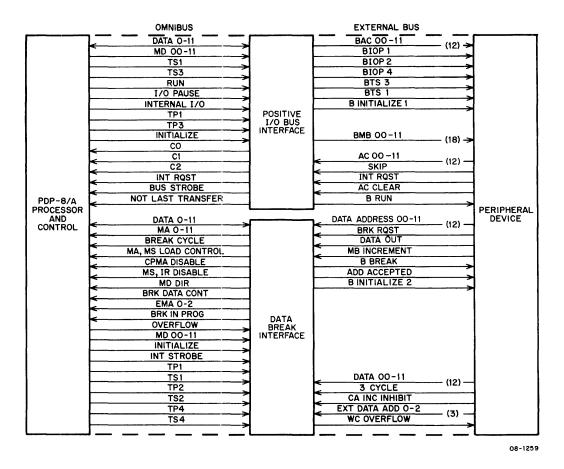

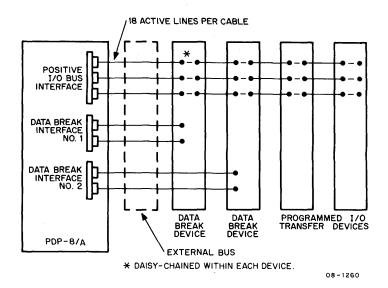

| 3.3.4     | The External Bus                                               |        |

| 3.4       | MODULE CONFIGURATION ON THE OMNIBUS                            |        |

| 3.5       | OMNIBUS PIN ASSIGNMENT                                         |        |

| 3.6       | MAJOR GROUPS OF SIGNALS                                        |        |

| 3.6.1     | Memory Address — 15 Lines                                      |        |

| 3.6.2     | Memory Data and Memory Direction Control — 13 Lines            |        |

| 3.6.2.1   | MD<0:11>L                                                      |        |

| 3.6.2.2   | MD DIR L                                                       |        |

| 3.6.3     | Data Bus — 12 Lines                                            |        |

| 3.6.4     | I/O Control Signals — 10 Lines                                 |        |

| 3.6.5     | DMA Control Signals — 8 Lines                                  |        |

| 3.6.6     | Timing Signals — 9 Lines                                       |        |

| 3.6.7     | - ·                                                            |        |

|           |                                                                |        |

| 3.6.8     | Memory Timing Signals — 5 Lines                                |        |

| 3.6.9     | Miscellaneous Signals — 18 Lines                               |        |

| 3.6.10    | Special Signals                                                |        |

| 3.6.11    | Interconnections                                               |        |

| 3.7       | DETAILED DESCRIPTION OF THE 96 OMNIBUS SIGNALS                 |        |

| 3.7.1     | Memory Address — 15 Lines                                      | . 3-9  |

|          |                                                    | Page |

|----------|----------------------------------------------------|------|

| 3.7.1.1  | EMA<0:2>L                                          | 3-9  |

| 3.7.1.2  | MA<0:11>L                                          |      |

| 3.7.2    | Memory Data and Direction Control – 13 Lines       |      |

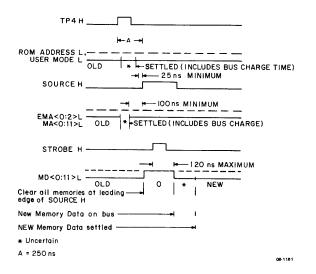

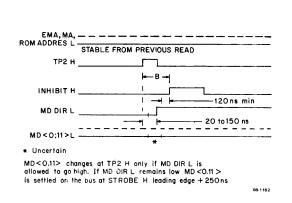

| 3.7.2.1  | MD<0:11>L                                          |      |

| 3.7.2.2  | MD DIR L                                           |      |

| 3.7.3    | Data Bus — 12 Lines                                |      |

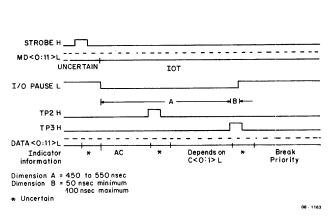

| 3.7.4    | I/O Control Signals — 10 Lines                     |      |

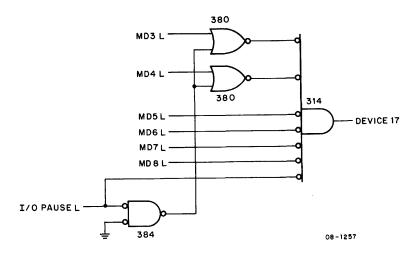

| 3.7.4.1  | I/O PAUSE L — Pin CD1                              |      |

| 3.7.4.2  | INTERNAL I/O L — Pin CL1                           |      |

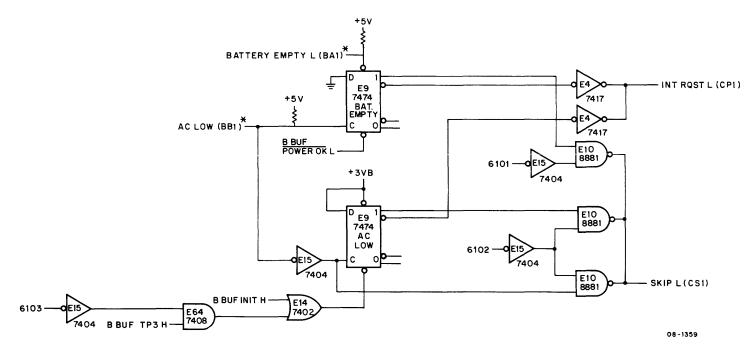

| 3.7.4.3  | SKIP L – Pin CS1                                   |      |

| 3.7.4.4  | INT RQST L — Pin CP1                               |      |

| 3.7.4.5  | C<0:2>L - Pins CE1 (C0 L); CH1 (C1 L); CJ1 (C2 L)  |      |

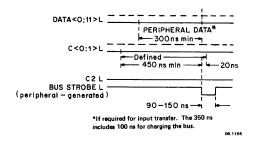

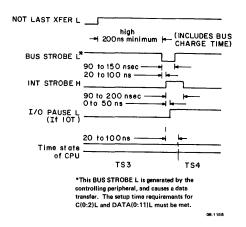

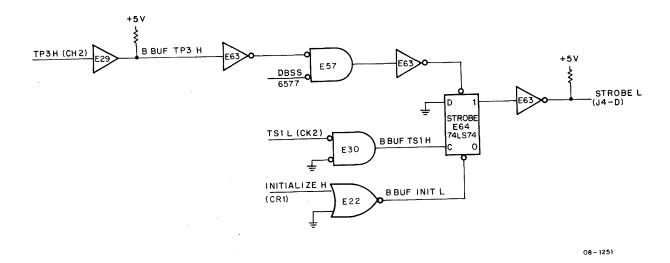

| 3.7.4.6  | BUS STROBE L — Pin CK1                             |      |

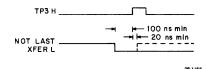

| 3.7.4.7  | NOT LAST XFER L – Pin CL1                          |      |

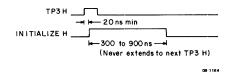

| 3.7.4.8  | INITIALIZE H – Pin CR1                             |      |

| 3.7.5    | DMA Control Signals – 8 Lines                      |      |

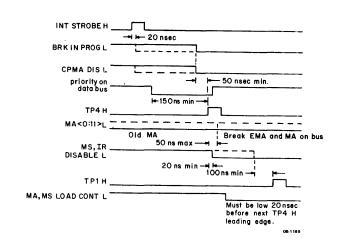

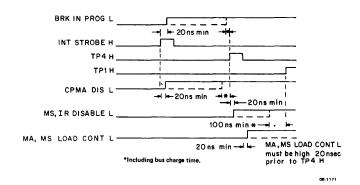

| 3.7.5.1  | BRK IN PROG L — Pin BE2                            |      |

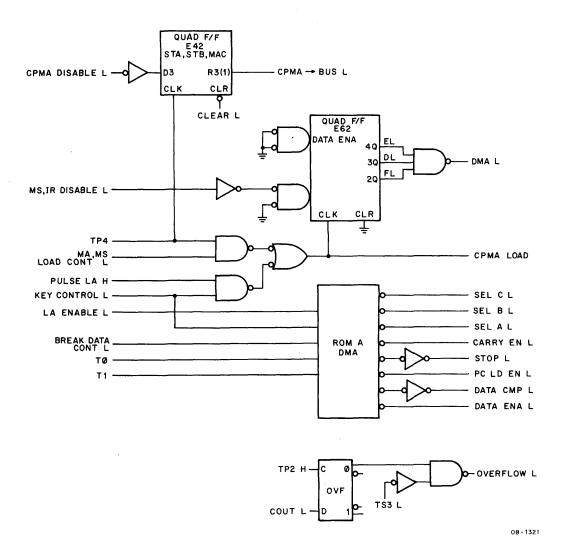

| 3.7.5.2  | CPMA DISABLE L – Pin CU1                           |      |

| 3.7.5.3  | MS, IR DISABLE L — Pin CV1                         |      |

| 3.7.5.4  | MA, MS LOAD CONT L — Pin BH2                       |      |

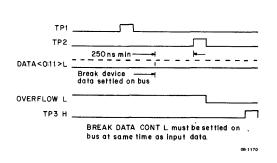

| 3.7.5.5  | BREAK DATA CONT L – Pin BK2                        |      |

| 3.7.5.6  | OVERFLOW L — Pin BJ2                               |      |

| 3.7.5.7  | BK CYCLE L – Pin BL2                               |      |

| 3.7.5.8  | RUN L – Pin BU2                                    |      |

| 3.7.6    | Timing Signals — 9 Lines                           |      |

| 3.7.7    | CPU STATE — 6 Lines                                |      |

| 3.7.7.1  | Major State Lines                                  |      |

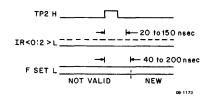

| 3.7.7.2  | IR < 0:2>L                                         |      |

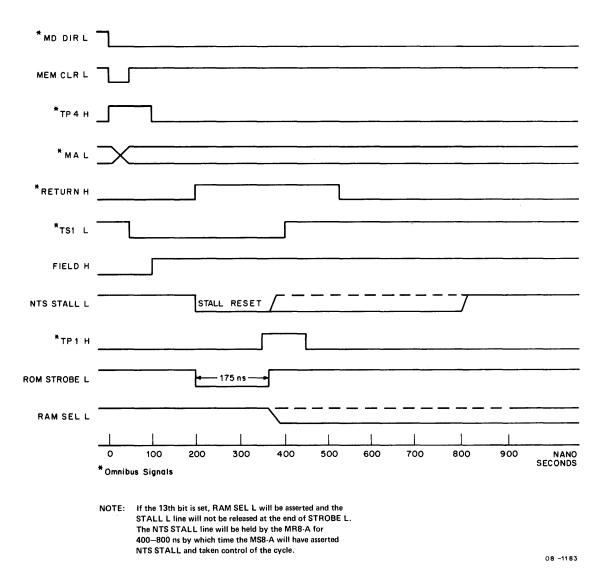

| 3.7.8    | Memory Timing Signals — 5 Lines                    |      |

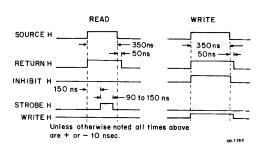

| 3.7.8.1  | SOURCE H — Pin AL2, and RETURN H — Pin AR2         |      |

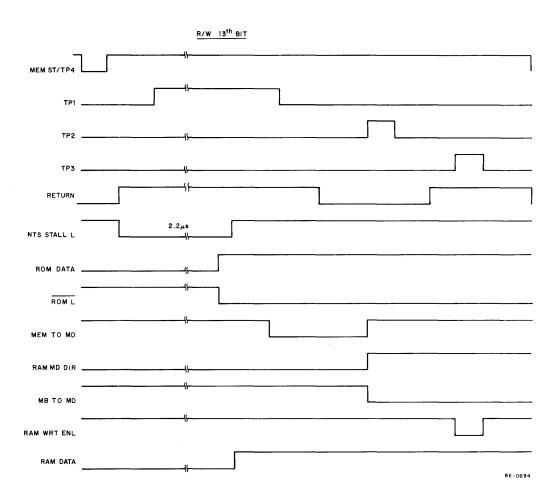

| 3.7.8.2  | WRITE H — Pin AS2                                  |      |

| 3.7.8.3  | INHIBIT H – Pin AP2                                |      |

| 3.7.8.4  | STROBE H – Pin AM2                                 |      |

| 3.7.9    | Miscellaneous Signals — 18 Lines                   |      |

| 3.7.9.1  | IND1 L – Pin CU2, and IND2 L – Pin CV2             |      |

| 3.7.9.2  | MEM START L — Pin AJ2                              |      |

| 3.7.9.3  | STOP L – Pin DS2                                   |      |

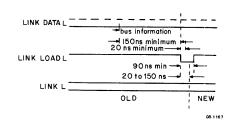

| 3.7.9.4  | LINK L – Pin AV2                                   |      |

| 3.7.9.5  | LINK LOAD L – Pin CS2, and LINK DATA L – Pin CR2   |      |

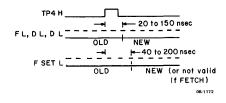

| 3.7.9.6  | F SET L — Pin DP2                                  |      |

| 3.7.9.7  | USER MODE L – Pin DM2                              |      |

| 3.7.9.8  | INT IN PROG H — Pin BP2                            |      |

|          | LA ENABLE L – Pin BM2, and KEY CONTROL L – Pin DU2 |      |

| 3.7.9.9  | PULSE LA H – Pin DR2                               |      |

| 3.7.9.10 | ROM ADDRESS L – Pin AU2                            |      |

| 3.7.9.11 | NTS STALL L – Pin BR2                              |      |

| 3.7.9.12 | SW – Pin DV2                                       |      |

| 3.7.9.13 | ·                                                  |      |

| 3.7.9.14 | POWER OK H — Pin BV2                               | ა-∠∪ |

|          |                                                   | Page |

|----------|---------------------------------------------------|------|

| 3.7.9.15 | RES – Pin BS2                                     | 3-20 |

| 3.7.9.16 | Special Signals                                   | 3-21 |

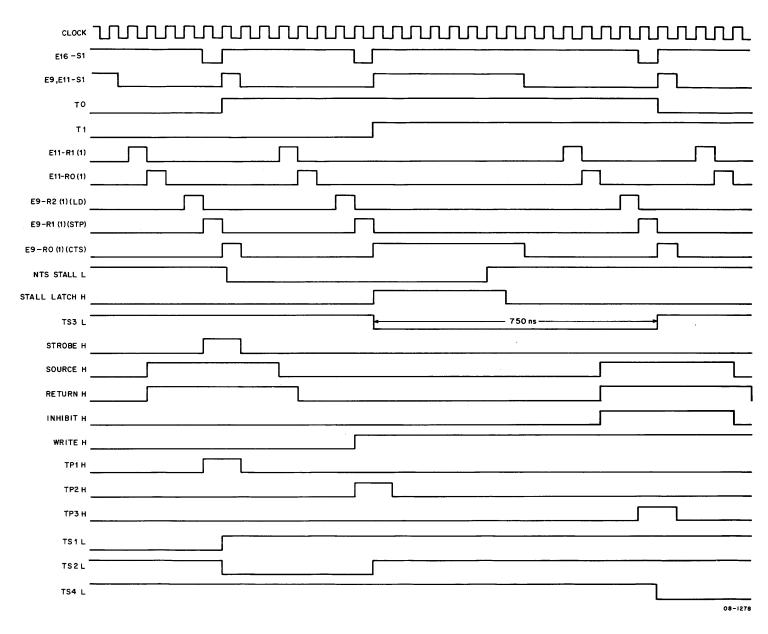

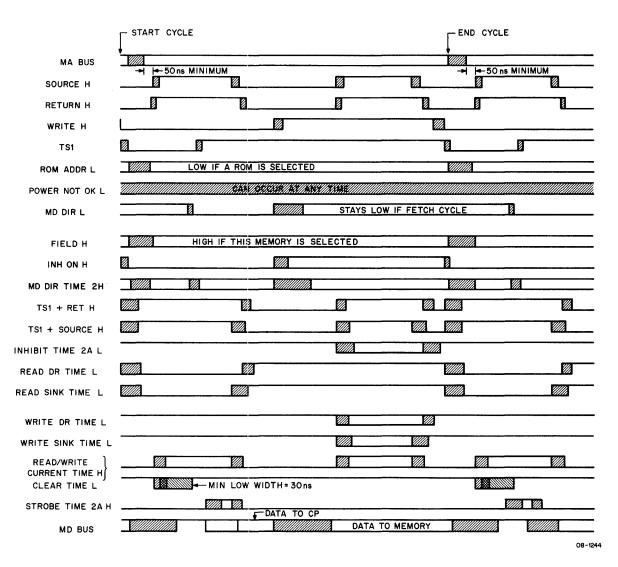

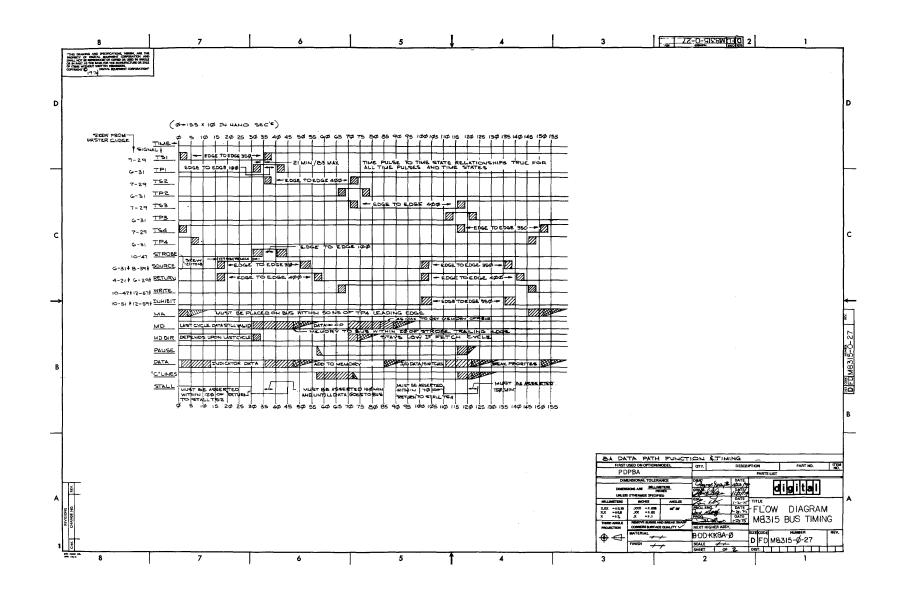

| 3.8      | TIMING                                            | 3-21 |

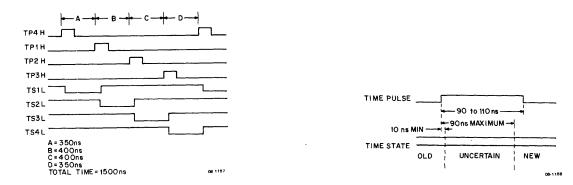

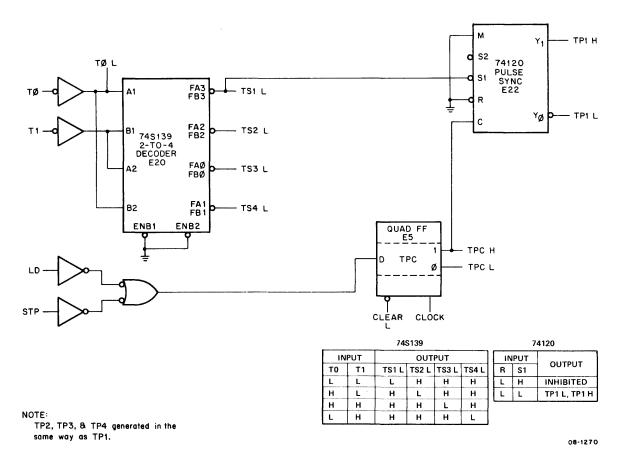

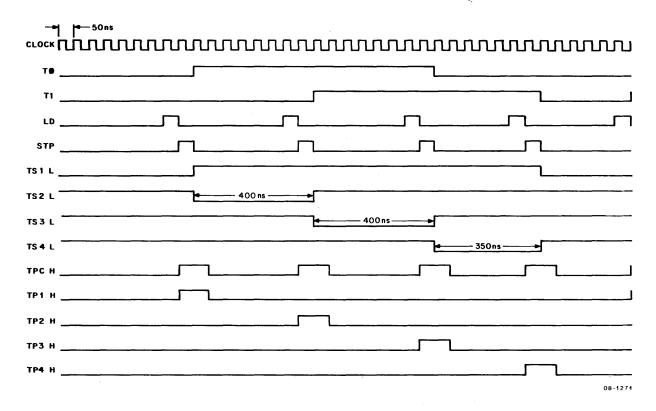

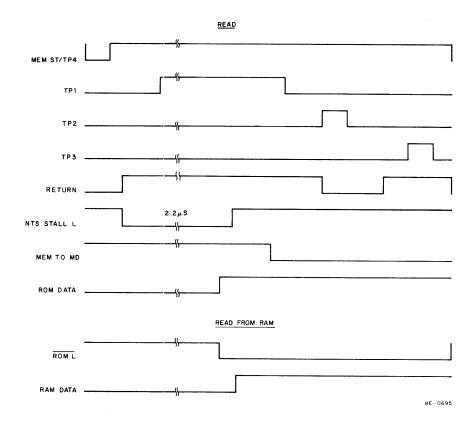

| 3.8.1    | Time Pulses and Time States                       | 3-21 |

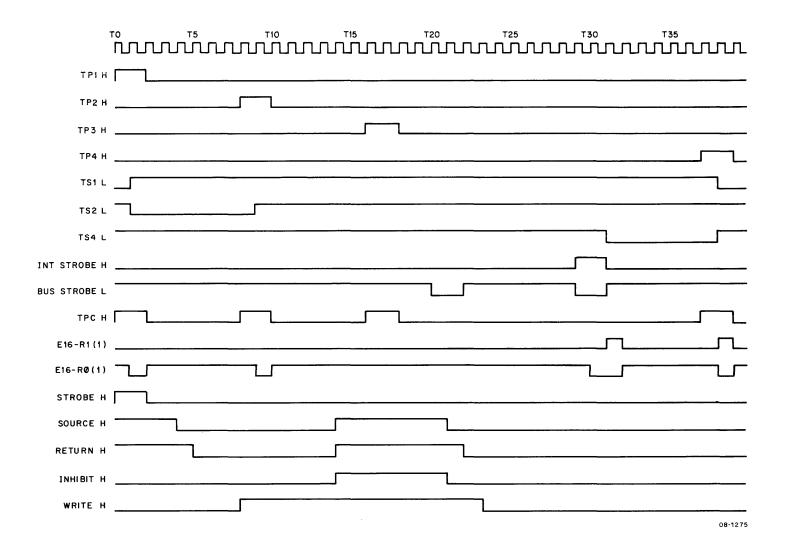

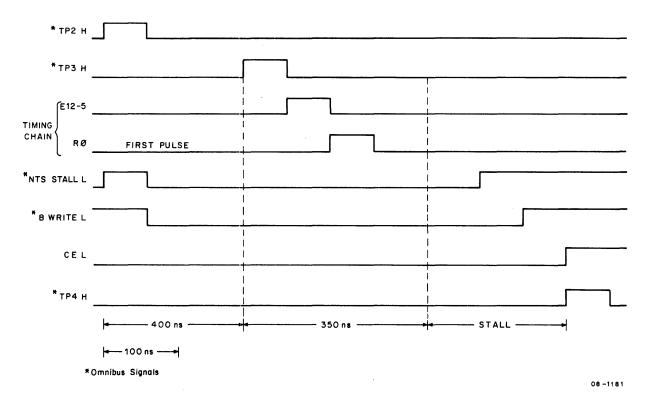

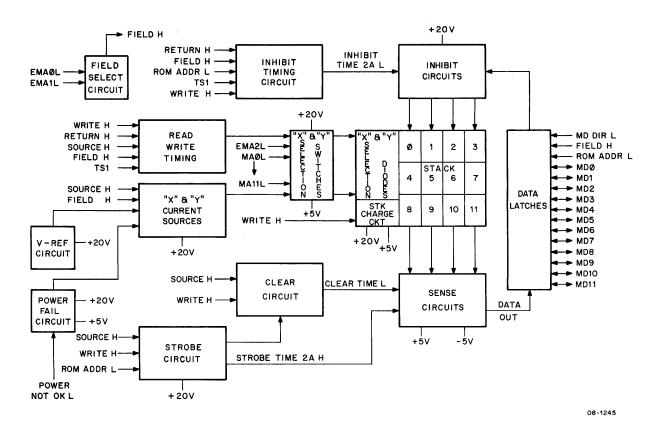

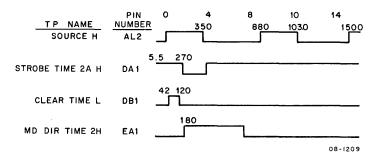

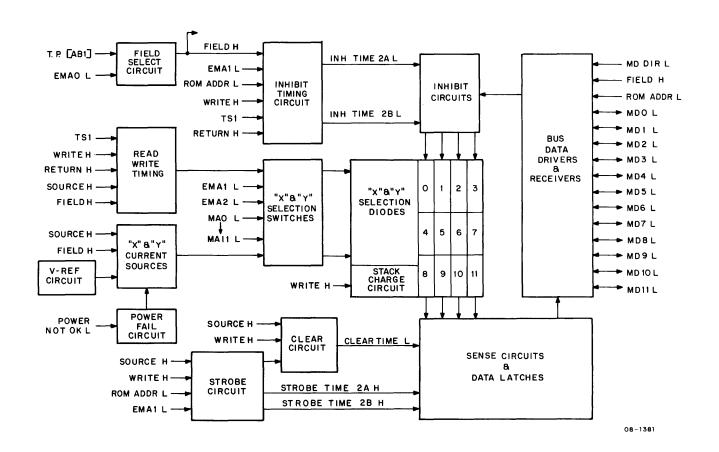

| 3.8.2    | Memory Timing                                     | 3-21 |

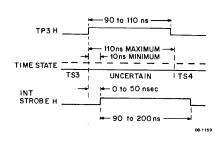

| 3.8.3    | Relationship Between CPU and Memory Timing        |      |

| 3.8.4    | Basic 1/O Timing                                  |      |

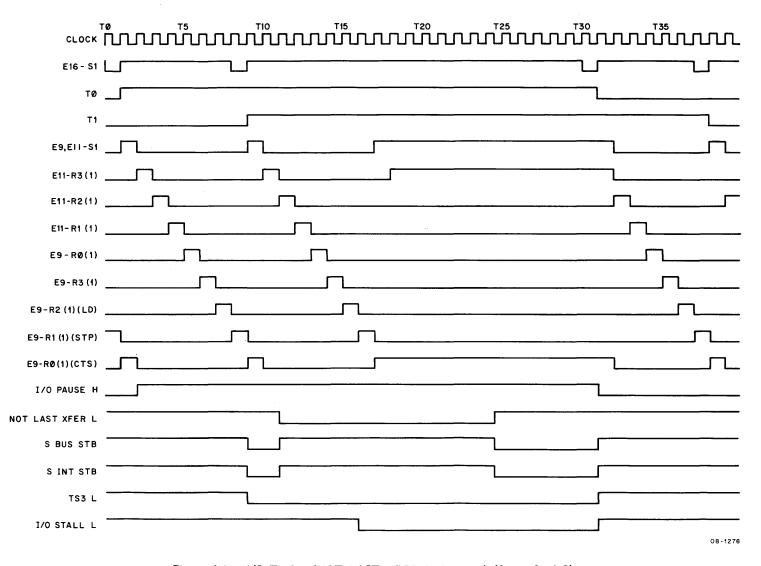

| 3.8.5    | Expanded I/O Timing                               |      |

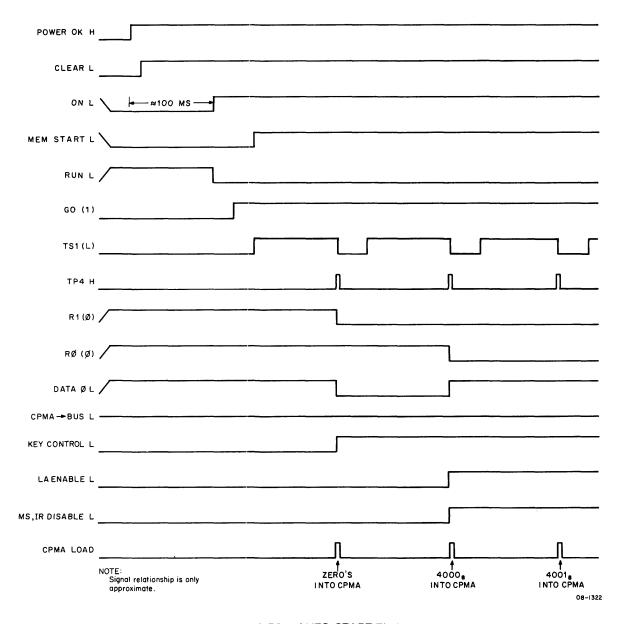

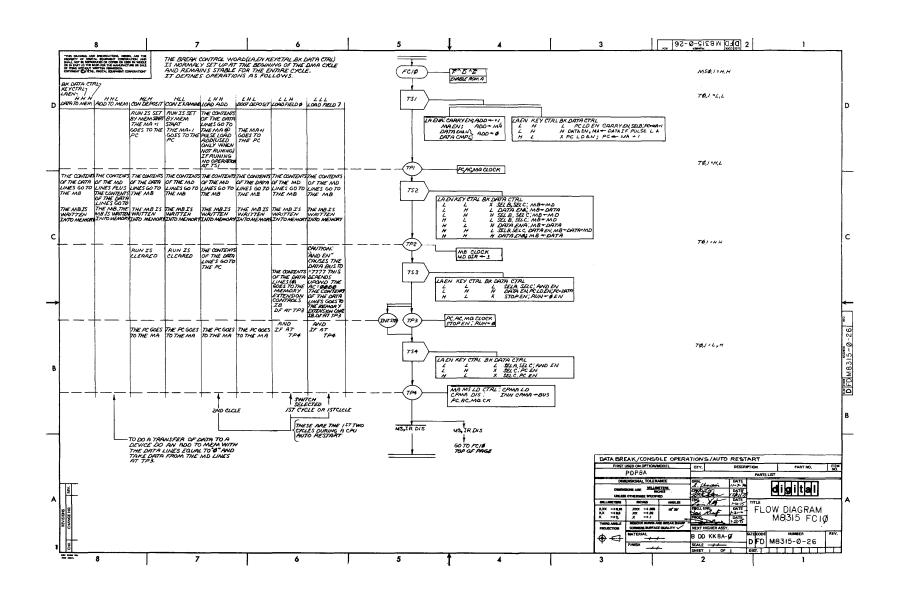

| 3.8.6    | Data Break Timing                                 |      |

| 3.8.6.1  | Data Exchange                                     |      |

| 3.8.6.2  | Final Operations                                  |      |

| 3.8.7    | CPU Major States                                  |      |

| 3.8.7.1  | IR (FETCH Cycle)                                  |      |

| 3.8.7.2  | Interrupt Recognition                             |      |

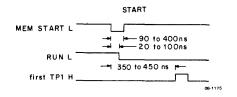

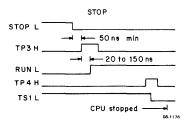

| 3.8.8    | Timing Start and Stop                             |      |

| 3.9      | ASYNCHRONOUS SIGNALS                              |      |

| 3.10     | SPECIAL SIGNALS                                   |      |

| 3.11     | ELECTRICAL CHARACTERISTICS AND INTERFACING        |      |

| 3.11.1   | Logic Levels                                      |      |

| 3.11.2   | Bus Loads                                         |      |

| 3.11.3   | Driving the Omnibus                               |      |

| 3.11.3   | DRIVE AVAILABLE FOR PERIPHERALS                   |      |

| 3.12     |                                                   |      |

|          | RECEIVERS AND LOAD RELIEF TECHNIQUES              |      |

| 3.14     | INTERFACE EXAMPLES                                |      |

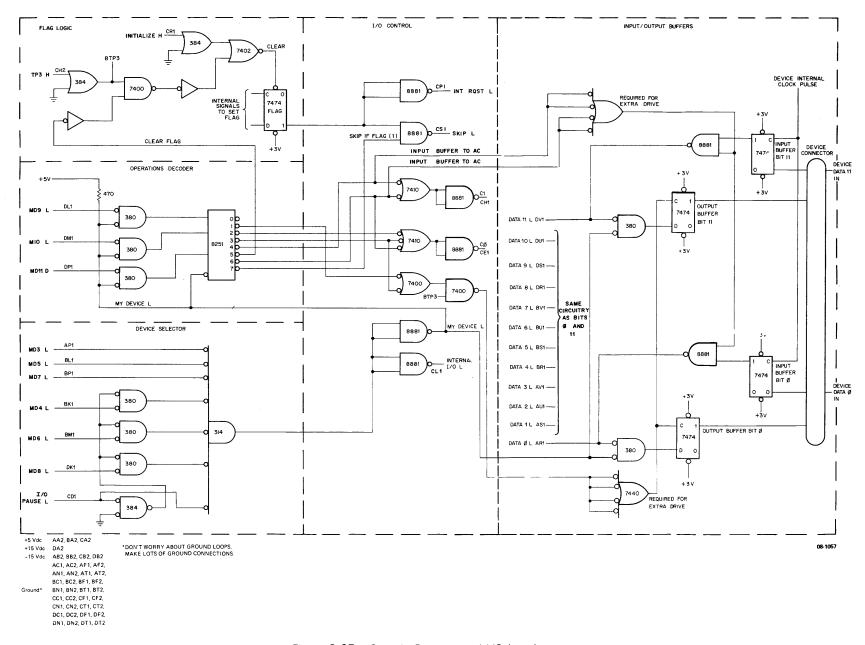

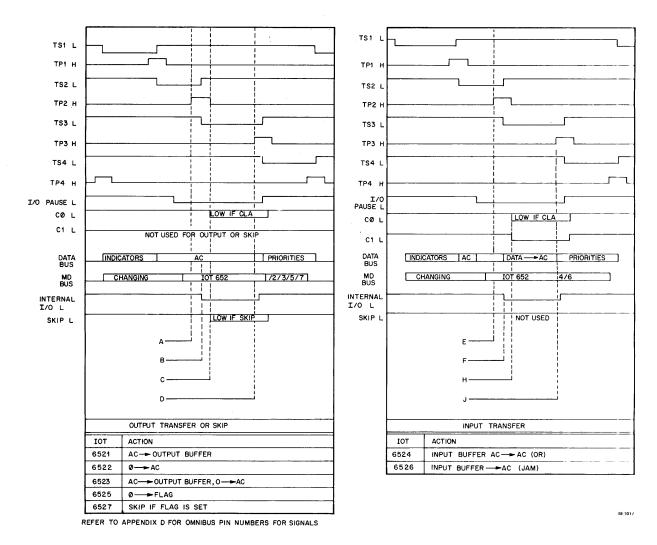

| 3.14.1   | Programmed I/O Interface Example                  |      |

| 3.14.2   | Flag Logic                                        |      |

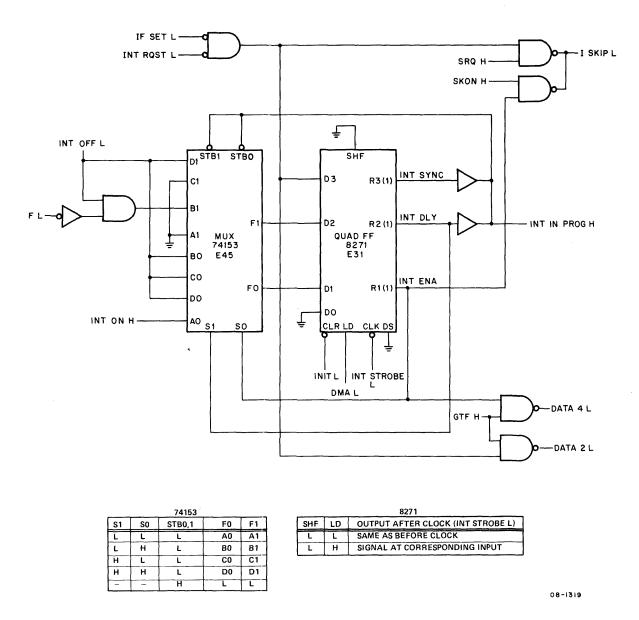

| 3.14.3   | Interrupt Request                                 |      |

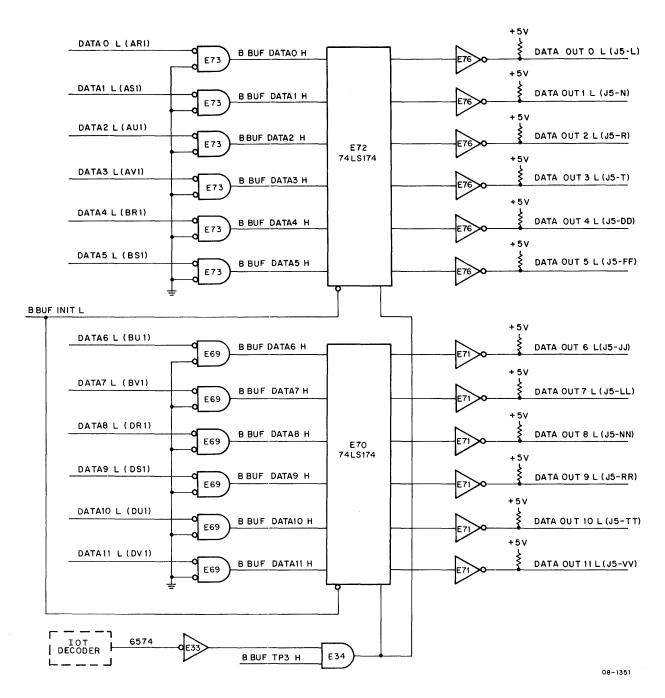

| 3.14.4   | Output Buffer                                     |      |

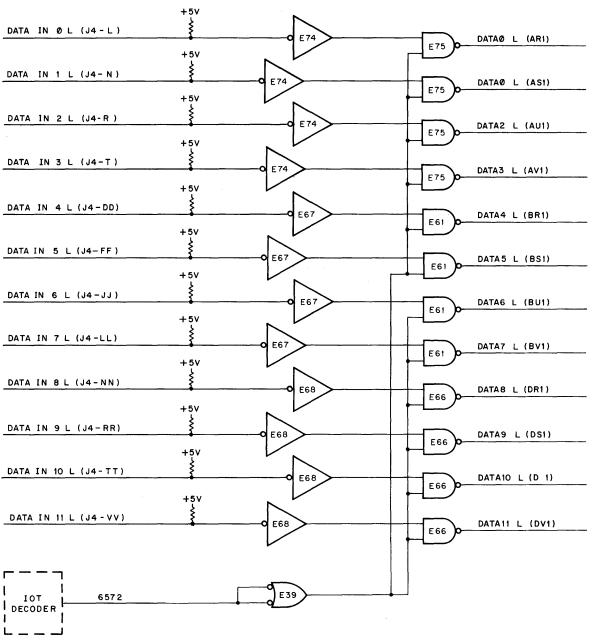

| 3.14.5   | Input Buffer                                      |      |

| 3.14.6   | I/O Control                                       |      |

| 3.14.7   | Input/Output Timing for Programmed I/O Interfaces |      |

| 3.15     | PROGRAM INTERRUPT TRANSFERS                       |      |

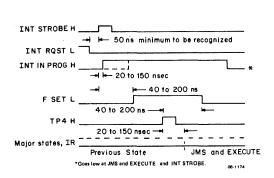

| 3.15.1   | Interrupt Timing                                  |      |

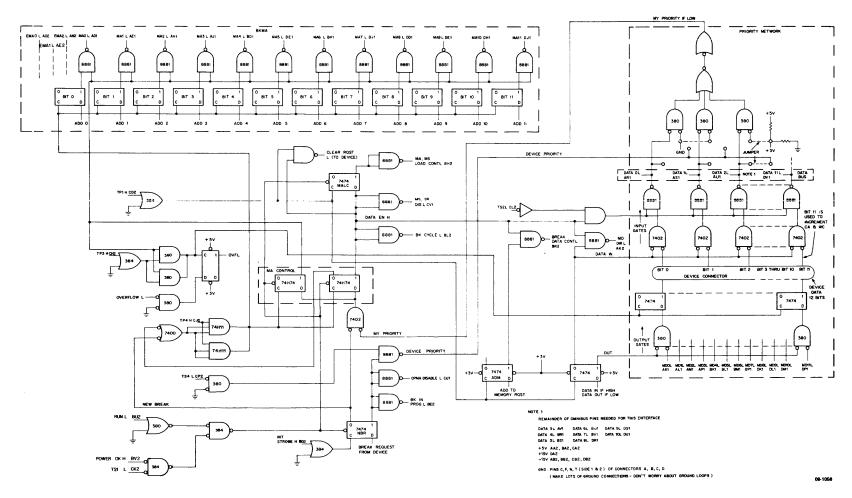

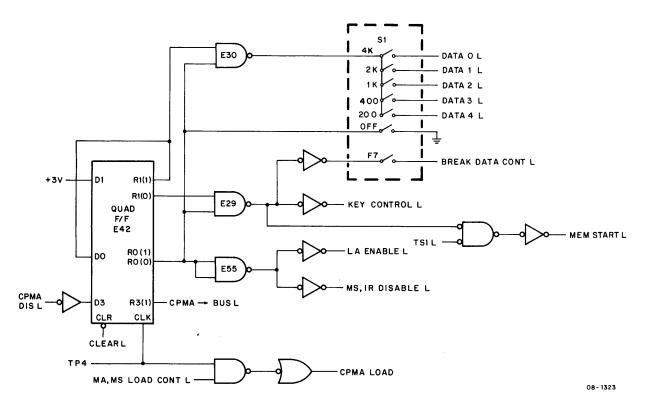

| 3.15.2   | Data Break Interface Example                      |      |

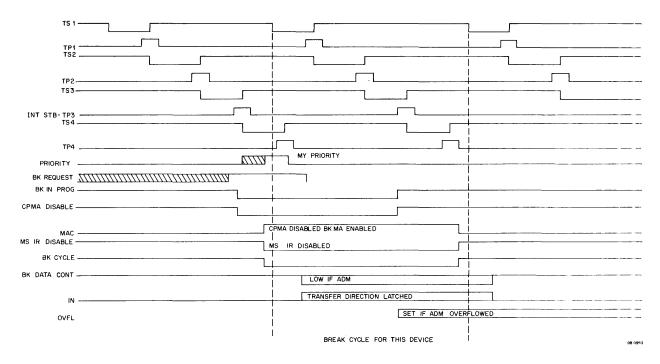

| 3.15.3   | Data Break Timing                                 |      |

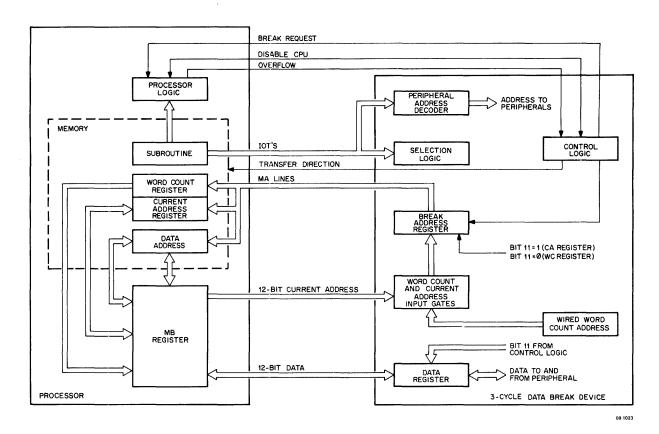

| 3.16     | THREE-CYCLE DATA BREAK                            |      |

| 3.17     |                                                   |      |

| 3.18     | TRANSMISSION LINE EFFECTS                         |      |

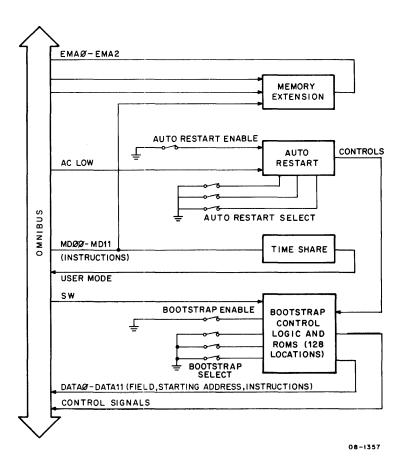

| 3.19     | EXTERNAL BUS                                      |      |

| 3.19.1   | Positive I/O Bus Interfacing                      |      |

| 3.19.2   | The Nature of the External Bus                    | 3-39 |

| 3.19.3   | External Bus Signals                              | 3-40 |

| 3.19.4   | External Bus Signals                              | 3-40 |

| 3.19.4.1 | BAC 00-11                                         | 3-40 |

| 3.19.4.2 | AC 00–11                                          | 3-40 |

| 3.19.4.3 | BMB 0011                                          | 3-41 |

| 3.19.4.4 | BIOP 1, 2, and 4                                  | 3-41 |

| 3.19.4.5 | BTS1, BTS3                                        | 3-41 |

|           |                                             | Page |

|-----------|---------------------------------------------|------|

| 3.19.4.6  | B RUN                                       | 3-41 |

| 3.19.4.7  | AC CLEAR                                    | 3-41 |

| 3.19.4.8  | SKIP                                        | 3-41 |

| 3.19.4.9  | B INITIALIZE 1                              | 3-41 |

| 3.19.4.10 | DATA 00–11                                  | 3-41 |

| 3.19.4.11 | B BREAK                                     |      |

| 3.19.4.12 | DATA OUT                                    |      |

| 3.19.4.13 | DATA ADD 00-11                              | 3-42 |

| 3.19.4.14 | BRK RQST                                    |      |

| 3.19.4.15 | ADD ACCEPTED                                | 3-42 |

| 3.19.4.16 | MB INCREMENT                                | 3-42 |

| 3.19.4.17 | CA INCREMENT INH                            | 3-42 |

| 3.19.4.18 | 3 CYCLE                                     |      |

| 3.19.4.19 | WC OVERFLOW                                 |      |

| 3.19.4.20 | EXT DATA ADD 0–2                            |      |

| 3.19.4.21 | B INITIALIZE 2                              |      |

|           |                                             | 0 .0 |

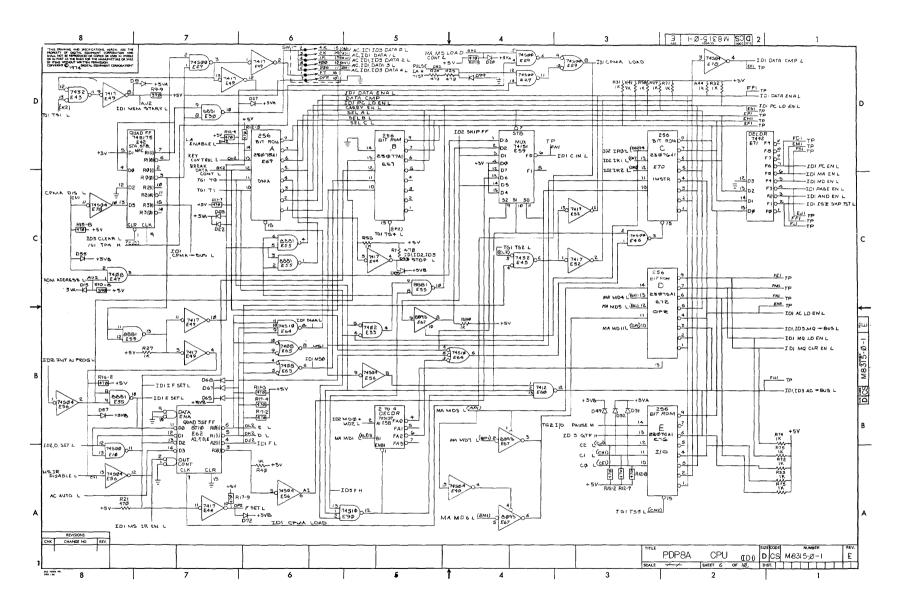

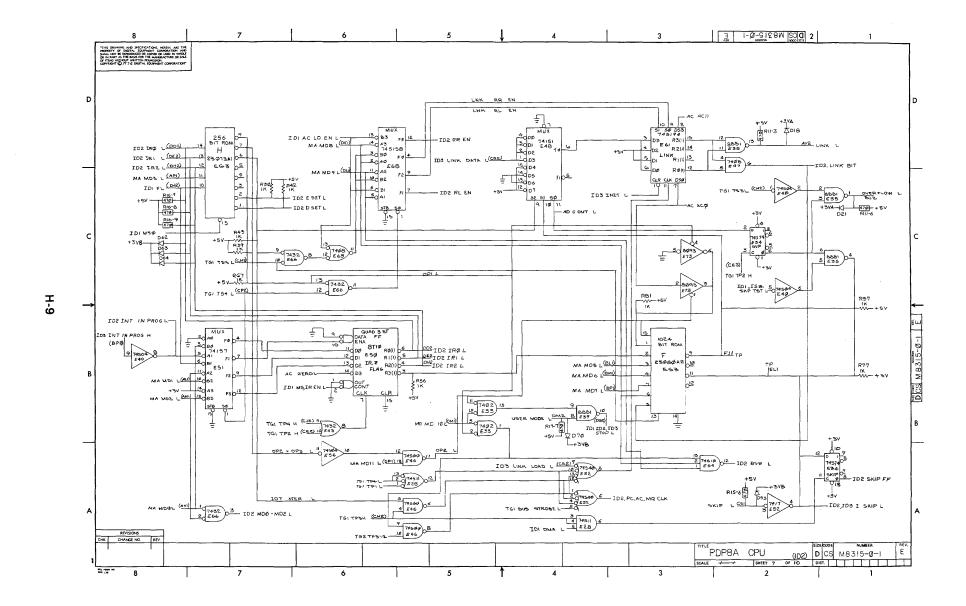

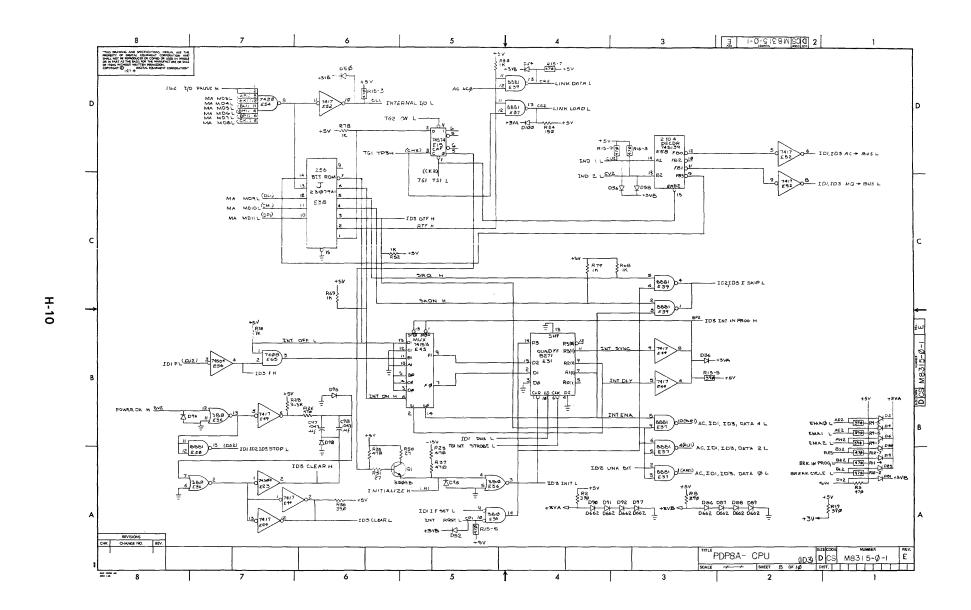

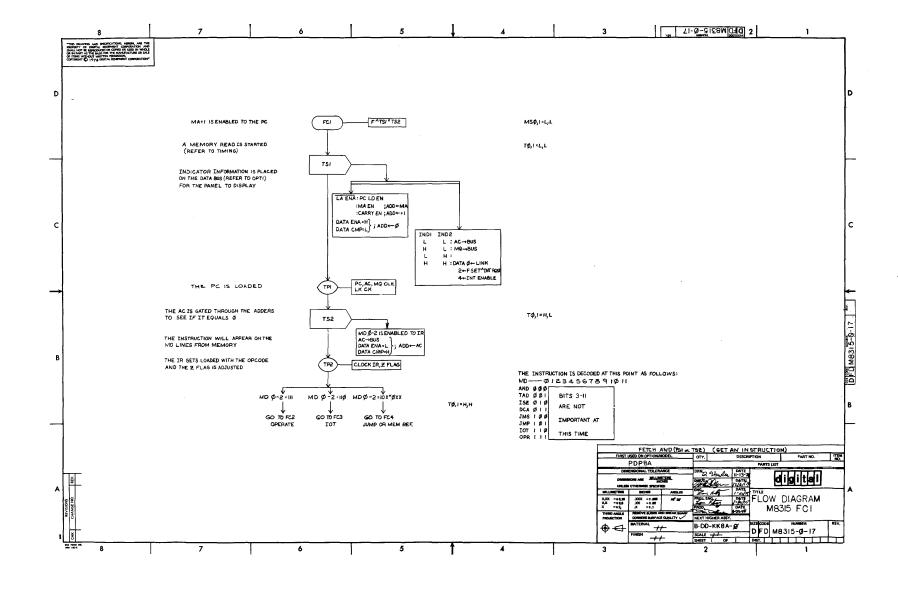

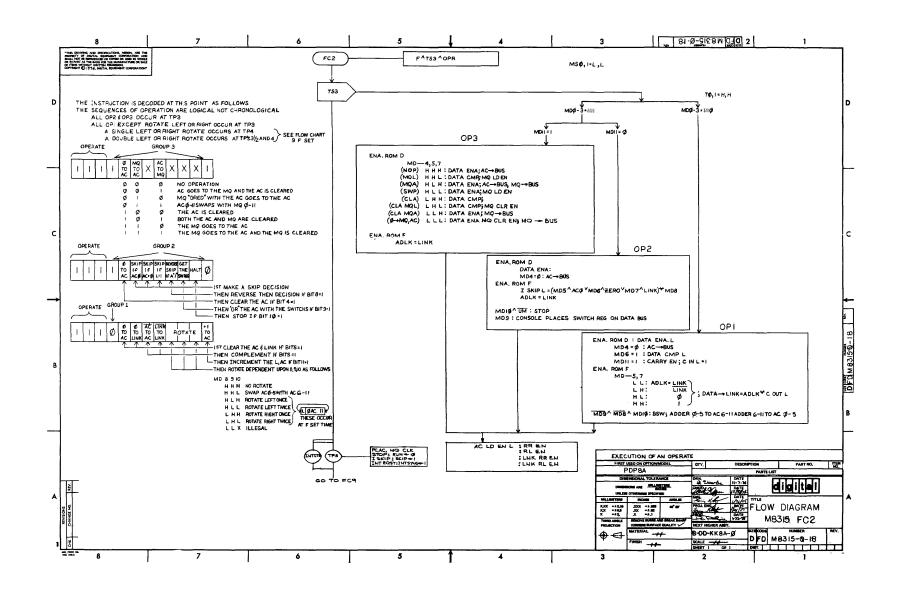

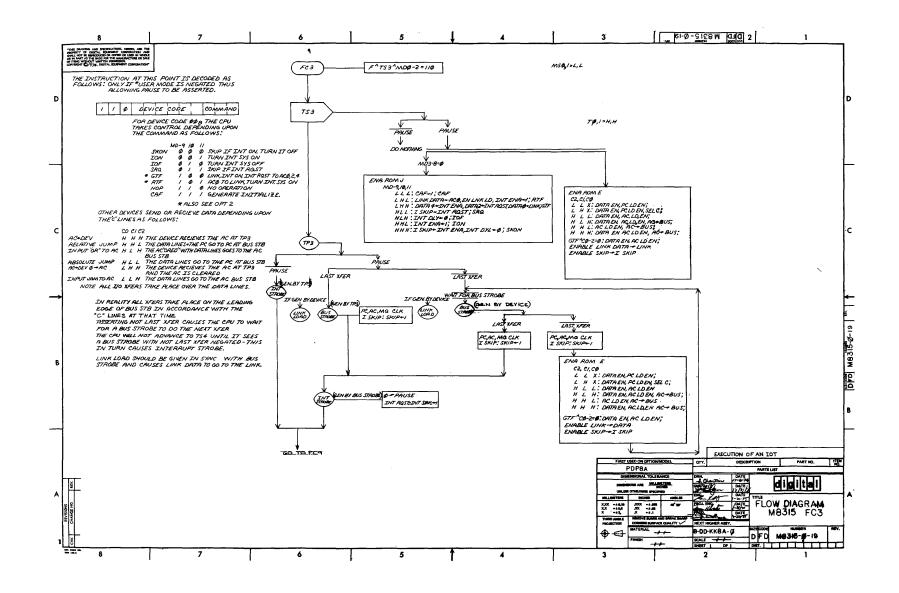

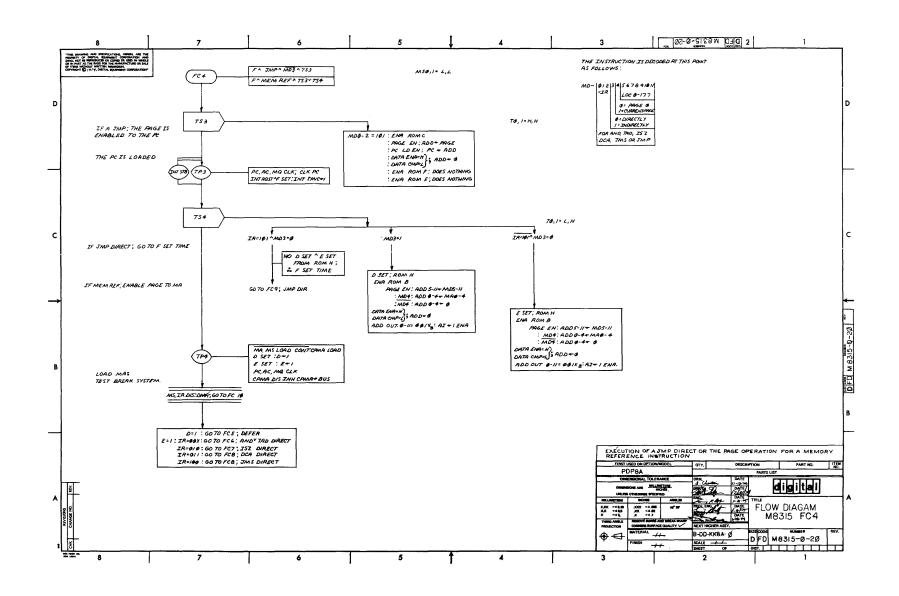

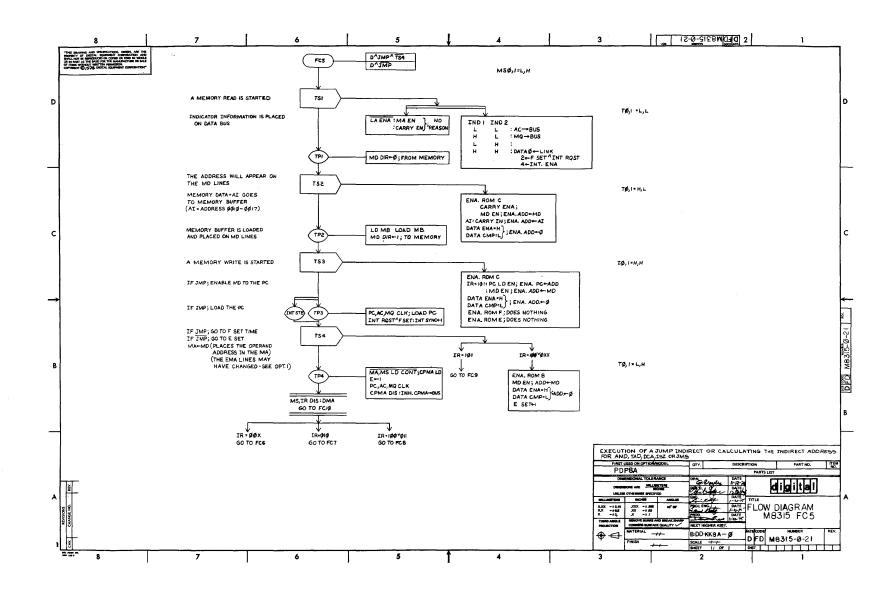

| CHAPTER 4 | CENTRAL PROCESSOR UNIT                      |      |

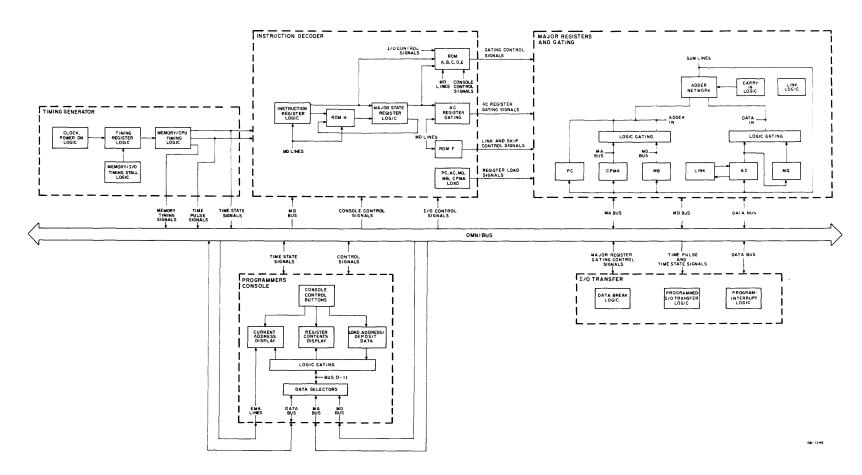

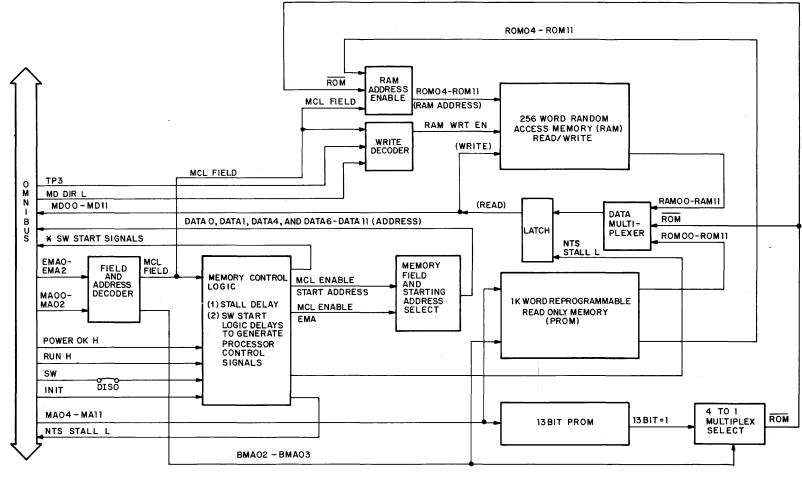

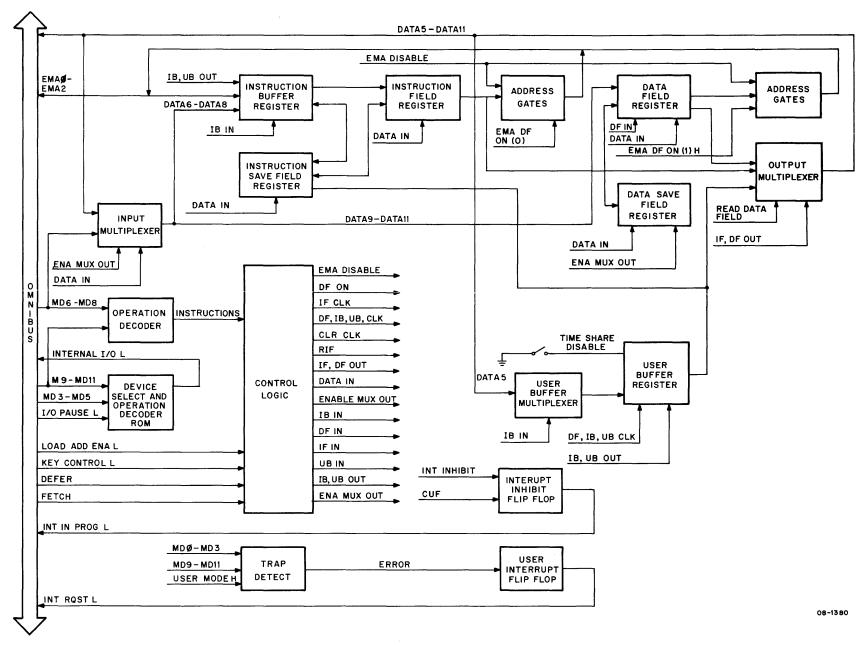

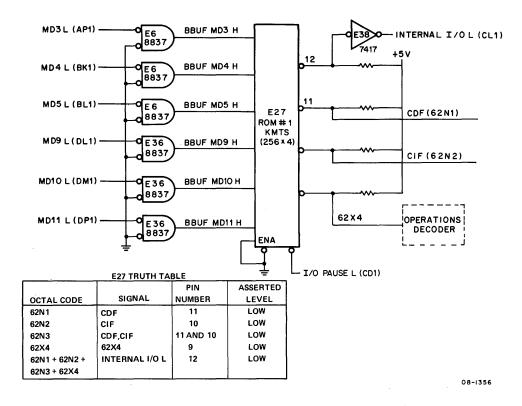

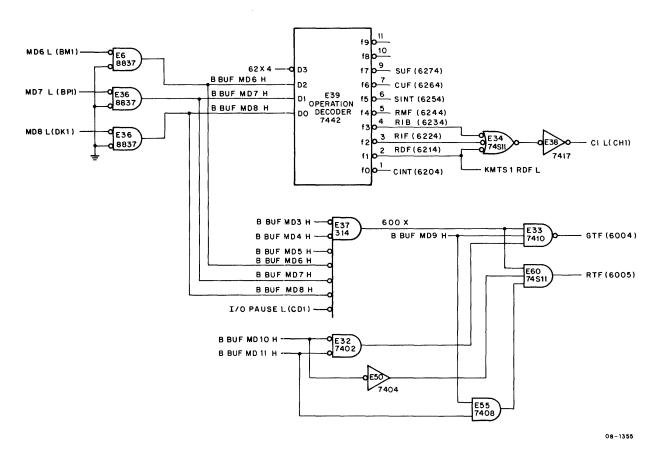

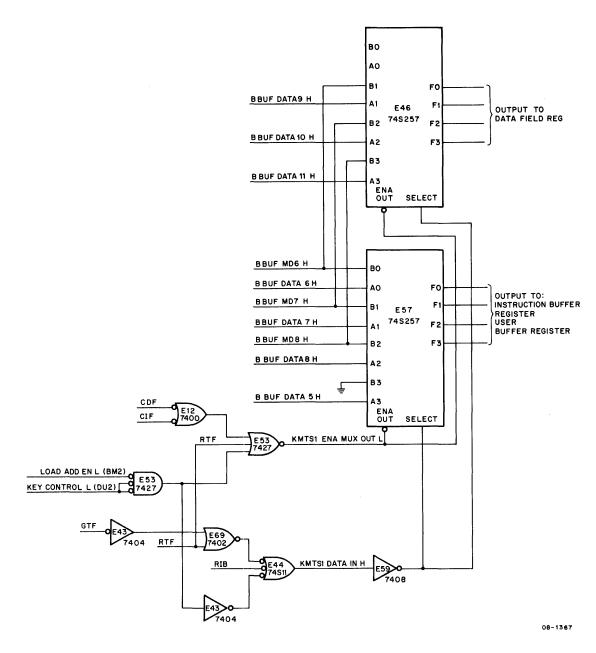

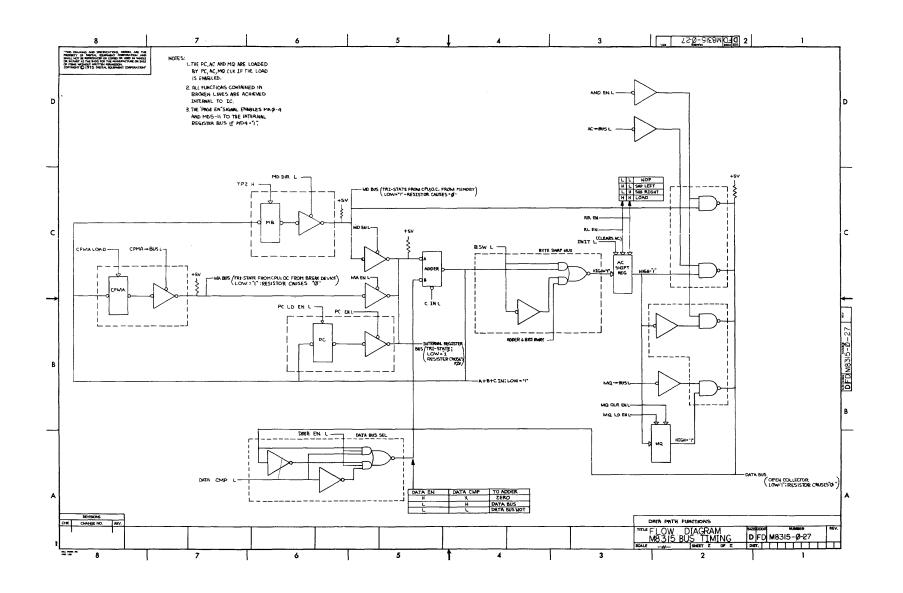

| 4.1       | CENTRAL PROCESSOR UNIT, GENERAL DESCRIPTION | 4-1  |

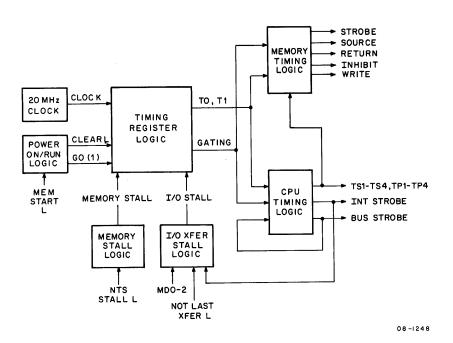

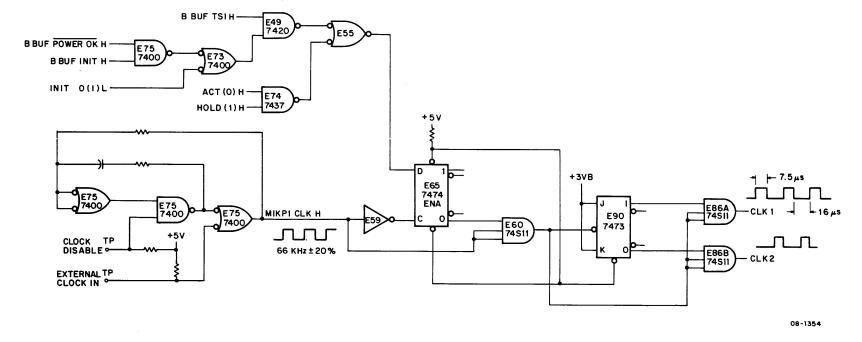

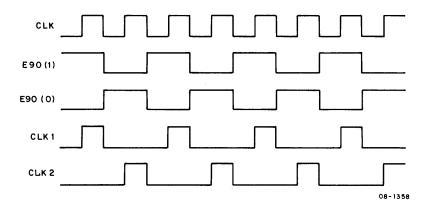

| 4.2       | TIMING GENERATOR                            | 4-3  |

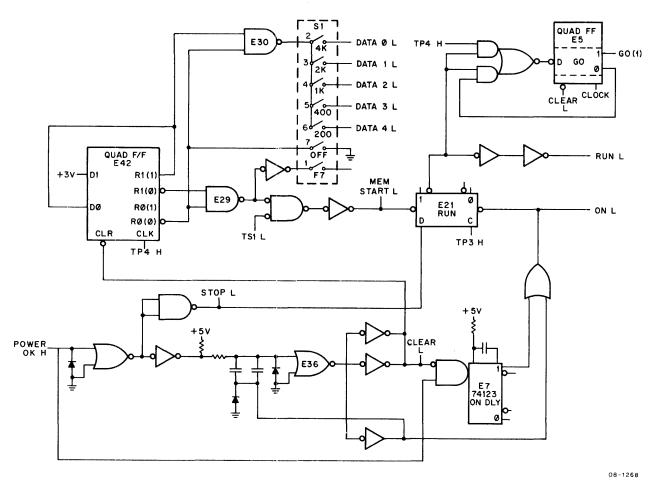

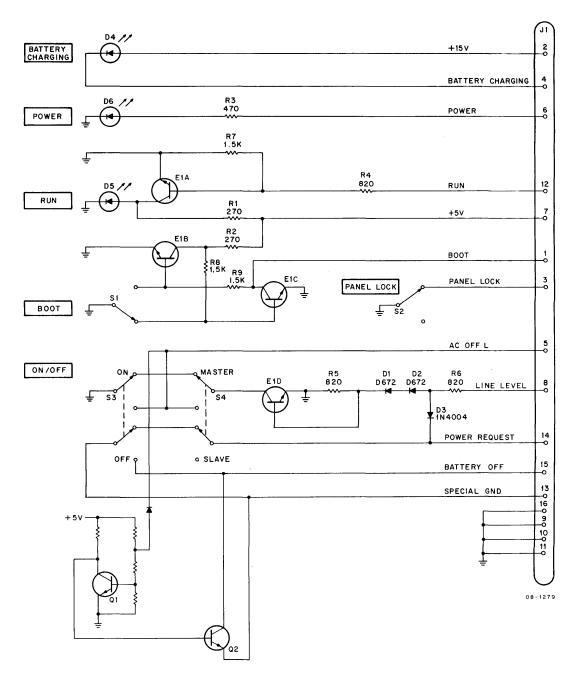

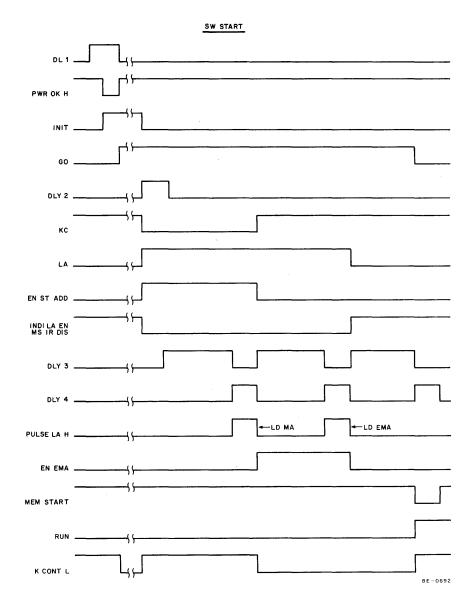

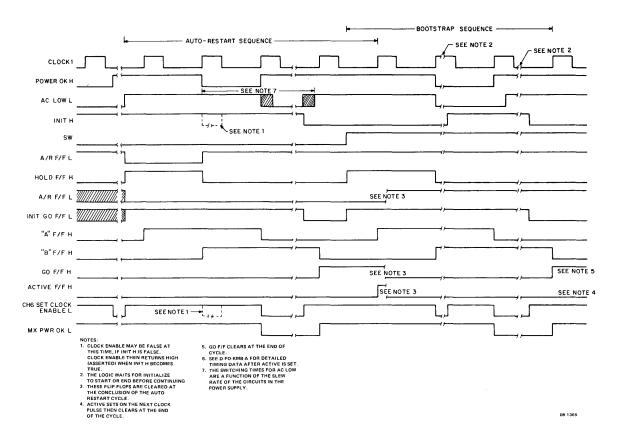

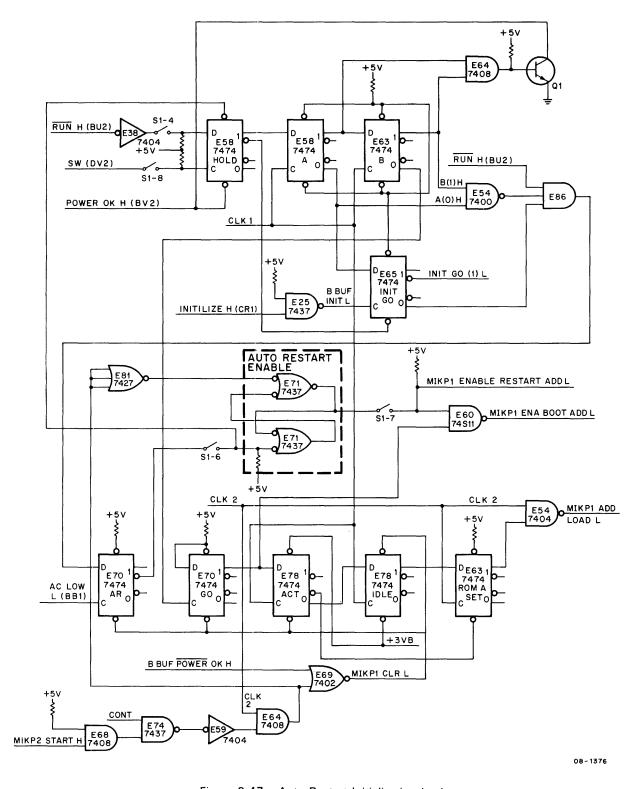

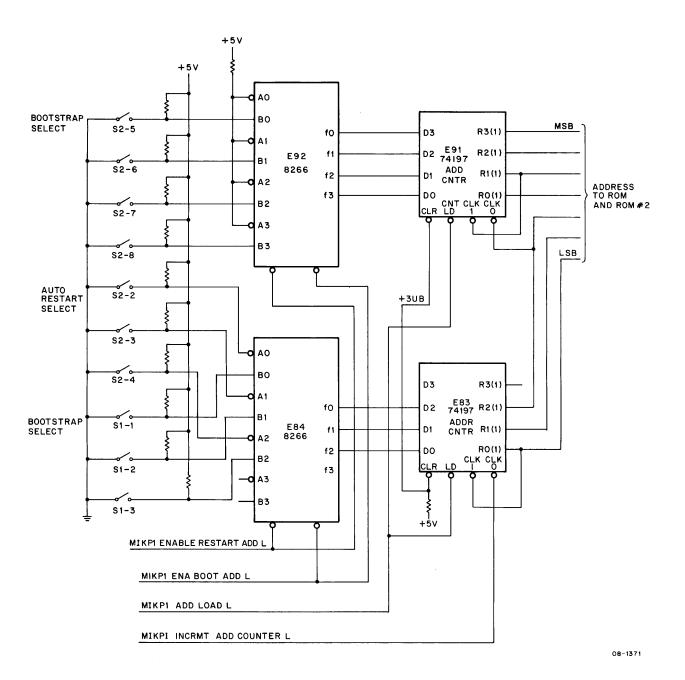

| 4.2.1     | Power On/Run Logic                          | 4-4  |

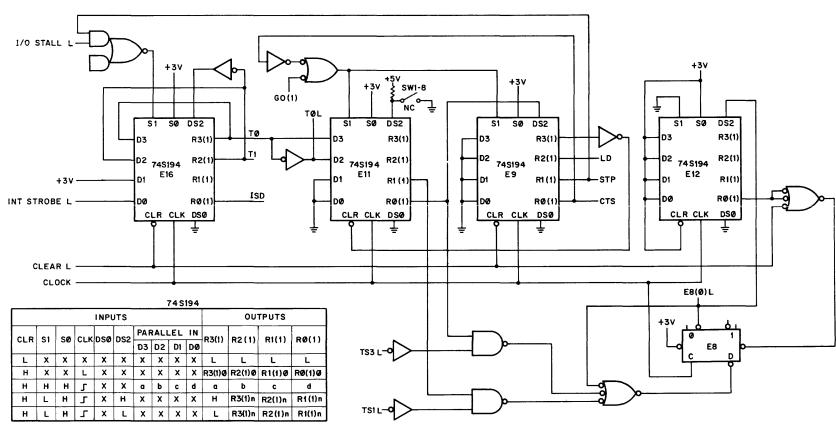

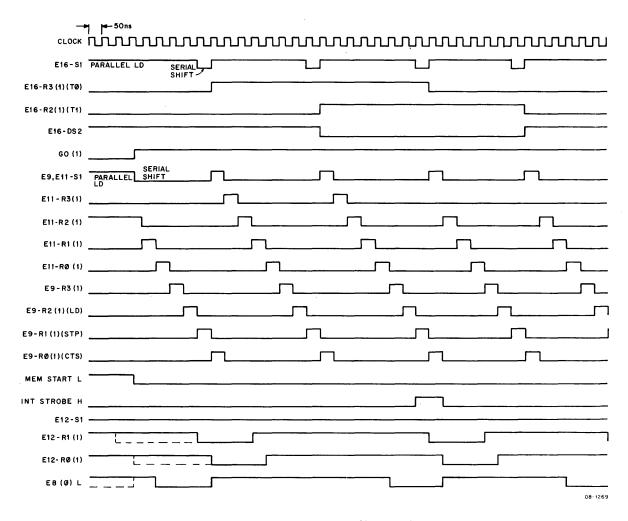

| 4.2.2     | Timing Register Logic                       | 4-5  |

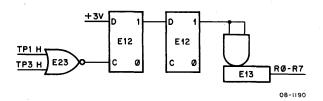

| 4.2.3     | CPU Timing Logic                            | 4-7  |

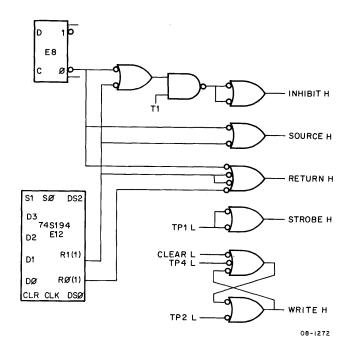

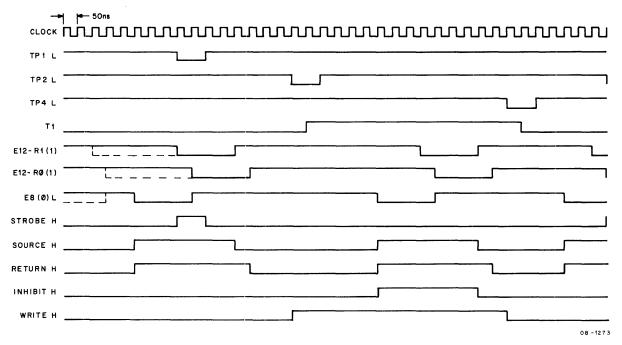

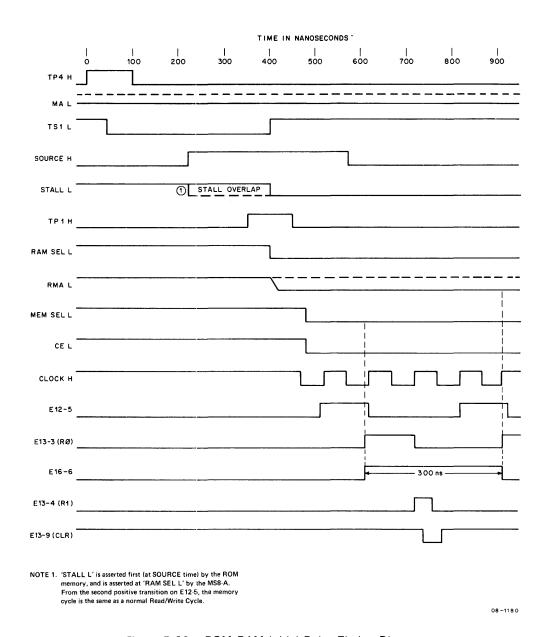

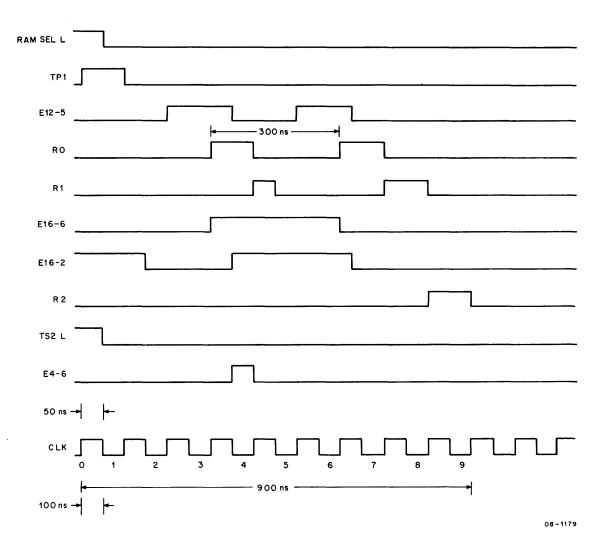

| 4.2.4     | Memory Timing Logic                         | 4-7  |

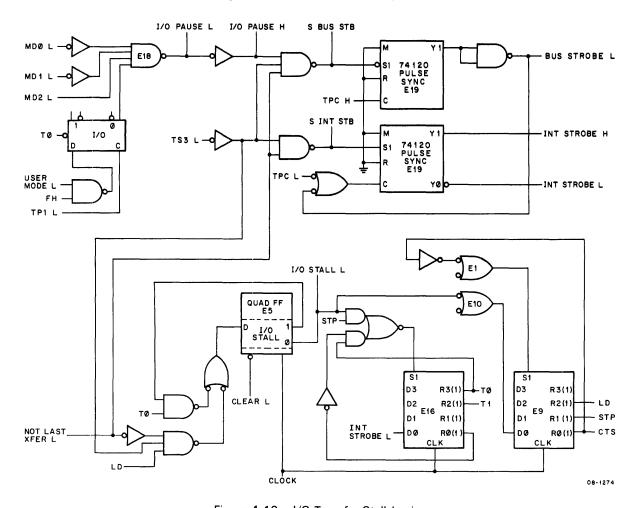

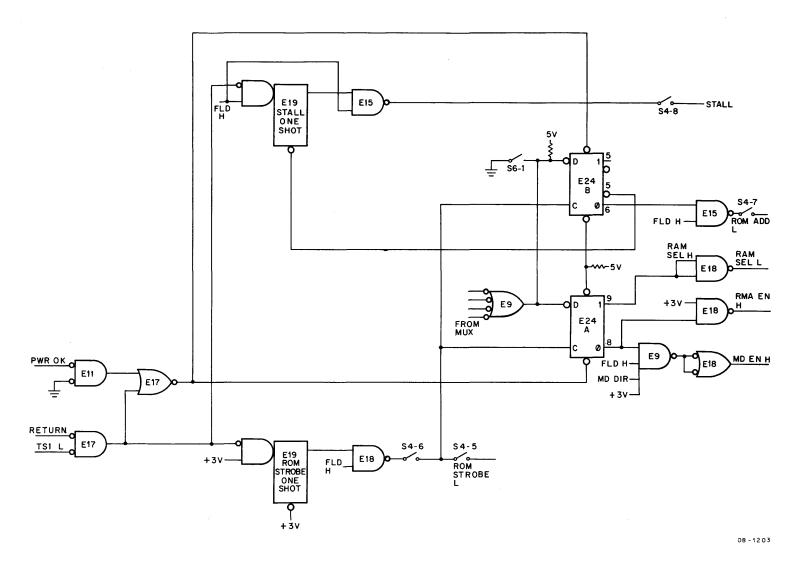

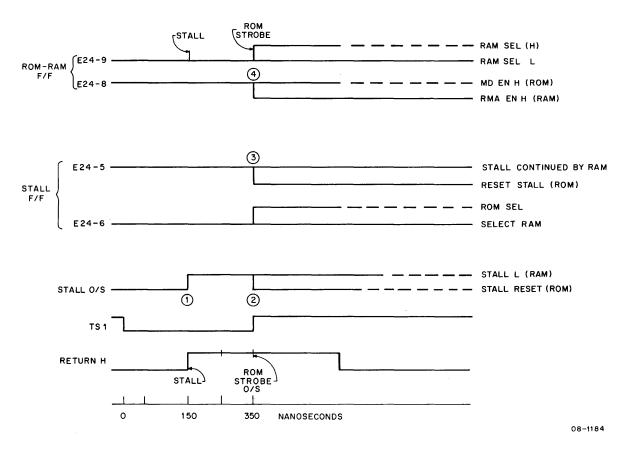

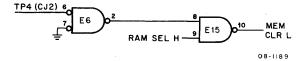

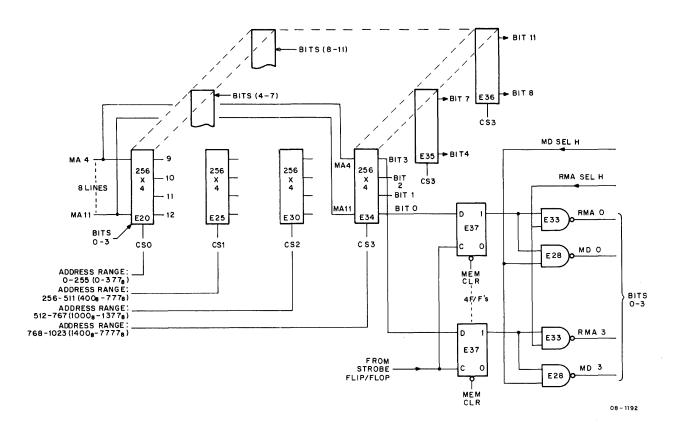

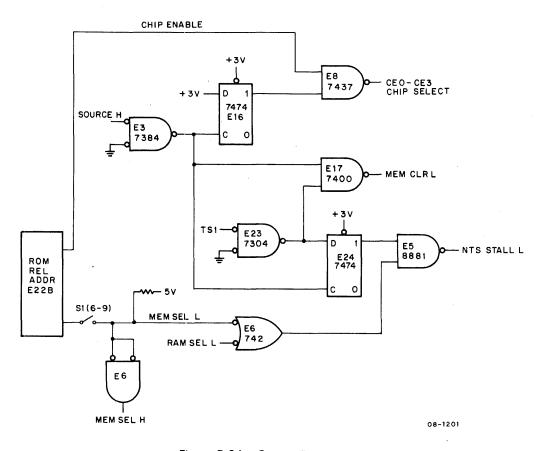

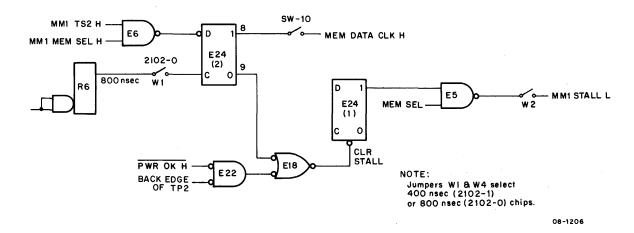

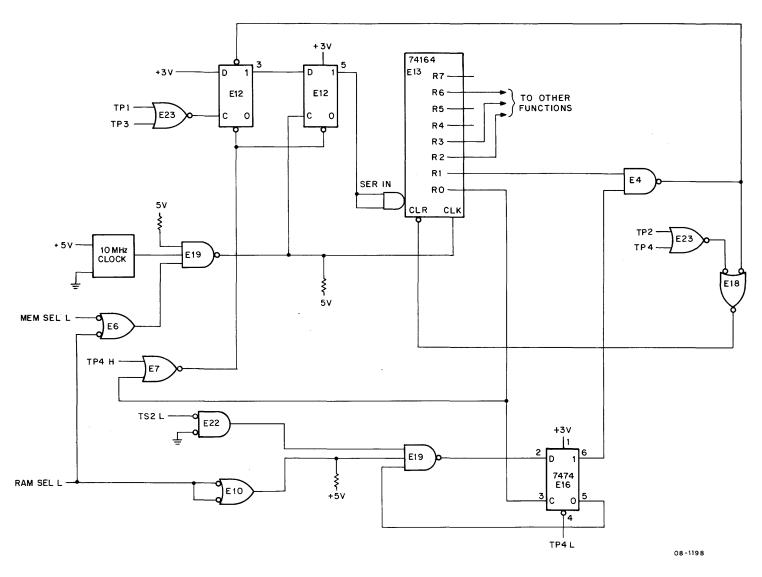

| 4.2.5     | I/O Transfer Stall Logic                    | 4-8  |

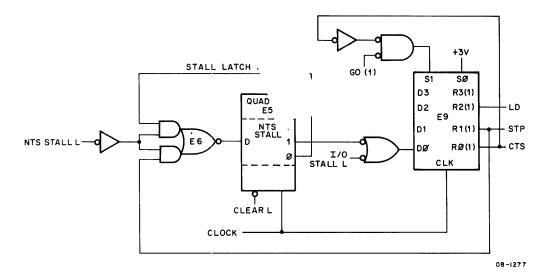

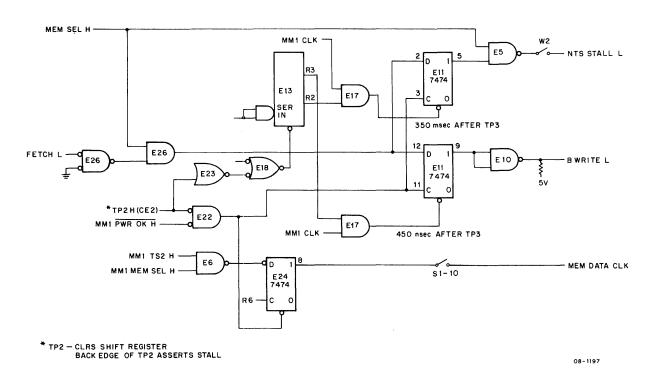

| 4.2.6     | Memory Stall Logic                          | 4-11 |

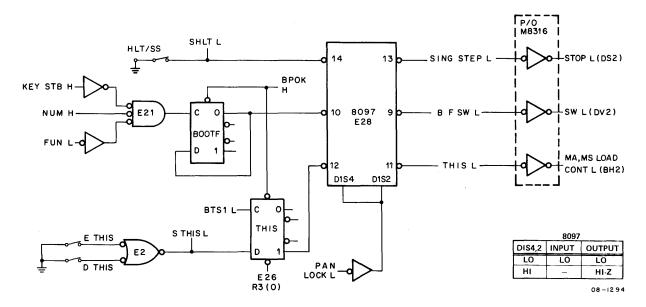

| 4.3       | FRONT PANEL OPERATIONS                      | 4-11 |

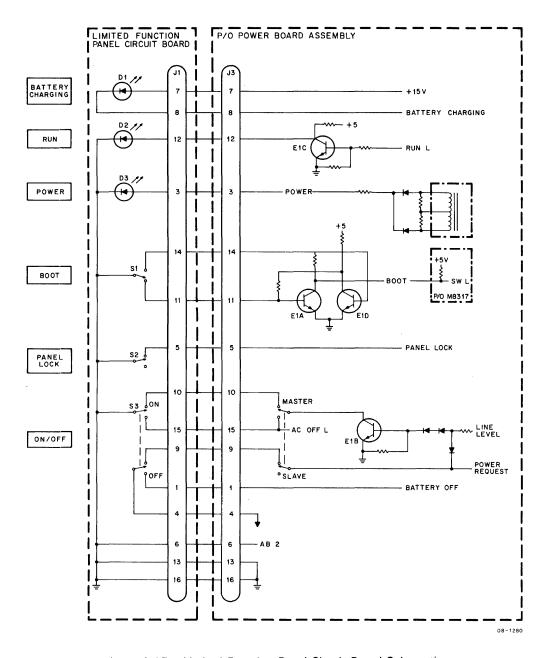

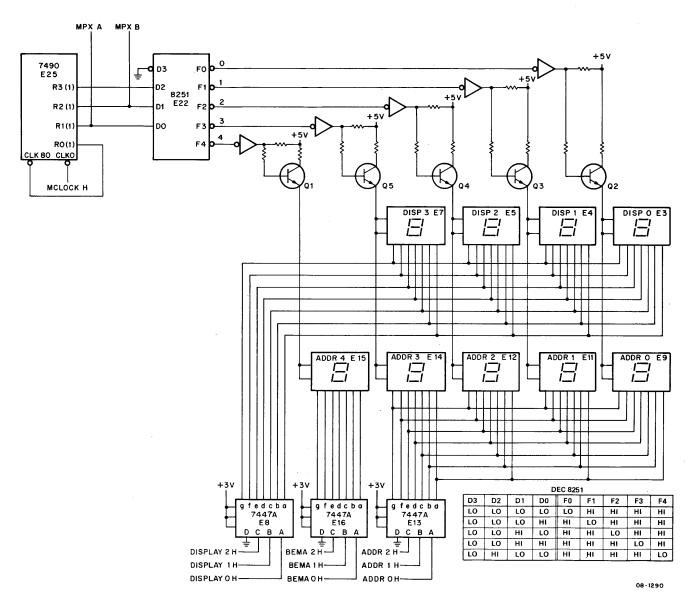

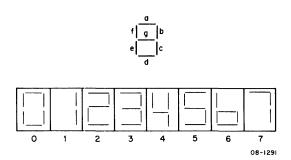

| 4.3.1     | Limited Function Panel                      | 4-14 |

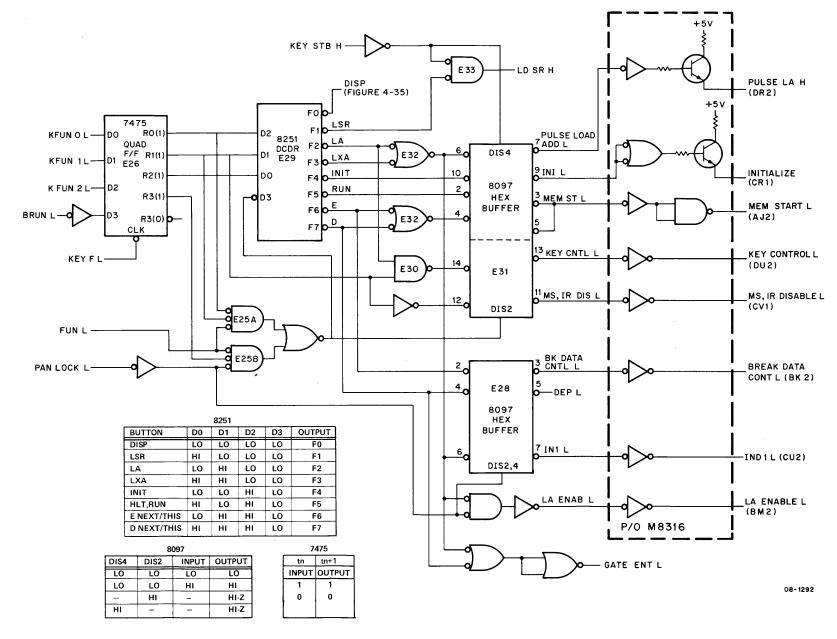

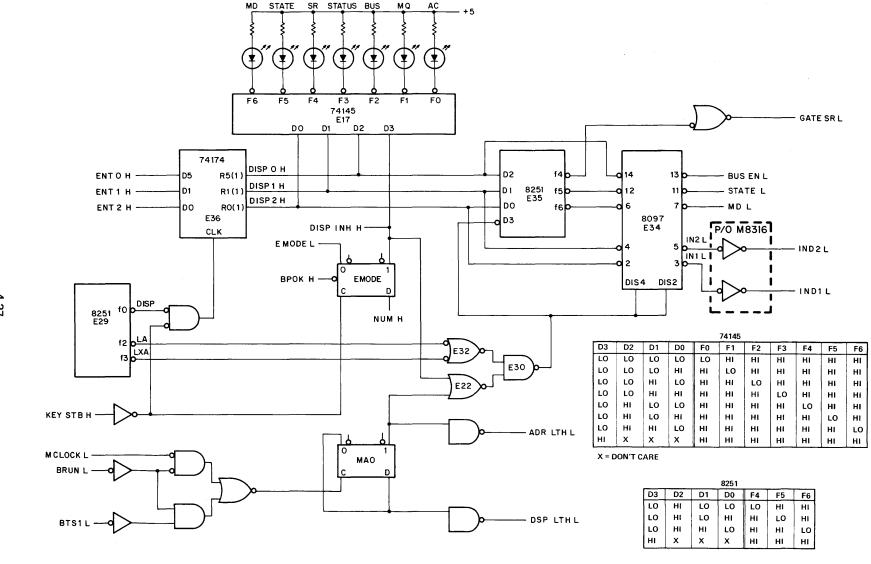

| 4.3.2     | Programmer's Console                        | 4-16 |

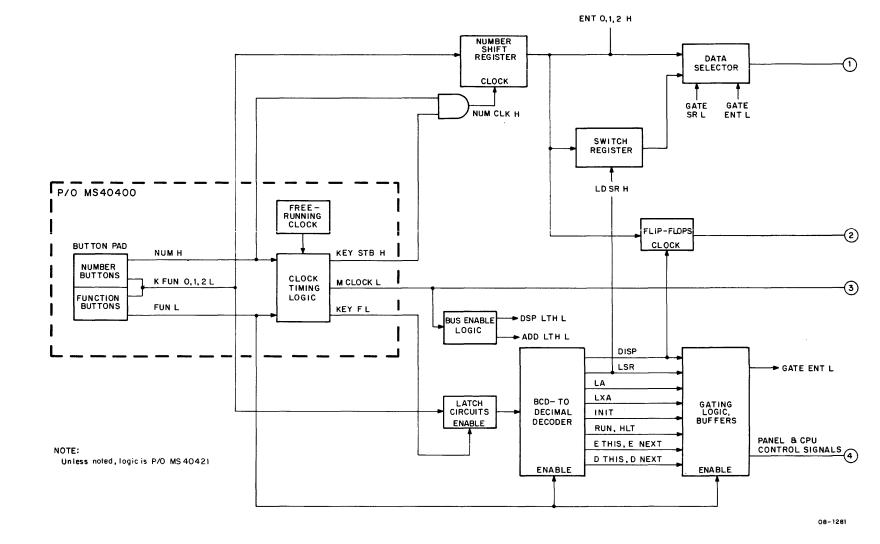

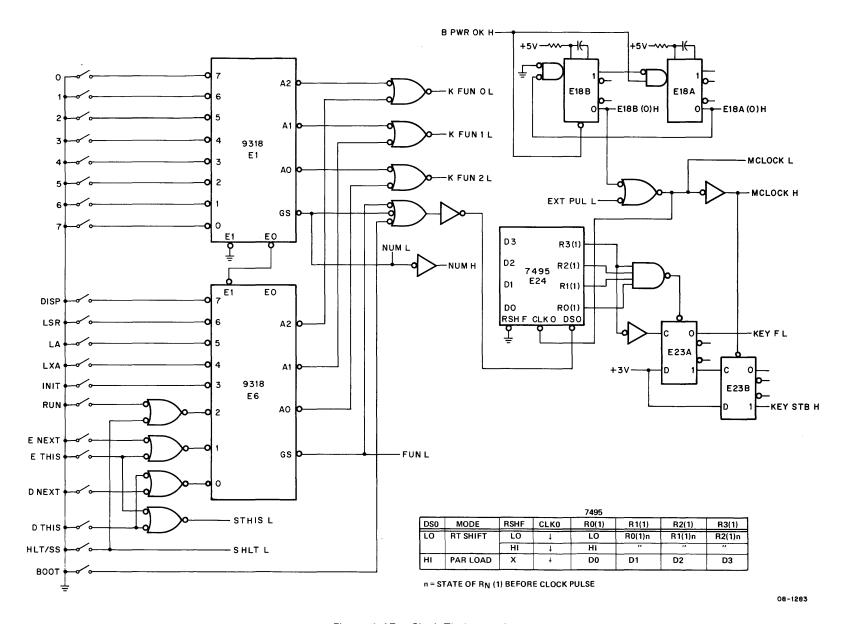

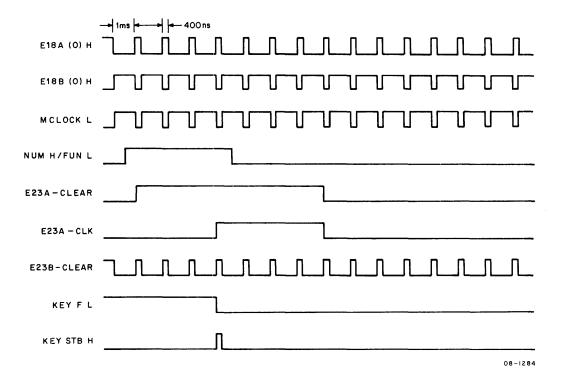

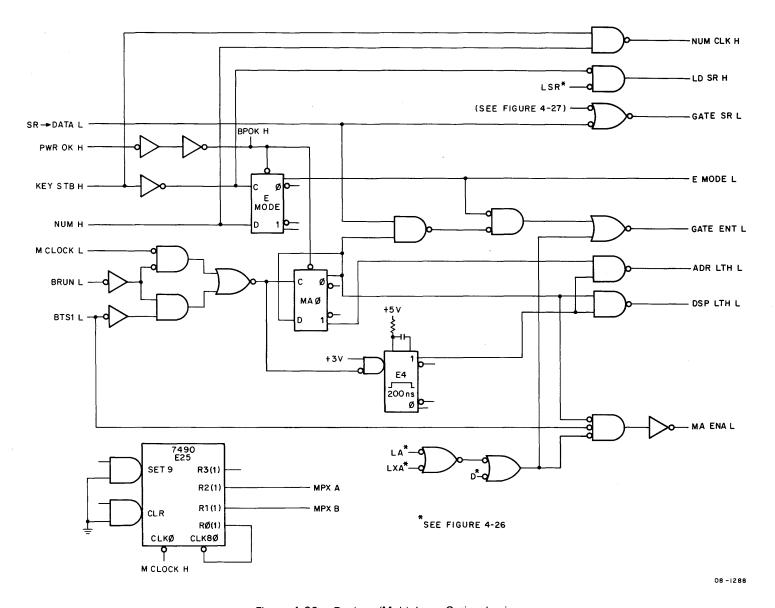

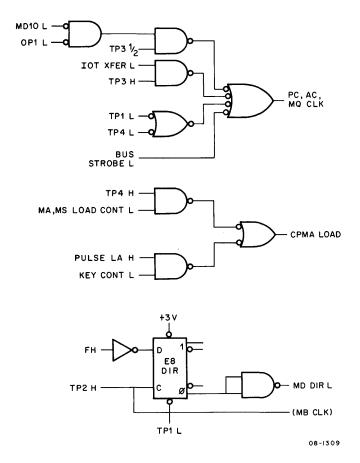

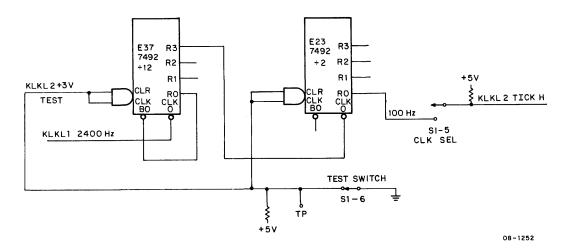

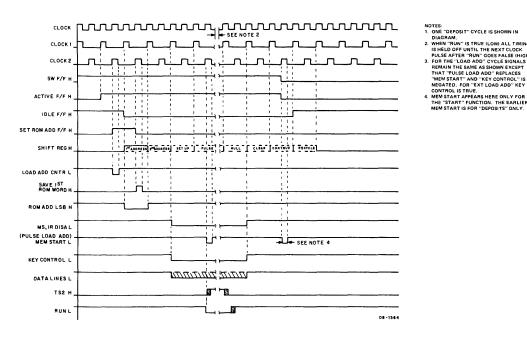

| 4.3.2.1   | Clock Timing Logic                          |      |

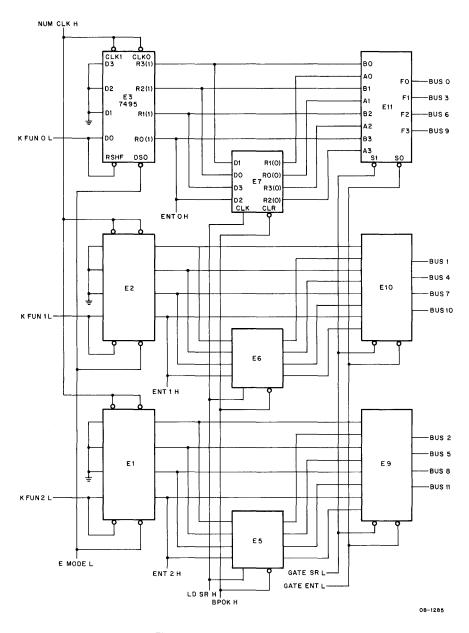

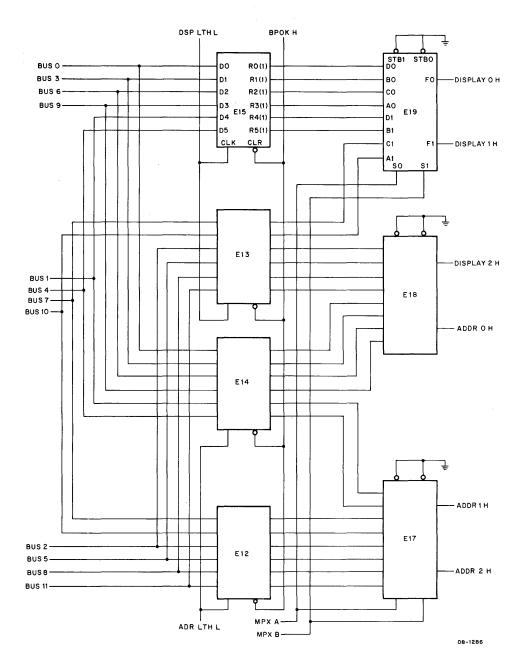

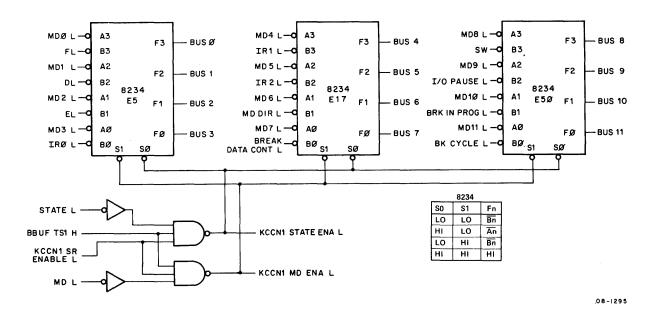

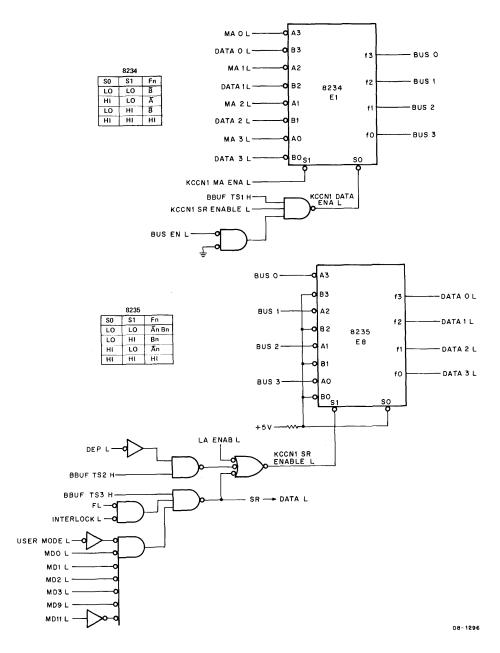

| 4.3.2.2   | Register Logic                              |      |

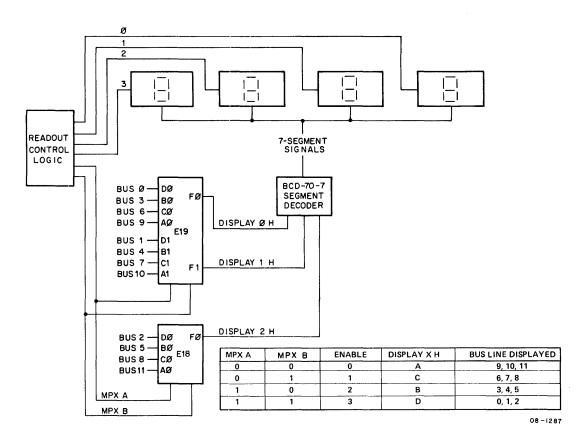

| 4.3.2.3   | Multiplexer Logic                           |      |

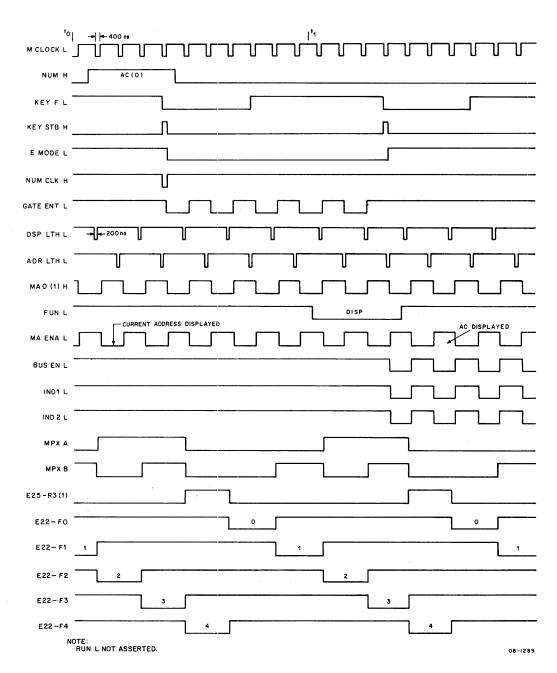

| 4.3.2.4   | Register/Multiplexer Gating Logic Timing    | 4-27 |

| 4.3.2.5   | ADDRS/DISP Readout Circuit Logic            |      |

| 4.3.2.6   | Function Button Logic                       |      |

| 4.3.2.7   | DISP Button Logic                           |      |

| 4.3.2.8   | THIS, HLT, BOOT Logic                       | 4-39 |

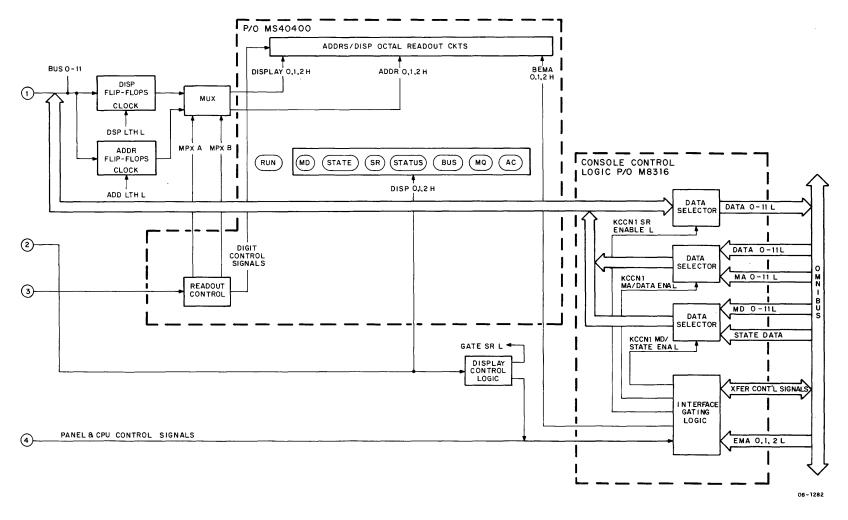

| 4.3.2.9   | Console Control Logic                       | 4-40 |

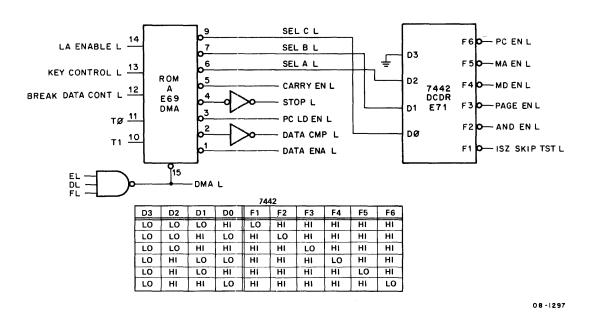

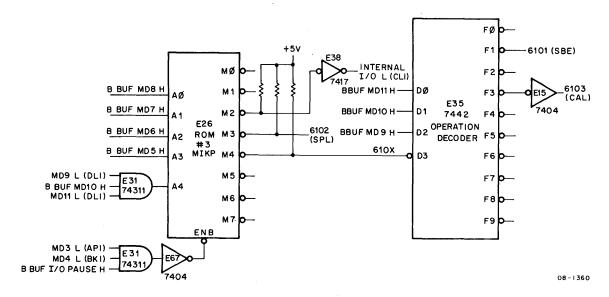

| 4.4       | INSTRUCTION DECODER                         |      |

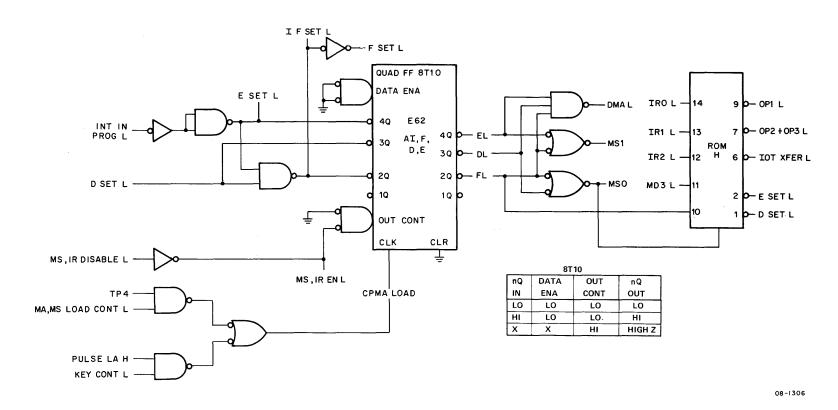

| 4.4.1     | Instruction Register Logic                  |      |

| 4.4.2     | Major State Register Logic                  |      |

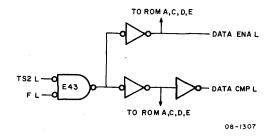

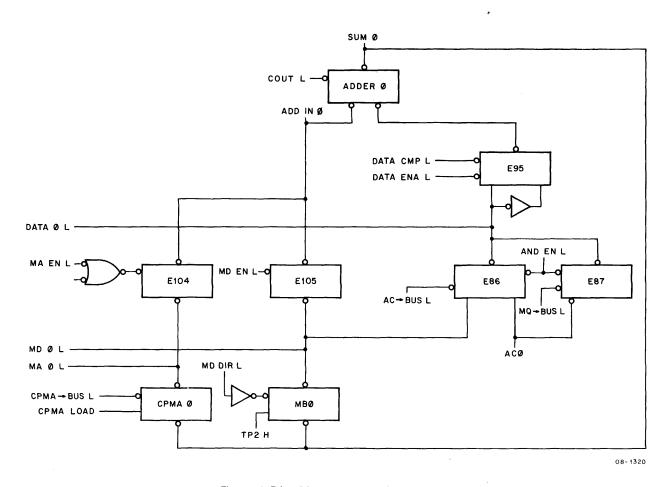

| 4.4.3     | DATA ENA/DATA CMP Logic                     |      |

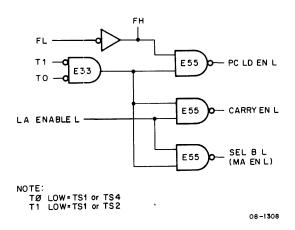

| 4.4.4     | Address Update Logic                        |      |

| 4.4.5     | Major Register Load Signal Logic            |      |

| 4.4.6     | AC Register Control Logic                   |      |

| 4.5       | MAJOR REGISTER GATING                       |      |

| 4.5.1     | Page Logic                                  |      |

| 4.5.2     | Carry In Logic                              |      |

|                    |                                                            | Page |