**Preliminary**

Product Specification and Hardware Reference Manual

# 8603/8605 PROCESSOR

Document No. 61636

August 1983

PRELIMINARY 8603/8605 PRODUCT SPECIFICATION AND HARDWARE REFERENCE MANUAL

August 1983

Document No. 61636. Rev. 8/83. Copyright © 1983 by DATAPOINT Corporation. All rights reserved. The "D" logo, DATAPOINT, DATASHARE, ARC and ATTACHED RESOURCE COMPUTER are trademarks of DATAPOINT Corporation and are registered in the U.S. Patent and Trademark Office. RESOURCE MANAGEMENT SYSTEM and RMS are trademarks of DATAPOINT Corporation.

System features and technical details are subject to change without notice.

## TABLE OF CONTENTS

| PART | <del>-</del>                                          |

|------|-------------------------------------------------------|

|      | RAL FEATURES                                          |

| 1.1  | Introduction                                          |

| 1.2  | Internal Bus Architecture                             |

| 1.3  | Keyboard/Display Subsystem                            |

| 1.4  | Memory                                                |

| 1.5  | Processor                                             |

| 1.6  | Disk Interface Options                                |

|      | Multiport Communications Adapter (MPCA) Option        |

| 1.8  | Multifunction Communications Adapter (MFCA) Option    |

| 1.9  | Parallel Bus Adapter Option                           |

|      | Ancillary Equipment                                   |

| 1.11 | General Specifications                                |

| 1.12 | Peripherals                                           |

| 1.13 | Model Codes                                           |

|      |                                                       |

| PART |                                                       |

|      | RNAL BUS ARCHITECTURE                                 |

| 2.1  | General                                               |

| 2.2  | Interrupts                                            |

| 2.3  | Direct Memory Access                                  |

| 2.4  | Common Bus Signals                                    |

|      | 2.4.1 Multiplex Signals                               |

|      | 2.4.2 Cycle Controls                                  |

|      | 2.4.3 Interupt Control Signals                        |

|      | 2.4.4 DMA Control Signals                             |

|      | 2.4.5 Miscellaneous Signals                           |

| 2.5  | Read/Write Cycles                                     |

| 2.5  | Interrupt Cycles                                      |

| 2.7  | Priority Transfer Cycles                              |

| PART | 2                                                     |

|      | DARD AND DISPLAY SUBSYSTEM (KDS)                      |

| 3.1  | General                                               |

|      | Keyboard                                              |

|      | 3.2.1 Keyboard Control                                |

|      | 3.2.2 Special Key Sequence Controls                   |

| 3.3  | Display                                               |

|      | 3.3.1 Display Character Format                        |

|      | 3.3.2 Video Attributes                                |

|      | 3.3.3 Character Font Load                             |

| 3.4  | Serial I/O Port                                       |

|      | KDS Programming Considerations                        |

| J. J | 3.5.1 Keyboard and Screen                             |

|      | 3.5.2 Speaker Commands                                |

|      | 3.5.3 Video Attributes                                |

|      | 3.5.4 Serial I/O Port                                 |

|      | 3.3.4 Deliai 1/0 Follossessessessessessessessessesses |

| PART       |                                           |

|------------|-------------------------------------------|

| MEMOR      |                                           |

|            | General29                                 |

| 4.2        | Parity Memory29                           |

|            | 4.2.1 Word Read (Parity Memory)29         |

|            | 4.2.2 Byte Read (Parity Memory)           |

|            | 4.2.3 Word Write (Parity Memory)30        |

|            | 4.2.4 Byte Write (Parity Memory)30        |

|            | 4.2.5 Refresh Cycles (Parity Memory)30    |

|            | 4.2.6 Cycle Arbitration (Parity Memory)32 |

|            | 4.2.7 Error Detection (Parity Memory)32   |

| 4.3        | ECC Memory32                              |

|            | 4.3.1 Word Read (ECC Memory)33            |

|            | 4.3.2 Byte Read (ECC Memory)34            |

|            | 4.3.3 Word Write (ECC Memory)34           |

|            | 4.3.4 Byte Write (ECC Memory)34           |

|            | 4.3.5 Refresh Cycles (ECC Memory)34       |

|            | 4.3.6 Error Detection (ECC Memory)35      |

|            | 4.3.7 Diagnostic Features (ECC Memory35   |

|            | ,                                         |

| PART       | 5                                         |

| PROCE      |                                           |

|            | General                                   |

| J•1        | 5.1.1 CP/RIM I & II Differences           |

| 5.2        | Registers42                               |

| J • Z      | 5.2.1 User Registers                      |

|            | 5.2.2 Condition Code Flags                |

|            | 5.2.3 System Status Register              |

|            | 5.2.4 System Control Register             |

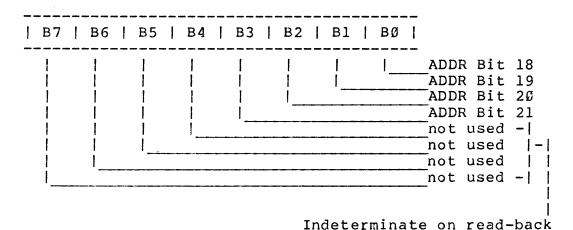

|            | 5.2.5 Base Register                       |

| 5.3        | Sector Tables                             |

|            | Address Generation                        |

|            | Stack                                     |

| 5.6        | Input/Output47                            |

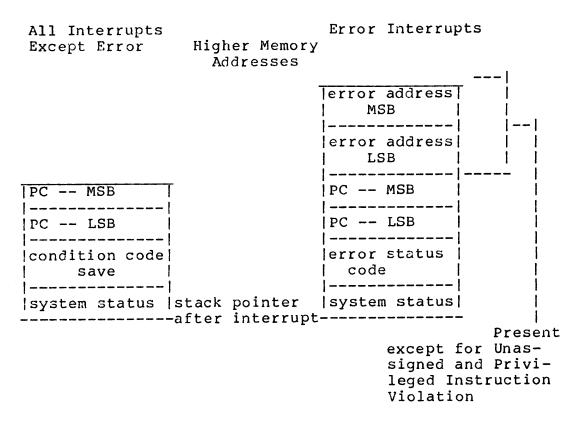

| 5.7        | Interrupts                                |

| J•/        | 5.7.1 Millisecond Interrupt               |

|            | 5.7.2 Restart Interrupt                   |

|            | 5.7.3 Error Interrupt                     |

|            |                                           |

| 5.8        | 5.7.4 Vector Interrupt                    |

|            | CP/RIM Indicator Port                     |

| 5.9        |                                           |

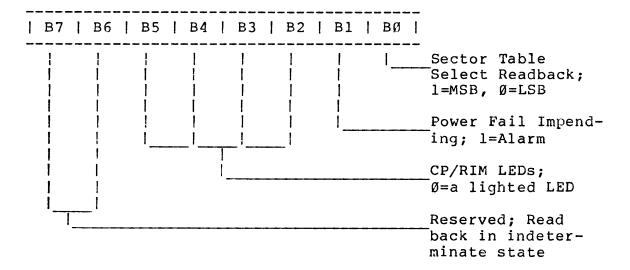

|            | 5.9.1 Input Indicator Port                |

|            | 5.9.2 Output Indicator Port               |

| 5.10       | System/Auxiliary ROM52                    |

| PART       | 6                                         |

|            | OURCE INTERFACE MODULE                    |

| 6.1        | General53                                 |

|            | Register Description54                    |

| 0.2        | FA                                        |

|            | 6.2.1 Read Status Register                |

|            | 6.2.3 Write RIM Commands                  |

| <i>c</i> 3 |                                           |

| 6.3        | Operation                                 |

|            | 6.3.1 Transmit                            |

| PART   | 7                                                    |

|--------|------------------------------------------------------|

|        | BUS INTERFACE MODULE (MIFM)                          |

|        | General59                                            |

| 7.2    | The Microbus59                                       |

|        | 7.2.1 Microbus Signals59                             |

|        | 7.2.2 Microbus Timing                                |

|        | 7.2.3 Microbus Input/Output Cycles61                 |

|        | 7.2.4 Microbus Interrupt Cycle                       |

| 7.3    | Software Interface                                   |

|        | 7.3.1 MIFM Instruction Coding                        |

|        | 7.3.2 MIFM Status Byte                               |

|        | 7.3.4 Polling Function Programming Considerations65  |

|        | 7.5.4 Politing function Programming Considerations55 |

| PART   | Ω                                                    |

|        | PHERAL INPUT/OUTPUT MODULE                           |

|        | General                                              |

|        | Peripheral Input/Output Bus                          |

| 0 . 2. | 8.2.1 Control Characters                             |

|        | 8.2.2 Addressing                                     |

| 8.3    | PIO Module Transmitter Logic                         |

| 8.4    | PIO Module Receiver Logic                            |

|        |                                                      |

| PART   | 9                                                    |

|        | LEL BUS ADAPTER                                      |

| 9.1    | General71                                            |

| 9.2    | Compatibility71                                      |

| 9.3    | Electrical Characteristics71                         |

| 9.4    | I/O Address Decode74                                 |

| 9.5    | Parity                                               |

| 9.6    | Status Register                                      |

| 9.7    | Indicators                                           |

| 9.8    | Parallel Bus Instruction Emulation                   |

| 9.9    | I/O Interface78                                      |

| D3.D0  | 1 a                                                  |

| PART   |                                                      |

|        | PORT COMMUNICATIONS ADAPTER (MPCA) General79         |

| 10.1   | Microprocessor                                       |

| 10.3   | Memory79                                             |

| 10.4   | UARTS                                                |

| 10.5   | Baud Rate Generators                                 |

| 10.6   | CPU Interface                                        |

| 10.7   | Interrupt Structure                                  |

| 10.8   | Firmware82                                           |

| 10.9   | Diagnostics82                                        |

|        | 21 mg. 10 2 0 10 0 10 10 10 10 10 10 10 10 10 10 10  |

| PART   | 11                                                   |

| MULTI  | FUNCTION COMMUNICATIONS ADAPTER (MFCA)               |

| 11.1   | General83                                            |

| 11.2   | Microprocessor83                                     |

| 11.3   | Serial Interface83                                   |

| 11.4   | Counter/Timer Circuit85                              |

| 11.5   | Memory                                               |

| 11.6  | Interr   | upt       | Str   | ıctı  | ıre.  |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    | •    | 86 |

|-------|----------|-----------|-------|-------|-------|------|-----------|-----|-----------|---|-----|-----|-----|-----|-----|-----|-----|-----|---|---|----|------|----|

| 11.7  | Firmwa   | re.       |       |       |       |      |           |     | • • •     |   |     |     |     |     |     |     |     |     |   |   |    |      | 86 |

| 11.8  | Diagno   | sti       | cs    |       |       |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    |      | 86 |

|       |          |           |       |       |       |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    |      |    |

| PART  |          |           |       |       |       |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    |      |    |

| SYSTE | M FIRMV  |           |       |       |       |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    |      |    |

| 12.1  | Introd   |           |       |       |       |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    |      |    |

| 12.2  | Initia   | aliza     | ation | 1     |       |      |           |     |           |   | • • |     |     |     |     |     |     |     |   |   |    |      | 87 |

| 12.3  | Diagno   | sti       | cs    |       |       |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    |      | 87 |

| 12.4  | System   | ı RA      | M Vec | ctor  | s.    |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    |      | 39 |

| 12.5  | IPL B1   |           |       |       |       |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    |      |    |

| 12.6  | Extern   |           |       |       |       |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    |      |    |

|       | 12.6.1   |           | eter  |       |       |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    |      |    |

|       | 12.6.2   |           | 86KE  |       |       |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    |      |    |

|       | 12.6.3   |           | 86KD  |       |       |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    |      |    |

|       | 12.6.4   |           | 85CH  |       |       |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    |      | -  |

|       | 12.6.5   |           | 86DSI |       |       |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    |      |    |

|       | 12.6.6   | •         | 86DSI |       |       |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    |      | _  |

|       | 12.6.7   | -         | 86CR  |       |       |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    |      |    |

|       | 12.6.8   | •         | 86CL  |       |       |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    |      |    |

|       | 12.6.9   | •         | 86RS1 |       |       |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    |      |    |

|       | 12.6.3   | •         | 86D09 |       |       |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    |      |    |

|       | 12.6.1   |           |       |       |       |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    |      |    |

|       |          |           | TRKL  |       |       |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    |      |    |

|       | 12.6.1   |           | CONB  |       |       |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    |      |    |

|       | 12.6.1   | _         | OMIMS |       |       |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    |      |    |

|       | 12.6.1   |           | ECCS  |       |       |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    |      |    |

| 12.7  | Debug.   |           |       |       |       |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    |      |    |

|       | 12.7.1   |           | ntry  |       |       |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    |      |    |

|       | 12.7.2   |           | aving |       |       |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    |      |    |

|       | 12.7.3   |           | ommar |       |       |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    |      |    |

|       | 12.7.4   |           | ommar |       |       |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    |      |    |

|       | 12.7.5   | 5 I       | nput  | Con   | mar   | nd I | Lis       | t.  |           |   |     |     |     |     |     |     | • • | • • |   | • |    | . 1! | 02 |

|       |          |           |       |       |       |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    |      |    |

|       | IDIX A   |           |       |       |       |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    |      |    |

|       | LLARY EQ |           |       |       |       |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    |      |    |

|       | General  |           |       |       |       |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    |      |    |

| A.2   | Power S  | Supp      | 1y    |       |       |      |           | • • |           |   |     |     | • • |     |     |     | • • |     |   |   |    | 1.   | 11 |

|       | A.2.1    | Pro       | tecti | ion   | Fea   | atu  | ces       |     |           |   |     |     |     |     |     |     |     |     |   |   |    | 1.   | 11 |

|       | A.2.2    | Pow       | er Fa | ail   | Ala   | arm  |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    | 1.   | 13 |

| A.3   | Motherh  | oar       | ₫     |       |       |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    | 1    | 13 |

|       | A.3.1    | Sign      | nal ( | Conf  | iqu   | ıra  | tio       | n.  |           |   |     |     |     |     |     |     |     |     |   |   |    | 1    | 13 |

|       | A.3.2    | Ope       | n Col | llec  | toi   | s S: | ign       | als | s.,       |   |     |     |     |     |     |     |     |     |   |   |    | 1.   | 13 |

|       | A.3.3    |           |       |       |       |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    |      |    |

|       | A.3.4    |           |       |       |       |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    |      |    |

|       |          |           | Pric  |       |       |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    |      |    |

|       |          | a a + & A |       | (     | - I - |      | - 1       | ~(  | <u></u> L | • | - • | - • | - • | - • | •   | •   | . • | . • | • | • | •• | _    |    |

| APPEN | IDIX B   |           |       |       |       |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    |      |    |

|       | RUCTION  | ттм       | INGS  |       |       |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    | 1    | 15 |

|       |          | 1         |       | • •   | - • • |      | - <b></b> | - • |           | • | - • | •   | ••  | ••  | •   | - • | •   | •   | • | • | •  | -    |    |

| APPEN | DIX C    |           |       |       |       |      |           |     |           |   |     |     |     |     |     |     |     |     |   |   |    |      |    |

|       | COMMON   | BIIS      | T / O | זרו ג | RES   | SSE  | 5.        |     |           |   |     |     |     | _   |     | _   |     |     |   |   |    | 1    | 21 |

| U 17  | ~ ~      |           | -/ -  |       |       |      |           | - • |           | • | - • | • • | - • |     | - • | - • | • • |     |   | • |    | -    |    |

## LIST OF FIGURES

| Figure |                                             | Page |

|--------|---------------------------------------------|------|

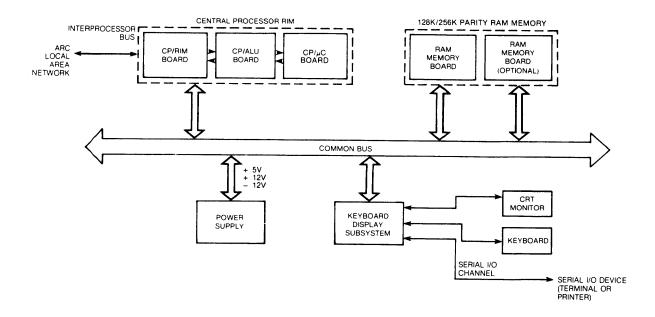

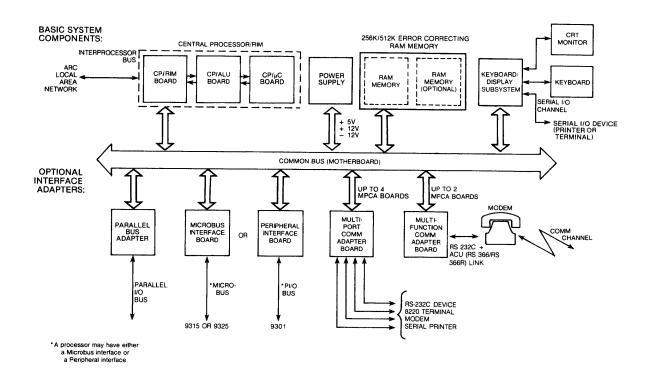

| 1-1    | 8603 Processor Block Diagram                |      |

| 1-2    | 8605 Processor Block Diagram                | 2    |

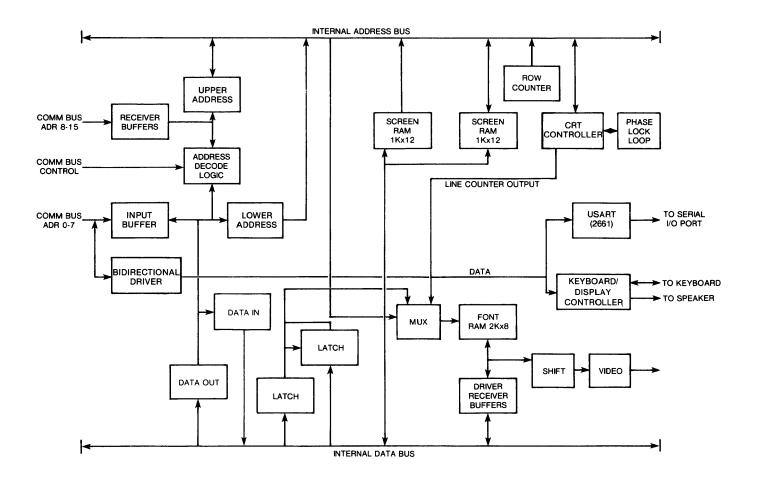

| 3-1    | KDS Module                                  |      |

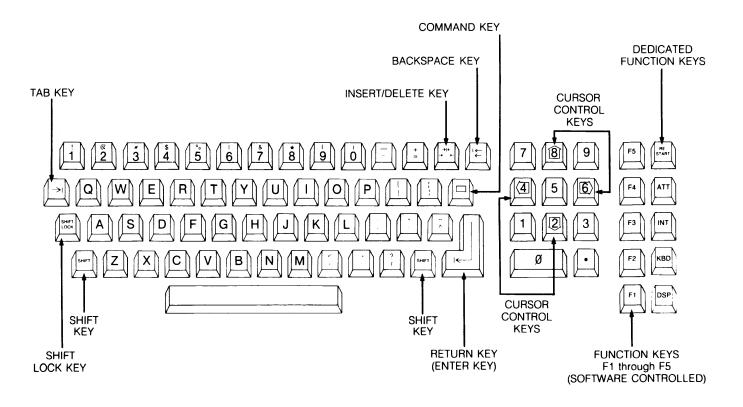

| 3-2    | General Purpose Keyboard                    |      |

| 3-3    | Character Row                               | 18   |

| 3-4    | Status Register                             | 26   |

| 3-5    | Command Register                            | 26   |

| 3-6    | Mode Register 1                             | 27   |

| 3 - 7  | Mode Register 2                             | 27   |

| 4-1    | Parity Memory Module                        | 31   |

| 4 - 2  | ECC Memory Block Diagram                    | 33   |

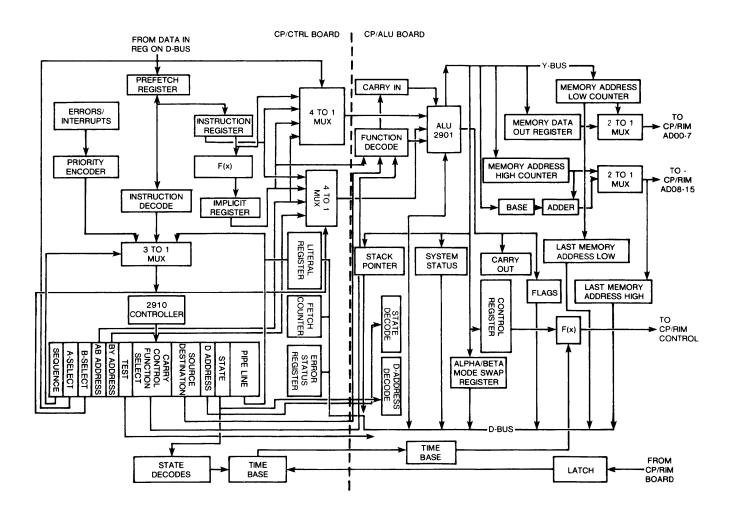

| 5 - 1  | CP/ALU and CP/CTRL Boards                   | 40   |

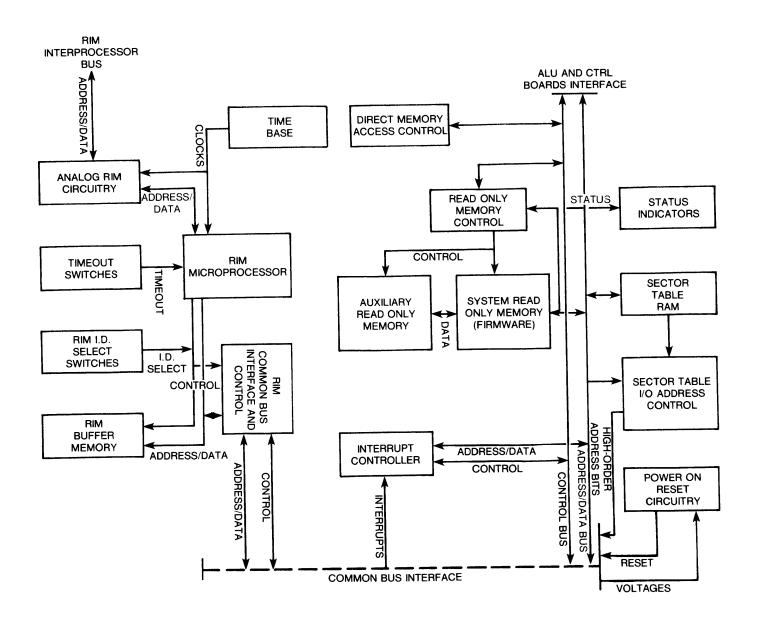

| 5-2    | CP/RIM Board                                | 41   |

| 5-3    | Stack Information After Interrupt           | 48   |

| 5-4    | Vector Interrupt Table Format               | 5Ø   |

| 5-5    | Interrupt Mask Byte Format                  | 51   |

| 6-1    | RIM I/O Allocation                          |      |

| 5-2    | RAM Buffer Packet Configuration             | 58   |

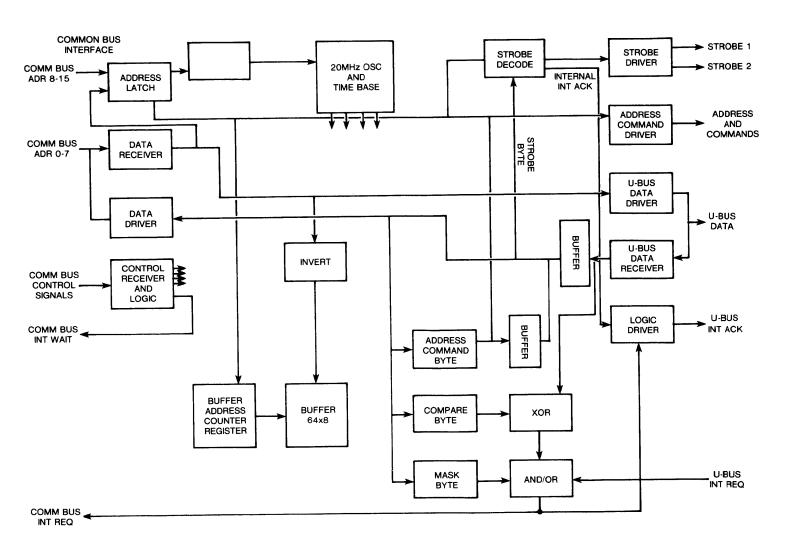

| 7-1    | Microbus Interface Module (MIFM)            |      |

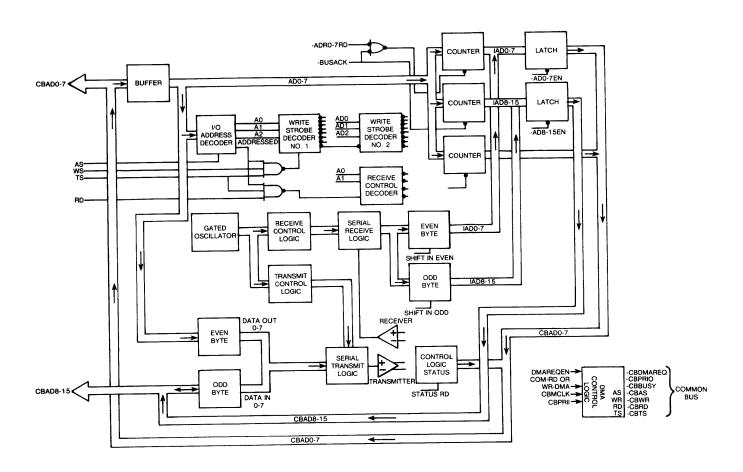

| 8-1    | Peripheral Input/Output Module              |      |

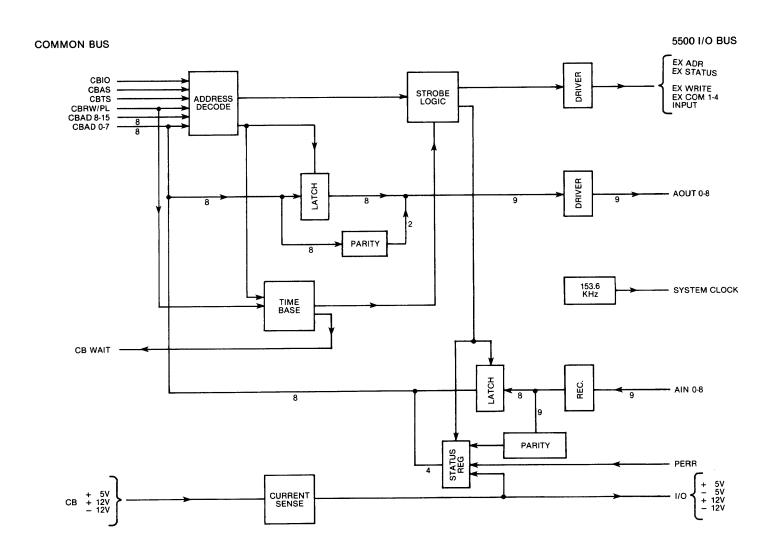

| 9-1    | Parallel Bus Block Diagram                  |      |

| 9-2    | Parallel Bus Drivers/Receivers              |      |

| 9-3    | PBA Address Structure                       |      |

| 10-1   | Multiport Communications Adapter Board      |      |

| 11-1   | Multifunction Communications Adapter Board. |      |

| 12-1   | System RAM Vectors                          |      |

| A-1    | Power Supply                                |      |

|        | ·                                           |      |

## LIST OF TABLES

| Table |                              | Page |

|-------|------------------------------|------|

| 3-1   |                              |      |

| 7-1   | MIFM Instruction Coding      | 64   |

| 9-1   | Status Register              |      |

| 12-1  | Keyboard Codes               | 88   |

| 12-2  | Default Character Font       | 109  |

| 12-3  | Debugger Sector Table Format | 110  |

#### PREFACE

The computer-oriented user will find this manual useful in evaluating the capabilities of the DATAPOINT® 8600 processor. However, only the hardware considerations are covered in this manual. The full utility of the Datapoint 8600 cannot be appreciated until the available software support for the machine is reviewed.

A complete family of software packages available for the 8600 processor includes items such as high-level languages, operating systems, source code and text editors, communications programs, and utility programs. Please refer to the latest issue of the Datapoint Software Catalog for the most complete information.

Warning: This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause interference to radio communications. It has been tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference, in which case the user, at his own expense, will be required to take whatever measures may be required to correct the interference.

## INTRODUCTION

This manual is designed to provide the programmer or other sophisticated user with the detailed information necessary for systems level programming of the DATAPOINT 8600 Business Computer.

Other manuals that may be helpful include the Product Specifications and Operator's Guides for individual components in the system as well as the appropriate software User's Guides.

## PART ONE GENERAL FEATURES

#### 1.1 Introduction

The DATAPOINT 8600 is a versatile, high-performance processor featuring up to 512K bytes of memory. The 8600 supports both of the DATAPOINT operating systems (DOS, the Disk Operating System and RMS, the Resource Management System™) and is compatible with a wide range of peripherals. Including a large, easy-to-read amber display screen and a typewriter-style keyboard, the 8600 may function as part of a stand-alone system, as the host processor for a DATASHARE® Business Timesharing System, or as a member of an Attached Resource Computer® (ARC™) local area network.

Printed circuit boards contain all of the 8600's logical subassemblies; these boards are contained in an internal nine-slot card cage and linked by the DATAPOINT common bus. The basic 8600 processor includes a three-card central processor, 128K or 256K bytes of memory, a Keyboard/Display Subsystem (KDS) module, a serial port, and an internal Resource Interface Module (RIM). The 8600 also includes an internal power supply that provides DC power for the keyboard, display, and logic boards.

The 8603 processor is designed to perform as an ARC applications processor for tasks requiring full processor power in a single workstation. The only configurable option for an 8603 is memory size (a maximum of 256K of parity memory).

The 8605 processor—with 256K or 512K of ECC (Error Correction Code) memory—supports all feature options, including additional ECC memory, the Multiple Port Communications Adapter (MPCA), the Multiple Function Communications Adapter (MFCA), the Parallel Bus Adapter (PBA), and the PIO or Microbus disk interface. The 8605 is also available in system configurations with the DATAPOINT 9301, 9315, 9324, and 9325 disk drives for stand-alone or ARC operation. An 8603 can be converted to an 8605 with a field upgrade kit.

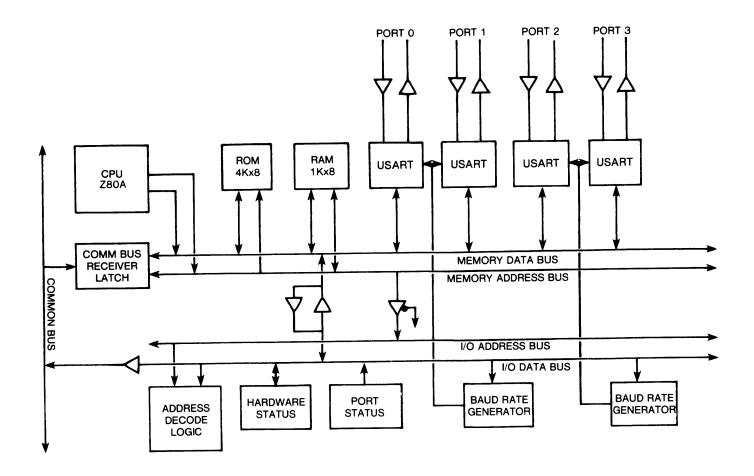

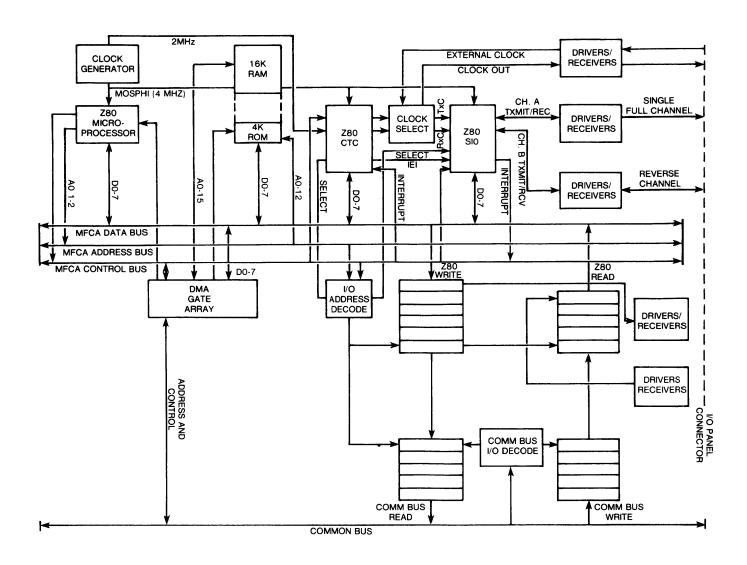

Figures 1-1 and 1-2 illustrate the 8603 and 8605 processors. The following sections introduce the basic elements of the 8600 processor family.

Figure 1-1: 8603 Processor Block Diagram

Figure 1-2: 8605 Processor Block Diagram

### 1.2 Internal Bus Architecture

The 8600 uses an internal bus to provide the interface between the processor, memory, Keyboard/Display Subsystem, and the internal option cards. This bus is implemented on the CP/RIM module through the motherboard and is referred to as the Common Bus.

To communicate with disk storage systems, the 8600 uses one of two external buses, either the Peripheral Input/Output (PIO) bus or the microbus. An external bus is linked directly to one of two types of internal logic boards (either a PIO module or a Microbus Interface Module, as explained in Section 1.6), which in turn is linked to the processor and main memory through the Common Bus.

## 1.3 Keyboard/Display Subsytem

The Keyboard/Display Subsystem (KDS) provides the interface between the keyboard and the processor. The KDS also controls the display screen and includes a serial I/O port for interface to a DATAPOINT serial printer or 8200-type terminal.

The 8500 is equipped with the DATAPOINT General Purpose Keyboard, which contains a 55-key typewriter pad, an ll-key numeric pad, and a 10-key function pad. The keyboard, which includes multi-key roll-over for ease of typing, is connected to the processor housing by a one-meter cord.

The display screen uses a cathode ray tube illuminated by a magnetic deflection technique. It displays 1920 characters, organized as 24 rows of 80 characters each. Character attributes such as inverse video, underlining, two-level video, and blink are available on a character-by-character basis under software control. The display uses a standard set of 128-characters or a user-defined font. The viewing area is 5.4 by 8.9 inches (13.7 by 22.6 cm), and standard characters are produced using a 7- by 9-dot matrix in a 9-by 12-dot field; the display refresh rate is line synchronized at 60/50 frames per second. Display brightness can be set to one of 16 levels from the keyboard; beep and click are available under software control.

### 1.4 Memory

The basic 8603 includes 128K bytes of parity memory and is expandable to 256K. An 8605 includes 256K or 512K of ECC (Error Correction Code) memory. Memory modules are linked to the Common Bus and may be addressed by word or byte under software control.

#### 1.5 Processor

The S600's central processor is implemented on three logic boards. The CP/mC (Microcode) board contains the instruction-decoding ROMs, the control store, and the sequencer. The CP/ALU (Arithmetic Logic Unit) encompasses most of the processor registers and manages the data flow within the machine. The CP/RIM (Resource Interface Module) contains the system and auxiliary ROM, the sector tables, and an integral RIM (the interface to the DATAPOINT Attached Resource Computer local area network).

The processor employs the DATAPOINT instruction set, and is driven by vectored interrupts, which means that it responds directly to interrupting devices. Access protect or write protect (or both) can be performed on 4K blocks of memory. Four sector tables are organized into system and user areas; the processor uses a 32-word stack located in the main memory and can use a stack exchange for multiple stacks. System and auxiliary ROMs contain system functions such as power-up, keyboard and display drivers, and interrupt, debug, and diagnostic routines.

## 1.6 Disk Interface Options

The 8605 communicates with disk systems through an internal printed circuit board. The processor supports two types of disk interface boards, the Peripheral Input/Output module (PIO) and the Microbus Interface Module (MIFM). The PIO module provides an interface to the DATAPOINT series of disk drives through the PIO bus; the MIFM module provides an interface to the Datapoint 9310, 9315, 9324, and 9325 disk drives and the 1401 diskette drive through the microbus. Either interface may be ordered with the 8605.

## 1.7 Multiport Communications Adapter (MPCA) Option

The MPCA logic board supports four serial asynchronous RS-232-C communications ports; each port has full duplex transmit and receive capability. Data transfer rates are software-programmable from 50 to 19,200 baud; character lengths and the number of stop bits are individually programmable. The MPCA provides parity bit generation and detection and includes a microprocessor, local memory, baud rate generators, and four UARTs (Universal Asynchronous Receiver/Transmitters). The 8605 processor can be configured with a maximum of four MPCAs.

## 1.8 Multiple Function Communications Adapter (MFCA) Option

The MFCA logic board provides a means of synchronous or asynchronous bidirectional information transfer between the processor an an RS-232-C compatible communications channel with reverse channel. The MFCA may be connected to an external modem and an RS-366 compatible Automatic Calling Unit (ACU) and can communicate over switched or leased lines using software-loadable communications protocols such as BISYNC, SDLC, HDLC, ADCCP, or GENSYNC. Baud rates are programmable, from 110 to 19.2K. The MFCA includes a microprocessor, a serial input/output channel, a counter/timer circuit, and 16K bytes of parity-protected local memory. The 8605 can be configured with a maximum of two MFCAs.

## 1.9 Parallel Bus Adapter Option

The Parallel Bus Adapter is used to connect peripheral devices that contain DATAPOINT parallel interfaces to the 8602 and 8605 processors. These peripheral devices include printers, magnetic tape drives, and communications adapters.

The Parallel Bus Adapter implements all of the signals required for compatibility with the DATAPOINT 5500 and 6600 processor I/O buses (the Parallel Bus Adapter does not supply power to external devices). The adapter supplies +5V at 1.8 amperes (+5%, -10%VDC) on the I/O bus to power the handshake circuits in a maximum of eight peripheral devices.

The logic is composed of data receivers and drivers, strobe drivers, parity generators and checkers, the time base, and diagnostic logic. Due to the functions performed by the Parallel Bus Adapter, only one may be configured with an 8605.

## 1.10 Ancillary Equipment

In addition to the components discussed above, the 8600 includes an internal power supply and a motherboard. The power supply is housed in the internal card cage and provides DC power for the keyboard, the Keyboard/Display Subsystem, and the logic boards. The motherboard is a nine-card backplane that implements the 8600 Common Bus and a tenth card slot which is reserved for the power supply.

## 1.11 General Specifications

Power Requirements: 120 or 240 VAC (+/-10%) 50 or 60 Hz (+/-1 Hz) 230 watts (785 BTU/hour, maximum)

## Equipment Dimensions:

Keyboard

Width: 20.00 inches (50.8 cm) Height: 2.75 inches (7.0 cm) Depth: 8.90 inches (22.6 cm)

#### Processor:

Width: 20.00 inches (50.8 cm)

Height: 13.20 inches (33.5 cm) without base

Depth: 14.50 inches (36.8 cm)

Weight: 60.00 pounds (22.4 kg)

## Operating Environment:

50 to 100 degrees Fahrenheit

10 to 38 degrees Celsius

20 to 90 percent relative humidity, noncondensing

## 1.12 Peripherals

The 8600 accommodates a wide variety of peripherals, including the DATAPOINT 9301, 9310, 9315, 9324, and 9325 disk drives, the 1401 diskette drive, printers, and communications equipment. Refer to the DATAPOINT Equipment Catalog (Model Code 60001) for a complete description of peripherals.

## 1.13 Model Codes

8603 Applications Processor, 128K-256K parity memory

8605 Stand-alone/Data Resource Processor, 256K-512K ECC memory

NOTE: The 8603 and 8605 supersede the earlier 8601 and

8602 processor models.

## PART 2 INTERNAL BUS ARCHITECTURE

#### 2.1 General

The 8600 uses an internal bus, referred to as the Common Bus, as an interface between the processor, memory, and peripheral attachments. The Common Bus provides continuous instruction cycles. Each instruction cycle contains three or more clock cycles, which are referred to as T-states. Timing flexibility is provided by optional wait states.

The first T-state (T1) provides address and control information on the Common Bus, which is latched with an address strobe. Address is replaced with data during T2, and a read or write signal is provided along with a Transfer Strobe. In T3, data is transferred and then removed from the bus.

## 2.2 Interrupts

The Common Bus uses vectored interrupts. In this scheme, eight interrupt requests are provided. Each of these requests generates a two-byte entry address when acknowledged. The interrupt routine may then poll individual devices if more than one is sharing the interrupt address. For interrupt devices that require more than one interrupt, multiple vectors may be created through cascade operation.

The eight interrupt requests are listed below:

CBIREQ Ø MIFM Module

CBIREQ 1 Keyboard

CBIREQ 2 Printer Port

CBIREQ 3 MPCA

CBIREQ 4 PIO Module

CBIREQ 5 RIM

CBIREQ 6 MFCA

CBIREQ 7 Reserved

## 2.3 Direct Memory Access

Direct memory access is a technique by which a peripheral device may obtain control of the Common Bus for direct data storage or retrieval, thus facilitating high-speed data transfers between peripherals and memory. The peripheral device provides all required address registers, count registers, and timing logic. The processor relinquishes the bus in response to a request; the peripheral returns control

of the bus to the processor after the required sequences have been performed.

## 2.4 Common Bus Signals

## 2.4.1 Multiplex Signals

The multiplex signals contain different data during the address and data portions of the cycle. Signals are controlled by the bus master during address. During data time, the data source device gates data or status information onto the bus. The signals (with address and data times) are given below:

|           | Address Time                | Data Time                                             |

|-----------|-----------------------------|-------------------------------------------------------|

| CBAD8-21  | Address positive true       | Data positive true                                    |

| CBADØØ-Ø7 | Address positive true       | Data positive true                                    |

| CBBW/PE/  | Byte mode (1) Word mode (0) | Memory Parity Error (0)<br>No memory Parity Error (1) |

| CBMC/PA/  | Memory cycle (Ø)            | Data Parity available (0)                             |

|           | Not memory cycle (1)        | Not applicable (1)                                    |

| CBRW/PL   | Read cycle (1)              | Odd parity for data bits 0-7                          |

|           | Write cycle (Ø)             | Positive true                                         |

| CBBPIO    | I/O cycle page Ø (Ø)        | Not applicable                                        |

| CBIO/CC/  | I/O cycle (Ø)               | Memory Error detected                                 |

|           | Not I/O cycle (1)           | by memory board (0)                                   |

| CBSRE/    | System ROM addressing(0)    | Not applicable                                        |

| CBRIH/    | Inhibit RAM (Ø)             | Valid only prior to CBRD/or                           |

|           |                             | CBWR/; data time strobe                               |

| CBSS/PH   | Not applicable              | Even parity for bits 8-15, positive true              |

## 2.4.2 Cycle Controls

The cycle control signals provide direct control of all bus timing.

| CBAS/    | Address Strobe - Negative True    |

|----------|-----------------------------------|

| CBRD/    | Read Strobe - Negative True       |

| CBWR/    | Write Strobe - Negative True      |

| CBTS/    | Transfer Strobe - Negative True   |

| CBMCLK   | Memory Clock                      |

| CBIWAIT/ | Input/Output Wait - Negative True |

| CBMWAIT/ | Memory Wait - Negative True       |

## 2.4.3 Interrupt Control Signals

| CBINTA/    | Interrupt Acknowledge - Negative Tru | ıe |

|------------|--------------------------------------|----|

| CBINTCY/   | Interrupt Cycle - Negative True      |    |

| CBINT/     | Interrupt Request - Negative True    |    |

| CBIREQØ-7/ | Interrupt Request - Negative True    |    |

## PART 3 KEYBOARD AND DISPLAY SUBSYSTEM (KDS)

#### 3.1 General

The Keyboard and Display Subsystem (KDS) is a logic board that provides the interface between the keyboard and the central processor. The KDS also controls the display screen and provides a serial I/O port for interface to a DATAPOINT serial printer or terminal. The KDS includes local RAM for screen memory, row pointers, the cursor pointer, and character font storage. A block diagram of the KDS module is shown in Figure 3-1.

Access to the KDS is through I/O address space. Common Bus reads or writes to the KDS are allowed at any time during the video cycle.

## 3.2 Keyboard

The 8600 processor is equipped with the DATAPOINT General Purpose Keyboard, which contains a 55-key typewriter pad, an 11-key numeric pad, and a 10-key function pad. The keyboard is used for data entry and control of the 8600. The keyboard is detached and may be placed up to three feet (one meter) from the processor. Figure 3-2 illustrates the general purpose keyboard. Keyboard coding is given in Table 3-1.

#### 3.2.1 Keyboard Control

The keyboard contains a number of control and function keys; these keys are defined below.

RETURN (ENTER) -- The Return key is under software control. It is normally programmed to do a carriage return, accept data, control entry, and/or start execution.

SHIFT -- The Shift key causes the keyboard to produce upper-case character code. When this key is not pressed, the keyboard produces lower-case character code.

SHIFT LOCK -- The Shift Lock key locks the Shift key in the upper-case position. When Shift Lock is activated, the LED on this key cap is illuminated.

TAB -- The Tab key is used in word processing to advance the cursor to predefined or user-defined

tabular fields within the text. When not used for word processing, this key acts as a Cancel key to move the cursor to the start of a line.

Figure '3-1: KDS Module

NOTE: ARROWS POINT TO EDIT AND CONTROL KEYS

Figure 3-2: General Purpose Keyboard

INSERT/DELETE -- The Insert/Delete key is used in word processing to open text for an insertion when unshifted, or to delete text when shifted. When not used for word processing, this key advances the cursor one position to the right, leaving a space.

COMMAND -- The Command key is used in word processing to enter selected commands. When not used for word processing, the key produces a backslash () when unshifted and an accent grave () when shifted.

BACKSPACE -- This key backspaces the cursor one position, erasing the preceding character.

CURSOR CONTROL -- These keys are used in word processing to move the cursor up, down, left, and right (when unshifted). When shifted, these keys produce the indicated numerals. When not used for word processing, these keys produce only numerals.

INT (Interrupt) -- The INT key, when pressed with the CTRL key, causes the processor to halt and execute the restart routine contained in system ROM. This key is also used in conjunction with the CTRL and DSP keys to cause entry to DEBUG.

CTRL (Control) -- The CTRL key works in conjunction with other function keys to initiate special action.

ATT (Attention) and KBD (Keyboard) -- These keys are used in conjunction with the CTRL key to increase or decrease display brightness.

DSP (Display) -- The DSP key causes entry into DEBUG when used with the CTRL and INT keys.

F1, F2, F3, F4, F5 -- Each of the function keys is under software control.

The INT, CTRL, ATT, KBD and DSP keys can be detected under software control.

#### 3.2.2 Special Key Sequence Controls

The 8600 processor has six functions that can be initiated through the use of special keyboard keys. These functions are listed below, followed by a group of keys that must be held down to control the functions (when more than one key is named, the keys should be held down together):

Restart CTRL, INT (release CTRL or INT)

Restart (RIM boot KBD, DSP, CTRL, INT (release when disk is attached) CTRL or INT))

Brightness Increase CTRL, ATT (release ATT)

Brightness Decrease CTRL, KBD (release KBD)

Keyboard Lockout Depress the CTRL key while

entering the TAB key, zero to four character lock code keys,

and then the ENTER key. Release the CTRL key.

Restart Lockout Same as Keyboard Lockout,

except that the shifted ENTER key is pressed. To check for the presence of Restart Lock-out, depress CTRL and DSP, then release DSP. A beep sounds if

lockout is set.

Restart Unlock Same as Restart Lockout.\*

Keyboard Unlock Same as Keyboard Lockout.\*

Debug DSP, CTRL, INT (release CTRL or

INT).

The brightness level of the display can be set from the keyboard to one of 16 levels. To increase brightness, press the CTRL key followed by the ATT key. Every release of ATT (while CTRL is still being held down) increases the brightness by one level. After a brightness level of zero has been reached, this command is ignored.

To decrease brightness, press the CTRL key followed by the KED key. Every release of KBD (while CTRL is depressed) decreases the brightness by one level. After a brightness level of 15 has been reached, this command is ignored.

<sup>\*</sup>Restart Unlock and Keyboard Unlock can be used interchangeably.

Table 3-1 General Purpose Keyboard Coding

| Α | 101 | а      | 141 | Ø       | ø6ø   | :        | Ø53  |

|---|-----|--------|-----|---------|-------|----------|------|

| В | 102 | b      | 142 | í       | Ø61   |          | Ø73  |

| C | 103 | C      | 143 | 2       | Ø62   | ;<br><   | Ø74  |

| D | 104 | d<br>d | 144 | 3       | Ø63   | =        | 137  |

| E | 105 | e      | 145 | 4       | Ø64   | >        | Ø76  |

|   |     | £      | 146 | 5       | Ø65   |          | Ø77  |

| F | 106 |        |     |         |       | ?        |      |

| G | 107 | g      | 147 | 6       | Ø66   | <u>@</u> | Ø42  |

| H | 110 | h      | 15Ø | 7       | Ø67   |          | 100  |

| I | 111 | i      | 151 | 8       | ø7ø   | ]        | 140  |

| J | 112 | j      | 152 | 9       | ¢71   |          | 135  |

| K | 113 | k      | 153 | Space   | Ø 4 Ø |          | Ø75  |

| L | 114 | 1      | 154 | 1       | Ø41   | {        | 174  |

| M | 115 | m      | 155 | 11      | Ø52   |          | Ø46  |

| N | 116 | n      | 156 | #       | Ø43   | }        | 134  |

| 0 | 117 | 0      | 157 | \$      | Ø44   | ~        | 175  |

| P | 12¢ | р      | 16Ø | ુ<br>સુ | Ø45   | Tab      | Ø33* |

| Q | 121 | q      | 161 | &       | Ø47   | Tab      | 233  |

| Ŕ | 122 | r      | 162 | 1       | Ø72   | Return   | Ø15* |

| s | 123 | s      | 163 | (       | Ø51   | Return   | 215  |

| T | 124 | t      | 164 | ì       | ØØØ   | Backspac |      |

| Ü | 125 | u      | 165 | /<br>*  | Ø5Ø   | Backspac |      |

| V | 125 | v      | 166 | +       | 177   | Insert   | 133* |

| W | 127 |        | 167 |         | Ø54   | Delete   | 173  |

|   |     | W      |     | ,       |       |          | 136* |

| X | 130 | X      | 170 | _       | Ø55   |          |      |

| Y | 131 | Ä      | 171 | •,      | Ø56   | Command  | 176  |

| Z | 132 | Z      | 172 | /       | Ø57   |          |      |

## Numeric Pad

## Function Keys

| Symbol | Unshifted | Shifted | Symi |     | nshifte<br>O** R** |     | fted<br>R** |

|--------|-----------|---------|------|-----|--------------------|-----|-------------|

| •      | 256       | 256     | F5   | 3ØØ | 320                | 34Ø | 320         |

| Ø      | 260       | 36Ø     | F4   | 3Ø2 | 322                | 342 | 322         |

| 1      | 261       | 361     | F3   | 3ø4 | 324                | 344 | 324         |

| 2      | 262       | 362     | F2   | 3Ø6 | 326                | 346 | 326         |

| 3      | 263       | 363     | Fl   | 31Ø | 33Ø                | 35Ø | 33Ø         |

| 4      | 264       | 364     | INT  | 3Ø1 | 321                | 341 | 321         |

| 5      | 265       | 365     | ATT  | 3Ø3 | 323                | 343 | 323         |

| 6      | 266       | 366     | CTRL | 3Ø5 | 325                | 345 | 325         |

| 7      | 267       | 367     | KBD  | 3Ø7 | 327                | 347 | 327         |

| 8      | 270       | 370     | DSP  | 311 | 331                | 351 | 331         |

| 9      | 271       | 371     |      |     |                    |     |             |

<sup>\*</sup>Unshifted representation

NOTE: These are key codes as presented directly from the keyboard and, in general, undergo translation in firmware or software. See Chapter 10 for key codes as presented from system firmware keyin routines.

<sup>\*\*</sup>D is the code for depression; R is the code for release.

## 3.3 Display

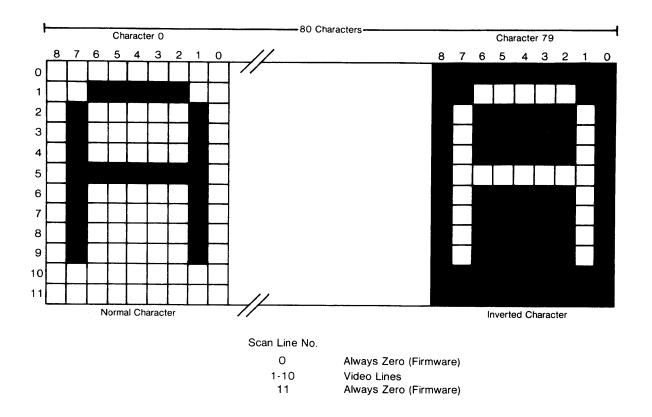

The display uses a magnetic deflection technique with an amber cathode-ray-tube screen. It provides a display of 1920 characters, organized as 24 rows of 80 characters each. The character font is generated through the use of RAM memory (a standard font is loaded into RAM from ROM after power-up). Other character fonts may be loaded as desired under software control. Up to 128 different individual 8- X 12-dot matrix characters may be produced (standard dot matrix is 7 X 9 for upper-case letters, 7 x 11 for lower-case descenders--see figure 3-3). The display/refresh rate is line synchronized at 60/50 frames per second.

The screen refresh memory is organized as 2K bytes in I/O memory space located at address 0140000 octal. It contains the cursor pointer, row pointer, and video information required for screen refresh.

The lower 64 bytes of the screen memory are dedicated for the cursor and row pointers (the cursor pointer is stored in locations 0000 and 0001). Any of the 1920 character locations can be loaded into these locations to display the cursor at any of the character locations.

The address of the first character of each of the 24 rows is stored in locations 0002-0061, with the first character address pointer for the first row at 0002 and 0003, and the first character address pointer for the last row at 0060 and 0061. The display can be manipulated by storing different character addresses in the row pointers. The cursor and row pointers must always be loaded as an even byte followed by an odd byte. All addresses are relative to a base address of KDS (0140000).

### 3.3.1 Display Character Format

Every display character is stored in the screen memory as a byte using its ASCII value. The lower seven bits represent the ASCII value of the display character; the eighth bit is a video attribute. The seven ASCII bits are used to obtain the start address of the character in the display font RAM. The video attribute bit is used for inverse video on a character-by-character basis.

### 3.3.2 Video Attributes

The character-by-character attributes are inverse video, underline, two-level video, and blink. Inverse video is the most significant bit of the screen memory data location.

When this bit is set (1), the character is displayed in inverse video. The character is displayed in regular video when the bit is reset (0).

Underline, two-level video, and blonk are discussed in Section 3.5.3.

Figure 3-3: Character Row

#### 3.3.3 Character Font Load

Displayed characters are generated from a loadable RAM memory, providing for foreign-language character sets and other user-selected character set variations. The RAM is down-line loaded through optional RCM software by the main program. The character generation RAM is a 2048 by 8 memory organized as 128 characters of twelve bytes each.

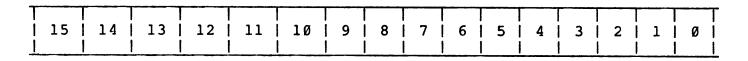

The display font is addressed by using the ASCII value of the character. The ASCII character value is shifted left four bits, and the result is added to the base address of Ø140000 to obtain the start address of the character font. The RAM address for the display font may be separated into fields as follows:

| Base Address |    |    |    | AS | ASCII (7 bit) |   |   |   |   |   |   | Vi | Video Lin |   |   |   |

|--------------|----|----|----|----|---------------|---|---|---|---|---|---|----|-----------|---|---|---|

| Α            | Y  | Α  | A  | A  | A             | Α | Λ | A | A | Α | Α |    | A         | A | A | A |

| 15           | 14 | 13 | 12 | 11 | 1 Ø           | 9 | 8 | 7 | 6 | 5 | 4 |    | 3         | 2 | 1 | Ø |

The top line of the display character is defined by the eight bits of data at the start address. The next nine lines of the character define the next nine memory bytes. The last line of the character is contained in the eleventh memory address. The first and twelfth data locations are filled with zeros so that a border can be formed for the inverse video. Twelve lines, total, can be loaded.

## 3.4 Serial I/O Port

The KDS is equipped with one standard RS-232-C serial interface for connection to a DATAPOINT printer or workstation. The baud rate is software controlled from 50 to 19200 baud. All control signal detection and character formatting is handled by an on-board USART (Universal Synchronous Asynchronous Receiver/Transmitter). When running a terminal off the KDS I/O port, the transmit and receive baud rates must be the same.

#### 3.5 KDS Programming Considerations

## 3.5.1 Keyboard and Screen

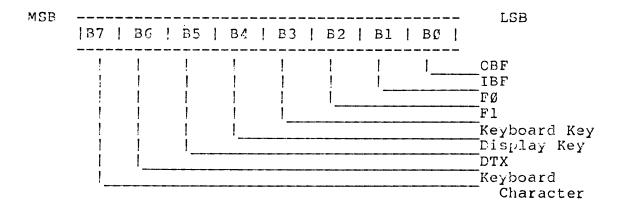

Status and commands for the keyboard and display are accessed by reading from base page I/O address Ø31 for status or writing to it for commands; the status word format follows. Once the appropriate command has been issued and executed by the KDS, any requested status is placed in the Data Bus Buffer (DBB) at base page I/O address Ø30.

The following descriptions explain the bits.

- Bit Ø -- Output Buffer Full (OBF). This is set by hardware whenever the KDS writes a byte to the master in the DBB; it is cleared when the master reads a byte.

- Bit 1 -- Input Buffer Full (IBF). This is set by hardware when the master writes a byte to the KDS in the DBB; it is cleared when the KDS reads it.

- Bit 2 -- The FØ busy flag is set by the KDS firmware to indicate that it is busy servicing a command; it is cleared when the KDS is ready to service a new command.

- Bit 3 -- The Fl flag is set by the hardware to the state of address line Ø and is used by firmware to distinguish between commands and data.

- Bit 4 -- If this bit is set, it indicates that the keyboard key is depressed.

- Bit 5 -- If this bit is set, it indicates that the display key is depressed.

- Bit 6 -- Data Transmit Ready (DTX). If this bit is set, the KDS is ready to transmit a character to the keyboard.

- Bit 7 -- If this bit is set, the KDS has a keyboard character available for the master upon request.

#### 3.5.1.1 Commands

There are three commands associated with the keyboard and display control: read request commands, screen commands, and restart clear commands.

## READ REQUEST COMMANDS

MSB ----- LSB | B7 | B6 | B5 | B4 | Ø | Ø | Ø | Ø |

The bits are defined as follows:

Bit Ø-Bit 3 -- ØØØØ informs the KDS that it is a read request command.

Bit 4-Bit 7 -- 0000 commands the KDS to reset.

0001 commands the KDS to present the key-down status in the DBB.

$\emptyset \emptyset 1 \emptyset$  commands the KDS to present the screen status byte in the DBB.

$\emptyset 1 \emptyset \emptyset$  commands the KDS to present the keyboard character into the DBB.

1000 commands the KDS to present the keyboard type in the DBB.

The format for the screen status byte is shown on the following page:

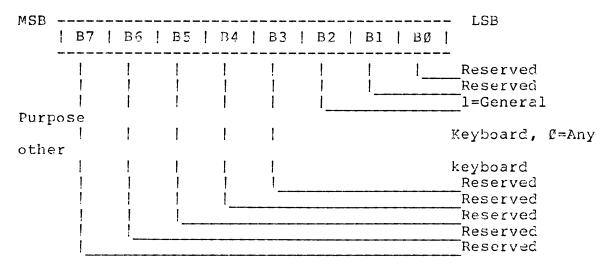

The keyboard type byte is shown below:

The key-down status byte is shown below. Each status bit is a one when the corresponding key is depressed and remains a one until the key is released.

| MSB |            |    |        |    |    |       |       |    | LSB                |

|-----|------------|----|--------|----|----|-------|-------|----|--------------------|

|     | B <b>7</b> | B6 | B5     | B4 | В3 | B2    | B1    | BØ |                    |

|     |            | !  | !      | !  | !  | <br>! | <br>! |    | _Fl Key            |

|     | 1          | !  |        | j  | ]  |       |       |    | F2 Key             |

|     | !          | :  | i<br>I | i  | 1  | i     |       |    | _F3 Key<br>_F4 Key |

|     | İ          | ĺ  | İ      | İ  | 1  | ····· |       |    | F5 Key             |

|     | !          | 1  | 1      |    |    |       |       |    | CTRL Key           |

|     | !          | !  |        |    |    |       |       |    | _ATT Key           |

|     | 1          |    |        |    |    |       |       |    | _INT Key           |

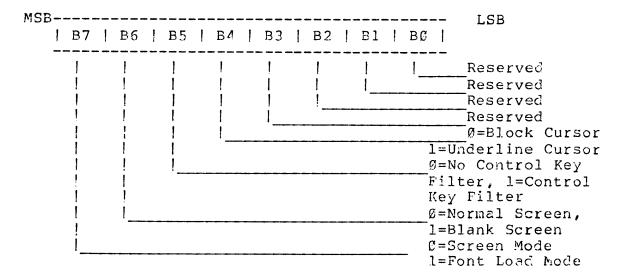

#### SCREEN COMMANDS

The reception of this control word informs the KDS to perform certain screen manipulations.

- Bits  $\emptyset$ -3 --  $\emptyset\emptyset$ 1 $\emptyset$  informs the KDS that it is a screen control word.

- Bit 4 -- When this bit is set to 1, the KDS sets the underline cursor mode. When it is a 0, the KDS sets the block cursor mode (on powering up, the cursor is set to the block mode).

- Bit 5 -- When this bit is set to 1, the KDS does not send control key codes to the master. When this bit is reset to 0, all key codes are sent to the master, except for the special key sequences (see Section 3.2.2).

- Bit 6 -- When this bit is set to 1, the KDS blanks the screen. When it is set to  $\emptyset$ , the screen operates in normal mode.

- Bit 7 -- When this bit is set to 1, the KDS overlays the 2K character font RAM on the screen buffer. When this is cleared, the screen enters normal mode (on powering up, normal mode is set).

## Brightness Control

Bits g-3 -- gglin = 0 informs the KDS that it is a brightness control byte.

Bits 4-7 -- These bits control the brightness of the screen.

The brightness can be set to any one of sixteen levels, Ø being the brightest and 15 being the dimmest.

## RESTART CLEAR COMMANDS

Bits 0-3 -- 0100 informs the KDS that it is a restart acknowledge byte. Upon receipt of this command, the KDS clears the restart pulse.

Bits 4-7 -- Reserved.

## 3.5.2 Speaker Commands

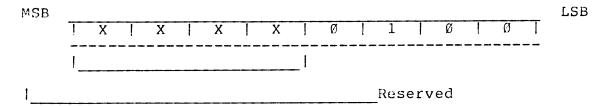

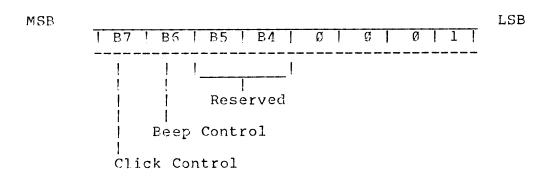

Speaker control is initiated by writing to base page I/O address #31. The byte format is as follows:

Upon receipt of this command, the KDS initiates the beep or click operation. The beep is a 1200Hz tone generated for a duration of 250 milliseconds. The click is an 800 microsecond pulse with a minimum of 800 microseconds guaranteed between clicks.

Bits 0-3 -- 0001 informs the KDS that it is a speaker control word.

Bits 4-5 -- Reserved.

Bit 6 -- When this bit is set, it commands the KDS to

initiate a beep operation.

Bit 7 -- When set, this bit commands the KDS to initiate a click operation.

#### 3.5.3 Video Attributes

Underline, two-level video, and blink are programmed by writing to the attribute RAM. Screen character locations run from 0140100 to 0143777, and attribute RAM extends from 0144000 to 0147777. Attribute data for a particular screen byte resides at a 04000 offset from the screen RAM location; therefore, screen data at location 0140100 has its attributes at extended I/O address 0144100 and so on. The bit positions for attributes are shown below:

| MSB | 1 B7        | B6          | B5 | B4 | B3                                    | B2 | B1 | ВØ | LSB<br>T                                     |

|-----|-------------|-------------|----|----|---------------------------------------|----|----|----|----------------------------------------------|

|     | !<br>!<br>! | !<br>!<br>! | !  | !  |                                       |    | !  | 1  | -<br>_Underline<br>_Two-level<br>_Blink      |

|     |             | !<br>!<br>! |    |    | · · · · · · · · · · · · · · · · · · · |    |    |    | Reserved Reserved Reserved Reserved Reserved |

As mentioned in Sections 3.3.1 and 3.3.2, the inverse video attribute bit is controlled by manipulation of the most significant bit of the screen RAM byte for a particular character.

#### 3.5.4 Serial I/O Port

The KDS serial I/O port is addressed through base page I/O address 0.34 to 0.37.

The RS-232C signals supported are Transmit Data, Receive Data, Secondary Receive Line Signal Detect (Printer Busy), Data Set Ready, and Data Carrier Detect. Control of all signals is handled by a USART.

Connections to the USART and the function of each signal are as follows. Transmit and receive data are self-explanatory. Emptying of the transmit holding register or filling of the receive holding register by a received character causes an interrupt to the CPU on Interrupt Request Line Two. The CPU then polls the status register of the USART and determines whether it was a receive or transmit interrupt. The status register bit positions are shown in Figure 3-4.

Secondary Receive Line Signal Detect is connected to Clear To Send on the USART. Clear To Send must be low, and TXEN in the command register (Figure 3-5) must be set in order to transmit. If the printer is busy, it pulls this line high, and transmission is halted until it is taken low again. This signal is not used for a terminal and no connection is necessary for transmission.

The RS-232-C signal Data Set Ready is connected to the Data Set Ready on the USART and appears as bit 7 in the status register (Figure 3-4). It is connected to Data Terminal Ready on the printer (power on).

Data Carrier Detect must be low, and RXEN in the command register (Figure 3-5) must be set for the receiver to operate. This signal is used only for terminals.

Loading the mode and command registers initializes the USART. The first read or write to address 036 addresses mode register 1; the second read or write to that address addresses mode register 2 (Mode register 1 bit definitions are shown in Figure 3-6). It contains parity type and control and character length; unused bits must be programmed as shown. Mode register 2 is broken down in Figure 3-7. It contains the baud rate selection. Once again, unused bits must be programmed as specified.

Manipulation of the command register is accomplished by access to address Ø37. This register is shown in Figure 3-5.

| SR7                                                   | SR6                                                   | SR5                            | SR4                            | SR3                           | SR2                                                                              | SR1                                                                       | SR0                    |

|-------------------------------------------------------|-------------------------------------------------------|--------------------------------|--------------------------------|-------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------|

| Data Set<br>Ready                                     | Data Carrier<br>Detect                                | Framing<br>ERROR               | Overrun                        | Parity<br>ERROR               | TxEMT/<br>DSCHG                                                                  | RxRDY                                                                     | TxRDY                  |

| 0=DSR<br>INPUT<br>IS HIGH<br>1=DSR<br>INPUT<br>IS LOW | 0=DCD<br>INPUT<br>IS HIGH<br>1=DCD<br>INPUT<br>IS LOW | 0=NORMAL<br>1=FRAMING<br>ERROR | 0=NORMAL<br>1=OVERRUN<br>ERROR | 0=NORMAL<br>1=PARITY<br>ERROR | 0=NORMAL<br>1=CHANGE<br>IN DSR OR<br>DCD, OR<br>TRANSMIT<br>SHIFT<br>REGISTER 16 | 0=RECEIVE<br>HOLDING REG<br>EMPTY<br>1=RECEIVE<br>HOLDING REG<br>HAS DATA | REG BUSY<br>1=TRANSMIT |

Figure 3-4: Status Register

| CR7 CR6                                                                                           | CR5                                       | CR4                                                                   | CR3                  | CR2                   | CR1                                                     | CRO                   |

|---------------------------------------------------------------------------------------------------|-------------------------------------------|-----------------------------------------------------------------------|----------------------|-----------------------|---------------------------------------------------------|-----------------------|

| Operating Mode                                                                                    | Request<br>to Send                        | Reset Error                                                           | Force<br>Break       | Receive<br>Control    | Data Terminal<br>Ready                                  | Transmit,<br>Control  |

| 00=NORMAL OPER<br>01=ASYNCH: AUTO<br>ECHO MODE<br>10=LOCAL LOOP<br>BACK<br>11=REMOTE LOOP<br>BACK | 0=FORCE RTS<br>HIGH<br>1=FORCE RTS<br>LOW | 0=NORMAL<br>1=RESET<br>ERROR FLAG<br>IN STATUS<br>REG<br>(FE, OE, PE) | 0=NORMAL<br>1=ENABLE | 0=DISABLE<br>1=ENABLE | 0=FORCE DTR<br>OUTPUT HIGH<br>1=FORCE DTR<br>OUTPUT LOW | 0=DISABLE<br>1=ENABLE |

Figure 3-5: Command Register

| MR17 MR16                                                                                  | MR15            | MR14                    | MR13 MR12                                        | MR11 MR10                                                                                                 |

|--------------------------------------------------------------------------------------------|-----------------|-------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| Stop Bit Length                                                                            | Parity Type     | Parity Control          | Character<br>Length                              | Mode and Baud<br>Rate Factor                                                                              |

| Async: Stop Bit Length<br>00=Invalid<br>01=1 stop bit<br>10=1½ stop bits<br>11=2 stop bits | 0=Odd<br>1=Even | 0=Disabled<br>1=Enabled | 00=5 bits<br>01=6 bits<br>10=7 bits<br>11=8 bits | 00=Synchronous 1X rate<br>01=Asynchronous 1X rate<br>10=Asynchronous 16X rate<br>11=Asynchronous 64X rate |

Figure 3-6: Mode Register 1

|      |     |     |       | MR27   | - MR24 |     |     |       |         |       | MR23 - MR20                |

|------|-----|-----|-------|--------|--------|-----|-----|-------|---------|-------|----------------------------|

|      | TxC | RxC | Pin 9 | Pin 25 |        | TxC | RxC | Pin 9 | Pin 25  | Mode  | Baud Rate Selection        |

| 0000 | E   | E   | TxC   | RxC    | 1000   | E   | E   | XSYNC | RxC/TxC | sync  |                            |

| 0001 | Ē   | Ī   | TxC   | 1X     | 1001   | E   | ı   | TxC   | BKDET   | async | See baud rates in table 1. |

| 0010 | Ī   | É   | 1X    | RxC    | 1010   | 1   | Ε   | XSYNC | RxC     | sync  | 1                          |

| 0011 | i   | ı   | 1X    | 1X     | 1011   | ı   | 1   | 1X    | BKDET   | async |                            |

| 0100 | E   | Ε   | TxC   | RxC    | 1100   | Ε   | Ε   | XSYNC | RxC/TxC | sync  |                            |

| 0101 | Ē   | 1   | TxC   | 16X    | 1101   | Ε   | - 1 | TxC   | BKDET   | async |                            |

| 0110 | ī   | Ε   | 16X   | RxC    | 1110   | - 1 | Ε   | XSYNC | RxC     | sync  |                            |

| 0111 | - 1 | Ī   | 16X   | 16X    | 1111   | 1   | - 1 | 16X   | BKDET   | async |                            |

Figure 3-7: Mode Register Mode 2

## PART 4 MEMORY

#### 4.1 General

The main memory of the 8600 processor is implemented in printed circuit boards housed in the processor's internal card cage. Two different types of memory are available, each in two different sizes. Parity memory may be configured with either 128K or 256K bytes; error correction code (ECC) memory is available in either 256K or 512K bytes (parity and ECC memory may not be mixed). The memory module is linked to the Common Bus and arbitrates memory-cycle and memory-refresh requests.

The memory may be requested dynamically to perform in either the word- or byte-access mode. The word-access mode is restricted to addressing even boundaries only; the memory-access mode may be accomplished through bus master cycles or using Direct Memory Access.

Section 4.2 describes the parity memory module; the ECC memory module is described in section 4.3.

## 4.2 Parity Memory

Memory cycles consist of word writes and reads, byte writes and reads, and refresh. These cycles are discussed in the following sections. Timings are listed below:

| Read Cycle    | 75Ø ns | (typical) |

|---------------|--------|-----------|

| Write Cycle   | 75¢ ns | (typical) |

| Refresh Cycle | 250 ns | (typical) |

| Access Time   | 300 ns | (maximum) |

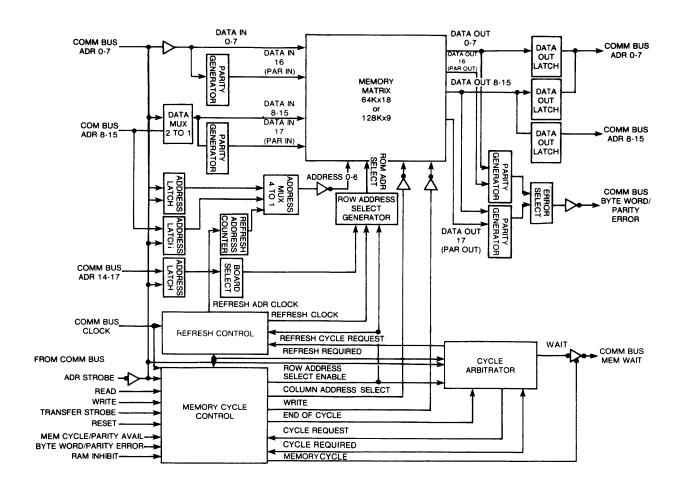

The 128K parity memory module is schematically illustrated in Figure 4-1.

## 4.2.1 Word Read (Parity Memory)

The word read cycle begins when the memory detects that it has been selected for access by decoding the proper address and memory cycle request bits from the Common Bus during the time that Address Strobe is present. This information is latched on the trailing edge of Address Strobe, thus generating the Row Address Strobe (RAS). The Address Mux Signal (MUX) and Column Address Strobe (CAS) are generated from delayed versions of RAS. The RAS signal input to the memory array is further decoded to select the proper bank of the array. All of these signals are terminated at the same

time when the CAS signal has met the minimum pulse width specification. This allows the cycle to run free of any bus timing restraints and only requires Address Strobe to initiate a cycle. Data is enabled onto the bus when Transfer Strobe has been detected during a read cycle and the board has been selected. If during the course of the cycle the RAM INHIBIT signal is detected, the output drivers are not enabled, although the cycle runs to completion.

### 4.2.2 Byte Read (Parity Memory)

The byte read cycle is identical to the word read cycle except for the case of an odd byte access. In this case, the odd byte is physically located in the upper byte of the memory word and, upon access, is driven to the lower byte where the bus master is expecting the data. These bits are also driven on the most significant part of the bus, although no device receives them. During even byte reads, the corresponding odd byte is driven to the MSB of the bus, although it is assumed no device receives it.

## 4.2.3 Word Write (Parity Memory)

The word write cycle is similar to the word read cycle except that when the Write Strobe and Transfer Strobe are present on the bus and the board has been selected, a write pulse is generated and sent to the memory array. Even parity is generated over each byte of the data to be written and is subsequently written into the array with the data.

#### 4.2.4 Byte Write (Parity Memory)

The byte write cycle is similar to the word write cycle except that the write pulse is sent only to the selected byte instead of the entire word. A read-modify-write cycle is not required, since parity is generated over the byte.

#### 4.2.5 Refresh Cycles (Parity Memory)

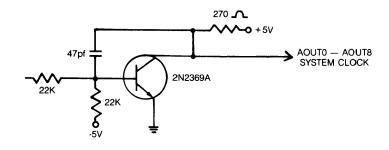

The refresh controller is synchronized to the System Bus Clock that runs at a nominal frequency of 4MHz. A counter is implemented such that a refresh request is generated every 15 microseconds.

A refresh is performed by selecting one of 128 rows in the memory and strobing the chip with the Row Address Strobe. A counter on the board is used to select the row to be refreshed. If no cycle is in progress and a refresh request is detected (by the 15-microsecond timeout), a refresh cycle is initiated. At this time the counter outputs are gated to

Figure 4-1 Parity Memory Module

the memory array, and RAS is generated from the bus clock. RAS is one cycle wide; its completion increments the row counter and resets the refresh request condition.

## 4.2.6 Cycle Arbitration (Parity Memory)

Bus access cycles and refresh cycles cannot have simultaneous memory access. Bus master requests to memory are deferred during a refresh cycle; refresh requests are deferred during a bus access cycle. Cycles proceed upon demand during those times that arbitration is not required. The refresh logic provides 128 refresh cycles every two milliseconds to ensure the validity of data within the memory.

## 4.2.7 Error Detection (Parity Memory)

The memory carries parity over each eight-bit byte. When a write to memory occurs, a ninth bit (for each byte) is generated using a parity generator and written to the memory. The parity is checked when the data is read from memory. If the parity checking logic does not compute, the correct parity, an error condition signal is placed on the Common Bus.

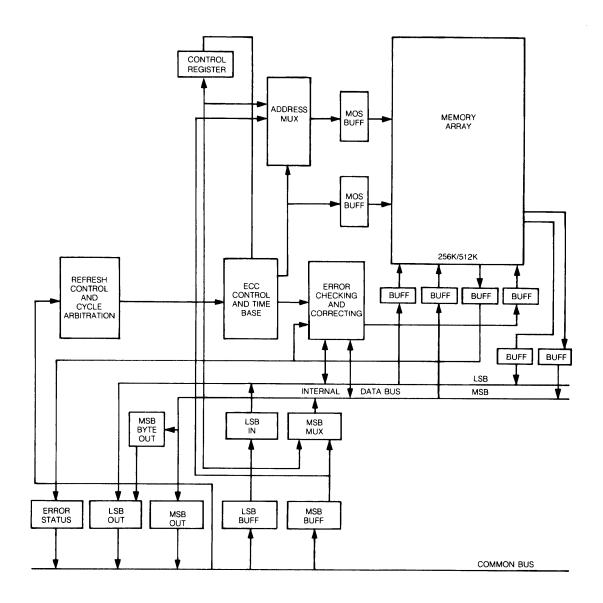

#### 4.3 ECC Memory

Each ECC memory module contains 256K or 512K bytes and uses six check bits for each word (16 bits) of memory. Word accesses are performed only on even boundaries; the ECC control logic corrects all single-bit errors and flags double-bit errors. Figure 4-2 is a schematic illustration of the ECC memory module. Timings are listed below:

| Read Cycle             | 750ns (t | ypical)  |

|------------------------|----------|----------|

| Write Cycle            | 750ns (t | ypical)  |

| Refresh Cycle          | 250ns (t | ypical)  |

| Access Time            | 300ns (t | ypical)  |

| Read and Correct Cycle | 1000ns ( | typical) |

Figure 4-2 ECC Memory Block Diagram

## 4.3.1 Word Read (ECC Memory)

The word read cycle begins when the memory detects that it has been selected for access by decoding the proper address and memory cycle request bits from the Common Bus during the time that Address Strobe is present. This information is latched on the trailing edge of Address Strobe, thus generating the Row Address Strobe (RAS). The Address Mux Signal (MUX) and Column Address Strobe (CAS) are generated from delayed versions of RAS. The RAS signal input to the memory array is further decoded to select the proper bank of the array. Data is enabled onto the bus when Transfer Strobe has been detected during a read cycle and the board has been selected. If, during the course of the cycle, the RAM INHIBIT signal is detected, the output drivers are not enabled although the cycle runs to completion.

## 4.3.2 Byte Read (ECC Memory)

The byte read cycle is identical to the word read cycle except for the case of an odd byte access. In this case, the odd byte is physically located in the upper byte of the memory word, and, upon access, is driven to the lower byte where the bus master is expecting the data. These bits are also driven on the most significant part of the bus, although no device receives them. During even byte reads, the corresponding odd byte is driven to the MSB of the bus, although it is assumed no device receives it.

## 4.3.3 Word Write (ECC Memory)

All ECC memory writes are performed as read-modify-write cycles. At the beginning of the write cycle, the 22-bit word is read in by the ECC control logic, which then compares the 16 bits of data to the six check bits to confirm that the data is correct.

After performing the check, the new 16-bit word is used to generate new check bits; all 22 bits are then written to the memory array.

## 4.3.4 Byte Write (ECC Memory)

The byte write cycle is similar to the word write cycle for the ECC memory except that after checking the old contents of the 16-bit word, one byte is replaced with the new data while the unaddressed byte is held in a register. The two bytes are then recombined into a 16-bit word, which is used to generate six new check bits. The two bytes and their check bits are then written to the memory array as a 22-bit word.

## 4.3.5 Refresh Cycles (ECC Memory)

Refresh and refresh arbitration are performed by a custom gate array. An internal counter is driven by the synchronous 4 MHz System Clock, and this determines when a refresh is required. If a Read or Write cycle is in progress at the time the refresh is needed, then the refresh is blocked until the current cycle is completed. The refresh can then proceed, with the strobes provided by the custom gate array.

Similarly, a memory cycle is blocked if a refresh cycle is under way. There are 128 refresh cycles performed every two

milliseconds or 256 refresh cycles performed every four milliseconds (depending on the RAM).

## 4.3.6 Error Detection (ECC Memory)

Error detection and correction are performed by means of generating a six-bit Hamming code accross 16 bits of data during writes. While reading the data, a check is made across the entire 22-bit word (16 bits of data, 6 bits for checking) for errors.

A single LSI chip does all of the bit generation and error detection performed by the ECC memory. It is capable of single-bit error correction and double-bit error detection (when a double-bit error is detected, an error condition signal is placed on the Common Bus).

## 4.3.7 Diagnostic Features (ECC Memory)

The ECC memory board contains several diagnostic features. There are two write registers and two read registers for diagnostic purposes.

These registers are located at I/O address octal 060 and octal 062.

## 4.3.7.1 Status Register

This register, when read, contains the six check bits and two bits reflecting the error status of the last memory read.

| ME   ER   CK5   CK4   CK3   CK2   CK1   CK0 | MSB |    |     |     |     |     | L  | SB |     |                                           |                   |                  |

|---------------------------------------------|-----|----|-----|-----|-----|-----|----|----|-----|-------------------------------------------|-------------------|------------------|

|                                             | ME  | ER | CK5 | CK4 | СКЗ | CK2 | CK | 1  | CKØ |                                           |                   |                  |

| Error                                       |     |    |     |     |     |     |    |    |     | Check<br>Check<br>Check<br>Check<br>Check | bit<br>bit<br>bit | 1<br>2<br>3<br>4 |

ER - This bit is negative true and indicates that an error occurred on the last memory read. If this bit is true and the ME bit is false, then a correctable error has occurred. If both this bit and the ME bit are true, then a non-correctable error has occurred.

ME - This bit is negative true and indicates that a multiple error occurred on the last read.

$CK\emptyset-5$  - These six bits are the check bits from memory on the last read.