B 7700

# INFORMATION PROCESSING SYSTEMS

REFERENCE MANUAL

PRICED ITEM

# B 7700 INFORMATION PROCESSING SYSTEMS

REFERENCE MANUAL

Copyright © 1973-1976, Burroughs Corporation, Detroit, Michigan 48232

AA430046

PRICED ITEM

Burroughs believes that the information described in this manual is accurate and reliable, and much care has been taken in its preparation. However, no responsibility, financial or otherwise, is accepted for any consequences arising out of the use of this material. The information contained herein is subject to change. Revisions may be issued to advise of such changes and/or additions.

#### TABLE OF CONTENTS

| Chapter | Title                                                    | Page                                                          | Chapter | Title                                                             | Page                |

|---------|----------------------------------------------------------|---------------------------------------------------------------|---------|-------------------------------------------------------------------|---------------------|

|         | INTRODUCTION                                             | xi                                                            |         | Data Descriptor                                                   | 2-27                |

| I       | DESCRIPTION OF B 7700 SYSTEM                             | 1-1                                                           |         | String Descriptor                                                 | 2-27                |

|         | The B 7700 System                                        | 1-1                                                           |         | Segment Descriptors                                               | 2-28                |

|         | Distinguishing Features                                  | 1-1                                                           |         | Words for Addressing Within Stacks                                | 2-28                |

|         | System Configuration                                     | 1-2                                                           |         | Program Control Word                                              | 2-28                |

|         | Maximum Configuration                                    | 1-3                                                           |         | Indirect Reference Word Stuffed Indirect Reference Word           | $\frac{2-29}{2-29}$ |

|         | Minimum Configuration                                    | 1-5                                                           |         | Words for Storing Stack History                                   | 2-23                |

| H       | SYSTEM ARCHITECTURE                                      | 2-1                                                           |         | Mark Stack Control Word                                           | 2-32                |

|         | Section 1 - Data Representation                          | 2-1                                                           |         | Return Control Word<br>Top of Stack Control Word                  | 2-32                |

|         | General                                                  | 2-1                                                           |         | Words Used as Special Parameters                                  | $\frac{2-32}{2-32}$ |

|         | Internal Character Codes and                             | 2-1                                                           |         | Step Index Word                                                   | 2-33                |

|         | Collating Sequences Numbers and Numbering Systems        | 2-1                                                           |         | Occurs Index Word                                                 | 2-33                |

|         | Binary Notation                                          | 2-1                                                           |         | Time of Day Function Word                                         | 2-33                |

|         | Hexadecimal and Octal Notation                           | 2-2                                                           |         | Section 4 - Input/Output Subsystem                                | 2-36                |

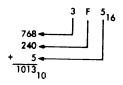

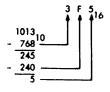

|         | Number Conversion                                        | 2-2                                                           |         | Map Structure                                                     |                     |

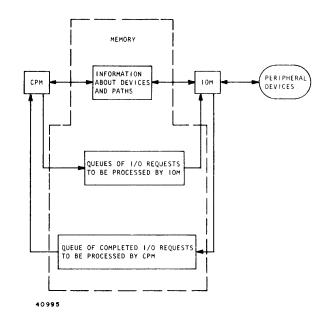

|         | Binary to Decimal Conversion                             | 2-2                                                           |         | Introduction                                                      | 2-36                |

|         | Decimal to Binary Conversion Decimal to Octal Conversion | 2-4                                                           |         | Queue-Driven I/O                                                  | 2-36                |

|         | Octal to Octal Conversion Octal to Decimal Conversion    | $\frac{2-5}{2-6}$                                             |         | Error Handling                                                    | 2-37                |

|         | Decimal to Hexadecimal Conversion                        | $\frac{2}{2}$ -7                                              |         | Deferment of Path Binding I/O Subsystem Map                       | 2-37                |

|         | Hexadecimal to Decimal Conversion                        | 2-7                                                           |         | Commands and Requests                                             | $\frac{2-38}{2-38}$ |

|         | Operand Formats                                          | 2-7                                                           |         | Map Integrity                                                     | 2-39                |

|         | Numeric Operands                                         | 2-7                                                           |         | Home Address Words                                                | 2-39                |

|         | Logical Operands                                         | $\frac{2-11}{2-11}$                                           |         | Unit Table                                                        | 2-39                |

|         | String Operands                                          |                                                               |         | I/O Queue Head and Tail Words                                     | 2-39                |

|         | Section 2 - Polish Notation and Stack                    | 2-13                                                          |         | Status Queue Headers<br>Input/Output Control Block                | $\frac{2-40}{2-40}$ |

|         | General                                                  | 2-13                                                          | III     | • • •                                                             |                     |

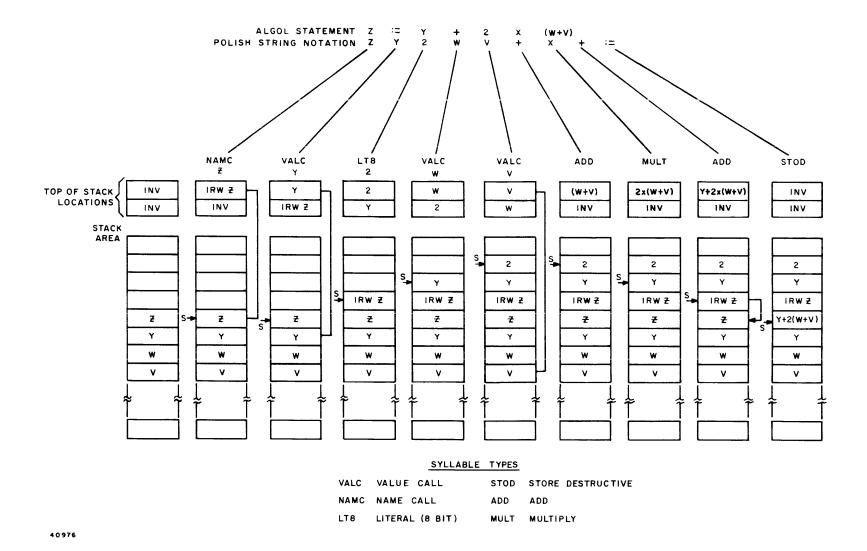

|         | Polish Notation General Rules for Generation of          | $\frac{2-13}{2-13}$                                           | 111     | CENTRAL PROCESSOR MODULE                                          | 3-1                 |

|         | Polish String                                            | Z-15                                                          |         | Section 1 - Functional Description of<br>Central Processor Module | 3-1                 |

|         | Evaluating Polish String                                 | 2-15                                                          |         |                                                                   |                     |

|         | Compilation Using Polish Notation                        | 2-15                                                          |         | Operational Concepts of the Central<br>Processor Module           | 3-3                 |

|         | Program Code String                                      | 2-15                                                          |         | Use of Divisional Overlap and Local                               | 3-3                 |

|         | Stack Concepts<br>General                                | $\begin{array}{c} 2\text{-}16 \\ 2\text{-}16 \end{array}$     |         | Buffering                                                         | 0-0                 |

|         | Base and Limit of Stack                                  | 2-16                                                          |         | Memory Overlap                                                    | 3-5                 |

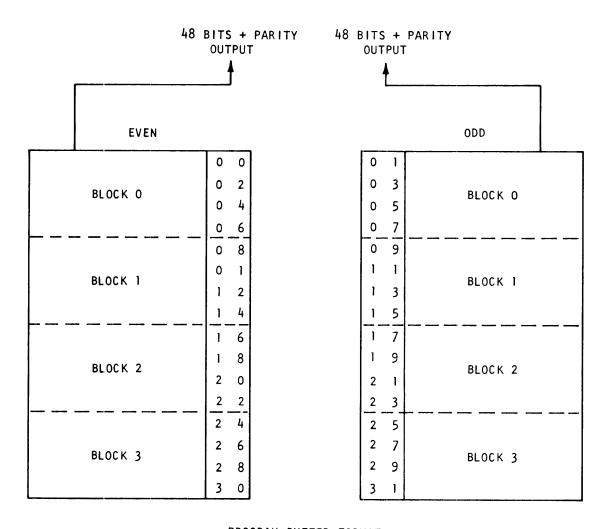

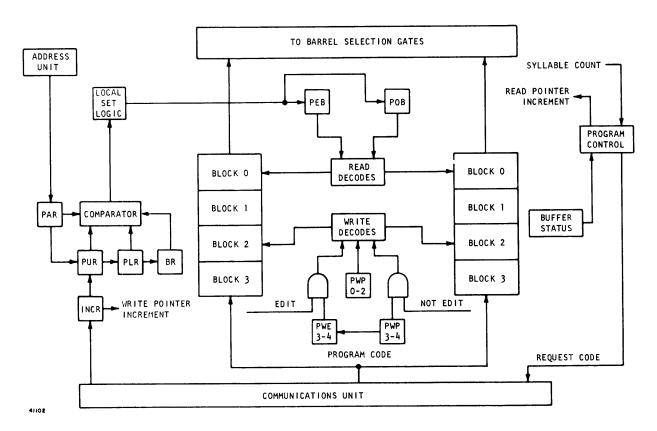

|         | Bi-Directional Data Flow in the Stack                    | 2-17                                                          |         | Program Buffer                                                    | 3-5                 |

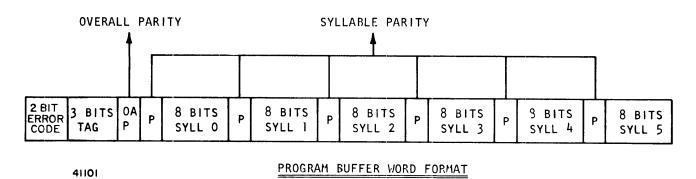

|         | Double Precision Stack Operation                         | 2-17                                                          |         | Buffer Word Format                                                | 3-5                 |

|         | Hardware Implementation                                  | 2-17                                                          |         | Reading from the Program Buffer Writing into the Program Buffer   | 3-5<br>3-5          |

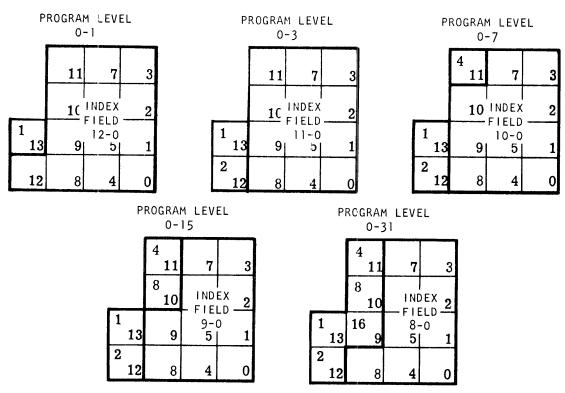

|         | Dynamic Program History Addressing History               | $\frac{2-17}{2-17}$                                           |         | Branching                                                         | 3-8                 |

|         | Direct Addressing                                        | 2-17                                                          |         | Edit Mode Operation                                               | 3-9                 |

|         | Relative Addressing                                      | 2-19                                                          |         | Vector Mode Operation                                             | 3-9                 |

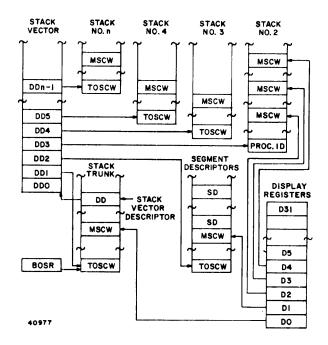

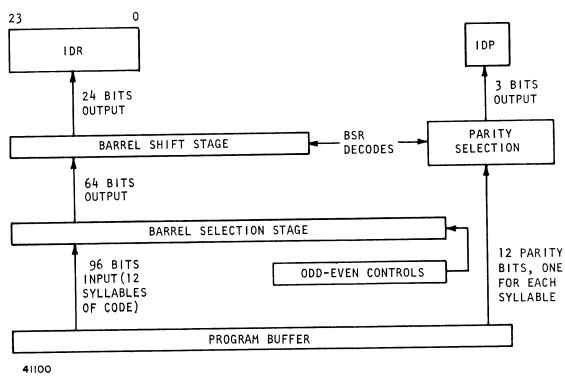

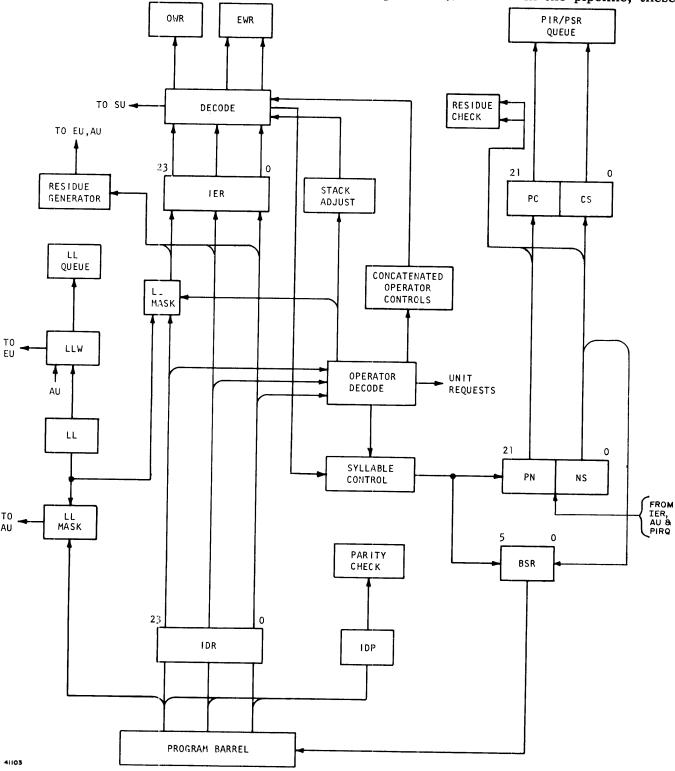

|         | Stack History                                            | 2-21                                                          |         | Program Barrel                                                    | 3-9                 |

|         | Simple Stack Operation                                   | 2-21                                                          |         | Selection Gating Stage<br>Barrel Shift Stage                      | $\frac{3-9}{3-10}$  |

|         | Interrupt Handling Multiple Stacks and Re-entrant Code   | $\begin{array}{c} 2 \text{-} 22 \\ 2 \text{-} 24 \end{array}$ |         | Syllable Parity Checking                                          | 3-10                |

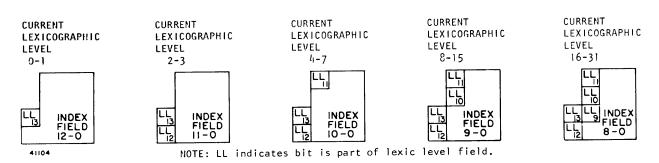

|         | Level Definition                                         | 2-24                                                          |         | Processing of LT48 Operator                                       | 3-10                |

|         | Re-entrance                                              | 2-24                                                          |         | Program Control Unit                                              | 3-11                |

|         | Job Splitting                                            | 2-24                                                          |         | Instruction Decode Register                                       | 3-12                |

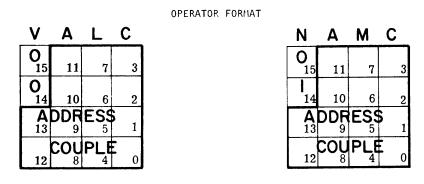

|         | Stack Descriptor                                         | 2-24                                                          |         | Instruction Execute Register Preprocessing of Value Call and      | 3-13                |

|         | Stack Vector Descriptor Presence Bit Interrupt           | $\begin{array}{c} 2\text{-}25 \\ 2\text{-}25 \end{array}$     |         | Name Call Operators                                               | 3-13                |

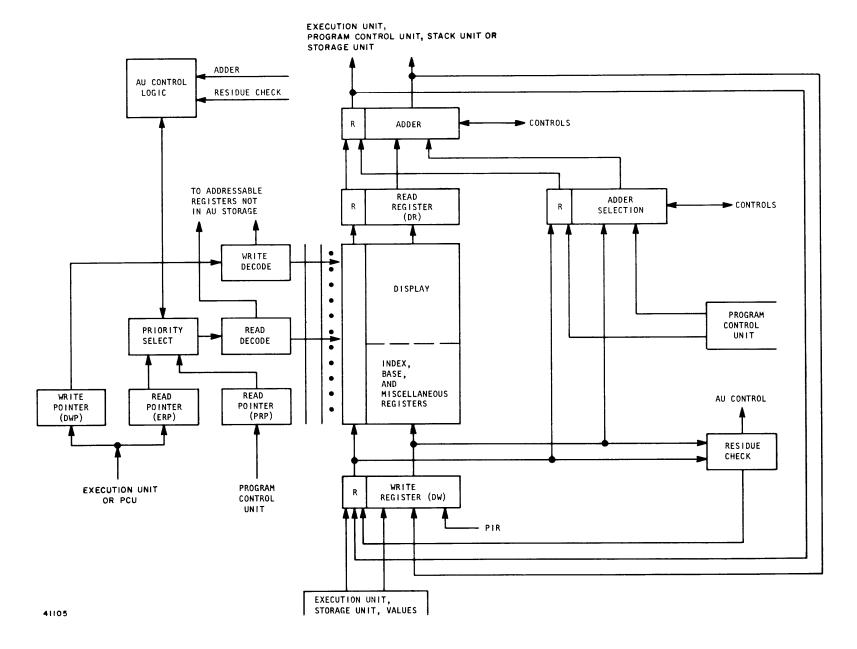

|         | •                                                        |                                                               |         | Address Unit                                                      | 3-15                |

|         | Section 3 - Processor Word Formats                       | 2-25                                                          |         | Execution Unit                                                    | 3-17                |

|         | General                                                  | 2-25                                                          |         | General                                                           | 3-17                |

|         | Words for Addressing Outside of the                      | 2-27                                                          |         | Input Queues<br>Operator Queue                                    | 3-18                |

|         | Stack<br>Presence Bit                                    | 2-27                                                          |         | EU Data Queue                                                     | $\frac{3-18}{3-18}$ |

|         | Index Bit                                                | 2-27                                                          |         | EU Look-Ahead Data Queue                                          | 3-18                |

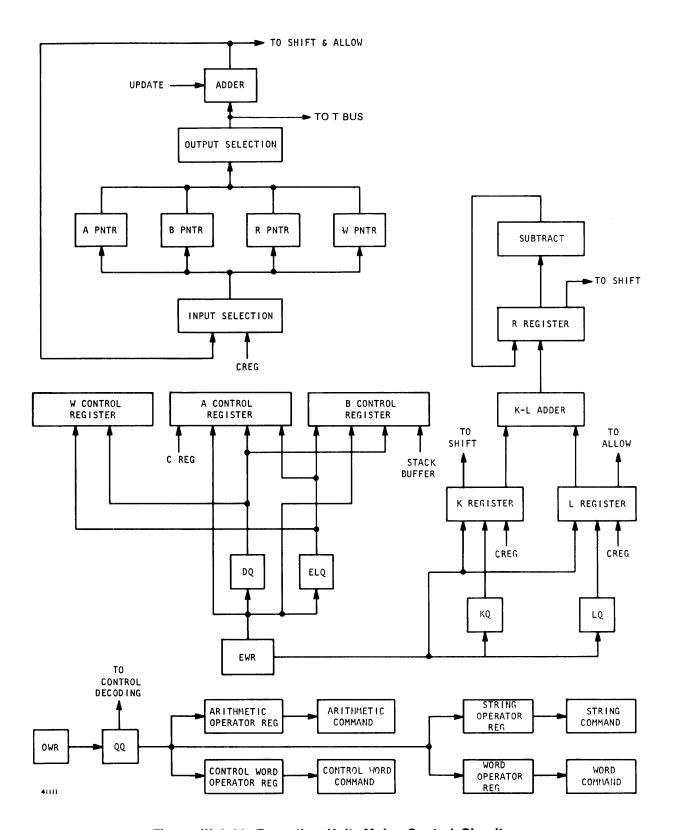

|         | Invalid Index                                            | 2-27                                                          |         | K and L Queues                                                    | 3-19                |

|         | Valid Index                                              | 2-27                                                          |         | PIR and PSR Queue                                                 | 3-19                |

|         | Read-Only Bit                                            | 2-27                                                          |         | Lexic Level Queue                                                 | 3-19                |

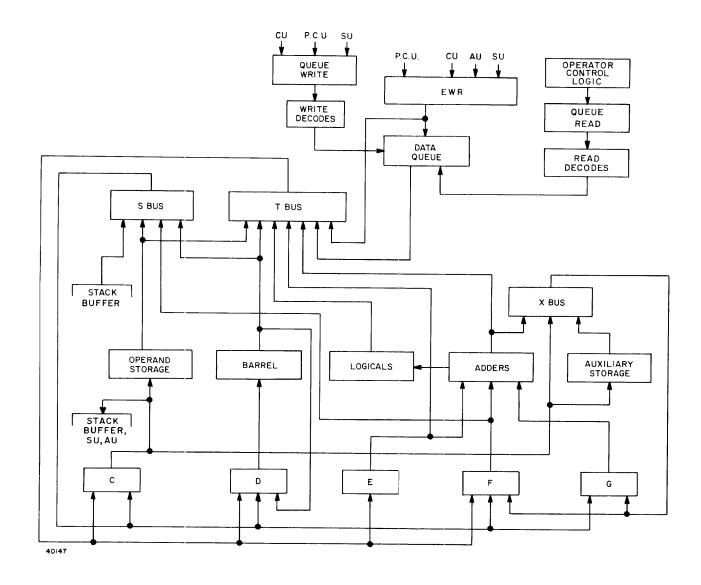

|         | Copy Bit                                                 | 2-27                                                          |         | Major EU Data Circuits                                            | 3-20                |

| Chapter | Title                                 | Page                | Chapter | Title                                                        | Page |

|---------|---------------------------------------|---------------------|---------|--------------------------------------------------------------|------|

|         | Adder                                 | 3-20                |         | Section 3 - Operators                                        | 3-65 |

|         | Shift Mechanism                       | 3-20                |         | Introduction                                                 | 3-65 |

|         | Local Memory                          | 3-20                |         | Grouping of Operators                                        | 3-66 |

|         | Data Registers                        | 3-22                |         | Primary Mode Operators                                       | 3-69 |

|         | Data Transfer Buses                   | 3-22                |         | Arithmetic Operators                                         | 3-69 |

|         | Major EU Control Circuits             | 3-23                |         | Add (ADD) (P)80                                              | 3-69 |

|         | Basic EU Operation                    | 3-25                |         | Subtract (SUBT) (P)81                                        | 3-69 |

|         | EU Error Detection Methods            | 3-26                |         | Multiply (MULT) (P)82                                        | 3-69 |

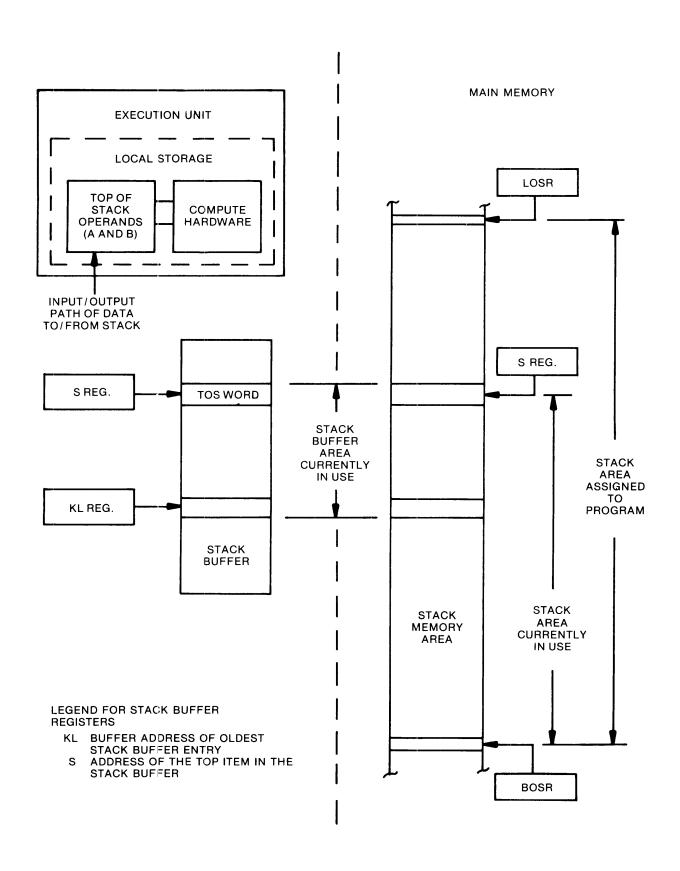

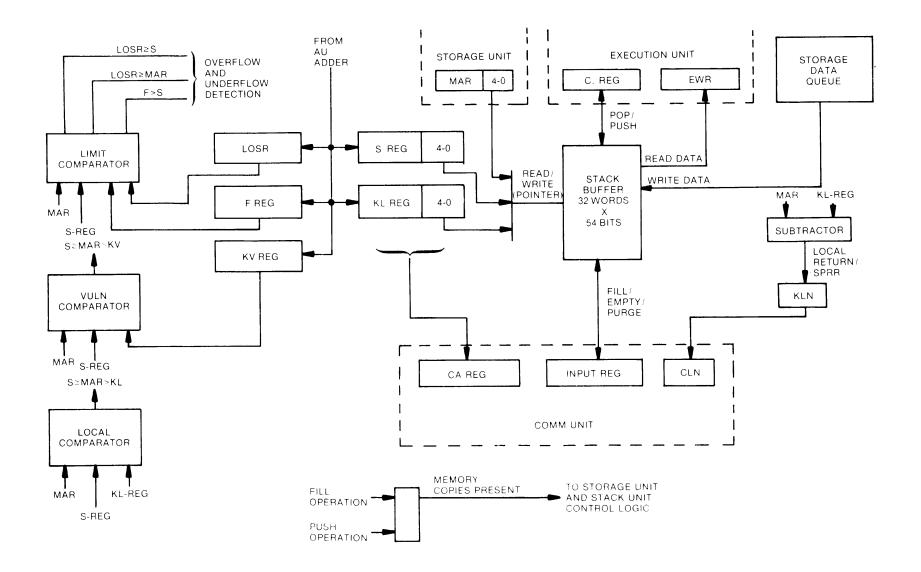

|         | Stack Buffer                          | 3-26                |         | Extended Multiply (MULX) (P)8F                               | 3-69 |

|         | Stack Buffer Function                 | 3-26                |         | Divide (DIVD) (P)83                                          | 3-69 |

|         | Stack Buffer Operation                | 3-26                |         |                                                              | 3-69 |

|         | Fetching the Top Item from the        | 3-28                |         | Integer Divide (IDIV) (P)84<br>Remainder Divide (RDIV) (P)85 |      |

|         | Stack Buffer                          | 0 20                |         |                                                              | 3-69 |

|         | Adding a New Item to the Contents     | 3-28                |         | Integerize, Truncated (NTIA) (P)86                           | 3-69 |

|         | of the Stack Buffer                   | 0-20                |         | Integerize, Rounded (NTGR) (P)87                             | 3-69 |

|         | Fetching and Storing of Local         | 3-29                |         | Integerize, Rounded, Double Precision                        | 3-70 |

|         | Information                           | 3-29                |         | (NTGD) (V)87                                                 |      |

|         |                                       | 2.90                |         | Bit Operators                                                | 3-70 |

|         | Stack Buffer Purge Operation          | 3-29                |         | Bit Set (BSET) (P)96                                         | 3-70 |

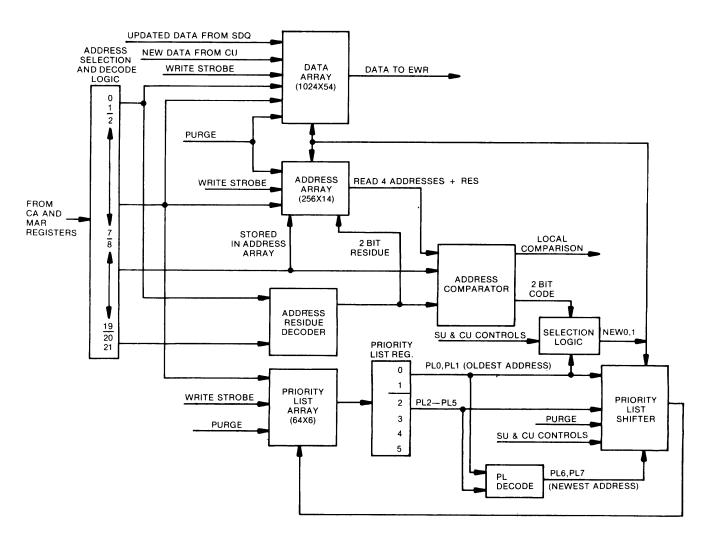

|         | Associative Memory                    | 3-29                |         | Dynamic Bit Set (DBST) (P)97                                 | 3-70 |

|         | ASM Local Operation                   | 3-31                |         | Bit Reset (BRST) (P)9E                                       | 3-70 |

|         | ASM Fill Operation                    | 3-32                |         | Dynamic Bit Reset (DBRS) (P)9F                               | 3-70 |

|         | ASM Purge Operation                   | 3-32                |         | Change Sign Bit (CHSN) (P)8E                                 | 3-70 |

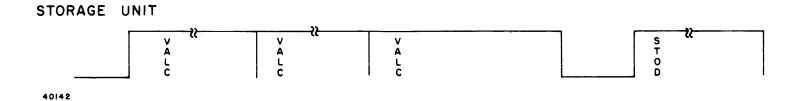

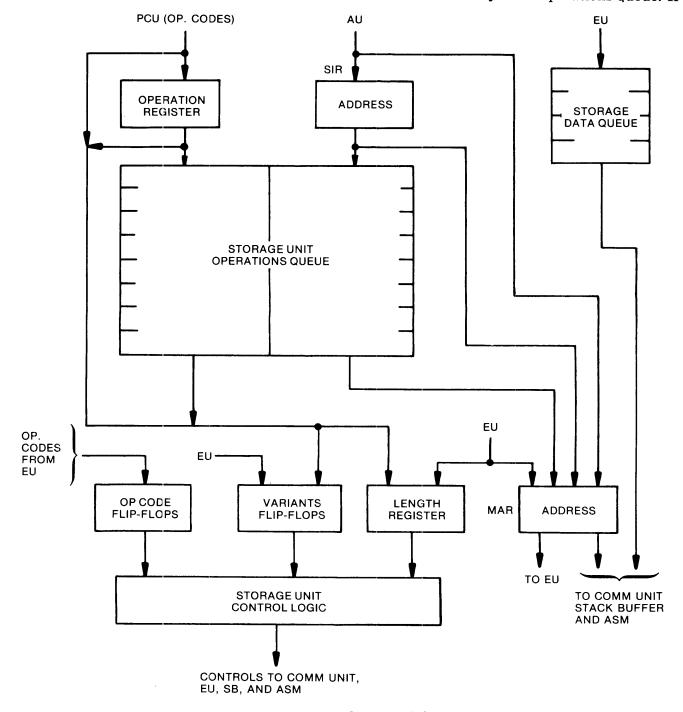

|         | Storage Unit                          | 3-33                |         | Count Binary One's (CBON) (V)BB                              | 3-70 |

|         | Input to Storage Unit Operations      | 3-34                |         | Leading One Test (LOG2) (V)8B                                | 3-70 |

|         | Queue                                 |                     |         | Branch Operators                                             | 3-70 |

|         | Storage Unit Operations Queue         | 3-34                |         | Branch Unconditional (BRUN) (P)A2                            | 3-70 |

|         | Loading the Storage Unit Op Code      | 3-34                |         | Branch on True (BRTR) (P)A1                                  | 3-70 |

|         | Flip-Flops                            |                     |         | Branch on False (BRFL) (P)A0                                 | 3-70 |

|         | Loading the Storage Unit Variants     | 3-34                |         | Dynamic Branch Unconditional                                 | 3-70 |

|         | Flip-Flops                            |                     |         | (DBUN) (P)AA                                                 | 9.0  |

|         | Loading the Storage Unit Length       | 3-35                |         | Dynamic Branch True (DBTR) (P)A9                             | 3-71 |

|         | Register                              |                     |         | Dynamic Branch False (DBFL) (P)A8                            | 3-71 |

|         | Storage Unit Data Queue               | 3-35                |         | Step and Branch (STBR) (P)A4                                 | 3-71 |

|         | Memory Address Register               | 3-35                |         | Compare Operators                                            | 3-71 |

|         | Storage Unit Control Logic            | 3-35                |         | Compare Characters Greater,                                  | 3-71 |

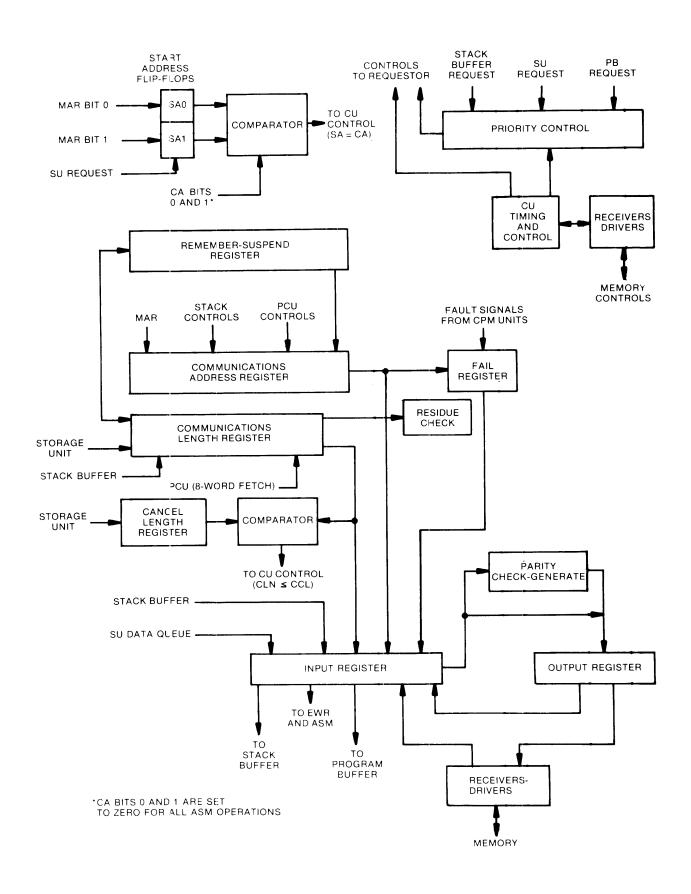

|         | Communications Unit                   | 3-36                |         | Destructive (CGTD) (P)F2                                     | 0-11 |

|         | Fault Control Logic                   | 3-39                |         | Compare Characters Greater, Update                           | 3-72 |

|         | -                                     |                     |         | (CGTU) (P)FA                                                 | 3-12 |

|         | Section 2 - Interrupts                | 3-41                |         | Compare Characters Greater or                                | 3-72 |

|         | Introduction                          | 3-41                |         | Equal, Destructive (CGED) (P)F1                              | 3-12 |

|         | Hardware Interrupt System             | 3-41                |         | Compare Characters Greater or                                | 3-72 |

|         | CPM States and Modes                  | 3-41                |         |                                                              | 0-12 |

|         | Control State                         | 3-41                |         | Equal, Update (CGEU) (P)F9                                   | 0.50 |

|         | Normal State                          | 3-42                |         | Compare Characters Equal,                                    | 3-72 |

|         | Fault Control Logic                   | 3-42                |         | Destructive (CEQD) (P)F4                                     | 0.50 |

|         | Fault Condition Register              | 3-42                |         | Compare Characters Equal, Update                             | 3-72 |

|         | Fault Mask Register                   | 3-42                |         | (CEQU) (P)FC                                                 |      |

|         | Interrupt Identification              | 3-43                |         | Compare Characters Less or Equal,                            | 3-72 |

|         | CPM Fail Register                     | $\frac{3-43}{3-44}$ |         | Destructive (CLED) (P)F3                                     |      |

|         | Control Mode Register                 |                     |         | Compare Characters Less or Equal,                            | 3-72 |

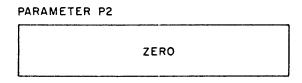

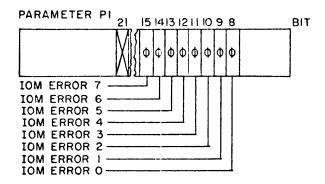

|         | IOM Fail Word                         | 3-45                |         | Update (CLEU) (P)FB                                          |      |

|         |                                       | 3-45                |         | Compare Characters Less, Destructive                         | 3-72 |

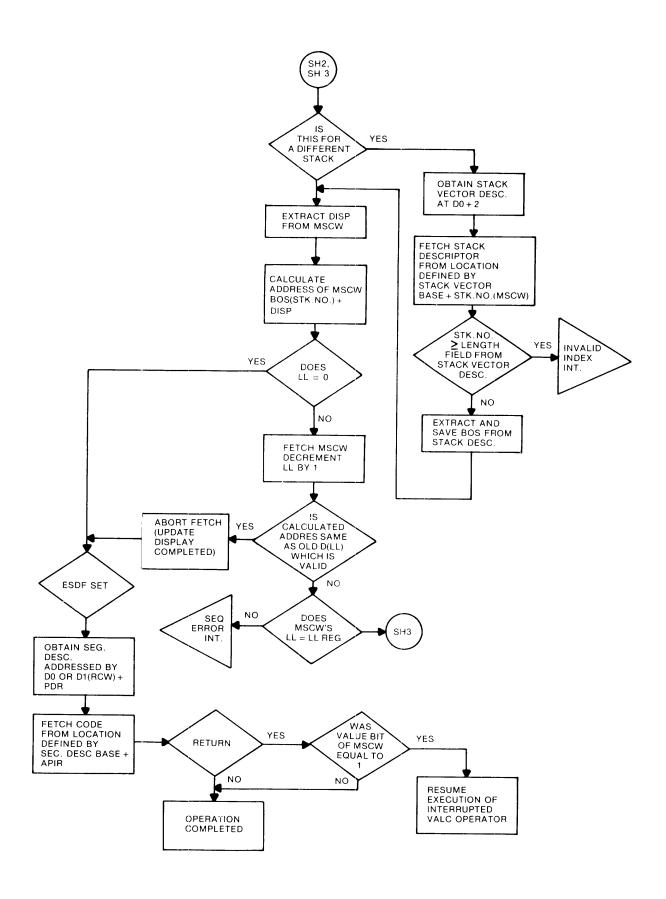

|         | Interrupt Processing                  | 3-45                |         | (CLSD) (P)F0                                                 |      |

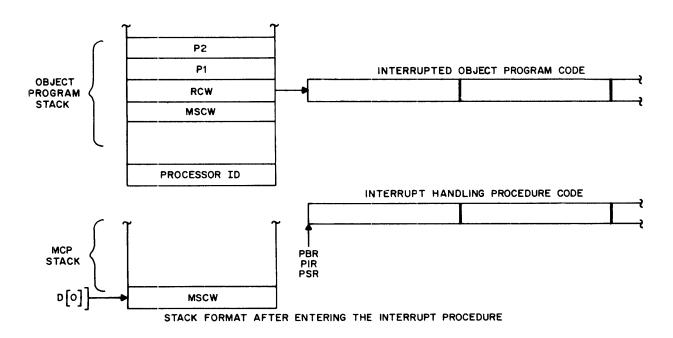

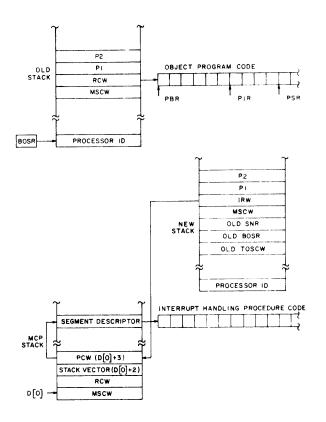

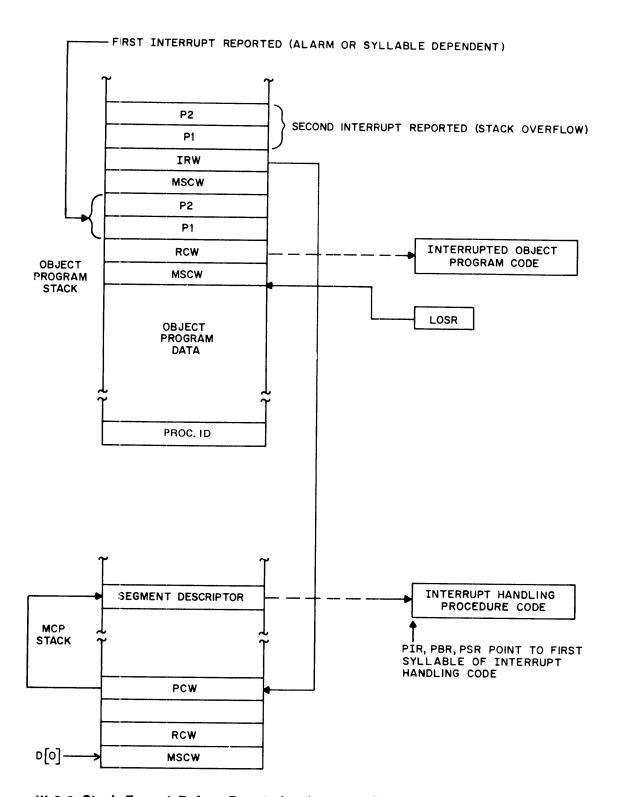

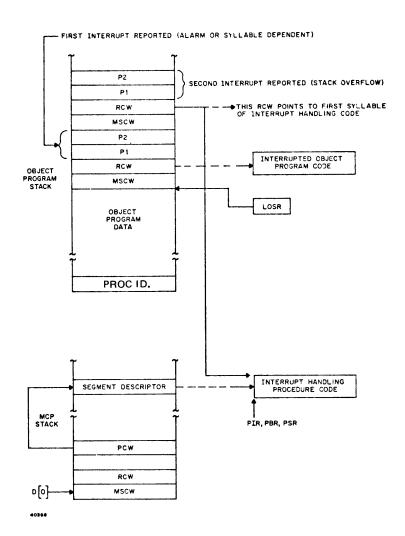

|         | Interrupt Processing in Normal Mode   | 3-45                |         | Compare Characters Less, Update                              | 3-72 |

|         | Interrupt Processing in CMI           | 3-48                |         | (CLSU) (P)F8                                                 |      |

|         | Interrupt Processing in CM2           | 3-48                |         | Compare Characters Not Equal,                                | 3-72 |

|         | Interrupt Processing in CM3           | 3-48                |         | Destructive (CNED) (P)F5                                     |      |

|         | Control Mode Advancement              | 3-48                |         | Compare Characters Not Equal,                                | 3-72 |

|         | Alarm Interrupts                      | 3-49                |         | Update (CNEU) (P)FD                                          |      |

|         | Syllable Dependent Interrupts         | 3-49                |         | Enter Edit Mode Operators                                    | 3-72 |

|         | (Second Priority)                     |                     |         | Table Enter Edit, Destructive (TEED)                         | 3-73 |

|         | Special Interrupts (Third Priority)   | 3-49                |         | (P)D0                                                        |      |

|         | External Interrupts (Fourth Priority) | 3-49                |         | Table Enter Edit, Update (TEEU)                              | 3-73 |

|         | Memory Related Interrupts             | 3-49                |         | (P)D8                                                        | 5 10 |

|         | Interrupt Descriptions                | 3-52                |         | Execute Single Micro, Destructive                            | 3-73 |

|         | Alarm Interrupts                      | 3-52                |         | (EXSD) (P)D2                                                 | 9-19 |

|         | Syllable Dependent Interrupts         | 3-56                |         | Execute Single Micro, Update (EXSU)                          | 3-73 |

|         | Special Interrupts                    | 3-62                |         | (P)DA                                                        | 0-10 |

|         |                                       |                     |         | \-/                                                          |      |

| Chapter | Title                                                              | Page                | Chapter | Title                                                        | Page |

|---------|--------------------------------------------------------------------|---------------------|---------|--------------------------------------------------------------|------|

|         | Execute Single Micro, Single Pointer<br>Update (EXPU) (P)DD        | 3-73                |         | Overwrite Non-Destructive (OVRN) (P)BB                       | 3-81 |

|         | Enter Vector Mode Operators                                        | 3-73                |         | Read With Lock (RDLK) (V)BA                                  | 3-81 |

|         | Single-Word Vector Mode (VMOS)                                     | 3-75                |         | String Operators                                             | 3-81 |

|         | (P)EF                                                              |                     |         | String Isolate (SISO) (P)D5                                  | 3-82 |

|         | Multiple-Word Vector Mode (VMOM)                                   | 3-76                |         | String Transfer Operators                                    | 3-82 |

|         | (P)E7                                                              |                     |         | Transfer Words, Destructive (TWSD)                           | 3-82 |

|         | Index and Load Operators                                           | 3-76                |         | (P)D3                                                        |      |

|         | Index (INDX) (P)A6                                                 | 3-76                |         | Transfer Words, Update (TWSU)                                | 3-82 |

|         | Index and Load Name (NXLN) (P)A5                                   | 3-77                |         | (P)DB                                                        |      |

|         | Index and Load Value (NXLV) (P)AD                                  | 3-77                |         | Transfer Words, Overwrite                                    | 3-83 |

|         | Load Transparent (LODT) (V)BC                                      | 3-77                |         | Destructive (TWOD) (P)D4                                     |      |

|         | Input Convert Destruction (ICVD)                                   | 3-77                |         | Transfer Words, Overwrite Update                             | 3-83 |

|         | Input Convert, Destructive (ICVD) (P)CA                            | 3-77                |         | (TWOU) (P)DC<br>Transfer While Greater, Destructive          | 3-83 |

|         | Input, Convert, Update (ICVU) (P)CB                                | 3-77                |         | (TGTD) (P)EZ                                                 | 0-00 |

|         | Literal Call Operators                                             | 3-77                |         | Transfer While Greater, Update                               | 3-83 |

|         | Lit Call Zero (ZERO) (P)B0                                         | 3-78                |         | (TGTU) (P)EA                                                 | 3 33 |

|         | Lit Call One (ONE) (P)B1                                           | 3-78                |         | Transfer While Greater or Equal,                             | 3-83 |

|         | Lit Call 8 Bits (LT8) (P)B2                                        | 3-78                |         | Destructive (TGED) (P)E1                                     | 3 00 |

|         | Lit Call 16 Bits (LT16) (P)B3                                      | 3-78                |         | Transfer While Greater or Equal.                             | 3-83 |

|         | Lit Call 48 Bits (LT48) (P)BE                                      | 3-78                |         | Update (TGEU) (P)E9                                          | 3.00 |

|         | Make Program Control Word (MPCW)<br>(P)BF                          | 3-78                |         | Transfer While Equal, Destructive (TEQD) (P)E4               | 3-83 |

|         | Logical Operators                                                  | 3-78                |         | Transfer While Equal, Update                                 | 9.00 |

|         | Logical and (LAND) (P)90                                           | 3-78                |         | (TEQU) (P)EC                                                 | 3-83 |

|         | Logical or (LOR) (P)91                                             | 3-78                |         | Transfer While Less or Equal,                                | 9 09 |

|         | Syllable Dependent Interrupts                                      | 3-51                |         | Destructive (TLED) (P)E3                                     | 3-83 |

|         | (Second Priority)                                                  |                     |         | Transfer While Less or Equal,                                | 3-83 |

|         | Special Interrupts (Third Priority)                                | 3-51                |         | Update (TLEU) (P)EB                                          | 9-09 |

|         | External Interrupts (Fourth Priority)                              | 3-51                |         | Transfer While Less, Destructive                             | 3-83 |

|         | Pack, Destructive (PACD) (P)D1                                     | 3-78                |         | (TLSD) (P)E0                                                 | 0-00 |

|         | Pack, Update (PACU) (P)D9                                          | 3-79                |         | Transfer While Less, Update (TLSU)                           | 3-83 |

|         | Relational Operators                                               | 3-79                |         | (P)E8                                                        | 0.00 |

|         | Greater Than (GRTR) (P)8A                                          | 3-79                |         | Transfer While Not Equal,                                    | 3-84 |

|         | Greater Than or Equal (GREQ) (P)89                                 | 3-79                |         | Destructive (TNED) (P)E5                                     |      |

|         | Equal (EQUL) (P)8C                                                 | 3-79                |         | Transfer While Not Equal, Update                             | 3-84 |

|         | Less Than or Equal (LSEQ) (P)8B                                    | 3-79                |         | (TNEU) (P)ED                                                 |      |

|         | Less Than (LESS) (P)88                                             | 3-79                |         | Transfer While True, Destructive                             | 3-84 |

|         | Not Equal (NEQL) (P)8D                                             | 3-79                |         | (TWTD) (V)D3                                                 |      |

|         | Logical Equal (SAME) (P)94                                         | 3-79                |         | Transfer While True, Update (TWTU)                           | 3-84 |

|         | Scale Operators                                                    | 3-80                |         | (V)DB                                                        |      |

|         | Scale Left (SCLF) (P)C0                                            | 3-80                |         | Transfer While False, Destructive                            | 3-84 |

|         | Dynamic Scale Left (DSLF) (P)C1<br>Scale Right Save (SCRS) (P)C4   | 3-80                |         | (TWFD) (V)D2                                                 |      |

|         | Dynamic Scale Right Save (DSRS)                                    | $\frac{3-80}{3-80}$ |         | Transfer While False, Update (TWFU) (V)DA                    | 3-84 |

|         | (P)C5<br>Scale Right Truncate (SCRT) (P)C2                         | 3-80                |         | Transfer Unconditional, Destructive                          | 3-84 |

|         | Dynamic Scale Right Truncate                                       | 3-80<br>3-80        |         | (TUND) (P)E6<br>Transfer Unconditional, Update               | 3-84 |

|         | (DSRT) (P)C3                                                       |                     |         | (TUNU) (P)EE                                                 |      |

|         | Scale Right Rounded (SCRR) (P)C8                                   | 3-80                |         | Subroutine Operators                                         | 3-84 |

|         | Dynamic Scale Right Rounded                                        | 3-80                |         | Mark Stack (MKST) (P)AE                                      | 3-85 |

|         | (DSRR) (P)C9                                                       |                     |         | Insert Mark Stack (IMKS) (P)CF                               | 3-85 |

|         | Scale Right Final (SCRF) (P)C6                                     | 3-80                |         | Name Call (NAMC) (P)40 thru (P)7F                            | 3-85 |

|         | Dynamic Scale Right Final (DSRF)                                   | 3-80                |         | Value Call (VALC) (P)00 thru (P)3F                           | 3-85 |

|         | (P)C7                                                              | 0.00                |         | Evaluate Descriptor (EVAL) (P)AC                             | 3-85 |

|         | Stack Operators Evaluation (EVCH) (D)DC                            | 3-80                |         | Enter (ENTR) (P)AB                                           | 3-88 |

|         | Exchange (EXCH) (P)B6 Rotate Stack Down (PSDN) (V)P7               | 3-80                |         | Exit (EXIT) (P)A3                                            | 3-88 |

|         | Rotate Stack Down (RSDN) (V)B7                                     | 3-80                |         | Return (RETN) (P)A7                                          | 3-88 |

|         | Rotate Stack Up (RSUP) (V)B6 Duplicate Top-Of0Stack (DUPL) (P)B7   | 3-81                |         | Transfer Operators                                           | 3-88 |

|         | Delete Top-Of-Stack (DUPL) (P)B7  Delete Top-Of-Stack (DLET) (P)B5 | 3-81                |         | Field Transfer (FLTR) (P)98                                  | 3-88 |

|         | Push Down Stack Registers (PUSH)                                   | 3-81                |         | Dynamic Field Transfer (DFTR) (P)99                          | 3-88 |

|         | (P)B4                                                              | 3-81                |         | Field Isolate (ISOL) (P)9A                                   | 3-88 |

|         | Store Destructive (STOD) (P)B8                                     | 9 01                |         | Dynamic Field Isolate (DISO) (P)9B                           | 3-88 |

|         | Store Non-Destructive (STON) (P)B9                                 | $\frac{3-81}{3-81}$ |         | Field Insert (InSR) (P)9C                                    | 3-96 |

|         | Overwrite Destructive (OVRD) (P)BA                                 | 3-81                |         | Dynamic Field Insert (DINS) (P)9D<br>Type-Transfer Operators | 3-96 |

|         | (1)D1                                                              | 3 01                |         | Type transfer Operators                                      | 3-96 |

| Chapter | Title                                                                        | Page                | Chapter | Title                                                                  | Page                  |

|---------|------------------------------------------------------------------------------|---------------------|---------|------------------------------------------------------------------------|-----------------------|

|         | Set to Single-Precision, Truncated (SNGT) (P)CC                              | 3-96                |         | Disable External Interrupts (DEXI)                                     | 3-98                  |

|         | Set to Single-Precision, Truncated (SNGL) (P)CD                              | 3-96                |         | (V)47 Idle Until Interrupt (IDLE) (V)44 Read Processor Register (RPRR) | 3-98<br>3-98          |

|         | Set to Double-Precision (XTND) (P)CE<br>Set Double to Two Singles (SPLT)     | 3-96<br>3-96        |         | (V)B8<br>Set Processor Register (SPRR) (V)B9                           | 3-99                  |

|         | (V)43<br>Set Two Singles to a Double (JOIN)                                  | 3-96                |         | Unpack Operators Unpack Absolute, Destructive (UABD)                   | 3-99<br>3-99          |

|         | (V)42<br>Miscellaneous Primary Mode                                          | 3-96                |         | (V)D1<br>Unpack Absolute, Update (UABU)                                | 3-99                  |

|         | Operators Escape to 16-Bit Instruction (VARI)                                | 3-96                |         | (V)D9<br>Unpack Signed, Destructive (USND)                             | 3-99                  |

|         | (P)95 Read and Clear Overflow Flip-Flop (ROFF) (P)D7                         | 3-96                |         | (V)D0<br>Unpack Signed, Update (USNU) (V)D8                            | 3-100                 |

|         | Read True False Flip-Flop (RTFF) (P)DE                                       | 3-96                |         | Linked List Lookup (LLLU) (V)BD<br>Masked Search for Equal (SRCH)      | 3-100<br>3-100        |

|         | Set External Sign (SXSN) (P)D6                                               | 3-96                |         | (V)BE<br>Move to Stack (MVST) (V)AF                                    | 3-100                 |

|         | Stuff Environment (STFF) (P)AF                                               | $\frac{3-96}{3-96}$ |         | Occurs Index (OCRX) (V)85                                              | 3-100                 |

|         | Universal Operators<br>Conditional Halt (HALT) (U)DF                         | 3-96                |         | Translate (TRNS) (V)D7                                                 | 3-101                 |

|         | Invalid Operator (NVLD) (U)FF                                                | 3-96                |         | Operators Exclusive to the B 7700                                      | 3-101                 |

|         | No Operation (NOOP) (U)FE                                                    | 3-96                |         | Set Memory Inhibits (SINH) (V)A8                                       | 3-101                 |

|         | Variant Mode Operations                                                      | 3-96                |         | (Control State Op)                                                     | 9 101                 |

|         | Scan Operators                                                               | 3-97                |         | Fetch Memory Fail Register (FMFR)                                      | 3-101                 |

|         | Scan In (SCNI) (V)4A                                                         | 3-97                |         | (V)AC (Control State Op) Ignore Parity (IGPR) (V)48 (Control           | 3-101                 |

|         | Scan While Operators                                                         | $\frac{3-97}{2.07}$ |         | State Op)                                                              | 9 101                 |

|         | Scan While Greater, Destructive                                              | 3-97                |         | Pause Until Interrupt (PAUS) (V)84                                     | 3-102                 |

|         | (SGTD) (V)F2<br>Scan While Greater, Update (SGTU)                            | 3-97                |         | Interrupt Channel N (INCN) (V)8F                                       | 3-102                 |

|         | (V)FA                                                                        | 00.                 |         | Stop (STOP) (V)BF                                                      | 3-102                 |

|         | Scan While Greater or Equal,                                                 | 3-97                |         | Edit Mode Operators                                                    | 3-102                 |

|         | Destructive (SGED) (V)FL                                                     |                     |         | Insert Operators                                                       | 3-102                 |

|         | Scan While Greater or Equal, Update                                          | 3-97                |         | Insert Unconditional (INSU) (E)DC                                      | $\frac{3-102}{3-102}$ |

|         | (SGEU) (V)F9                                                                 | 0.05                |         | Insert Conditional (INSC) (E)DD<br>Insert Display Sign (INSG) (E)D9    | 3-102                 |

|         | Scan While Equal, Destructive                                                | 3-97                |         | Insert Overpunch (INOP) (E)D8                                          | 3-102                 |

|         | (SEQD) (V)F4                                                                 | 3-97                |         | Move Operators                                                         | 3-102                 |

|         | Scan While Equal, Update (SEQU)                                              | 0-01                |         | Move With Insert (MINS) (E)D0                                          | 3-102                 |

|         | (V)FC<br>Scan While Less or Equal,                                           | 3-97                |         | Move With Float (MFLT) (E)D1                                           | 3-103                 |

|         | Destructive (SLED) (V)F3                                                     |                     |         | Move Characters (MCHR) (E)D7                                           | 3-103                 |

|         | Scan While Less or Equal, Update                                             | 3-97                |         | Skip Operators                                                         | 3-103                 |

|         | (SLEU) (V)FB<br>Scan While Less, Destructive (SLSD)                          | 3-97                |         | Skip Forward Source Characters<br>(SFSC) (E)D2                         | 3-103                 |

|         | (V)F0                                                                        | 3-97                |         | Skip Reverse Source Characters<br>(SRSC) (E)D3                         | 3-103                 |

|         | Scan While Less, Update (SLSU)<br>(V)F8<br>Scan While Not Equal, Destructive | 3-97                |         | Skip Forward Destination Characters (SFDC) (E)DA                       | 3-103                 |

|         | (SNED) (V)F5 Scan While Not Equal, Update                                    | 3-98                |         | Skip Reverse Destination Characters (SRDC) (E)DB                       | 3-103                 |

|         | (SNEU) (V)FD                                                                 | 9.00                |         | Reset Float (RSTF) (E)D4                                               | 3-103                 |

|         | Scan While True, Destructive (SWTD)                                          | 3-98                |         | End Float (ENDF) (E)D5                                                 | 3-103                 |

|         | (V)D5                                                                        |                     |         | End Edit (ENDE) (E)DE                                                  | 3-104                 |

|         | Scan While True, Update (SWTU)                                               | 3-98                |         | Universal Operators                                                    | 3-104<br>3-104        |

|         | (V)DD                                                                        | 0.00                |         | No Operation (NOOP) (U)FE<br>Conditional Halt (HALT) (U)DF             | 3-104                 |

|         | Scan While False, Destructive                                                | 3-98                |         | Invalid Operator (NVLD) (U)FF                                          | 3-104                 |

|         | (SWFD) (V)D4                                                                 | 3-98                |         | Vector Mode Operators                                                  | 3-104                 |

|         | Scan While False, Update (SWFU)                                              | 0-90                |         | Vector Branch (VEBR) (Z)EE                                             | 3-105                 |

|         | (V)DC<br>Tag Field Operators                                                 | 3-98                |         | Vector Exit (VXIT) (Z)E6                                               | 3-105                 |

|         | Set Tag Field (STAG) (V)B4                                                   | 3-98                |         | Vector Stack Operators                                                 | 3-105                 |

|         | Read Tag Field (RTAG) (V)B5                                                  | 3-98                |         | Load A (LDA) (Z)E0                                                     | 3-105                 |

|         | Set Internal Timer (SINT) (V)45                                              | 3-98                |         | Load B (LDB) (Z)EZ                                                     | 3-105                 |

|         | (Control State Operator)                                                     |                     |         | Load C (LDC) (Z)E4                                                     | $\frac{3-105}{3-105}$ |

|         | Read Processor Identification (WHOI)                                         | 3-98                |         | Load A, Increment (LDAI) (Z)E1<br>Load B, Increment (LDBI) (Z)E3       | 3-105<br>3-105        |

|         | (V)4E                                                                        | 9.00                |         | Load C, Increment (LDCI) (Z)E5                                         | 3-105                 |

|         | Enable External Interrupts (EEXI)<br>(V)46                                   | 3-98                |         | Store A (STA) (Z)F0                                                    | 3-105                 |

|         |                                                                              |                     |         |                                                                        |                       |

| Chapter | Title                                                              | Page                    | Chapter | Title                                                               | Page                |

|---------|--------------------------------------------------------------------|-------------------------|---------|---------------------------------------------------------------------|---------------------|

|         | Store B (STB) (Z)F2                                                | 3-105                   |         |                                                                     |                     |

|         | Store C (STC) (Z)FA Store A, Increment (STAI) (Z)F1                | 3-105<br>3-105<br>3-105 |         | Synchronous I/O Command (Home<br>Code 1010)                         | 4-14                |

|         | Store B, Increment (STBI) (Z)FB<br>Store C, Increment (STCI) (Z)F5 | 3-105<br>3-105          |         | Interrogate Peripheral Status<br>Command (Home Code 1011)           | 4-14                |

|         | Double Load A (DLA) (Z)E8 Double Load B (DLB) (Z)EA                | 3-105<br>3-105<br>3-105 |         | Inhibit IOM Command (Home Code 1100)                                | 4-14                |

|         | Double Load C (DLC) (Z)EC Double Load A, Increment (DLAI)          | 3-105                   |         | Activate IOM Command (Home Code 1101)                               | 4-15                |

|         | (Z)E9 Double Load B, Increment (DLBI)                              | 3-105                   |         | Load DFO Flags Command (Home<br>Code 1110)                          | 4-15                |

|         | (Z)EB Double Load C, Increment (DLCI)                              | 3-105                   |         | Automatic Service of Disk Jobs for<br>Units Under DFO Control       | 4-15                |

|         | (Z)ED                                                              | 3-105                   |         | Automatic Disk-Pack Operation Data Translation                      | $\frac{4-15}{4-16}$ |

|         | Double Store A (DSA) (Z)F8 Double Store B (DSB) (Z)FA              | 3-105                   |         | EBCDIC-BCL Exceptions                                               | 4-16                |

|         | Double Store C (DSC) (Z)FC                                         | $\frac{3-106}{3-106}$   |         | IOM-Generated Interrupts                                            | 4-16                |

|         | Double Store A, Increment (DSAI) (Z)F9                             | 3-106                   |         | Section - 2 Functional Operation of Input/Output Module Subsections | 4-18                |

|         | Double Store B, Increment (DSBI)<br>(Z)FB                          | 3-106                   |         | General<br>Functional Operation of Translator                       | 4-18                |

|         | Double Store C, Increment (DSCI)                                   | 3-106                   |         | Job Service Iniation                                                | 4-18<br>4-18        |

|         | (Z)FD                                                              | 3 200                   |         | Job-Service Termination                                             | 4-18<br>4-18        |

|         | Vector Fetch and Store Operators                                   | 3-106                   |         | Exchange Ring Walk                                                  | 4-20                |

|         | Vector Fetch (FTCH) (Z)00 thru (Z)3F                               | 3-106                   |         | Automatic Service of Disk Jobs via                                  | 4-20                |

|         | Vector Store (STOR) (Z)40 thru (Z)7F                               | 3-106                   |         | DFO Units                                                           |                     |

| IV      | INPUT/OUTPUT SUBSYSTEM                                             | 4-1                     |         | Disk-Pack Control                                                   | 4-21                |

|         | Section 1 - General Description and                                | 4-1                     |         | Fail Mode of Operation                                              | 4-21                |

|         | Operation of the Input/Output                                      | 4-1                     |         | Functional Operation of MIU                                         | 4-21                |

|         | Module                                                             |                         |         | Functional Components of the MIU                                    | 4-22                |

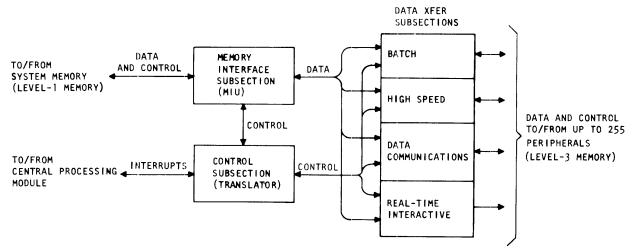

|         | Preliminary                                                        | 4 1                     |         | Functional Operation of PCI Channel Initiation Operation            | $\frac{4-24}{4-24}$ |

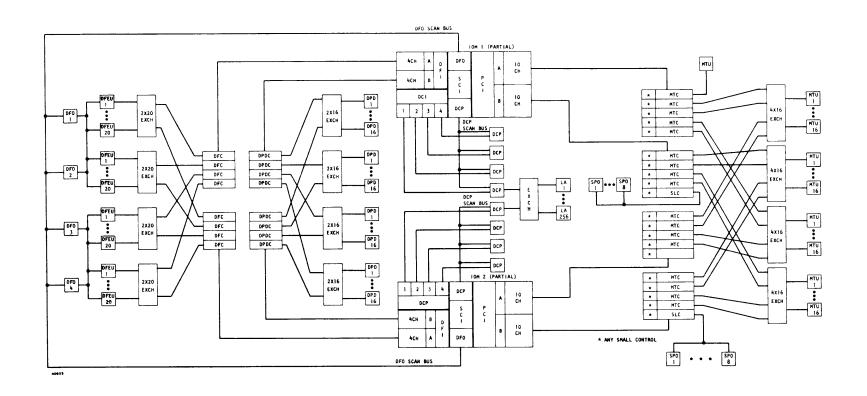

|         | Basic IOM Configuration                                            | 4-1<br>4-1              |         | Channel Service Operation                                           | 4-24                |

|         | Control Word Flow                                                  | 4-1                     |         | Memory Operation                                                    | 4-26                |

|         | Data Flow                                                          | 4-1                     |         | Channel Termination Operation                                       | 4-26                |

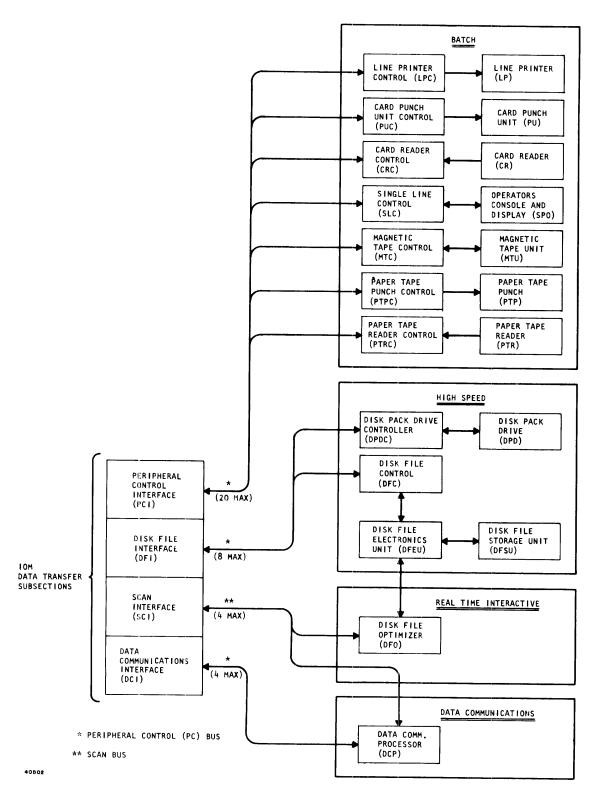

|         | IOM/Peripheral Interface                                           | 4-2                     |         | Functional Components of the PCI                                    | 4-26                |

|         | Configuration                                                      |                         |         | Functional Operation of DFI                                         | 4-27                |

|         | Peripheral Control Interface (PCI)                                 | 4-2                     |         | Channel Initiation Operation                                        | 4-27                |

|         | Disk File Interface (DFI)                                          | 4-2                     |         | Channel Service Operation                                           | 4-27                |

|         | Scan Interface (SCI)                                               | 4-2                     |         | Channel Termination Operation                                       | 4-29                |

|         | Data Communications Processor Interface (DCI)                      | 4-2                     |         | Functional Components of the DFI<br>Functional Operation of SCI     | $\frac{4-29}{4-29}$ |

|         | IOM/Main and IOM/CPM Interface                                     | 4-2                     |         | Scan Interface                                                      | 4-29                |

|         | Configurations                                                     | *-2                     |         | DCP Scan Interface                                                  | 4-31                |

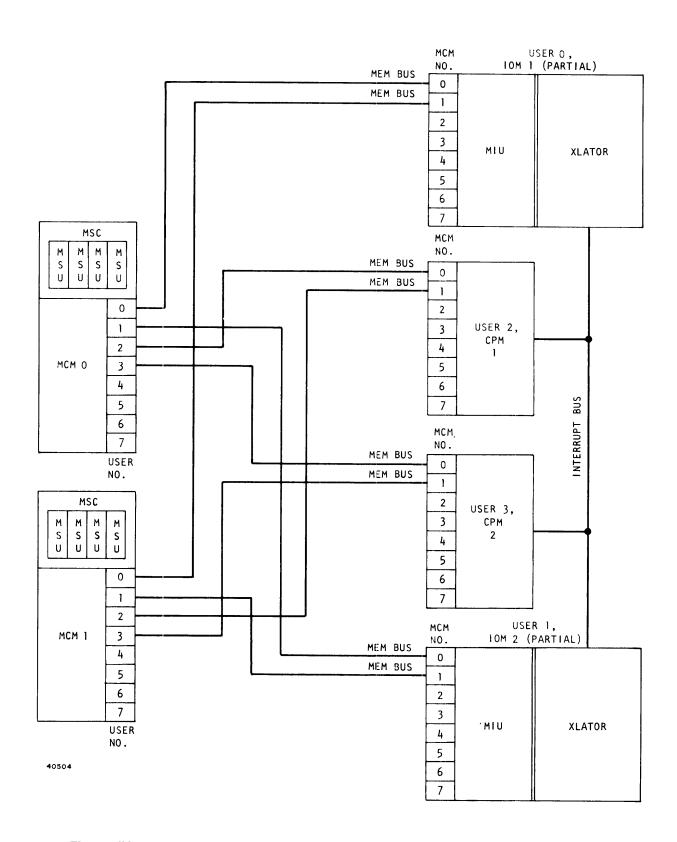

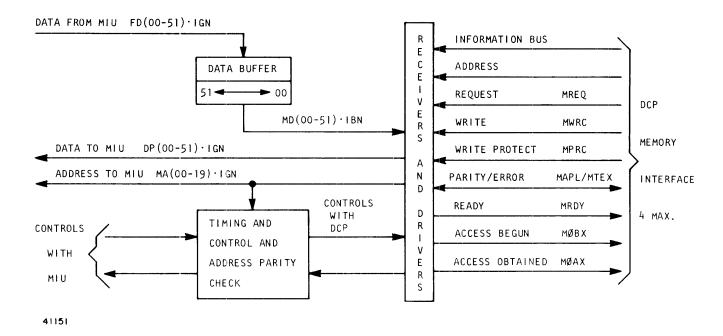

|         | IOM/MCM Interface                                                  | 4-2                     |         | Section 3 - Peripherals and Control                                 |                     |

|         | IOM/CPM Interface                                                  | 4-6                     |         | Word Formats                                                        | 4-32                |

|         | IOM Operational Characteristics                                    | 4-6                     |         |                                                                     |                     |

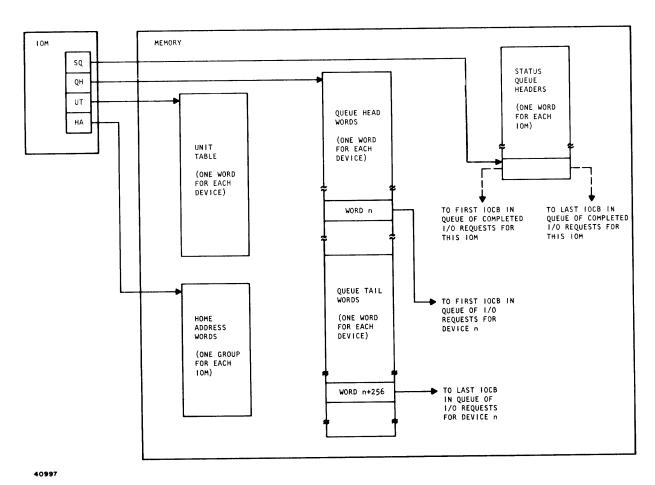

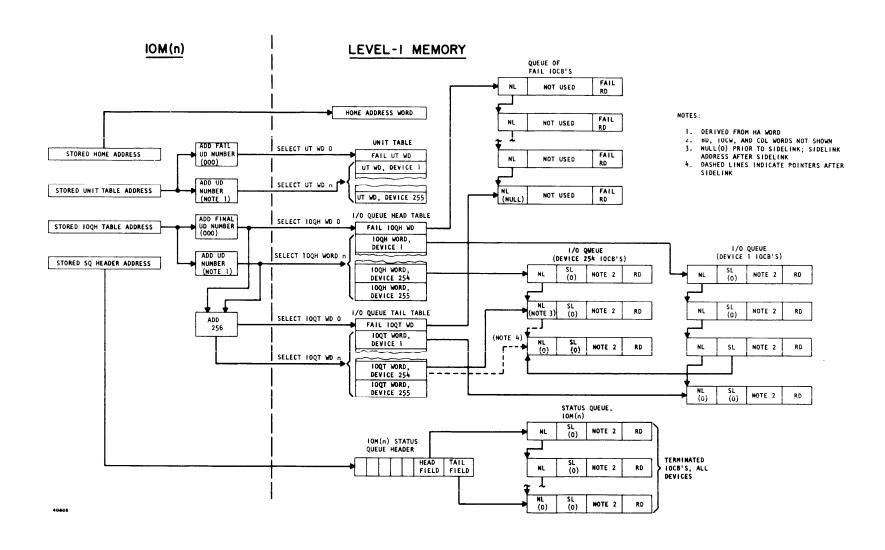

|         | IOM Job Map                                                        | 4-6                     |         | Standard Result Descriptor                                          | 4-33                |

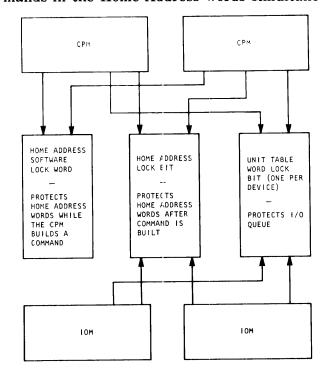

|         | Home Address Word                                                  | 4-8                     |         | Unit Related Errors Fail Result Descriptor                          | $\frac{4-34}{4-35}$ |

|         | Unit Table Word<br>IOQ Head (IOQH) and IOQ Tail                    | 4-8                     |         | Card Punch                                                          | 4-36                |

|         | (IOQT) Tables and Words                                            | 4-8                     |         | Card Punch Control                                                  | 4-36                |

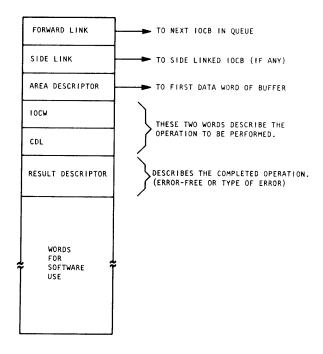

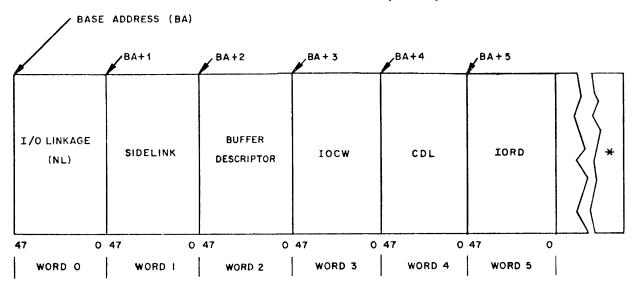

|         | I/O Control Blocks                                                 | 4-10                    |         | Operations                                                          | 4-36                |

|         | Fail I/O Control Blocks                                            | 4-10                    |         | BCL (Op 23)                                                         | 4-36                |

|         | Status Queue                                                       | 4-11                    |         | Binary (Op 24)                                                      | 4-37                |

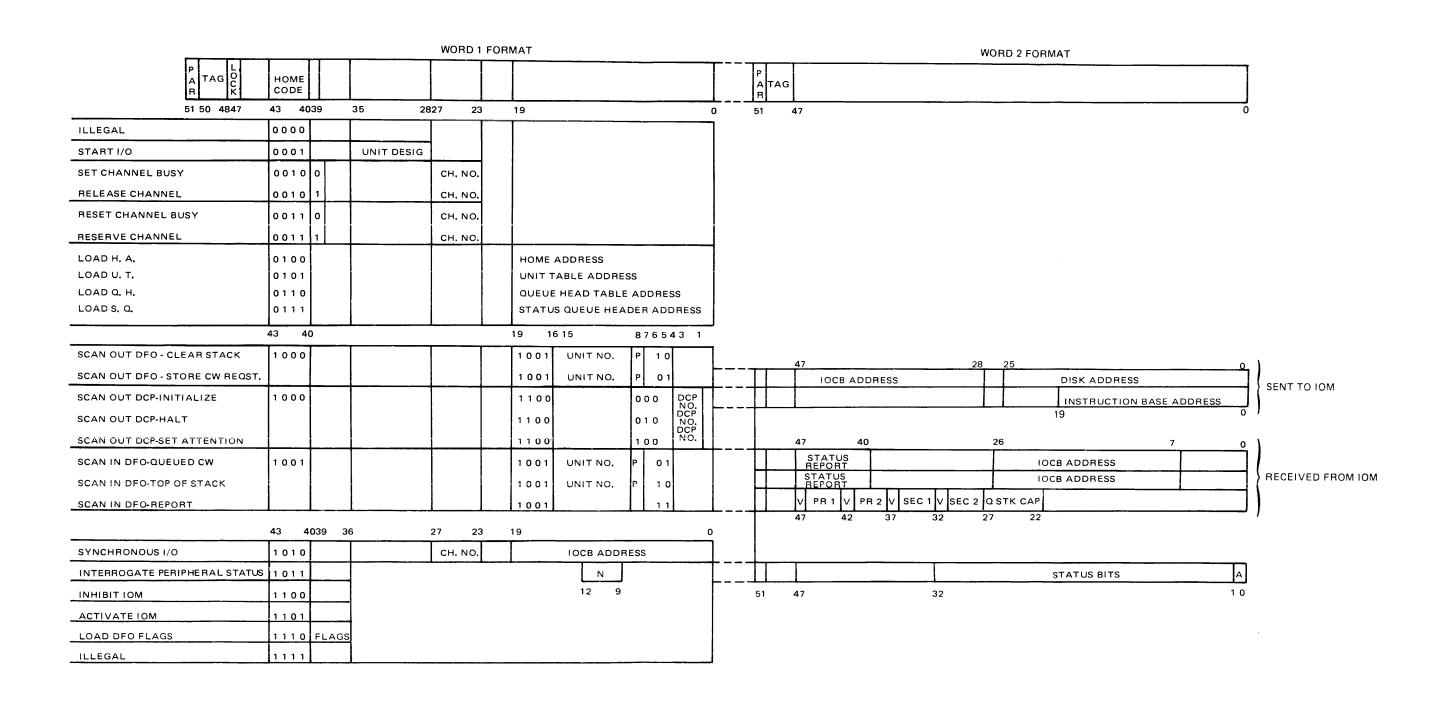

|         | IOM Home (HA) Commands                                             | 4-11                    |         | Card Punch EBCDIC (Op 25)                                           | 4-37                |

|         | Start I/O (Home Code 0001)                                         | 4-12                    |         | Test (Op 99)<br>Punch Check Error                                   | 4-37                |

|         | Set Channel Busy/Set Channel                                       | 4-12                    |         | Card Reader Control                                                 | 4-37                |

|         | Reserved (Home Code 0010) Reset Channel Busy/Reset Channel         | 4 10                    |         | BCL (Op 20)                                                         | $\frac{4-37}{4-38}$ |

|         | Reserved (Home Code 0011)                                          | 4-12                    |         | Binary (Op 21)                                                      | 4-38<br>4-38        |

|         | Load Address Commands                                              | 4-12                    |         | EBCDIC (Op 22)                                                      | 4-38                |

|         | DFO/DCP Scan-out Commands (Home                                    | 4-12                    |         | Test (Op 99)                                                        | 4-38                |

|         | Code 1000)                                                         |                         |         | Disk File Subsystem                                                 | 4-38                |

|         | DFO Scan-out Commands                                              | 4-12                    |         | Disk File Exchanges                                                 | 4-38                |

|         | DCP Scan-out Commands                                              | 4-14                    |         | Exchange Modularity                                                 | 4-39                |

|         | DFO Scan-in Commands (Home Code                                    | 4-14                    |         | Disk<br>Write (Op 50)                                               | 4-39                |

|         | 1001)                                                              |                         |         | write (Op 80)                                                       | 4-39                |

| Chapter | Title                                                     | Page           | Chapter | Title                                         | Page                |

|---------|-----------------------------------------------------------|----------------|---------|-----------------------------------------------|---------------------|

| Chapter |                                                           |                |         |                                               | 4.50                |

|         | Read (Op 51)                                              | 4-39           |         | Space Backward (Op 43)                        | $\frac{4-56}{4-56}$ |

|         | Check (Op 52)                                             | 4-39           |         | Rewind (Op 47)                                | 4-56<br>4-56        |

|         | Error Termination                                         | 4-39           |         | Test (Op 99)                                  | 4-56                |

|         | Disk-Pack Drive Memory System                             | 4-40           |         | Exception Conditions Single Line Control      | 4-56                |

|         | Read Binary Address Operation                             | 4-41           |         | Burroughs Terminal Computer Model             | 4-56                |

|         | Sector Address Conversion                                 | 4-42           |         | TC500                                         |                     |

|         | Disk Pack                                                 | 4-42           |         | Read (Op 32)                                  | 4-57                |

|         | Write (Op Code 50)                                        | $4-43 \\ 4-43$ |         | Write (Op 34)                                 | 4-57                |

|         | Read (Op Code 51)                                         | 4-43<br>4-43   |         | Test (Op 99)                                  | 4-57                |

|         | Initialize (Op Code 56)                                   | 4-43           |         | Single Line Control                           | 4-57                |

|         | Verify (Op Code 57)<br>Relocate (Op Code 58)              | 4-43           | V       | MEMORY SUBSYSTEM                              | 5-1                 |

|         | Test (Op Code 99)                                         | 4-43           |         | GENERAL DESCRIPTION OF THE                    | 5-1                 |

|         | Exception Conditions                                      | 4-43           |         | MEMORY SUBSYSTEM                              |                     |

|         | Single Bit Error Correction (SBE)                         | 4-43           |         | T t d                                         | 5-1                 |

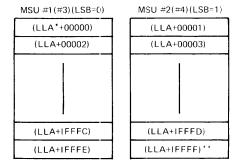

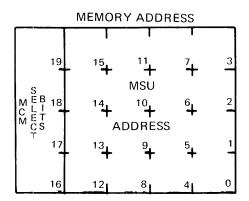

|         | Disk-Pack Drive Busy (Time-Out)                           | 4-43           |         | Introduction Memory Capacity                  | 5-2                 |

|         | (DRB)                                                     |                |         | Minimum Memory Size                           | 5-2                 |

|         | Speed Error (1081)                                        | 4-43           |         | Maximum Memory Size                           | 5-2                 |

|         | Address Position Error (Verify) (1101)                    | 4-43           |         | MSU Reconfiguration                           | 5-2                 |

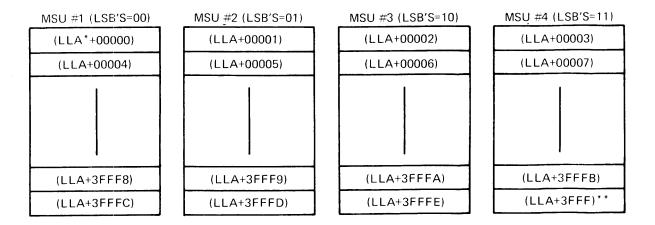

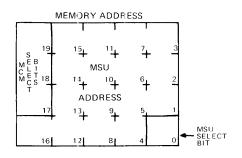

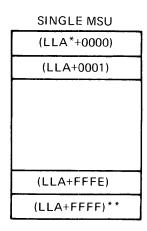

|         | Transmission Parity Error (1181)                          | 4-43           |         | Address Allocation                            | 5-2                 |

|         | Seek Time-Out (1801)                                      | 4-43           |         | Subsystem Allocation                          | 5-3                 |

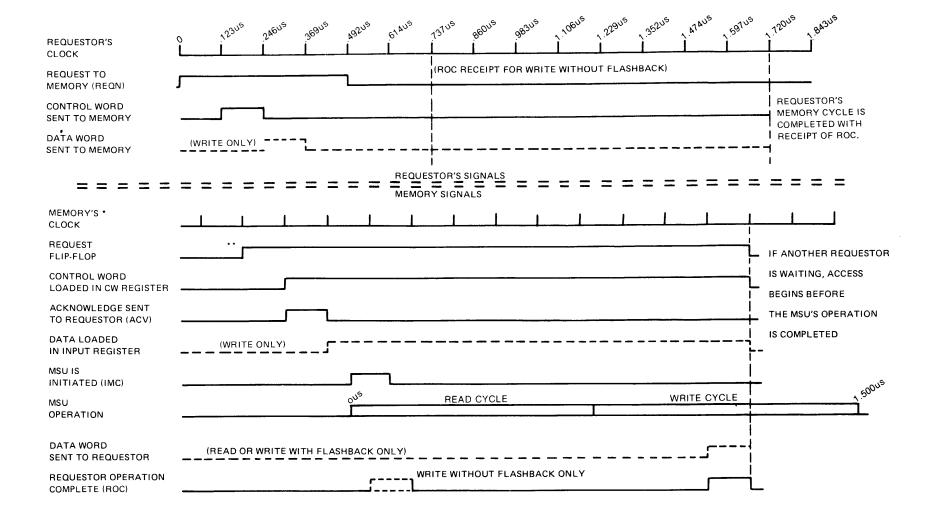

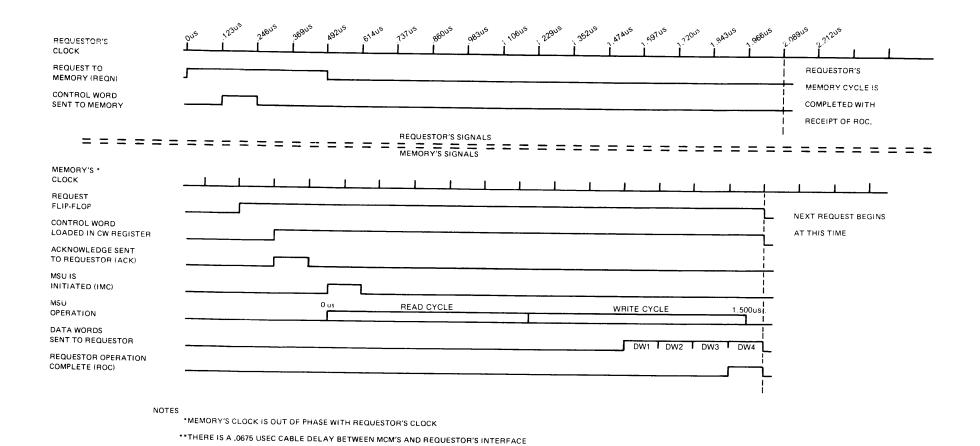

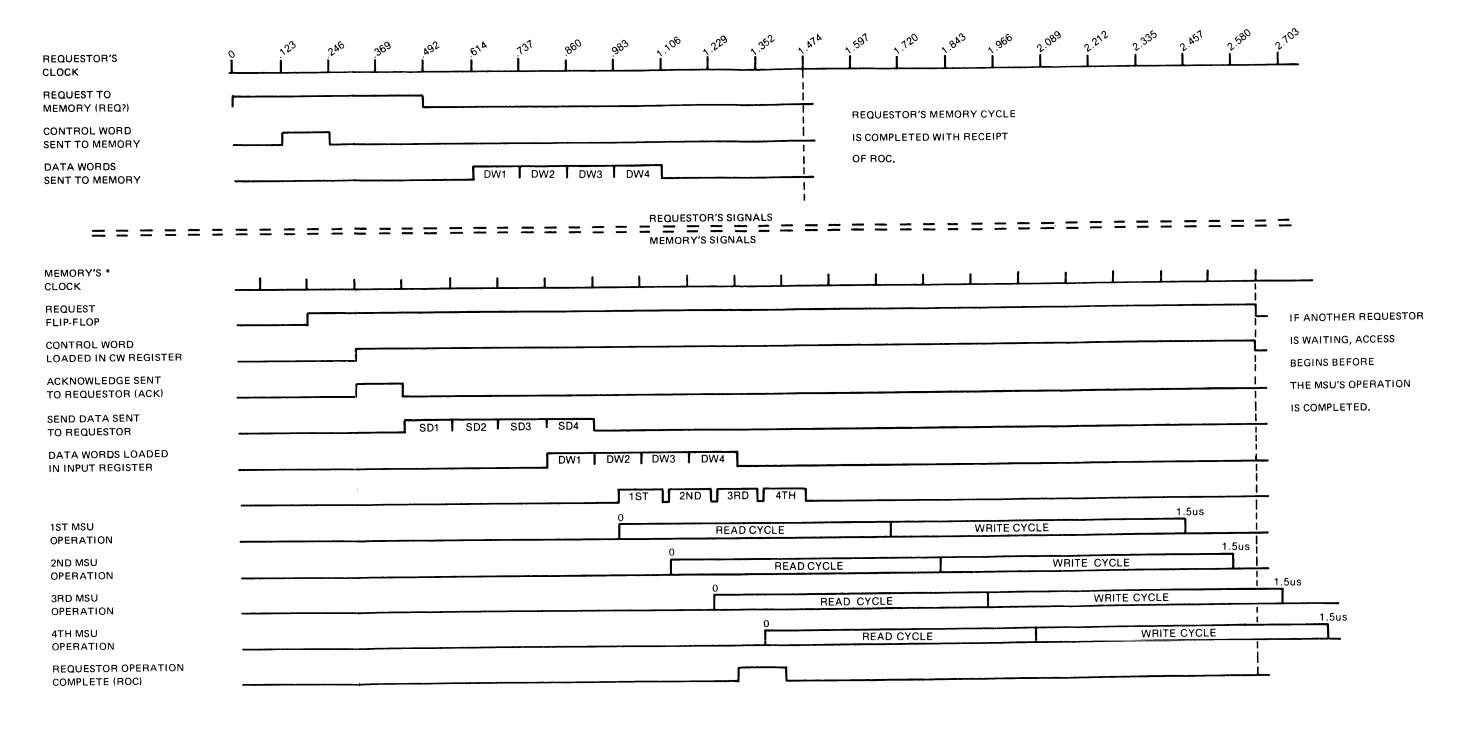

|         | Seek Error (DSK)                                          | 4-43           |         | Clock Rate and Read Access Times              | 5-3                 |

|         | Sector Time-Out (0901)                                    | 4-43           |         | Multiple-Word Transfer (Phasing)              | 5-3                 |

|         | Write-Lockout (0501)                                      | 4-43<br>4-44   |         | MSU Phasing                                   | 5-4                 |

|         | First Action (0301)                                       | 4-44           |         | Memory Operations Timing                      | 5-5                 |

|         | Memory Interface Parity Error (0081)                      | 4-44           |         | Word Formats                                  | 5-5                 |

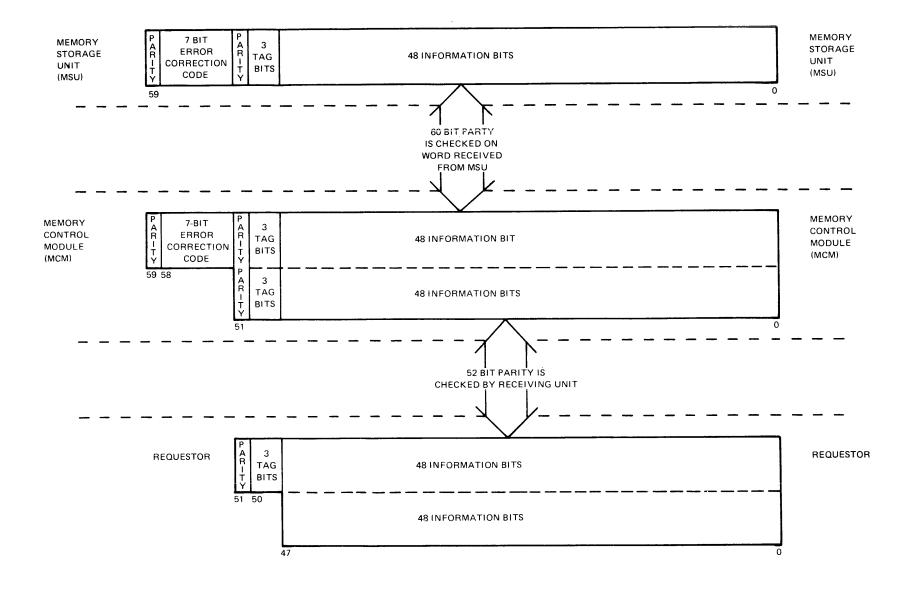

|         | Control Cleared (0089) General Information                | 4-44           |         | MCM Control Word                              | 5-10                |

|         | Multisector-Per-Track (Standard)                          | 4-44           |         | MCM Fail Word                                 | 5-10                |

|         | Format                                                    |                |         | Memory Address Limits Word                    | 5-12<br>5-13        |

|         | Spare Sectors                                             | 4-47           |         | Memory Requestor Inhibits Word                | 5-13<br>5-13        |

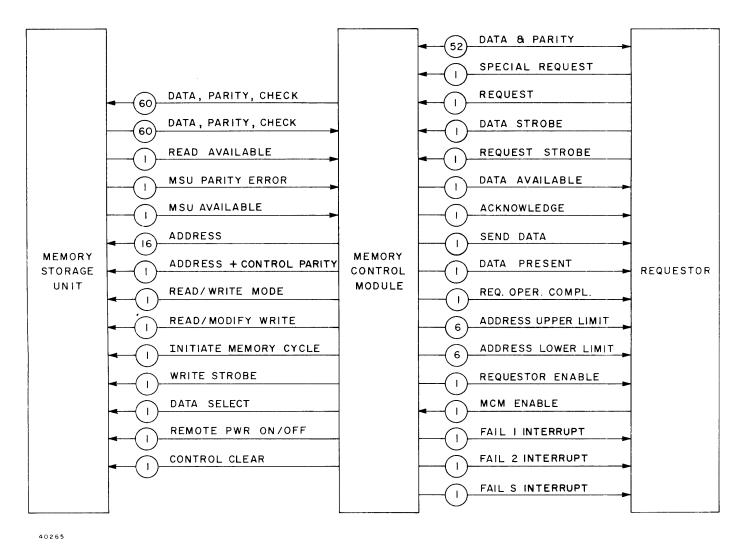

|         | Line Printer                                              | 4-47           |         | Signal Interface Between Requestor,           | 9-19                |

|         | Printer Control                                           | 4-47           |         | MCM, and MSU Signal Interface Between MCM and | 5-13                |

|         | Space (Op 11)                                             | 4-51           |         | Requestor                                     | 0.10                |

|         | Skip (Op 11)                                              | 4-51           |         | Signal Interface Between MCM and              | 5-15                |

|         | Test (Op 99)                                              | 4-51           |         | MSU                                           |                     |

|         | Error Termination                                         | 4-51           |         | Definition of MCM Operations                  | 5-16                |

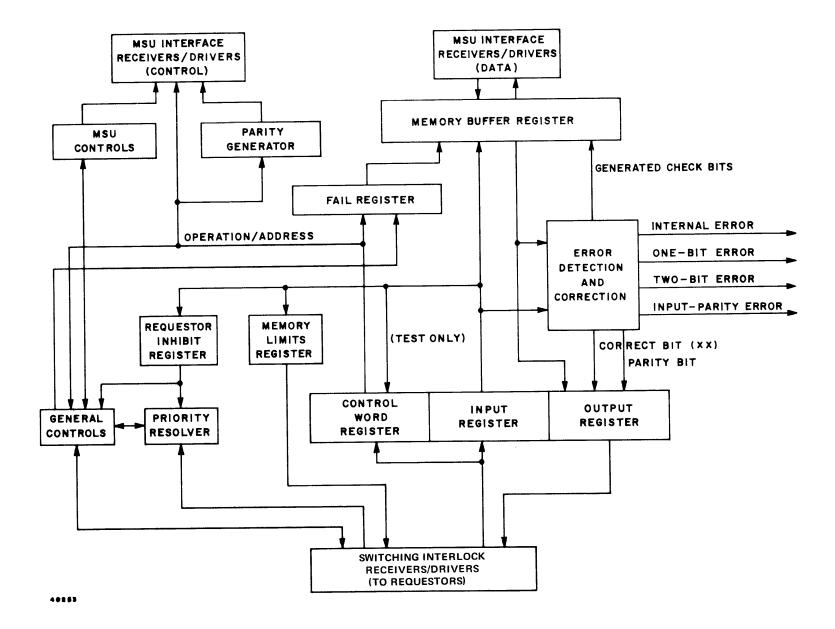

|         | Buffered Printer Control No. 2                            | 4-51           |         | MCM Logic Functions                           | 5-16                |

|         | Magnetic Tape                                             | 4-51           |         | Priority-Resolution Logic                     | 5-16                |

|         | Tape Subsystem                                            | 4-51<br>4-51   |         | Data-Transfer-and Control Logic               | 5-16                |

|         | Tape Exchanges, Free-Standing Units                       | 4-51           |         | Error-Detection Logic                         | 5-17                |

|         | Magnetic Tape Exchange No. 2                              | 4-52           |         | MSU Operational Modes                         | 5-17                |

|         | Magnetic Tape Exchange No. 1 Tape Exchange, Cluster Units | 4-52           |         | Master Clock and System Distribution          | 5-17                |

|         | Rewind (Op 01)                                            | 4-54           | VI      | CONTROLS AND INDICATIONS                      | 6-1                 |

|         | Read Op 02 (Forward) or Op 03                             | 4-54           |         |                                               | 6-1                 |

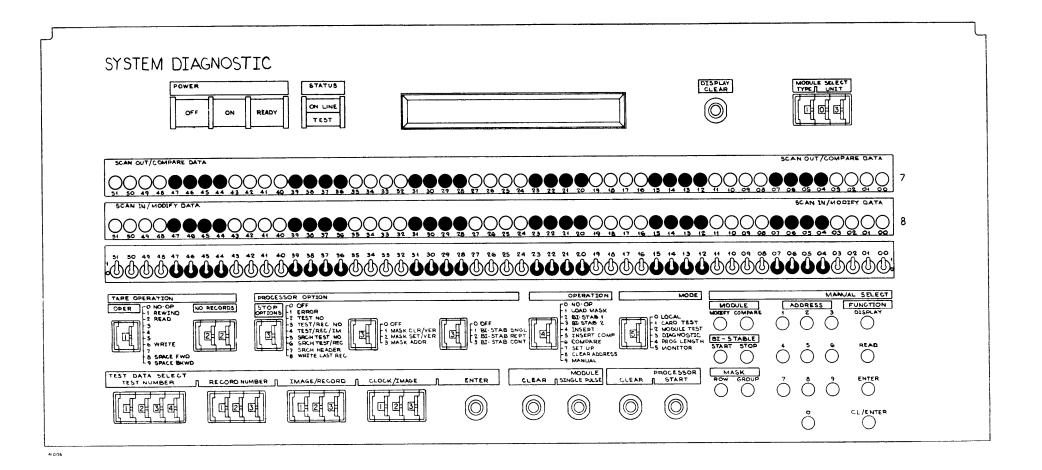

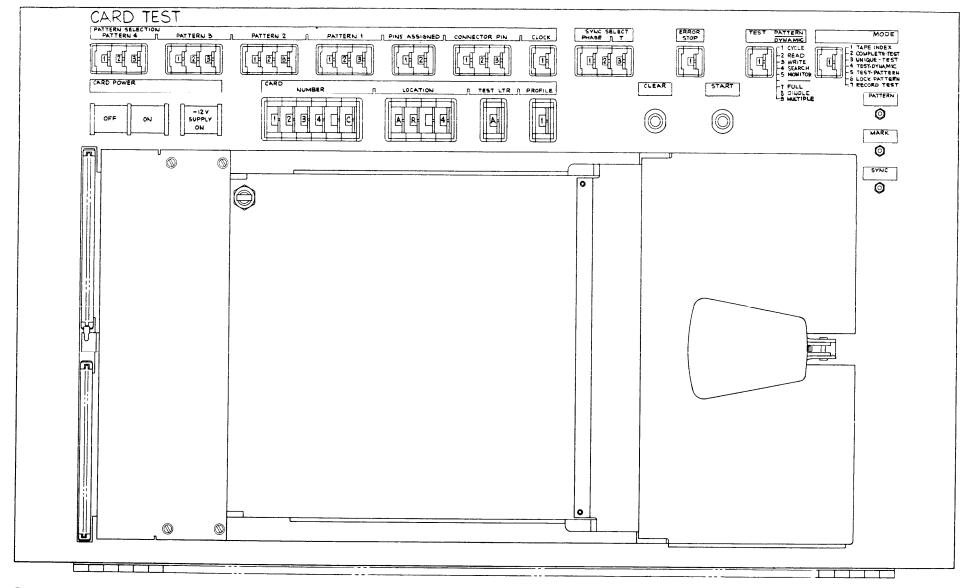

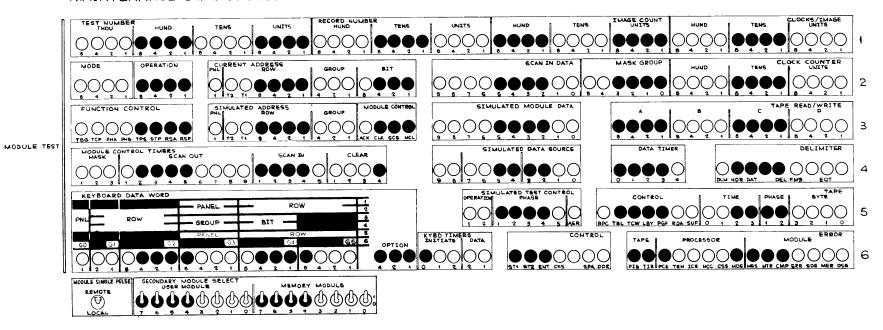

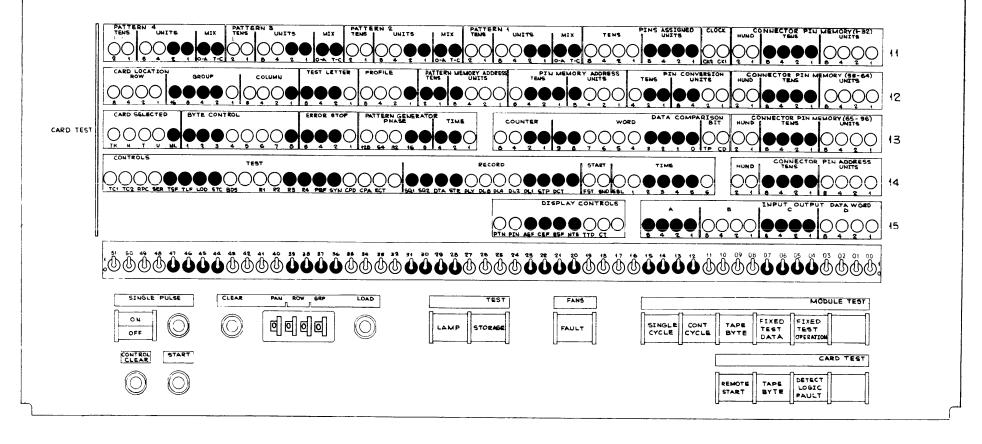

|         | (Reverse)                                                 |                |         | Section 1 - Operating Controls                |                     |

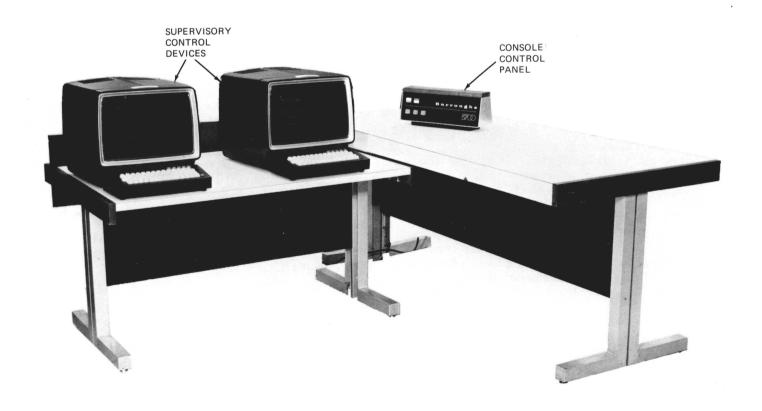

|         | Erase (Op 04)                                             | 4-54           |         | Introduction                                  | 6-1                 |

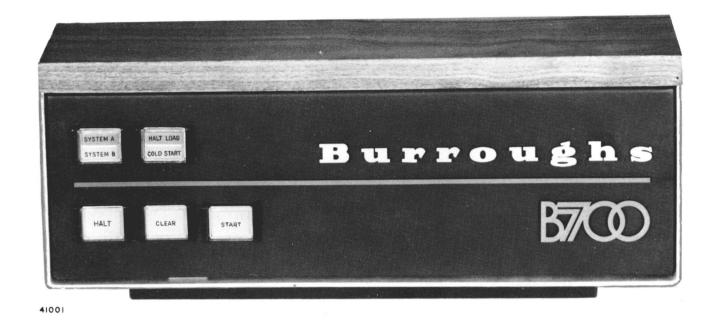

|         | Write (Op 06)                                             | 4-54           |         | Console Control Panel                         | 6-1                 |

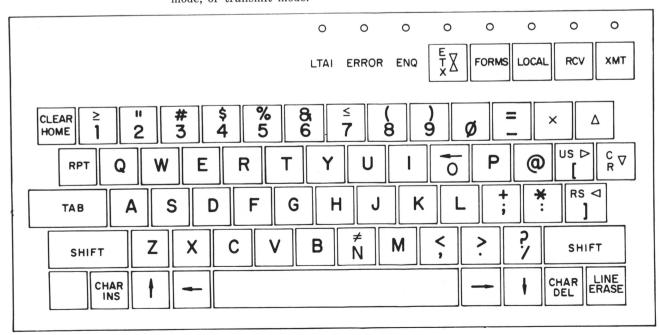

|         | Write Tape Mark (Op 06)                                   | 4-54           |         | Supervisory Console                           | $\frac{6-2}{6-3}$   |

|         | Space (Op 08 (Forward): Op 09                             | 4-54           |         | Keyboard Control Keys                         | 6-5                 |

|         | (Reverse)                                                 |                |         | Disk Load/Card Load                           |                     |

|         | Test (Op 99)                                              | 4-54           |         | Section 2 - Central Processor Module          | 6-6                 |

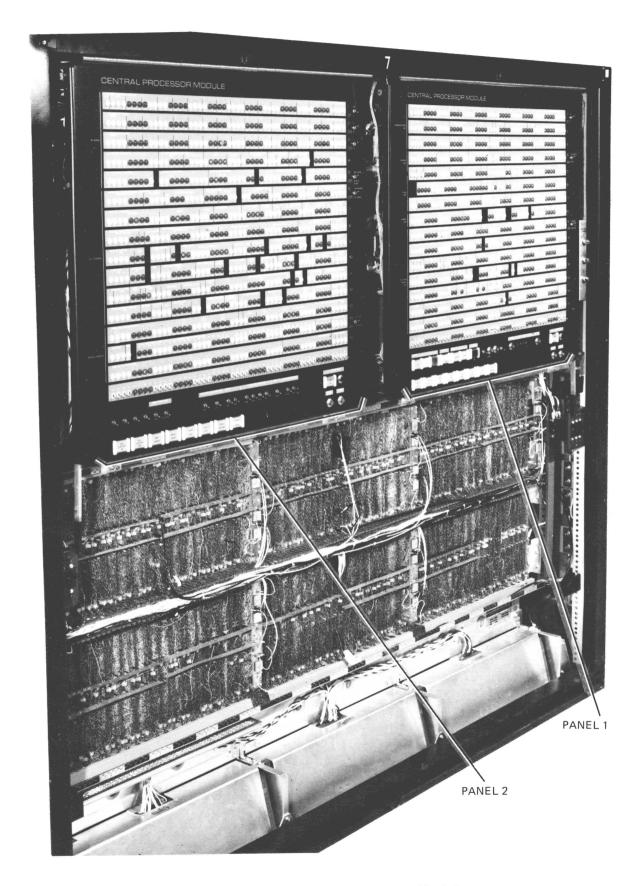

|         | BCL Alpha Operation (7-Track Tape                         | 4-54           |         | Panels                                        |                     |

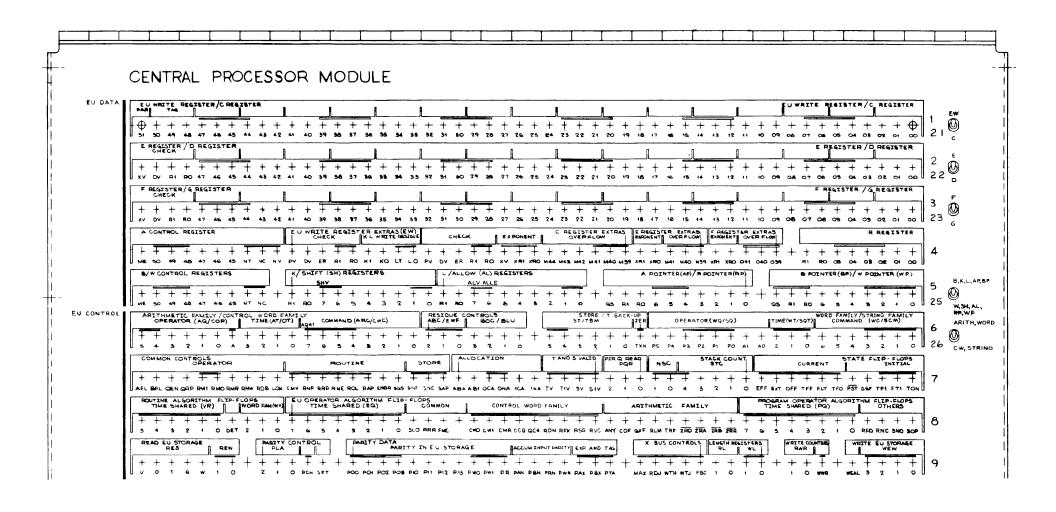

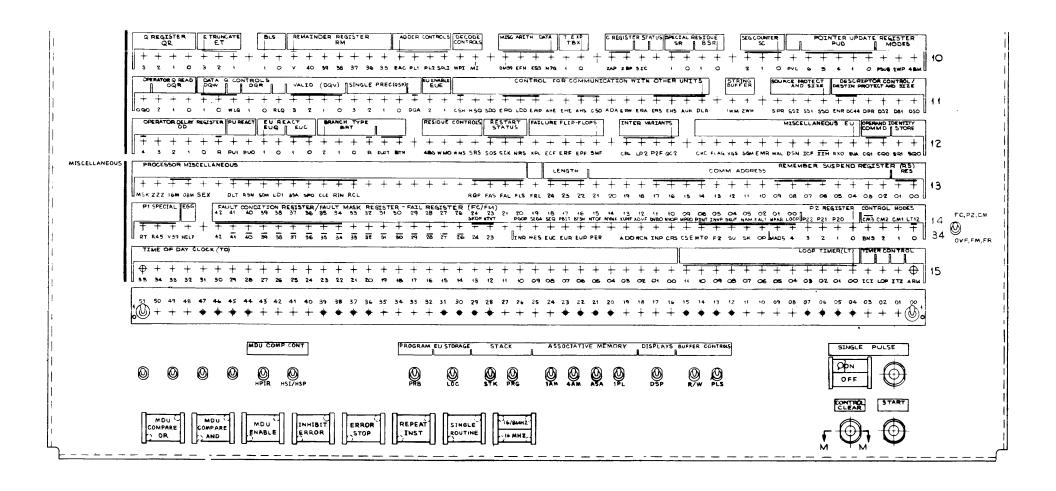

|         | with Even Parity)                                         | 4-54           |         | Display Organization                          | 6-6                 |

|         | Exception Conditions                                      | 4-54<br>4-54   |         | Panel 2 Indicators (Left-Hand Panel)          | 6-6                 |

|         | CRC Correction (9-Track, 800 BPI                          | 4-04           |         | EU Data Section                               | 6-6                 |

|         | Only)                                                     | 4-54           |         | Row 1 - Row 21 Display Selection              | 6-6                 |

|         | Paper Tape Punch paper Tape Punch Control                 | 4-54           |         | EU Control Section                            | 6-14                |

|         | Write (Op 48)                                             | 4-55           |         | String Family                                 | 6-15                |

|         | Punch Leader (Op 49)                                      | 4-55           |         | Arithmetic Family                             | 6-17                |

|         | Text (Op 99)                                              | 4-55           |         | Panel 2 Switches (Left-Hand Panel)            | 6-22                |

|         | Exception Conditions                                      | 4-55           |         | Panel 1 Indicators (Right Panel)              | $6-23 \\ 6-23$      |

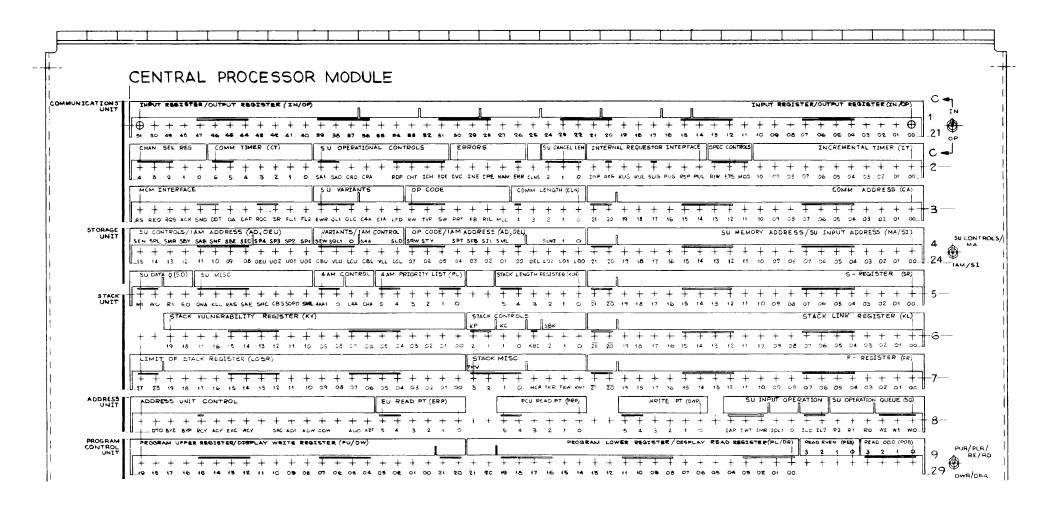

|         | Paper Tape Reader                                         | 4-55           |         | Communications Unit                           | 6-25                |

|         | Paper Tape Reader Control                                 | 4-55           |         | Storage and Stack Units                       | 6-26                |

|         | Read (Op 40)                                              | 4-56           |         | Address Unit<br>Program Control Unit          | 6-26                |

|         | Space Forward (Op 41)                                     | 4-56           |         | Trogram Control Cint                          |                     |

|         |                                                           |                |         |                                               |                     |

| Chapter | Title                                                                      | Page                 | Chapter       | Title                                     | Page  |

|---------|----------------------------------------------------------------------------|----------------------|---------------|-------------------------------------------|-------|

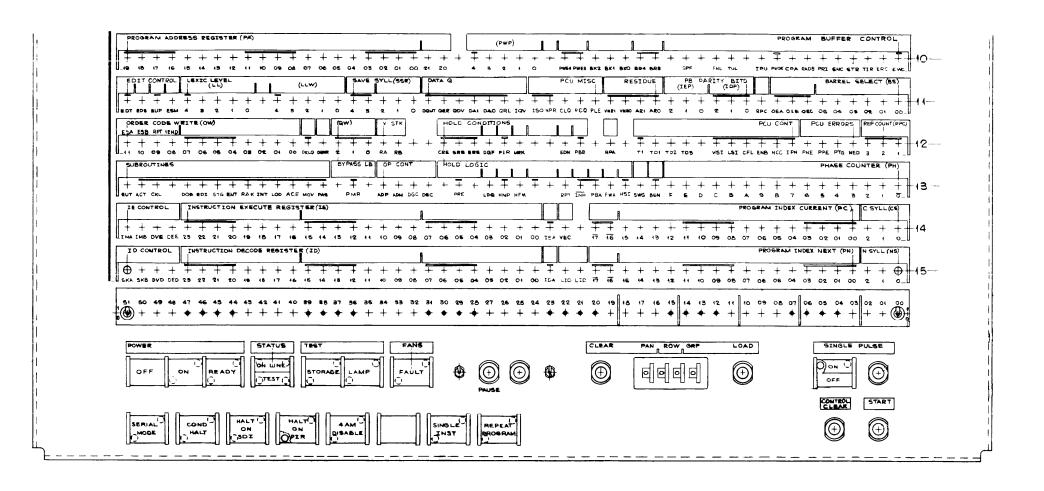

|         | Panel 1 Switches (Right Hand Panel)<br>Lamp Test                           | 6-30<br>6-31         | APPENDIX<br>B | HEXADECIMAL ADDITION TABLE                | Е В-1 |

|         | Panel Operations Storage Test Program Buffer Operation                     | 6-31<br>6-32<br>6-33 | APPENDIX<br>C | HEXADECIMAL TO DECIMAL CONVERSION TABLES  | C-1   |

|         | Stack Buffer Operation Display Buffer Operation EU Local Storage Operation | 6-34<br>6-34<br>6-35 | APPENDIX<br>D | DECIMAL - HEXADECIMAL<br>CONVERSION TABLE | D-1   |

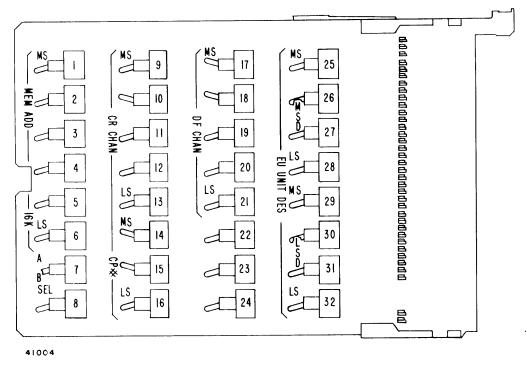

|         | Section 3 - Input/Output Module<br>Panels                                  | 6-36                 | APPENDIX      | COLLATING INFORMATION                     | E-1   |

|         | Section 4 - Memory Control Module                                          | 6-40                 | E             | DAMA DEDDEGRAM MARKET                     |       |

|         | Rows 1 through 12<br>Switches and Indicators                               | $6-40 \\ 6-45$       | APPENDIX<br>F | DATA REPRESENTATION                       | F-1   |

|         | MCM Panel Operations                                                       | 6-46                 | APPENDIX<br>G | PROCESSOR OPERATORS, BY HEXADECIMAL CODE  | G-1   |

|         | Section 5 - Maintenance Diagnostic<br>Unit Panels                          | 6-48                 | APPENDIX<br>H | PROCESSOR OPERATORS BY MNEMONICS          | H-1   |

| APPEND: | IX ORDER OF MAGNITUDE CHART                                                | A-1                  | APPENDIX<br>I | IOM WORD FORMATS                          | I-1   |

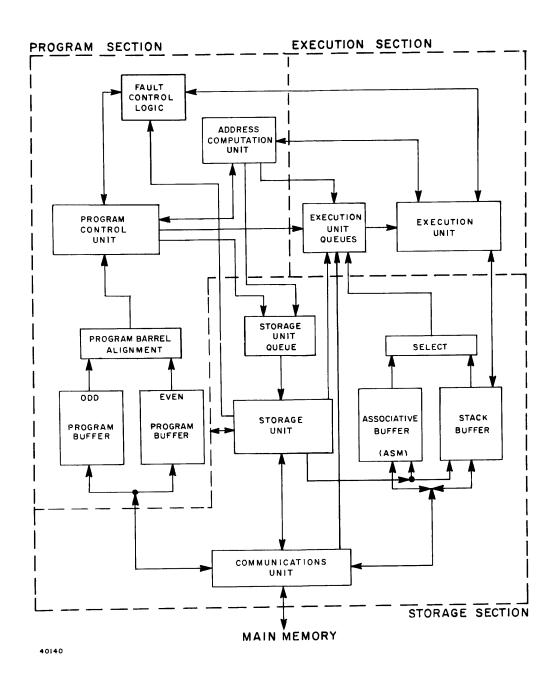

## LIST OF ILLUSTRATIONS

| Figure           | Title                                                  | Page | Figure | Title                               | Page |

|------------------|--------------------------------------------------------|------|--------|-------------------------------------|------|

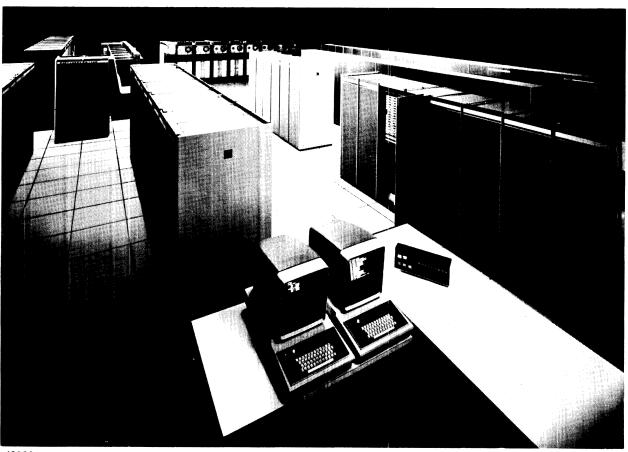

|                  | Frontispiece                                           |      |        |                                     |      |

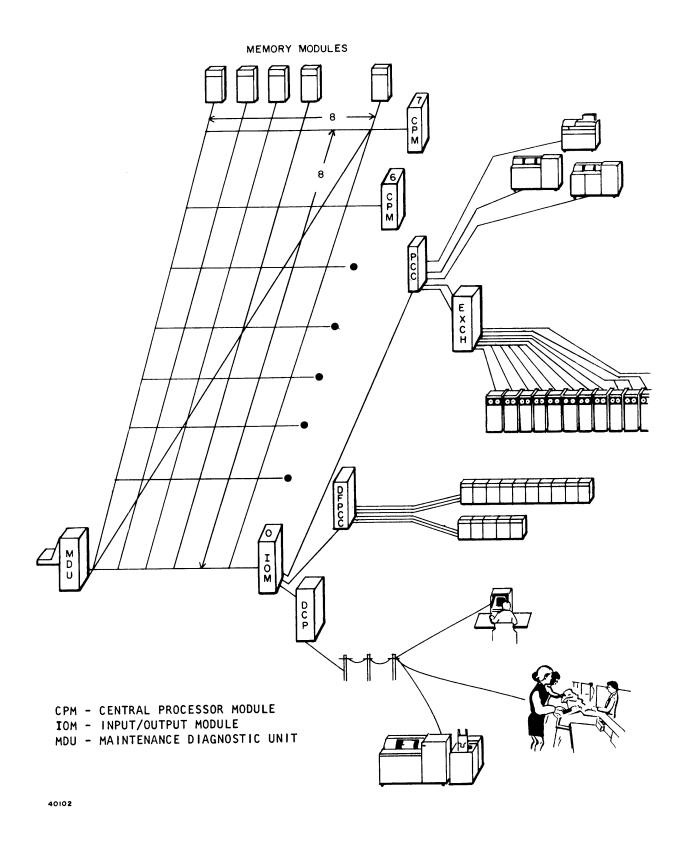

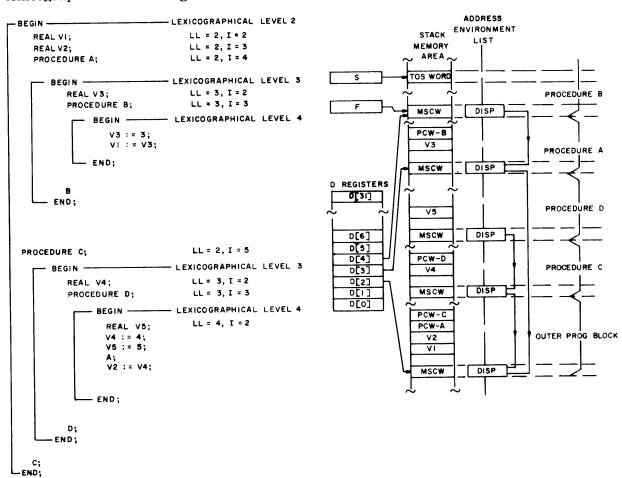

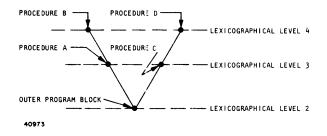

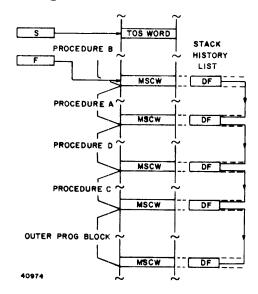

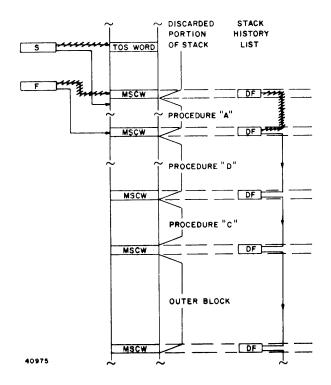

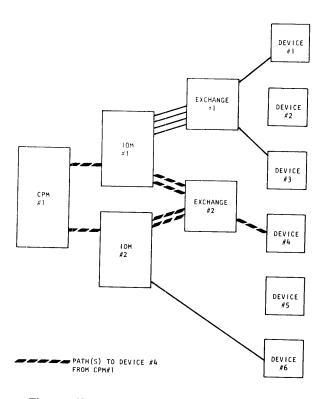

| I-1              | B 7700 Exchange                                        | 1-0  | II-2-8 | Addressing Environment Tree of      | 2-21 |

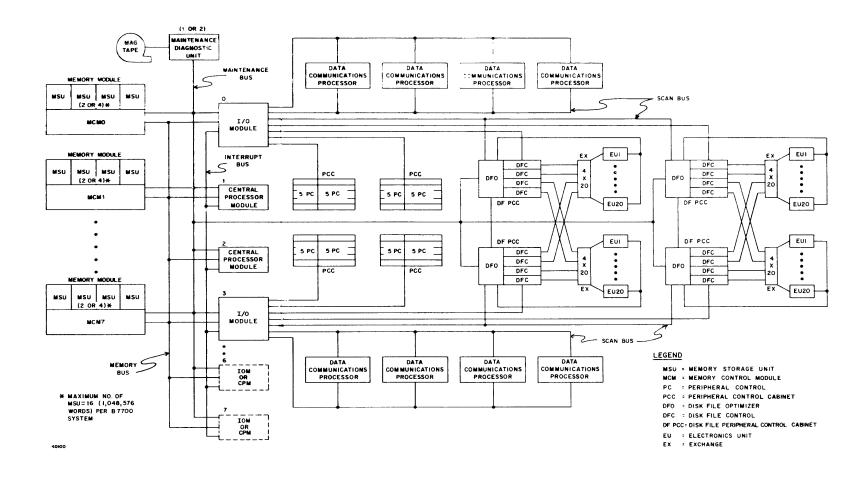

| II-2             | Maximum Configuration of the                           | 1-4  |        | ALGOL Program                       |      |

|                  | B 7700 System                                          |      | 11-2-9 | Stack History List                  | 2-21 |

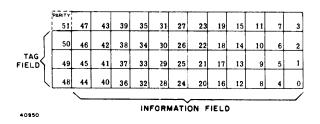

| II-1-1           | Word Structure                                         | 2-1  | II-2-  | Stack Cut Back on Procedure Exit    | 2-22 |

| II-1-2           | Number Base Graphic Characters                         | 2-1  | 10     |                                     |      |

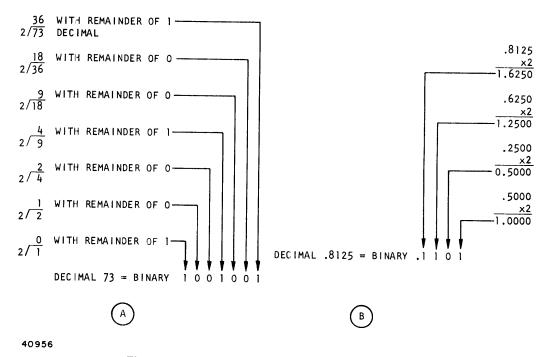

| II-1-3           | Binary Integers                                        | 2-2  | II-2-  | Stack Operation                     | 2-23 |

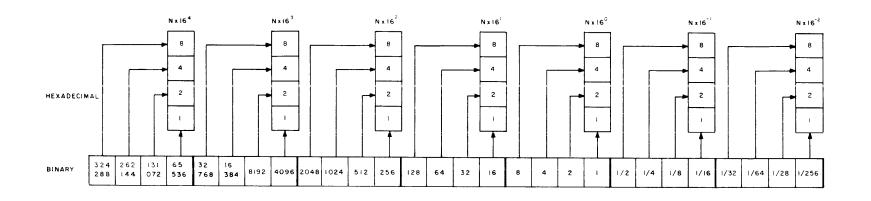

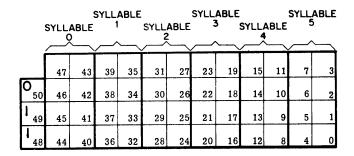

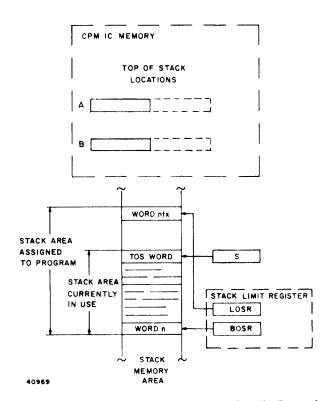

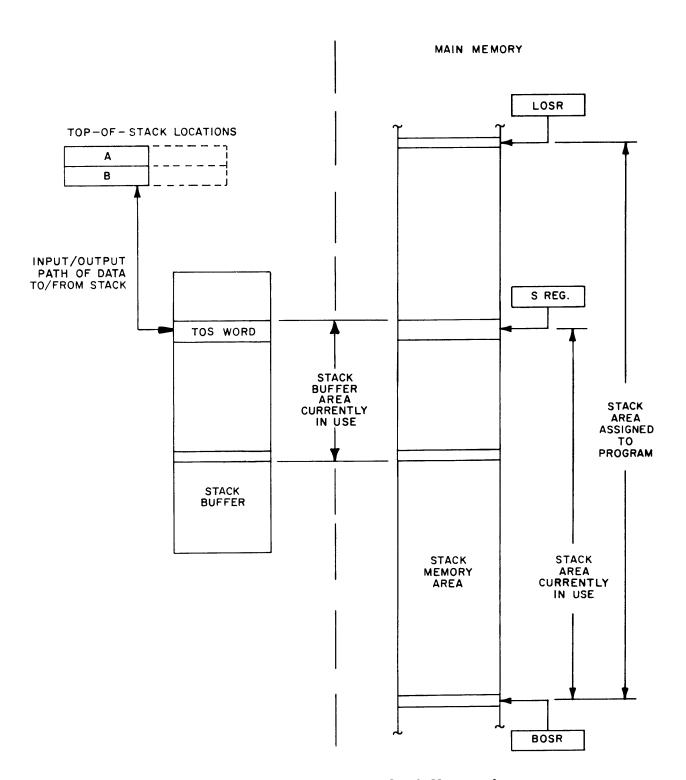

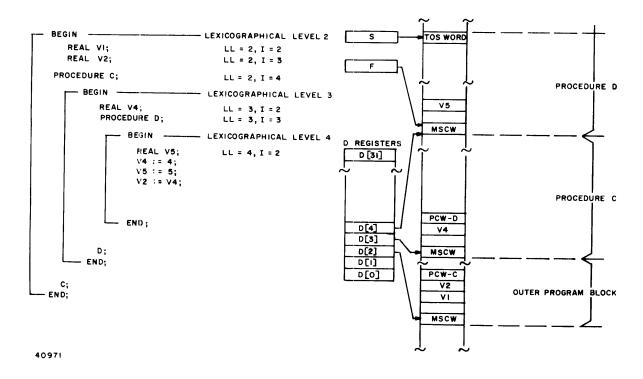

| II-1-4           | Binary to Hexadecimal and Octal                        | 2-3  | 11     | •                                   |      |

|                  | Conversion                                             |      | II-2-  | Multiple Linked Stacks              | 2-25 |

| II-1-5           | Relationship of Cctal, Decimal and                     | 2-2  | 12     | •                                   |      |

|                  | Hexadecimal Numbers                                    |      | II-3-1 | Basic Word Format                   | 2-26 |

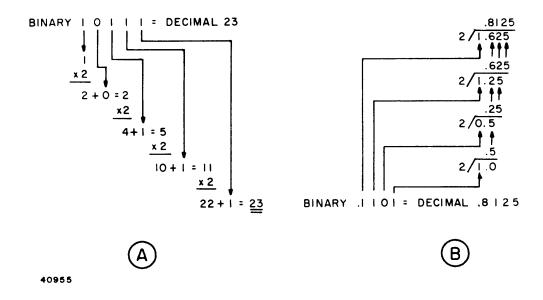

| II-1-6           | Binary to Decimal Conversion                           | 2-4  | II-3-2 | Data Descriptor                     | 2-28 |

| II-1-7           | Decimal to Binary Conversion                           | 2-5  | II-3-3 | String Descriptor                   | 2-29 |

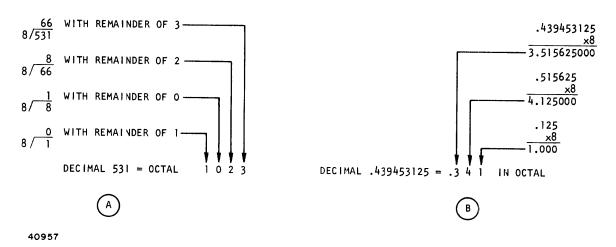

| II-1-8           | Decimal to Octal Conversion                            | 2-5  | II-3-4 | Segment Descriptor                  | 2-30 |

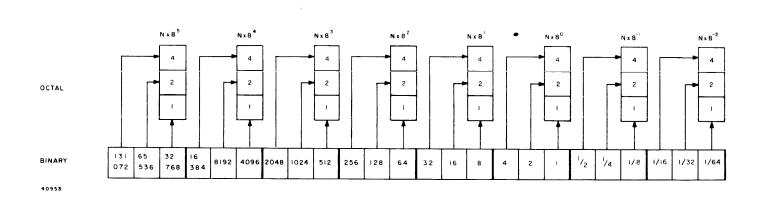

| II-1-9           | Powers of 8                                            | 2-6  | II-3-5 | Program Control Word                | 2-30 |

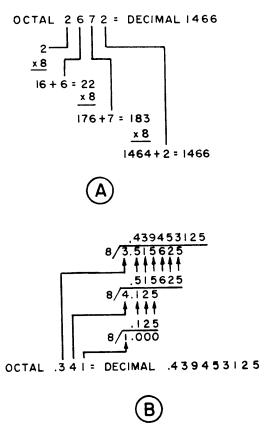

| II-1-            | Octal to Decimal Conversion                            | 2-6  | II-3-6 | Indirect Reference Word             | 2-31 |

| 10               |                                                        |      | II-3-7 | Stuffed Indirect Reference Word     | 2-32 |

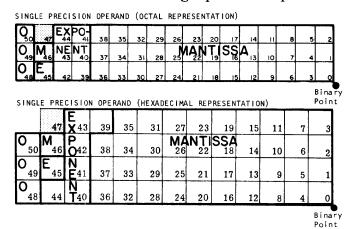

| II-1-            | Single Precision Operand                               | 2-7  | II-3-8 | Mark Stack Control Word             | 2-33 |

| 11               |                                                        |      | II-3-9 | Return Control Word                 | 2-34 |

| II-1-<br>12      | Order of Magnitude Chart                               | 2-8  | II-3-  | Top of Stack Control Word           | 2-34 |

|                  |                                                        |      | 10     |                                     |      |