# Advanced Computer Architecture Advanced Technology Apple Computer, Inc.

# Scorpius Architectural Specification Revision 1.0

Confidential and Proprietary Information of Apple Computer, Inc.

The information contained in this document is copyrighted in the name of Apple Computer, Inc., and is highly confidential and proprietary. It may only be accessed by authorized Apple employees and/or authorized Apple independent contractors on a "need to know" basis.

Unauthorized use, misuse, access, copying, or disclosure of any or all of the information contained in this document may constitute a violation of your Apple employment agreement or independent contractor's agreement and may result in termination of your employment with Apple and/or in civil or criminal liability.

By proceeding into this document, you acknowledge the copyrighted, confidential, and/or proprietary nature of the information contained in it and you agree to use the information only for the purpose for which it is intended, to maintain the confidentiality of the information, and to refrain from any and all unauthorized use, access, copying, and/or disclosure of such information.

# Scorpius Architectural Specification Contents

| Chapter | 1. Introduction                          |       |

|---------|------------------------------------------|-------|

| 1.1     | Scope                                    | 1-1   |

| 1.2     | The Scorpius CPU                         | 1-3   |

| 1.3     | Scorpius-Based Systems                   | 1-5   |

| 1.4     | Parallel Execution                       |       |

| 1.5     | Notation and Terms                       |       |

| Chapter | 2. CPU Organization                      |       |

| 2.1     | Introduction                             | . 2-1 |

| 2.2     | Data and Address Formats                 |       |

| 2.3     | Programming Model                        |       |

|         | General Registers                        |       |

|         | Program Counters                         | . 2-4 |

|         | Status Registers                         | . 2-6 |

|         | Special Registers                        | . 2-6 |

|         | • Caches                                 | 2-13  |

| 2.4     | Instruction Set Overview                 | 2-13  |

|         | Addressing Modes                         |       |

|         | • Load, Store, and Move Instructions     |       |

|         | — Delayed Loads                          |       |

|         | Branch, Compare, and Jump Instructions   | 2-16  |

|         | — Delayed Branches                       |       |

|         | Logical and Shift Instructions           |       |

|         | Field Manipulation Instructions          |       |

|         | Arithmetic Instructions                  |       |

|         | Broadcast and Semaphore Instructions     |       |

|         | Cache Control Instructions               |       |

| 2.5     | Prefixing                                | 2-22  |

|         | Immediate Prefixing                      |       |

|         | Displacement Prefixing                   |       |

|         | Field Manipulation Instruction Prefixing |       |

|             | Branch Displacement Prefixing                       | 2-26 |

|-------------|-----------------------------------------------------|------|

| 2.6         | Condition Codes                                     | 2-26 |

| 2.5         | Multi-Gauge Arithmetic                              | 2-29 |

| Chapter     | 3. Addressing                                       |      |

| 3.1         | Introduction                                        | 3-1  |

| 3.2         | Address Space Organization                          |      |

|             | Access Privileges                                   |      |

|             | • Inter-Node Messaging Via Interrupt-on-Write Pages | 3-4  |

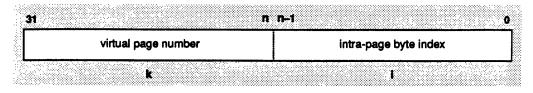

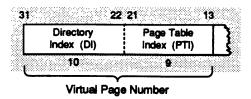

| 3.3         | Address Formats                                     | 3-6  |

|             | Virtual Addresses                                   | 3-6  |

|             | Address Arithmetic                                  | 3-6  |

|             | Real Addresses                                      | 3-6  |

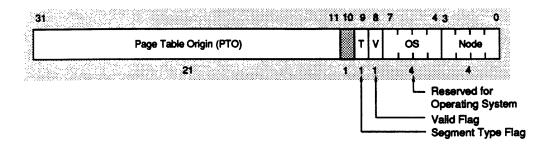

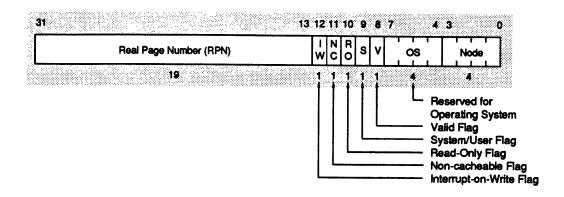

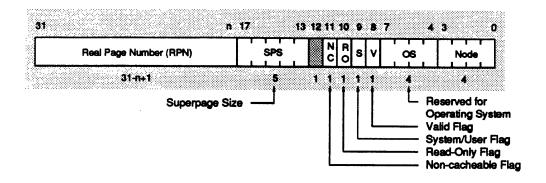

| 3.4         | Translation Tables                                  | 3-7  |

|             | Structure                                           | 3-7  |

|             | Entry Formats                                       | 3-9  |

|             | Directory                                           | 3-10 |

|             | User Region Page Table                              | 3-11 |

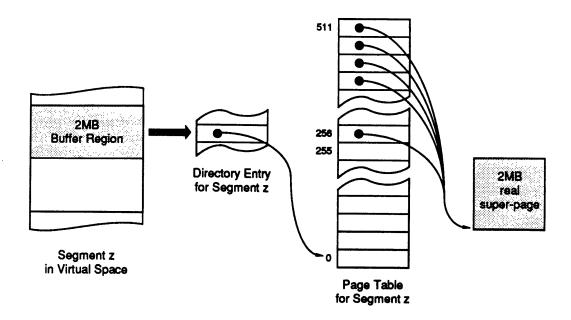

|             | Buffer Region Page Table                            | 3-13 |

|             | Page Faults                                         | 3-15 |

|             | Access Privilege Violations                         | 3-16 |

|             | Buffer Region Table Organization                    | 3-16 |

| 3.5         | Translation Table Placement                         |      |

| <b>3</b> .6 | The Translation (Lookaside) Buffer                  |      |

|             | The Antares Translation Buffer                      |      |

|             | Translation Buffer Invalidation                     |      |

|             | Translation Changes and the Cache                   |      |

|             | • Translation Changes and the Write Buffer          |      |

|             | Translation Changes and the Pipeline                | 3-21 |

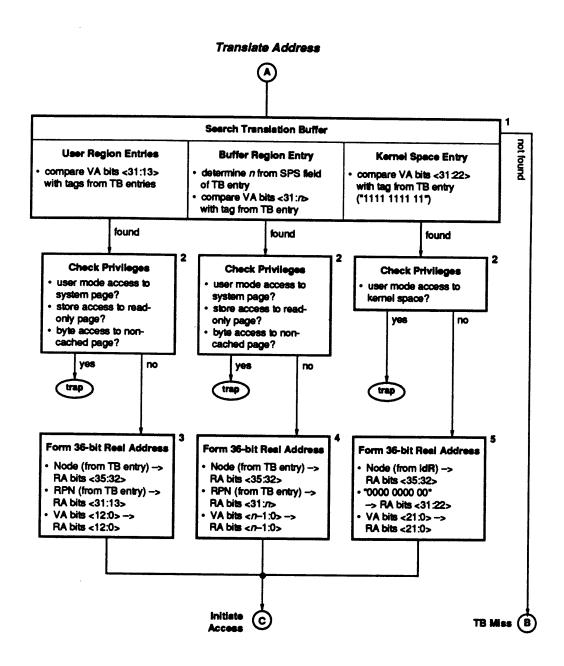

| 3.7         | Address Translation in Antares                      | 3-22 |

|             | • TB Search                                         | 3-22 |

|             | TB HIt                                              | 3-22 |

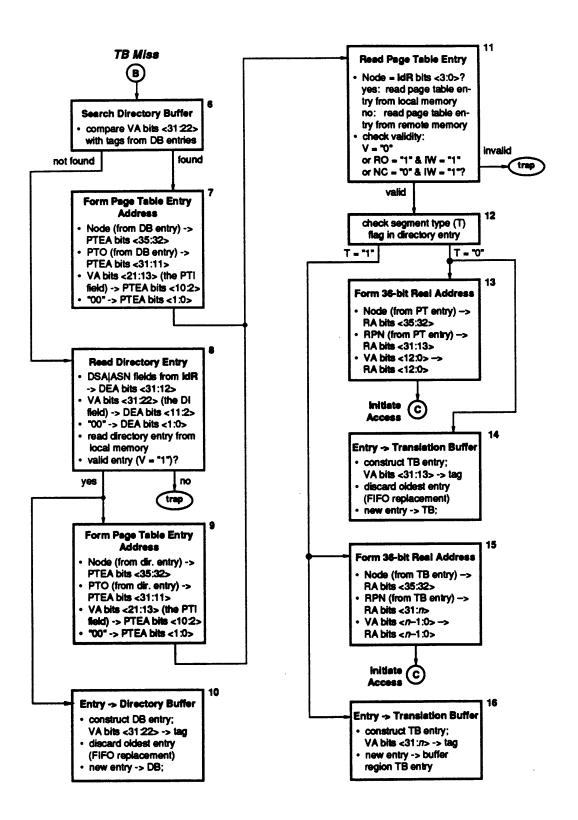

|             | • TB Miss                                           |      |

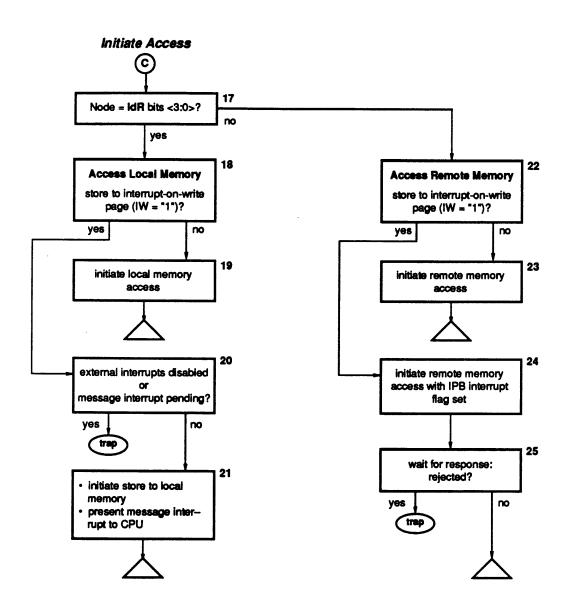

|             | Access Initiation                                   | 3-27 |

| 3.8         | Cache and TB Coherency in Antares                   | 3-28 |

|             | Cache Coherency in Single CPU Systems               |      |

|             | Cache Coherency in Multiple CPU Systems             |      |

|             | TR Coherency                                        | 3-29 |

| Chapter 4. Interrupts and Traps                                |         |

|----------------------------------------------------------------|---------|

| 4.1 Introduction                                               | 4-1     |

| 4.2 Interrupts and Traps                                       | 4-1     |

| 4.3 Interrupt Generation, Presentation,and Recognition Control | 4-4     |

| Pending Interrupt Flags     Interrupt Arguments                |         |

| 4.4 Trap Generation, Presentation,and Recognition Control      |         |

| Trap Source Flags                                              | 4-8     |

| Trap Arguments     Multiple Exception Instances                |         |

| 4.5 Interrupt/Trap Entry Addresses                             |         |

| 4.6 PU State at Interrupt/Trap Recognition                     |         |

| The PCQ Enable Flag                                            |         |

| The PU Available Flag                                          |         |

| PU State Saving                                                | 4-15    |

| PC Save Queue Access                                           |         |

| 4.7 Return From Interrupt                                      | 4-17    |

| • Return                                                       | 4-18    |

| Switch                                                         | 4-19    |

| Startup                                                        | 4-20    |

| 4.8 Interrupt/Trap Summary                                     | 4-21    |

| MachineCheck                                                   | 4-22    |

| • Power/Temp                                                   | 4-22    |

| Deadlock                                                       | 4-23    |

| • 10                                                           | 4-23    |

| Message      Front Counter Overflow                            | 4-24    |

| - Event Counter Overnow                                        | 4-24    |

| , o onon                                                       | 4-25    |

| PU Restart                                                     |         |

| PU Preempt                                                     |         |

| Data Page Fault                                                | * * * * |

| Data Access Privilege Violation                                |         |

| Message Reject                                                 |         |

| System Call                                                    |         |

| Operation Fault                                                |         |

| • Overflow                                                     | 4-30    |

| I INSTITUTION MODE FOUR                                        | 4 7 4   |

|             | Instruction Access Privilege Violation     | 4-31         |

|-------------|--------------------------------------------|--------------|

| 4.9         | Interrupt/Trap Processing in Antares       | 4-32         |

| Chapter     | 5. Inter-PU Communication & Coordination   |              |

| 5.1         | Introduction                               | 5-1          |

| 5. <i>2</i> | Broadcast Instructions                     |              |

| J.Z         | The PU Mask Field                          |              |

|             | The Wait instruction                       |              |

|             | Halt Operation                             |              |

|             | Synchronize Operation                      | 5-2          |

|             | Address Broadcasting                       | 5-3          |

|             | • Data Broadcasting                        | 5-4          |

| <i>5.3</i>  | Inter-PU Traps                             | 5-6          |

|             | Preempt                                    |              |

|             | Restart                                    | 5-7          |

| 5.4         | Semaphore Instructions                     |              |

|             | Lock and Unlock                            |              |

|             | Service Order                              |              |

|             | Applications                               |              |

| 5.4         |                                            |              |

|             | • PU States                                | 5-10         |

|             | • run state                                | 5-10         |

|             | • halt state                               | 5-10         |

|             | • wait state                               | 5-11<br>5-11 |

|             | State Change Delay      Deadlock Detection |              |

|             | - Deadlock Detection                       | J-11         |

| Chapter     | r 6. Cache Control Operations              |              |

| 6.1         | Introduction                               | . 6-1        |

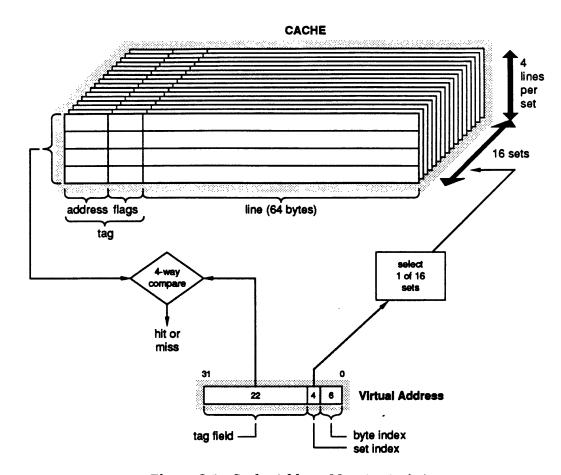

| 6.2         | Cache Organization                         | . 6-1        |

| 6.3         | Cache Line Control                         | . 6-5        |

| 6.4         | Prefetching                                | . 6-7        |

|             | Cache Invalidation in Antares              |              |

| 0.0         | Instruction Cache                          |              |

|             | Data Cache                                 |              |

| Chapter     | r 7. Measurement Facilities                |              |

| 7 4         | Introduction                               | 7- 1         |

| 7.2         | Event Counters and Their Controls                | . 7-1        |

|-------------|--------------------------------------------------|--------------|

| 7.3         | The Measurement Process                          | . 7-5        |

| Chapter     | 8. Instructions                                  |              |

| 8.1         | Introduction                                     | . 8-1        |

| 8.2         | Load, Store, and Move Instructions               | . 8-4        |

|             | Load Immediate (LdI)                             |              |

|             | Load/Store Register (LdR/StR)                    | . 8-6        |

|             | • Load/Store Register + Displacement (LdRD/StRD) | . <i>8-7</i> |

|             | Load/Store Byte (LdB/StB)                        | . 8-8        |

|             | Load/Store Multiple (LdM/StM)                    | . 8-9        |

|             | Load Condition (Lcc)                             | 8-10         |

|             | Load Carry Partial (LdCP)                        | 8-11         |

|             | Load Program Counter (LdPC)                      |              |

|             | Load PU Number (LdPU)                            |              |

|             | Move Register (Mov)                              |              |

|             | Move From/To Special (MovFS/MovTS)               | 8-13         |

| <b>8.3</b>  | Branch, Compare, and Jump Instructions           | 8-14         |

|             | Branch on Condition (Bcc)                        | 8-15         |

|             | Compare (Cmp)                                    | 8-17         |

|             | Compare Immediate (Cmpl)                         | 8-18         |

|             | Compare Partial (CmpP)                           | 8-19         |

|             | Jump Relative (Jmp)                              |              |

|             | Jump and Link (JmpL)                             | 8-21         |

|             | Jump Register (JmpR)                             |              |

|             | Test Field (TstF)                                |              |

|             | Test Mode (TstM)                                 | 8-23         |

| 8.4         | Logical and Shift Instructions                   | 8-24         |

|             | • And (And)                                      | 8-24         |

|             | And Complement (AndC)                            | 8-25         |

|             | • Not (Not)                                      | 8-25         |

|             | • Or (Or)                                        |              |

|             | Exclusive Or (Xor)                               |              |

|             | Shift Double (Dsh)                               |              |

|             | Shift Left (ShL)                                 |              |

|             | Shift Right (ShR)                                | 8-29         |

| 8. <b>5</b> | Field Manipulation Instructions                  | 8-29         |

|             | Clear/Set Field (ClrF/SetF)                      | 8-30         |

|             | Deposit (Dep)                                    | 8-31         |

|     | Extract Signed/Unsigned (ExtS/ExtU)       | 8-32 |

|-----|-------------------------------------------|------|

|     | • Insert (Ins)                            | 8-33 |

|     | Define Field (Msk)                        | 8-34 |

|     | Prefix Immediate (PfxI)                   | 8-35 |

| 8.6 | Arithmetic Instructions                   | 8-35 |

|     | Add/Subtract (Add/Sub)                    | •    |

|     | Add/Subtract with Carry (AddC/SubC)       | 8-37 |

|     | Add Immediate (AdI)                       | 8-38 |

|     | Subtract Immediate (Subl)                 | 8-39 |

|     | Add/Subtract Partial (AddP/SubP)          | 8-40 |

|     | Count Leading Zeroes (CLZ)                | 8-41 |

|     | • Divide (Div)                            | 8-42 |

|     | Divide Extended (DivE)                    | 8-43 |

|     | Divide Unsigned (DivU)                    | 8-44 |

|     | Divide Unsigned Extended (DivUE)          |      |

|     | Multiply (Mul)                            | 8-46 |

|     | Multiply Unsigned (MulU)                  | 8-46 |

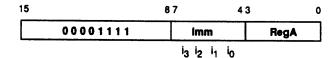

|     | Multiply Partial (MulP)                   | 8-47 |

|     | Multiply Partial Unsigned (MulPU)         | 8-48 |

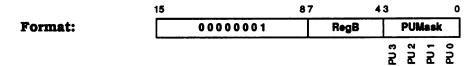

| 8.7 | Broadcast and Semaphore Instructions      | 8-49 |

|     | Receive (Rcv)                             | 8-50 |

|     | • Resume (Rsm)                            | 8-51 |

|     | • Send (Send)                             | 8-52 |

|     | • Start (Start)                           | 8-53 |

|     | • Wait (Wait)                             | 8-54 |

|     | • Lock (Lock)                             | 8-55 |

|     | Unlock (Unlk)                             | 8-55 |

| 8.8 | Cache Control Instructions                | 8-56 |

|     | Create Data Cache Line (CDC)              | 8-57 |

|     | • Flush Data Cache Line (FDC)             |      |

|     | Invalidate Data Cache Line (IDC)          |      |

|     | • Invalidate Instruction Cache Line (IIC) |      |

|     | Invalidate Instruction Cache (IICA)       |      |

|     | Read Data Tag By Index (RDTX)             |      |

|     | Update Data Cache Line (UDC)              |      |

|     | Validate Data Cache Line (VDC)            |      |

| 8.9 | Control and Miscellaneous Instructions    |      |

|     | Clear/Set Mode (CirM/SetM)                |      |

|     | Preempt (Prmpt)                           |      |

|     | • Restart (Res)                           |      |

|     |                                           |      |

| Return From Interrupt (RtI)     System Call (Trap)  |       |

|-----------------------------------------------------|-------|

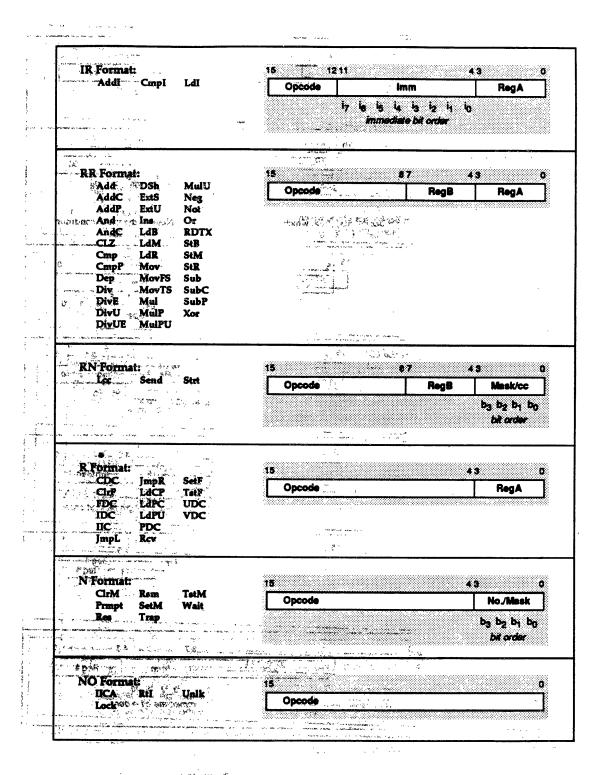

| Appendix A. Instruction Formats and Operation Codes |       |

| Basic Formats                                       | . A-2 |

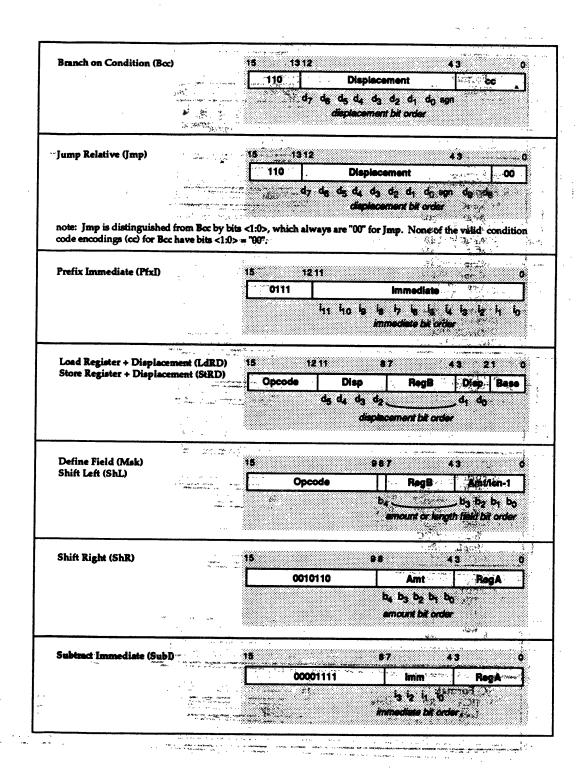

| Unique Formats                                      | . A-3 |

| Operation Codes                                     |       |

| Appendix B. Real Memory Organization in Antares     |       |

| Appendix C. Machine Reset in Antares                |       |

|   | •, |    |

|---|----|----|

|   |    |    |

|   |    |    |

|   |    |    |

|   |    |    |

|   |    |    |

|   |    |    |

| • |    |    |

|   | •  |    |

|   |    |    |

|   |    |    |

|   |    |    |

|   |    |    |

|   |    |    |

|   |    |    |

|   |    |    |

|   |    |    |

|   |    |    |

|   |    |    |

|   |    |    |

|   |    | 61 |

|   |    |    |

|   |    |    |

|   |    | ,  |

|   |    |    |

|   |    |    |

|   |    |    |

|   |    |    |

|   |    |    |

|   |    |    |

|   |    |    |

|   |    |    |

|   |    |    |

|   |    |    |

|   |    |    |

|   |    |    |

|   |    |    |

|   |    |    |

|   |    |    |

|   |    | -  |

|   |    |    |

|   |    |    |

|   |    |    |

# 1. Introduction

# 1.1 Scope

This document provides a specification of the Scorpius CPU architecture and a systems-programming-level reference for the Antares CPU, a particular implementation of the Scorpius architecture. Scorpius is a tightly-coupled multiprocessor CPU with efficient support for fine-grained parallelism; the architecture was developed to take advantage of the inter-connectivity of single-chip VLSI implementations. Scorpius is intended to be the processing element of a high-performance personal computer system constructed with a minimal number of components.

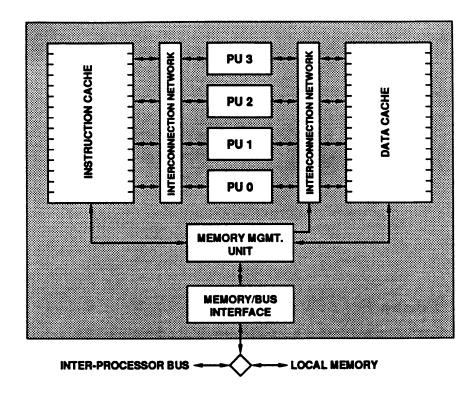

A Scorpius CPU comprises four independent processing units (PUs) which share access to separate instruction and data caches, a Memory Management Unit, and a Memory/Bus Interface. In addition to communicating through memory, PUs can communicate and can coordinate their activities via broadcast instructions, which permit one PU to send data and addresses simultaneously to other PUs and to suspend its execution until other PUs complete execution of their activities. Multiple Scorpius CPUs can be connected via an Interprocessor Bus to form a multiprocessor system in which each CPU has its own local memory which it can share with other CPUs. Support for inter-CPU messaging is provided by interrupt-on-write pages. The Interprocessor Bus also provides a means of communicating with other processors (e.g., IO processors).

This chapter gives an overview of the Scorpius CPU, briefly describes the organization of Scorpius-based systems, and introduces terms and notation used in the remainder of the document. Chapter 2 describes CPU organization and presents a programming model of the CPU. Address space organization, translation table structure, and the address translation process are described in

<sup>&</sup>lt;sup>1</sup>However, multi-chip implementations are feasible. A multi-chip prototype of the Scorpius CPU, called Venus, is currently being developed.

Figure 1.1. Major CPU Elements

Chapter 3. Chapter 4 describes interrupt and trap processing, and gives a summary description of each interrupt and trap. Inter-PU coordination and communication is effected via broadcast and semaphore instructions, which are discussed in Chapter 5. The instruction and data caches are architecturally visible in Scorpius, and instructions are provided to invalidate and flush cache lines. These and other cache control instructions are discussed in Chapter 6. Scorpius provides a pair of event counters with associated controls for use in measuring various aspects of CPU performance, such as instruction execution rates, PU utilization, and cache miss ratios. These measurement facilities are described in Chapter 7. The Scorpius instruction set is described in Chapter 8. In most chapters, descriptions of the Antares implementation are included. Also, the Antares versions of certain implementation-dependent aspects of the CPU→system interface are described in appendices.

The intent of an CPU architectural specification is to provide a description which is sufficiently complete so that different implementations of that architecture can be built, possibly by different design teams, with confidence that a program executed on any one implementation will produce identical results when executed on any other implementation. These implementations are said to be instruction-level compatible. Instruction-level compatibility is frequently, but not always, required. Sometimes it is sufficient to provide only application-level compatibility, and permit changes in operations performed

only by the operating system, so that some operating system functions become model-dependent. To help identify such functions, architectural aspects subject to change in future implementations (to the extent currently recognized) are identified in the text.

# 1.2 The Scorpius CPU

The major elements of a Scorpius CPU are shown in Figure 1.1. (The shaded region encloses those elements contained on the Antares CPU chip.) The CPU has four identical and independent processing units, or PUs; each is a 32-bit RISC (Reduced Instruction Set Computer). The four PUs access instruction and data caches via interconnection networks. In addition to providing PU cache data transfer paths, these networks provide a direct inter-PU communication path for broadcast operations and global register access, as well as a path for interrupt routing. In Antares, instruction and data caches are divided into four banks, and each network is a  $5 \times 4$  crossbar switch, permitting simultaneous instruction and data accesses by all four PUs.

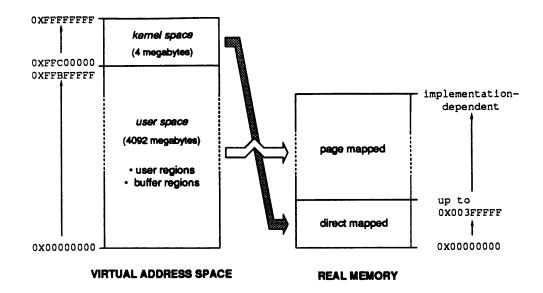

Scorpius provides a flat — unsegmented — virtual address space of 4096 megabytes (MB). A 4-megabyte area at the high end of each address space is reserved for the system kernel; the remaining 4092 megabytes, called user space, are available for the user and for other parts of the operating system. The kernel region is not paged, but instead maps directly to the first 4 megabytes of real memory. A single instance of the kernel, then, is common to all address spaces. User space is pageable. The standard page size is 8192 bytes (8KB), but it is possible to define special frame buffer regions in which space is allocated in super-page units, which can range from 256KB to 8MB.

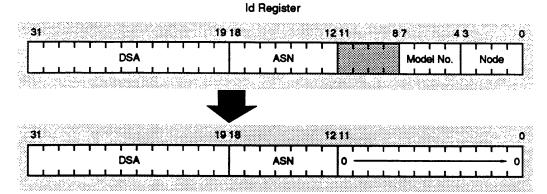

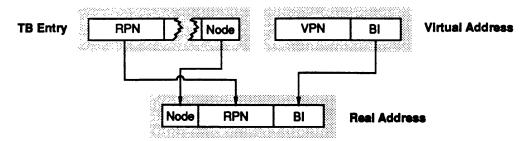

An address space is defined by a set of virtual-to-real page mappings which are recorded in a translation table. Each address space has its own translation table. At any instant, only one address space can be active on a CPU; the four PUs always execute in the same address space. A global register holds a pointer to the start of the translation table for the currently-active address space. Translation table have a simple, two-level structure, composed of a first-level directory and one or more second-level page tables. In addition to virtual-real mappings, translation table entries identify pages as system, read-only, non-cacheable, or interrupt-on-write.

Translation of virtual addresses to real addresses is done by the Memory Management Unit (MMU) using mappings obtained from translation table entries. To avoid reading directory and page table entries on every translation, the MMU maintains the most recently used mappings in a Translation Buffer. Antares has virtually-addressed caches; address translation is required only on a cache miss or on an access to a non-cached page. (The Antares MMU also maintains the CPU's global registers.) A 32-bit virtual address translates into a 36-bit real address, comprising a 4-bit node number and a 32-bit intra-node address. A node number identifies a position on the Inter-Processor Bus (IPB); the node at which a particular real page resides is said to be the *owner* of that page. On a cache miss or a non-cached memory access, the MMU sends a

memory access request to the Memory/Bus Interface (MBI), which examines the node number of the real address accompanying the request. If the node number is the same as that of the CPU generating the request, then the request is directed to local memory; otherwise, the request is sent to the specified node, or remote memory, via the IPB.

Pages (other than super-pages) can be marked "interrupt-on-write". A store to an interrupt-on-write page causes a message interrupt to be presented to the node owning that page when the store is performed. The interrupt-on-write page can reside in either local or remote memory, and must also be non-cacheable. Interrupt-on-write pages provide a mechanism for transmitting messages between nodes and for coordinating activities of different nodes.

When a CPU receives a message interrupt or an external interrupt (such as an IO interrupt), it examines the status of its four PUs. If one of the PUs is halted, it is assigned to process the interrupt; only if all four PUs are busy is it necessary to actually interrupt PU execution. Interrupt processing, then, frequently can be done in parallel with application execution. Each PU has a flag which indicates if its state must be saved on interrupt. If a PU sets this flag prior to halting, state saving overhead on interrupt processing can be eliminated.

**PUs.** Scorpius PUs have a small register-oriented instruction set in which all data access to memory is done by register load and store instructions. (Register and word size is 32 bits.) Each PU has 16 general-purpose registers — a total of 64 for the CPU — and 7 local registers. Local registers include product, remainder, prefix, and various state saving registers. In addition, the four PUs share 8 global registers, including interrupt, event counter, and global status registers.

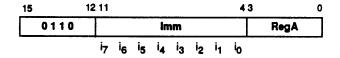

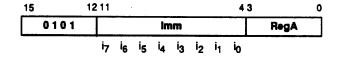

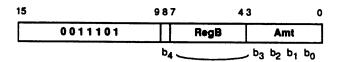

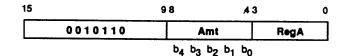

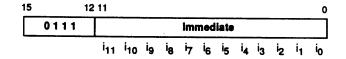

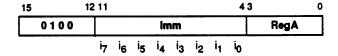

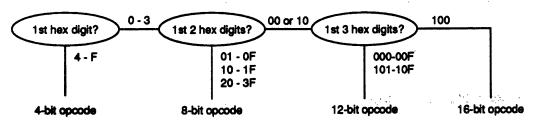

All Scorpius instructions are 16 bits in length. Instructions are tightly encoded, with operation code lengths generally reflecting the number of operands (zero, one, or two). There are only two address modes: register, and base plus displacement. Base plus displacement addressing provides a displacement of up to 64 words from the base register address, with the base register limited to registers 0–3. However, prefixing can be used to increase the displacement range, transform register addressing into base plus displacement addressing (with any register as base), and provide signed displacements.

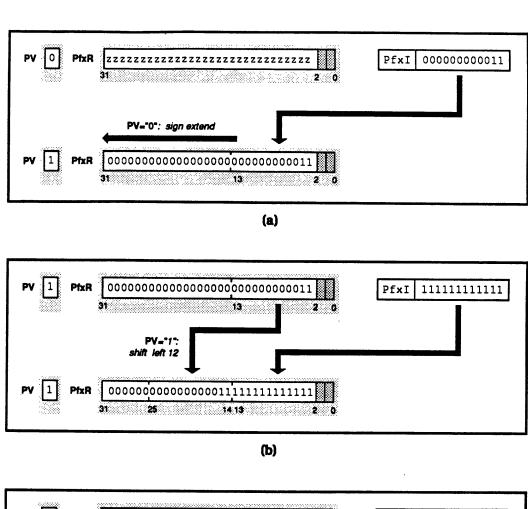

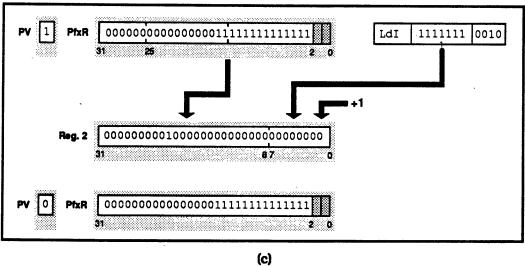

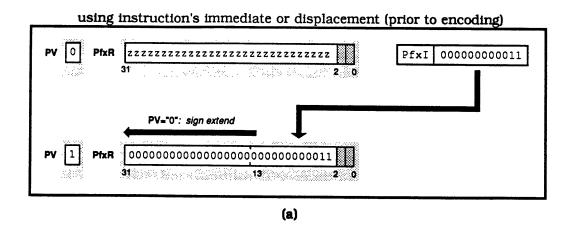

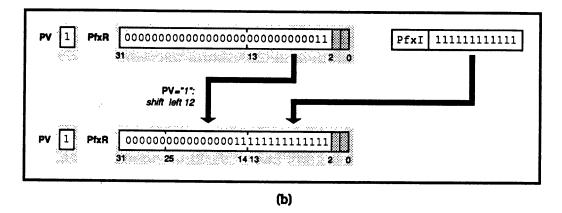

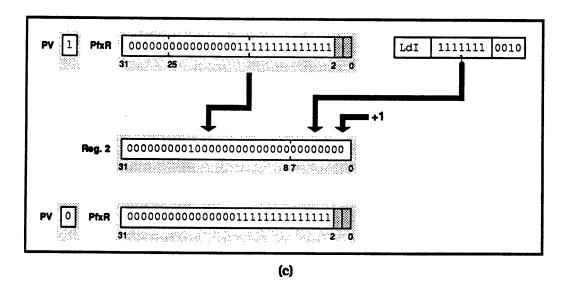

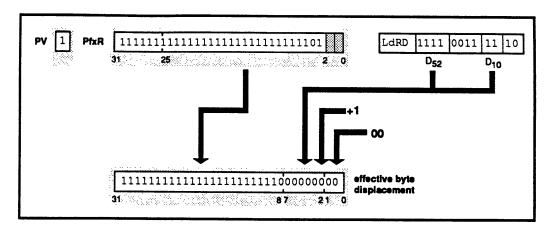

The 16-bit instruction length limits the size of immediate and displacement fields in Scorpius instructions. However, a large proportion of immediate and displacement values encountered in programs are small enough to be contained in these fields. When necessary, larger values can be created by prefixing the immediate or displacement field value. Each PU has a local register called the Prefix Register, whose state (empty or not empty) is represented by a Prefix Valid flag. Values are loaded into the Prefix Register by a Prefix instruction. If the Prefix Register is empty when a Prefix instruction is executed, the immediate field of the Prefix instruction is stored in the low-order bits of the Prefix Register and sign extended, and the Prefix Valid flag set to not empty. If a second Prefix instruction then is executed, the contents of the Prefix Register are shifted left and the immediate field of the second Prefix instruction stored in the low-

order bits of the Prefix Register. When a instruction with a prefixable immediate or displacement is executed, the Prefix Valid flag is examined. If the Prefix Register is not empty, the contents of the Prefix Register are concatenated with the instruction's immediate or displacement field to form the effective immediate or displacement value. Prefixing also is used to define fields for field manipulation instructions.

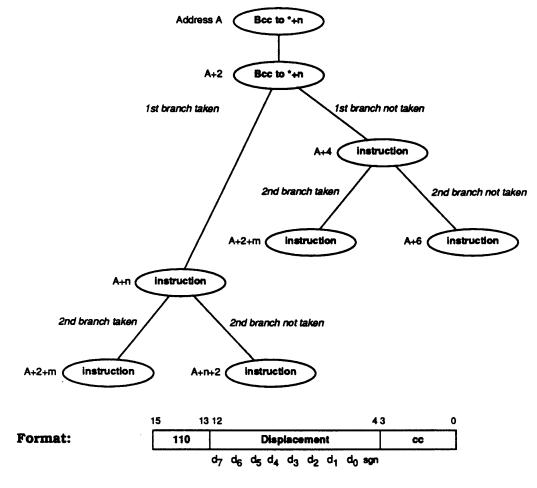

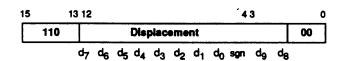

Like many RISCs, the Scorpius PU has delayed branching. The instruction immediately following a branch, called the branch shadow instruction, always is executed, regardless of whether or not the branch is taken. In many implementations, this eliminates the delay which otherwise would result from a a taken branch; compilers usually can move a useful instruction into the branch shadow. Implementations of Scorpius also may have delayed loads. The value loaded from memory into a register by a load instruction may not be immediately available; if the instruction following the load attempts to use that value, it may be delayed. While this is of concern from a performance viewpoint, it is not a functional concern; all implementations provide the necessary interlocks to insure that using instruction does not execute until the register load completes.

Other important aspects of the Scorpius instruction set include the following:

- load byte and store byte instructions with auto-incrementing to speed string handling;

- load and store multiple instructions with auto-incrementing on load and auto-decrementing on store to facilitate register saving and restoring on procedure calls;

- multi-gauge arithmetic instructions which operate simultaneously on both half-words or all four bytes of a word (depending on the mode selected), for high-performance graphics;

- extract, insert, deposit, and double shift instructions to aid in bit field manipulation;

- cache control instructions, including cache line prefetch, flush and invalidate; and

- broadcast instructions, which a PUs uses to send data (or an address) simultaneously to to other PUs, and to suspend its execution until other PUs complete execution of parallel activities.

In Antares, multiply and divide are asynchronous operations which can be overlapped by other instructions.

# 1.3 Scorpius-Based Systems

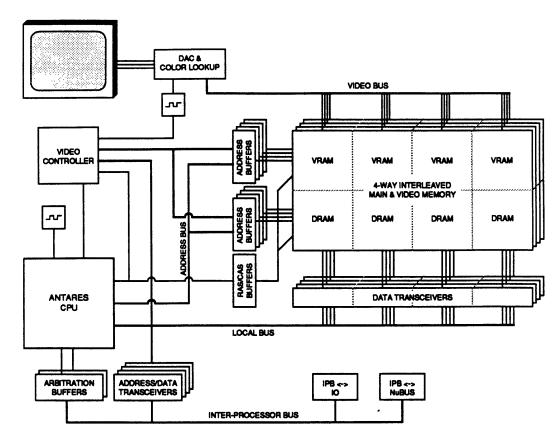

With Antares and other single-chip implementations of the Scorpius CPU architecture, systems can be constructed using relatively few components. Figure 1.2 shows the major components of a single-CPU system using the

Figure 1.2. Single-CPU System Components

Antares CPU. Because of the parallel processing capabilities of the CPU, and its multi-gauge arithmetic, no separate graphics processor is required. Incorporation of RAM, ROM, and bus control into the Antares CPU chip further reduces the number of components. In this system, memory is four-way interleaved so that data transfers between CPU and memory take place at a maximum rate of one word per cycle. Note that memory is composed of both dynamic and video RAMs. A frame buffer region is created using a single superpage allocated in that part of real memory composed of video RAMs, a screen image is created in the buffer by the CPU using normal load and store operations, and the image then written to the screen over the video bus.

The system of Figure 1.2 can be extended into a multi-CPU system by connecting additional CPUs, each with its own local memory and IPB interface, to the IPB. Sixteen nodes can be directly addressed on the IPB; additional notes can be added via gateways. In a typical multi-CPU system, one CPU will provide the video interface and have its local memory constructed of both VRAMs and DRAMS; the remaining CPUs will have local memory constructed of only DRAMS. However, it is possible that very high performance graphics systems may be developed in which, for example, four CPUs share screen display responsibilities, each operating on a quarter of the screen.

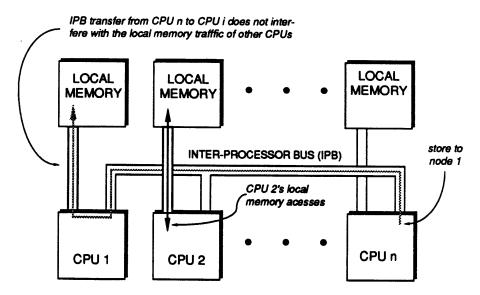

Figure 1.3. Multi-CPU System

A Scorpius virtual address translates into a real address comprising a node number and a intra-node address, so any CPU in a multi-CPU system can share pages with any other CPU in that system. However, the system organization is different from that of a conventional shared memory multiprocessor in which all processors access the same real memory; the operating system model appropriate for the shared memory multiprocessor may be inappropriate for a Scorpius-based multi-CPU system. (From the operating system viewpoint, a Scorpius-based system perhaps should be considered as a form of distributed system.)

In the shared memory multiprocessor, all processors compete for memory access (often by competing for a memory bus), and all memory accesses have the same expected delay. In most Scorpius-based multi-CPU systems, access to local memory is independent of the IPB and is not delayed by IPB activity involving other CPUs, as illustrated in Figure 1.2. Also, depending on implementation, IPB transfers may have greater latency and possibly a lower transfer rate than local memory transfers so that, even in the absence of conflicts, an IPB transfer may take longer than a local memory transfer. Thus, frequently-accesses pages should be located in local memory. Depending on the number of accesses to a shared page, it can be more efficient to copy it from remote memory to local memory before accessing it rather than to access it over the IPB.

Inter-CPU communication in a Scorpius-based system is based on interrupt-on-write pages; various message passing schemes can be implemented using the interrupt-on-write mechanism and shared pages. (The interrupt-on-write mechanism is the only mechanism provided for synchronization of multiple CPUs.) Because of the differences between a Scorpius-based system and a conventional shared-memory multiprocessor, Scorpius, as currently defined, does not incorporate cache coherence in hardware.

Figure 1.3(a). SIMD Mode Execution

Figure 1.3(b). MISD Mode Execution

Figure 1.3(c). MIMD Mode Execution

#### 1.4 Parallel Execution

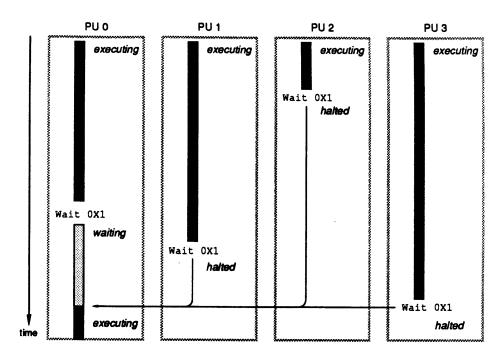

Scorpius programs can execute in any of several parallel modes. These are categorized using (with some liberties) the taxonomy developed by Flynn (Flynn, M. J. Some Computer Organizations and Their Effectiveness. *IEEE Trans. on Computers 21*, 9 (Sept. 1972), pp948-960). These modes are referred to by acronym in later chapters, and are described below.

SISD (Single Instruction stream, Single Data stream). This mode corresponds to uni-, or serial, processing; only one PU executes. Scorpius programs typically alternate between intervals of serial and of parallel processing. A single PU initiates (and usually participates in) a set of parallel computation activities, and, upon activity completion, may accumulate the results.

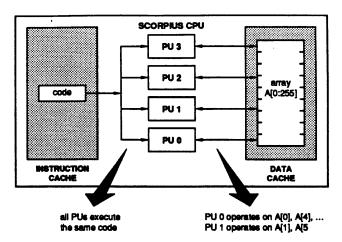

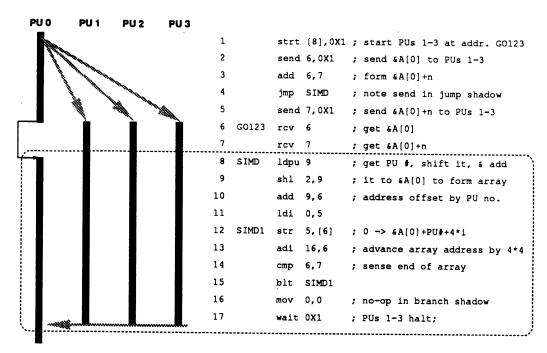

SIMD (Single Instruction stream, Multiple Data streams). This mode corresponds to the usual view of parallel processing: each PU executes the same operation on different data streams, as illustrated in Figure 1.3(a), or on different elements of the same data stream. Data access may be ordered or random. In ordered access, inter-PU coordination is implicit, as when each PU operates on every fourth element of a vector. In random access, explicit inter-PU coordination is required, as when PUs operate concurrently on a linked list or take work from a queue. Coordination in this case can be effected through the use of semaphore instructions. This is the easiest form of parallelism to exploit, either with assembly code or by a compiler. For example, the compiler may be able to "unwind" a loop which operates on an array to run on four PUs, with each PU operating on every fourth array element. Optimal performance is easily obtained, since all PUs are doing the same work.<sup>2</sup>

As an example of **SIMD** mode execution, consider the common graphics transformation operation (used in scaling, rotation, and translation) which involves the  $1 \times 4$  matrix multiplication

where

$[x \ y \ x \ w] = original coordinate set,$

[x\* y\* z\* w\*] = transformed coordinate set,

and the

$c_{ij}$  are fixed (pre-computed) for any given transformation. (For any particular transformation, some of the  $c_{ij}$  are known to be 0 or 1.)

<sup>&</sup>lt;sup>2</sup>In Antares, having each PU operate on every fourth element of a one-dimensional array eliminates data cache conflicts, since the Antares data cache is four-way interleaved with adjacent words located in different banks.

The matrix product can be written as

```

x^* = xc_{11} + yc_{21} + zc_{31} + wc_{41}

y^* = xc_{12} + yc_{22} + zc_{32} + wc_{42}

z^* = xc_{13} + yc_{23} + zc_{33} + wc_{43}

w^* = xc_{14} + yc_{24} + zc_{34} + wc_{44}

```

In a **SIMD** mode implementation of this transformation, PU 0 can be assigned to compute  $x^*$ , PU 1 to compute  $y^*$ , and so on. Each PU preloads its registers with the appropriate set of constants and, after each nth transformation, each PU executes a cache prefetch instruction to prefetch the next line of coordinate data. (Only one prefetch actually takes effect.) By careful scheduling of prefetch and computation operations, very high transformation rates can be realized.

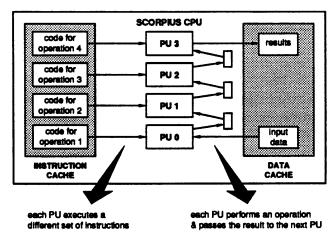

**MISD** (Multiple Instruction streams, Single Data streams). In this mode, each PU executes a different operation on the same data stream element; data is "pipelined" between PUs (Figure 1.3(b)). For example, consider the computation of

$$y_i = ax_i^3 + bx_i^2 + cx_i + d$$

which might be divided across PUs as follows. (It is assumed that a, b, c, and d are constants and are preloaded into registers of the appropriate PUs.)

- PU 0: load and send x<sub>i</sub>, compute and send cx<sub>i</sub> + d

- PU 1: compute and send x<sub>i</sub><sup>2</sup>, bx<sub>i</sub><sup>2</sup>

- PU 2: compute  $x_i^3 = x_i(x_i^2)$ , compute and send  $ax_i^3$

- PU 3: sum intermediate results to form y<sub>i</sub> and store y<sub>i</sub>

Pipelining of intermediate results from one PU to the next can be done with data broadcast instructions, which also serve to coordinate operations. For example, PU 1 sends  $\mathbf{x_i}^2$  to PU 2 by executing a Send instruction; to receive this value, PU 2 executes a Receive instruction. If this Receive is executed before PU 1's Send, PU 2's execution is blocked until the Send is executed. Pipelining also could be done through memory, using Wait and Resume instructions for coordination.

This is a relatively difficult form of parallelism to code or for which to compile code. It is not easy to balance PU execution times to optimize performance. However, carefully crafted hand-coded MISD processing sometimes is useful in improving the performance of critical programs. One stage of the Antares graphics pipeline uses two PUs executing in SIMD mode and two PUs executing in MISD mode.

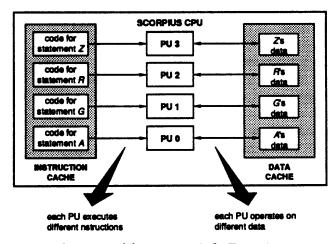

MIMD (Multiple Instruction streams, Multiple Data streams). This mode is analogous to multiprocessing: each PU executes a different and independent set of instructions which operate on different and independent data elements (Figure 1.3(c)). These might correspond to independent expressions within a single statement, to independent statements, or to certain types of procedures. It is easy to exploit this form of parallel execution at the assembly code level, and it is not too difficult for the compiler to generate MIMD code. However, it may be hard for the compiler to determine independence (because of pointers, for

example), and it also can be hard to obtain optimal performance (allocate comparable work to each PU). The independence problem is eased somewhat by compiler directives (e.g., C pragmas) which can be used to identify independent program units.

#### 1.5 Notation and Terms

This section describes notation and terms used throughout the remainder of this document. Notation used in instruction operation descriptions is used only in Chapter 8 and is described in that chapter.

numbers. Unless otherwise specified, all numbers are decimal. Hexadecimal numbers are specified using C language notation in which the hexadecimal number is prefixed by "0x" or "0X". For example, decimal 127 is written in hexadecimal as 0XFF. Bit positions in entities such as registers are indicated in brackets; bracketed numbers separated by a colon indicate a range. For example, "bits <7:0>" specifies bits 7 through 0. Single binary digit and certain multiple binary digit numbers are indicated in quotes, as in "if bit <1> = "1" ". Multi-digit binary numbers are specified by appending the letter "B". For example, decimal 15 is written in binary as 1111B. The letters K and M appended to a number indicate the multipliers 1024 and 1048576; these often appear in conjunction with the letter B, indicating that the unit of measure is bytes. Thus, 64KB, which usually is read as "64 kilobytes", specifies 65536 bytes. Similarly, 2MB usually is read as "2 megabytes" and specifies 2097152 bytes.

undefined and unpredictable operations. The operation of the CPU may be described in certain cases as undefined or as producing unpredictable results. While any given implementation may produce predictable results in such cases, different implementations may produce different results; the behavior of operations described in this way is not reliable.

|   | •. | , |

|---|----|---|

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   | •  |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    | , |

| • |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    | • |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

|   |    |   |

# 2. CPU Organization

#### 2.1 Introduction

This chapter describes the elements and organization of the Scorpius CPU. Data and address formats are described, and the programming model is presented. The programming model comprises the elements of the CPU which are visible to the programmer (i.e., can be operated on by instructions). These elements include general registers, status register and program counter, special registers, and, because the Scorpius caches are architecturally visible, the instruction and data caches. An overview of the Scorpius instruction set follows. A detailed description of prefixing, which is used to extend the range of immediate and displacement fields, is given next. Following a description of Scorpius condition codes, the chapter concludes with a discussion of the rationale for and operation of multi-gauge arithmetic.

#### 2.2 Data and Address Formats

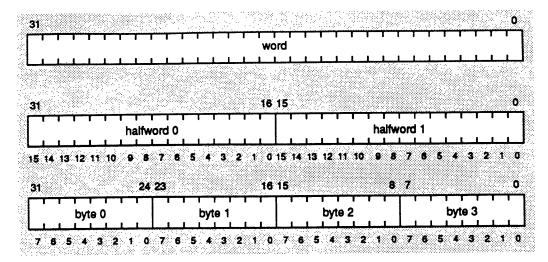

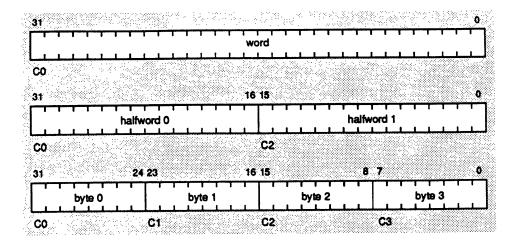

Various Scorpius instructions operate on 32-bit words, 16-bit halfwords, 8-bit bytes, and bits; instructions themselves always are a halfword in length. Only words and bytes can be directly loaded into a register from memory or stored to memory from a register; arithmetic operations can be performed on words, half-words, and bytes. The 32 bits of a word are numbered, right to left, from 0 to 31. Bit 0, the rightmost bit, is the least significant bit. Highernumbered bits often are referred to as the high-order bits, and lower-numbered bits often are referred to as the low-order bits.

Halfwords and bytes within a word are positioned as shown in Figure 2.1; this figure also shows bit ordering within halfwords and bytes. Byte 0 is the most significant (leftmost) byte, while byte 3 is the least significant (rightmost) byte. This ordering is compatible with that of Motorola 680x0 processors, and sometimes is referred to as "big-endian".

Figure 2.1. Scorpius Data Formats

Figure 2.2. Scorpius Address Format

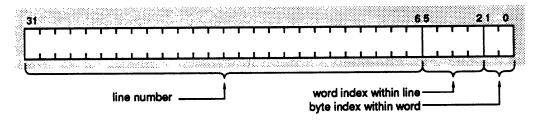

Unless otherwise specified, instructions and data are transferred between memory and the CPU in 64-byte (16-word) blocks called *lines*, which are stored in the instruction cache and data cache. (The term "line" or "cache line" tends to be used both for a physical location in a cache and for a block of 16 memory words which can be stored in that location. The intended meaning usually is clear from the context.) Scorpius instruction and data caches are architecturally visible, and instructions are provided to perform operations on cache lines including prefetch, invalidate, and flush.

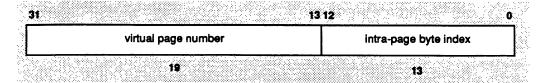

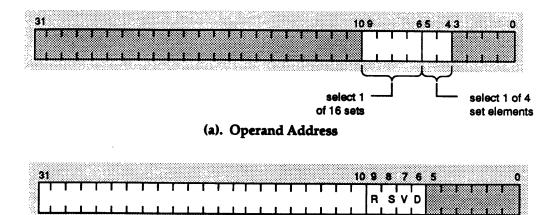

Scorpius instruction and data addresses are byte addresses, 32 bits in length, spanning a virtual address space of 4096 megabytes. (Address space organization is discussed in Chapter 3.) While all addresses are byte addresses, memory accesses for instructions and data are constrained to the appropriate boundaries. A halfword boundary is a byte address with bit <0> = "0", a word boundary is a byte address with bits <1:0> = "00", and a line boundary is a byte address with bits <5:0> ="000000". Instructions always must be aligned on a halfword boundary; the low-order bit of an instruction address is ignored. Word operands always must be aligned on word boundaries; the low-order two bits of the operand address of a load or store word instruction are ignored. Cache lines, by definition, are aligned on cache line boundaries; line transfers

Figure 2.3. Programming Model: Registers

between the CPU and memory always are done on line boundaries. The low-order six bits of the operand address of a cache control instruction are ignored.

From the viewpoint of the cache, memory comprises a set of lines numbered 0, 1, ..., 0X3FFFFFF. The mapping between these lines and the much smaller number of cache line locations is implementation-dependent. Addresses can be viewed as comprising a line number in bits <31:6>, a intra-line word index in bits <5:2>, and an intra-word byte index in bits <1:0>, as shown in Figure 2.2.

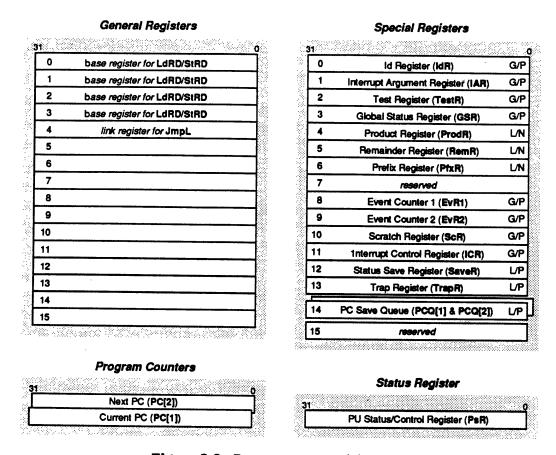

# 2.3 Programming Model

The programming model comprises the general register set, status register and program counters, the special register set, and the instruction and data caches. The various registers of the programming model are illustrated in Figure 2.3 and described below. Each PU has its own general register set, status register, and program counters; these registers are said to be *local* to the PU. Each PU also has its own copy of certain special registers, while other special registers are common to all PUs; these are called *global* registers. In Figure 2.3, local and global special registers are marked "L" and "G".

# Current PC (PC[1]) and Next PC (PC[2])

Figure 2.4. Program Counters

PUs execute in one of two modes: user mode or system mode. The current mode is determined by the setting of a flag in the PU Status/Control Register. Generally, applications execute in user mode, while the operating system kernel and other parts of the operating system execute in system mode. Execution in system mode confers certain privileges. Some special registers can be accessed only in system mode, certain instructions can be executed only in system mode, and pages marked "system only" can be accessed only in system mode. In Figure 2.3, special registers which can be accessed only in system mode are marked "P" (for privileged), while those which can be accessed in either mode are marked "N" (for non-privileged).

General Registers. Each PU has 16 32-bit general registers, numbered 0-15, so there are 64 general registers for the CPU as a whole. With two exceptions, registers are inter-changeable; any register can be used for any purpose. Registers 0-3, only, can be used as base registers for the Load/Store Register + Displacement instructions, LdRD/StRD, and register 4 is used by the Jump and Link instruction, JmpL, to store the return address. 1

Any individual general register can be loaded from memory or have its contents stored to memory via Load/Store Register + Displacement and Load/Store Register instructions. The Load Byte instruction loads the addressed byte, right-justified with zero fill, into a general register; the Store Byte instruction stores the rightmost byte of a general register to memory. From 1 to 15 registers can be loaded from memory or have their contents stored to memory via Load/Store Multiple instructions.

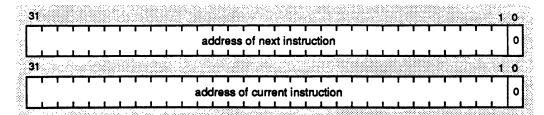

**Program Counters.** Scorpius has two program counters (PCs), called the Current PC and the Next PC. Current PC holds the address of the currently-executing instruction; Next PC holds the address of the next instruction to be executed. Two program counters are required because of delayed branching. On a taken branch or jump, Current PC holds the address of the branch shadow instruction, and the branch target address is stored in Next PC. For sequential

<sup>&</sup>lt;sup>1</sup>Using prefixing, any register can be used as a base register for base plus displacement addressing; see section 2.5.

# PU Status/Control Register (PsR)

| <i>t</i> :           | 4.4                |               | ,                                                                                                                                                                                                                          |

|----------------------|--------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| field<br><u>name</u> | bit<br>position(s) | <u>lenath</u> | docarintina                                                                                                                                                                                                                |

| Rmod                 | <31>               | 1             | Register modified flag. Set to "1" on interrupt/trap recognition if the address register of Load/Store Byte or Load/Store Multiple requires adjustment prior to return from interrupt; "0" otherwise (Section 4.6).        |

| Hlt                  | <24>               | 1             | Halt flag. Set to "1" when a PU executes a Wait instruction specifying itself as a target; cleared to "0" when another PU executes a Start or a Resume instruction with the halted PU specified as a target (Section 5.2). |

| N                    | <22>               | 1             | Negative condition code flag (Section 2.6).                                                                                                                                                                                |

| V                    | <21>               | 1             | Overflow condition code flag (Section 2.6).                                                                                                                                                                                |

| C0-C3                | <20:17>            | 4             | Carry condition code flags (Section 2.6).                                                                                                                                                                                  |

| Z                    | <16>               | 1             | Zero condition code flag (Section 2.6).                                                                                                                                                                                    |

| I/TE                 | <15>               | 1             | Interrupt/Trap Enable flag. When set to "1", enables recognition of interrupts and traps by the PU; when "0", disables interrupt/trap recognition (Sections 4.3, 4.4).                                                     |

| ВТ                   | <14>               | 1             | Taken Branch Trap enable flag. When set to "1", causes a taken branch trap to be generated whenever the PU attempts to execute a taken branch or a jump instruction; when "0", no trap is generated (Sections 4.4,4.8).    |

| U/S                  | <13>               | 1             | User/System mode flag. Set to "1" when the PU is executing in user mode and to "0" when the PU is executing is system mode.                                                                                                |

| PCQE                 | <12>               | 1             | PCQ Enable flag. When set to "1", causes PsR and PC contents to be transferred to SaveR and PCQ on interrupt/trap recognition (Section 4.6).                                                                               |

| PV                   | <3>                | 1             | Prefix Valid flag. Set to "1" if the contents of the Prefix Register are valid and to "0" otherwise (Section 2.5).                                                                                                         |

| H/B                  | ❖                  | 1             | Halfword/Byte mode flag. When set to "1", specifies that multi-gauge arithmetic instructions are to operate on halfwords; when "0", specifies that these instructions are to operate on bytes (Section 2.6).               |

| OVT                  | <1>                | 1             | Overflow Trap enable flag. When set to "1", specifies that a trap is to be generated when overflow occurs on an arithmetic operation; when "0", specifies that no trap is to be generated on overflow (Sections 4.4,4.8).  |

| PUA                  | ❖                  | 1             | PU Available flag. When set to "1", advises the operating system that PU state does not have to be saved and restored when the PU processes an interrupt (Section 4.10).                                                   |

Figure 2.5. PU Status/Control Register Fields

code, the address in Next PC usually is equal to the address in Current PC plus two. Instructions must start on halfword boundaries, so program counter bit <0> always is "0".

The contents of Current PC can be read by executing a Load Program Counter instruction, which loads the address in the Current PC, plus 2, into a general register. In addition to the normal incrementing which takes place in execution of sequential code, program counters are modified when a taken branch or jump instruction is executed, or when a return from interrupt takes place. When an interrupt or a trap is recognized by an interrupt/trap enabled PU, the contents of the Current and Next PCs are saved in a special register pair called the PC save queue; on return from interrupt, the contents of the PC Save Queue are transferred to Current PC and Next PC (see Sections 4.6 and 4.7).

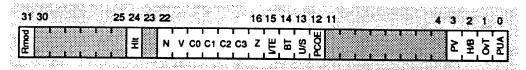

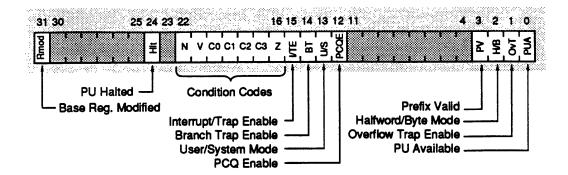

Status Register. The PU Status and Control Register (PsR) contains flags which control PU execution modes, enable or disable generation of certain traps and recognition of interrupts, and record information about the state of the PU and about the results of arithmetic operations. Figure 2.5 shows the PsR and briefly describes each of its flags. Shaded areas in this figure indicate fields reserved for future use.

PsR bit <31> (Rmod flag), bit <24> (Hlt flag), and bits <22:16> (condition codes) are set and cleared only by hardware. Other PsR bits can be set, tested, or cleared via Set Mode, Test Mode, and Clear Mode instructions. Bits <15:8> can be accessed only in system mode; an attempt to access these bits while in user mode causes an operation fault trap to be generated. Bits <7:0> can be accessed in either system mode or user mode. An attempt to set or clear a reserved bit causes unpredictable results. Testing a reserved bit causes the Z flag to be set.

When an interrupt or trap is recognized, the contents of the PsR are transferred to a special register called the Save Register, and PsR bits <24> and <15:0> then are cleared to "0". Among other things, this clears the mode flag (selecting system mode), disables interrupt/trap recognition, and clears the Halt and PU Available flags. Interrupt/trap recognition also causes a transfer of control to a kernel interrupt/trap address. (The kernel is distinguished from other system code by the range of addresses in which it runs.) On return from interrupt, the contents of the Save Register are transferred to the PsR. In preparing for the the initial dispatch of an address space, the kernel initializes a PU's PsR by setting or clearing Save Register bits as required; return from interrupt causes the Save Register contents to be transferred to the PsR (see Sections 4.6 and 4.7).

Special Registers. Some special registers are local (one instance per PU), while others are global (one instance per CPU). Both local and global special

$<sup>^2</sup>$ In Antares, this occurs only if the PU is interrupt/trap enabled (PsR bit <15> = "1"). If the PU is disabled (in which case the interrupt or trap represents an error), the PsR is not saved in the Save Register (also, PC contents are not saved in the PC Save Queue).

# Id Register (IdR)

| field<br><u>name</u> | bit<br>position(s) | <u>length</u> | description                                                                                                                                                                                                 |

|----------------------|--------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DSA                  | <31:19>            | 13            | Directories Starting Address. The concatenation of the DSA and ASN fields provide bits <31:12> of the real address of the translation table directory for the currently active address space (Section 3.4). |

| ASN                  | <18:12>            | 7             | Address Space Number. Address space number of the currently-active address space.                                                                                                                           |

| Model                | <7:4>              | 4             | Model number. "Hardwired" number assigned each implementation of the Scorpius CPU architecture.3                                                                                                            |

| Node                 | <3:0>              | 4             | Node Number. IPB location, assigned during machine powerup.                                                                                                                                                 |

Figure 2.6. Id Register Fields

registers are read or written via Move From Special and Move To Special instructions, which move values between general and special registers. An attempt to move to or from a privileged special register (one of the special registers marked "P" in Figure 2.3) while in user mode causes an operation trap to be generated. Also, an attempt to access a non-existent (reserved) special register while in user mode causes generation of an operation fault trap. (The result of an attempt to access a non-existent special register while in system mode is undefined.)

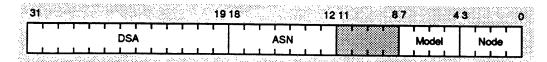

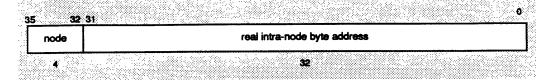

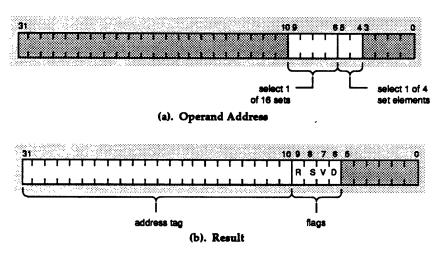

#0 — Id Register. Fields of the Id Register (IdR) identify the model of the CPU, its position on the Inter-Processor Bus (IPB), the number of the currently-active address space, and the starting location of address translation tables in the system. The IdR is a global, privileged, register. Figure 2.6 shows the IdR and briefly describes each of its fields (bits <11:8> are reserved for future use).

The DSA and ASN fields of the IdR specify the starting address of the directory, or first level translation table, for the current active address space. (Translation tables and the translation process are described in Chapter 3.) The DSA and ASN fields (IdR bits <31:12>) can be read or written; other IdR fields can only be read. Generally, the contents of the DSA field are written only on operating system initialization after powerup, and the contents of the ASN field are written only on an address space switch.<sup>4</sup>

<sup>&</sup>lt;sup>3</sup>Venus is model number 0; Antares is model number 1.

<sup>&</sup>lt;sup>4</sup>In Antares, writing to the IdR causes the Translation Buffer and its associated Directory Buffer to be flushed; see section 3.6.

The Model field of the IdR contains a "hardwired" model number; this number is used by implementation-dependent code to determine which implementation of the Scorpius architecture it is running on.

The Node field contains the CPU's node number; this number corresponds to the CPU's location on the Inter-Processor Bus (IPB) and is assigned during machine powerup (see Appendix C). A Scorpius real address comprises a 32-bit intra-node real byte address and a 4-bit node number. When performing an address translation, the MMU compares the node number of the translated address with the number in the IdR's node field. If these match, the memory access for which the translation was performed is sent to local memory; if they do not, the access is sent to the appropriate remote memory via the IPB.

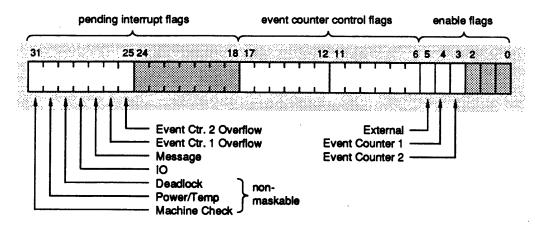

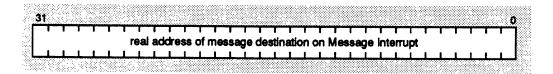

- #1 Interrupt Argument Register. The Interrupt Argument Register (IAR) is a privileged global register which holds the argument associated with a pending Message interrupt. This argument is the real intra-node address of the message destination. The IAR is shown in Figure 4.2(b). The contents of IAR can be read via a Move From Special instruction; the contents are valid from the point at which the Message interrupt is presented up to the point at which the Message Interrupt Pending flag in the Interrupt Control Register is cleared (see Section 4.3). The IAR can be written (for test purposes) via a Move To Special instruction; however, the CPU should be disabled for external interrupts so that a real Message interrupt is not presented while testing.

- #2 Test Register. The Test Register (TestR) is a global, privileged register provided for diagnostic purposes. The Test Register can be read or written; its functions are implementation-dependent.

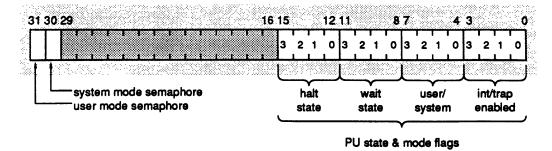

- #3 Global Status Register. The Global Status Register (GSR) is a privileged global register which serves two functions: it holds the user and system mode semaphore flags (in bits <31:30>), and it records the state and mode of the four PUs (in bits <16:0>). Figure 2.7 shows the GSR and briefly describes its fields. Bits <29:16> are reserved for future use; the values returned in these bit position when the GSR is read are undefined. The GSR cannot be written; the result of attempting to execute a Move To Special instruction with the GSR as the destination register is unpredictable.

Semaphore operations are performed by Lock and Unlock instructions. The Lock instruction examines the semaphore flag corresponding to the PU's mode. If the flag is "1", it is changed to "0", and Lock instruction execution completes. If the flag initially is "0", the Lock instruction waits until it becomes "1", changes it to "0", and then completes. The semaphore flag is unconditionally set to "1" via an Unlock instruction. Semaphore operations are discussed in Section 5.4.

The state and mode flags in bits <15:0> are used in deadlock detection and analysis. The CPU monitors the halt and wait flags in the GSR. If it finds that all four PUs are either halted or waiting, it generates a Deadlock interrupt. This is a non-maskable interrupt which is presented to and immediately recognized by PU 0. PU 0 uses the state and mode information to help analyze the cause of the deadlock and to determine how to initiate recovery (see Section 5.5).

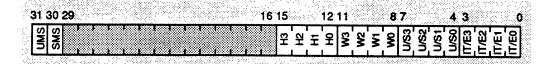

# Global Status Register (IdR)

| field<br><u>name</u> | bit<br>position(s) | <u>length</u> | description                                                                                                                                 |

|----------------------|--------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| UMS                  | <31>               | 1             | User Mode Semaphore flag. Set to "0" if the user semaphore is locked and to "1" if the semaphore is unlocked (Section 5.4).                 |

| SMS                  | <30>               | 1             | System Mode Semaphore flag. Set to "0" if the system semaphore is locked and to "1" if the semaphore is unlocked (Section 5.4).             |

| Н3-Н0                | <15:12>            | 4             | Halt flag copies. Hi is "1" if PU i is halted (PsR bit $<24>$ = "1") and is "0" otherwise.                                                  |

| W3-W0                | <11:8>             | 4             | Wait flags. Wi is "1" if PU i is in wait state (see Section 5.5 for definition) and is "0" otherwise.                                       |

| U/S1-US3             | <7:4>              | 4             | User/System Mode flag copies. U/Si is "1" if PU i is in user mode (PsR $<13>=$ "1") and is "0" if PU i is in system mode (PsR $<13>=$ "0"). |

| TT/E3-TT/E           | 0 <3:0>            | 4             | Interrupt/Trap Enabled flag copy. IT/Ei is "1" if PU i is interrupted/trap enabled (PsR $<15> = "1"$ ) and is "0" otherwise.                |

Figure 2.7. Global Status Register Fields

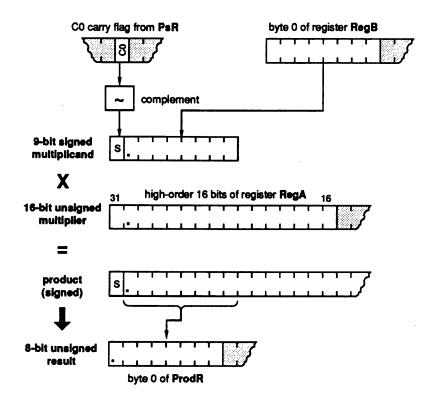

- #4 Product Register. The Product Register (ProdR) is a local, non-privileged register which holds the upper 32 bits of the 64-bit product produced by a 32-bit multiply instruction (Mul or MulU), or the four product bytes or two product halfwords produced by a multiply partial instruction (MulP or MulPU).

- #5 Remainder Register. The Remainder Register (RemR) is a local non-privileged, register which holds the remainder produced by a divide instruction (Div, DivE, DivU, or DivUE). RemR also is used by the divide extended instructions (DivE and DivUE) in forming the 64-bit dividend; for these instructions, the 64-bit dividend is formed by concatenating the contents of the Remainder Register with the contents of the specified general register.

- #6 Prefix Register. The Prefix Register (PfxR) is a local, non-privileged, register which can be loaded with a constant value to be used in extended the range of a displacement or an immediate, or with a field description (position and length) for field manipulation instructions. Values are loaded in the PfxR by Prefix Immediate and Mask Generate instructions; these also set the Prefix Valid flag in the PsR (bit <3>). Instructions which use the PfxR clear the Prefix Valid flag. The PfxR also can be read or written via

# 25 24 18 17 12 11 6 5 3 2 0

# Interrupt Control Register (ICR)

| field<br>name    | bit<br>position(s) | <u>length</u> | description                                                                                                                                                                                             |

|------------------|--------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

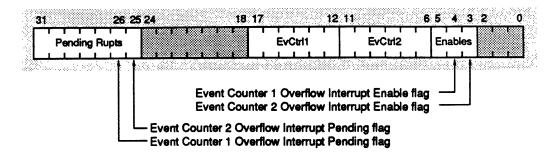

| Pending<br>Rupts | <31:25>            | 7             | Pending Interrupt flags. This field contains a flag for each interrupt type; a Pending Rupt flag is set to "1" if an interrupt of the corresponding type is pending and is "0" otherwise (Section 4.3). |

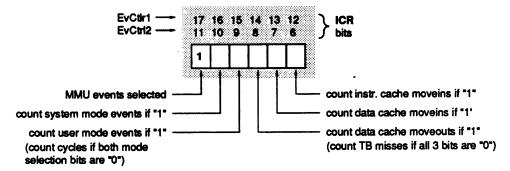

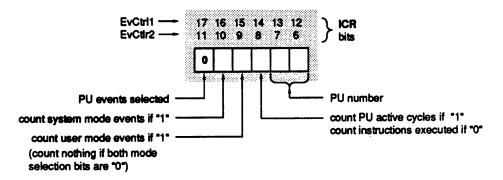

| EvCtrl1          | <17:12>            | 6             | Event Counter 1 Control flags. The flags of this field specify the source of events (PU or MMU) to be counted by event counter 1, and specify the event to be counted (Chapter 7).                      |

| EvCtrl2          | <11:6>             | 6             | Event Counter 2 Control flags. The flags of this field specify the source of events (PU or MMU) to be counted by event counter 2, and specify the event to be counted (Chapter 7).                      |

| Enables          | <5:3>              | 3             | Interrupt Enable flags. This field contains flags which control the generation of Event Counter Overflow interrupts and the presentation of external (IO and Message) interrupts (Section 4.3).         |

Figure 2.8. Interrupt Control Register Fields

Move From/To Special instructions, but these instructions do not affect the Prefix Valid flag. (This flag can be set or cleared via Set/Clear Mode instructions.) Bits <1:0> of the PfxR are unused; writing the PfxR (via a Move To Special instruction) does not affect these bits. When reading the PfxR using a Move From Special instruction, "0" is returned in these bit positions. A detailed description of prefixing and PfxR use is presented in Section 2.5.

- #8, #9 Event Counters 1 and 2. The two event counters (EvR1 and EvR2) are 32-bit global, privileged, registers which, under control of event counter control flags in the Interrupt Control Register, can be used to count various PU and MMU events as well as PU active time. Setup and use of these counters is discussed in Chapter 7.

- #10 Scratch Register. The Scratch Register (ScR) is a global, privileged, register used in saving registers on interrupt/trap recognition. When an interrupt or a trap is recognized and PU state must be saved (the PUA flag in the PsR = "0"), the kernel uses the system mode semaphore to enter a critical section, stores the contents of one general register in ScR and uses that register typically register 0 to form the address of a save area in memory. After saving registers, including the register temporarily moved to ScR, the kernel exits the critical section, making the ScR available to some other PU.

Pending Rupts

# Trap Register (TrapR)

Figure 2.9. Trap Register Fields

#11 — Interrupt Control Register. The Interrupt Control Register (ICR) is a global, privileged, register which contains interrupt pending and enable (mask) flags, together with control flags for the two event counters. Figure 2.8 shows the fields of the ICR and briefly describes their function; ICR bits <24:18> and <2:0> are reserved fields. There is a pending interrupt flag for each type of interrupt; when an interrupt occurs, the corresponding flag is set in the ICR and a PU selected to process the interrupt; the kernel clears the interrupt pending flag as part of interrupt processing. Figure 4.2(a) shows the individual pending interrupt and interrupt enable flags, which are discussed at length in Section 4.3. Individual event counter control flags are described in Chapter 7.

The contents of the ICR can be read via a Move From Special instruction; the values returned in reserved field bits are undefined. The ICR can be written via a Move To Special instruction. However, pending interrupt flags are set to "1" only by hardware; software can only clear a pending interrupt flag to "0". If an attempt is made to write a "1" to a pending interrupt flag, the state of the flag does not change. (See **Pending Interrupt Flags** in Section 4.3.)

#12 — Status Save Register. The Status Save Register (SaveR) is a local, privileged, register. When an interrupt or a trap is recognized, the contents of the PsR are moved to the SaveR, from where they can be examined via a Move From Special instruction.<sup>5</sup> The fields of the SaveR correspond to those of the PsR (Figure 2.5): when reading the SaveR, the values returned in reserved field bits are undefined. Following interrupt/trap recognition, the contents of the SaveR remain valid only up to the point at which the PU reenables interrupt/trap recognition.

The SaveR can be written via a Move to Special instruction. On return from interrupt (which is effected by executing a Return From interrupt instruction pair), the contents of the SaveR are copied to the PsR and the contents of the PCQ are copied to the Current and Next PC. To dispatch a newly-initiated address space, each PU sets SaveR and PCQ as appropriate and performs a return from interrupt. (See Sections 4.6 and 4.7).

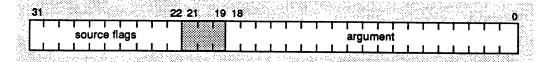

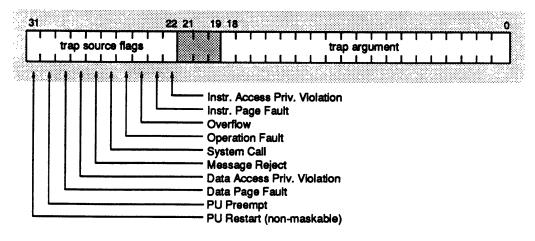

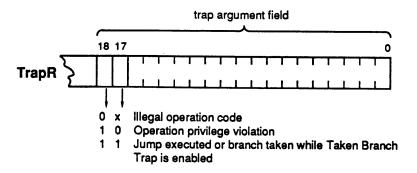

#13 — Trap Register. The Trap Register (TrapR) is a local, privileged, register which contains trap source flags and, for certain traps, a trap

$<sup>^{5}</sup>$ In Antares, the transfer of the PsR to SaveR on interrupt or trap recognition takes place only if the PU was interrupt/trap enabled — PsR bit <15> = "1" — at the time of recognition.

### PC Save Queue (PCQ)

Figure 2.10. The PC Save Queue

argument. The Trap Register is shown in Figure 2.9; Figure 4.2(c) shows the individual trap source flags. There is a trap flag for each trap (except the PU Check trap, which is identified by its kernel entry address); a trap source flag is set to "1" by hardware when the corresponding trap is recognized, and cleared by the kernel as part of trap processing. TrapR bits <21:19> are reserved.

Following interrupt/trap recognition, the contents of TrapR remain valid only up to the point at which the PU reenables interrupt/trap recognition. The Trap Register can be read via a Move From Special instruction and written via a Move To Special instruction. When reading TrapR, the values returned in bits <21:19> are undefined. While trap source flags can be set to "1" by software, as well as cleared to "0", software setting of a trap source flag is ignored and does not result in trap recognition.

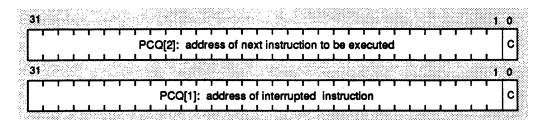

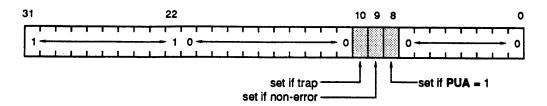

#14 — PC Save Queue. This register (Figure 2.10) is a FIFO register pair, comprising two 32-bit register, PCQ[1] and PCQ[2]. (The register pair sometimes is referred to as PCQ.) When an interrupt or a trap is recognized, the instruction address in Current PC is transferred to PCQ[1], and the instruction address in Next PC is transferred to PCQ[2]. On return from interrupt, these transfers are reversed. Following interrupt/trap recognition, the contents of PCQ remain valid only up to the point at which the PU reenables interrupt/trap recognition.

Because instructions must start on halfword boundaries, the low-order bit of an instruction address is ignored when fetching instructions. In the PCQ, this bit position is used to hold a Correction flag, or C flag. When the Correction flag in PCQ[1] is set on interrupt/trap recognition, it is necessary to adjust the address in PCQ[1] prior to returning from interrupt (see Section 4.6). The Correction flag in PCQ[2] can always be ignored. (Address adjustment may be required because of the "folding" of branch, prefix, and other instructions.)

<sup>&</sup>lt;sup>6</sup>In Antares, the transfer of Current PC and Next PC to PCQ[1] and PCQ[2] on interrupt or trap recognition takes place only if the PU was interrupt/trap enabled — PsR bit <15> = "1" — at the time of recognition.

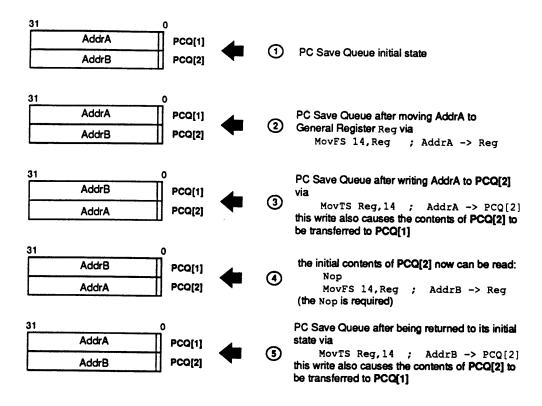

The contents of PCQ[1], only, can be read via a Move From Special instruction; PCQ[2], only, can be written via a Move To Special instruction. Whenever PCQ[2] is written, the original contents of PCQ[2] are transferred to PCQ[1]. Thus, correcting the address in PCQ[1] or saving PCQ contents prior to an address space switch requires that moves be done in the correct order. (See PC Save Queue Access in Section 4.6.)

Caches. In Scorpius, the instruction and data caches are architecturally visible and constitute part of the programming model (cache control instructions are discussed in Chapter 6). The extent of the visibility of the caches depends on the implementation. All implementations have a cache line size of 64 bytes, and separate instruction and data caches with software maintenance of coherence between the two. Antares has a virtually-addressed caches which may contain synonyms. Coherence and synonym issues are discussed in Section 3.8. Also, the size of the data cache (64 lines) is visible in Antares, which provides an instruction, Read Data Tag by Index, to read data cache line tags (used in clearing the cache on an address space switch).

#### 2.4 Instruction Set Overview