# MOSTEK 1977 MEMORY PRODUCTS CATALOG

# **CONTENTS**

- I. Functional/Numerical Index

- II. Shift Registers

- III. Read Only Memories 16K ROMs 32K/64K ROMs Programmable ROMs

- IV. Random Access Memories

4K Dynamic RAMs

16K Dynamic RAMs

4K Static RAMs

- V. Application Information

- VI. Packaging

- VII. Reliability Information

- VIII. Microprocessors

- IX. Industrial

- X. Consumer

- XI. Reference

Direct Replacement Guide

Memory Product Guide

# FUNCTIONAL/NUMERICAL INDEX

| II. | SHIFT REGISTE              | ERS .                                                    |        |       |                           |                                             |          |

|-----|----------------------------|----------------------------------------------------------|--------|-------|---------------------------|---------------------------------------------|----------|

|     | MK 1002P                   |                                                          |        |       | MK 4096P-77               | 4096x1-Bit Dynamic RAM                      |          |

|     | MK 1002N                   | Dual 128-Bit Static Shift Register                       | II-2   |       |                           | 250ns Access Time                           | IV-43    |

|     | MK 1007P<br>MK 1007N       | Quad 80-Bit Dynamic Shift Register                       | II-6   |       | MK 4096P-86               | 4096x1-Bit Dynamic RAM<br>300ns Access Time | IV-43    |

| ш.  | READ ONLY M                | EMODIES                                                  |        |       | MK 4096P-85               | 4096x1-Bit Dynamic RAM                      |          |

| ш.  | READ CIVET IVI             | EIVIONIES                                                |        |       | MK 4200P-11               | 350ns Access Time                           | IV-43    |

|     | MK 2300P                   | 2240-Bit ROM Character Generator                         | III-2  |       | MK 4200N-11               | 350ns Access Time                           | IV-47    |

|     | MK 2300N                   | ASCII Francisco Communication                            | W 0    |       | MK 4200P-16               | 4096x1-Bit Dynamic RAM                      |          |

|     | MK 2302P<br>MK 2302N       | ASCII Encoded Generator                                  | III-2  |       | MK 4200N-16<br>MK 4227P-2 | 300ns Access Time                           | IV-47    |

|     | MK 2400P                   | 2560-Bit ROM                                             | 111-7  |       | WIN 42271 -2              | 150ns Access                                | IV-54    |

|     | MK 2408P                   | 2560-Bit Row-Out Character                               | 40     |       | MK 4227P-3                | 4096x1-Bit Dynamic RAM                      |          |

|     | MK 2500P                   | Generator                                                |        |       | MK 4227N-3<br>MK 4227P-4  | 200ns Access Time                           | IV-54    |

|     | MK 2503P                   | ASCII/EBCDIC Code Converter                              |        |       | MK 4227P-4<br>MK 4227N-4  | 4096x1-Bit Dynamic RAM<br>250ns Access Time | 1\/_5/   |

|     | MK 2600P                   | 4096-Bit ROM                                             | III-14 |       |                           |                                             |          |

|     | MK 2601P<br>MK 30000P      | ASCII/EBCDIC Code Converter                              | III-14 |       | 16K DYNAMIC RAI           | MS                                          | IV-65    |

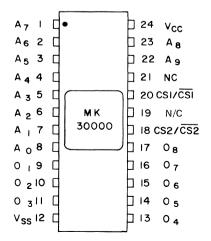

|     | MK 30000P                  | 8192-Bit Static ROM                                      | III-19 |       | MK 4116P-2                | 16,384-Bit Dynamic RAM                      |          |

|     | 16K ROMS                   |                                                          | III-23 |       | MK 4116P-3                | 150ns Access Time                           | IV-66    |

|     |                            |                                                          | 111-20 |       | IVIN 41 10F-3             | 200ns Access Time                           | IV-66    |

|     | MK 28000P<br>MK 28000N     | 16394 Bit Dunamia BOM                                    | 111.24 |       | MK 4116P-4                | 16,384-Bit Dynamic RAM                      |          |

|     | MK 31000P-3                | 16384-Bit Dynamic ROM                                    | 111-24 |       |                           | 250ns Access Time                           | IV-78    |

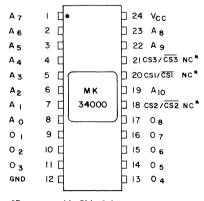

|     | MK 31000N-3<br>MK 34000P-3 | 16384-Bit Static ROM                                     | III-28 |       | 4K STATIC RAMS            |                                             | IV-89    |

|     | MK 34000P-3<br>MK 34000N-3 | 16384-Bit Static ROM                                     | III-32 |       | MK 4104P-3                | 4096x1-Bit Static RAM                       |          |

|     | 2014/2414 DOM              |                                                          | 05     |       | MK 4104N-3                | 200ns Access Time                           | IV-90    |

|     | 32K/64K HUWS               |                                                          | 111-35 |       | MK 4104P-4<br>MK 4104N-4  | 4096x1-Bit Static RAM<br>250ns Access Time  | IV. or   |

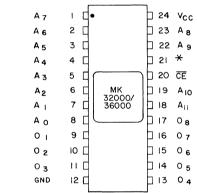

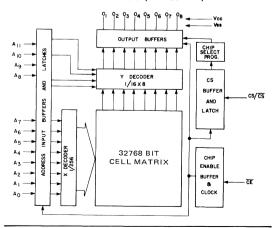

|     | MK 32000P                  | 32K-Bit ROM                                              | III-36 |       | MK 4104P-5                | 4096x1-Bit Static RAM                       | 14-30    |

|     | MK 36000P                  | 64K-Bit ROM                                              | III-36 |       | MK 4104N-5                | 300ns Access Time                           | IV-90    |

|     | PROGRAMMARI                | E ROMS                                                   | III-39 |       | MK 4114P-3<br>MK 4114N-3  | 1024x4-Bit Static RAM<br>200ns Access Time  | 11/ 05   |

|     |                            |                                                          | 00     |       | MK 4114P-4                | 1024x4-Bit Static RAM                       | 10-90    |

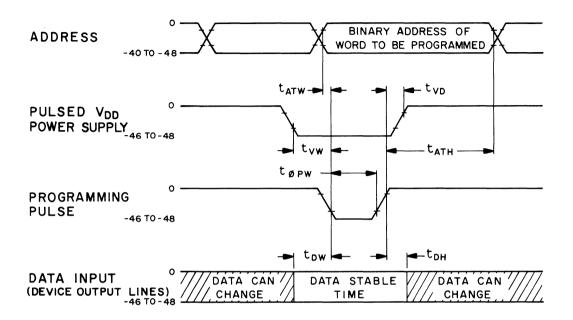

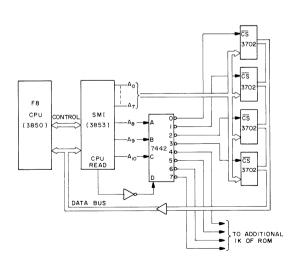

|     | MK 3702T-1                 | 2048-Bit Electrically Programmable ROM 550ns Access Time |        |       | MK 4114N-4                | 250ns Access Time                           | IV-95    |

|     | MK 3702T-2                 | 2048-Bit Electrically Programmable                       | 111-42 |       | MK 4114P-5<br>MK 4114N-5  | 1024x4-Bit Static RAM<br>300ns Access Time  | IV QE    |

|     |                            | ROM 750ns Access Time                                    | 111-42 |       |                           |                                             | 10-50    |

|     | MK 3702T-3                 | 2048-Bit Electrically Programmable ROM 1µs Access Time   | III 40 | V.    | APPLICATION IN            | FORMATION                                   |          |

|     | MK 3602P                   | 2048-Bit Electrically Programmable                       | 111-42 |       | An In-Depth Look at       | t MOSTEK's                                  |          |

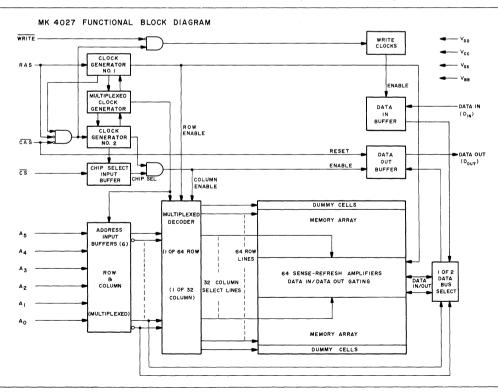

|     |                            | ROM                                                      | 111-42 |       | High Performance N        | MK 4027                                     | V-2      |

|     | MK 2708T                   | 1024x8-Bit Electrically Programmable ROM                 | III-48 |       | MK 4096 Application       | n Information                               | V-16     |

| IV. | BANDOM ACC                 | ESS MEMORIES                                             |        |       |                           |                                             |          |

|     |                            |                                                          |        |       |                           | Designing a High Density y System           | V-24     |

|     | MK 4006P-6                 | 1024x1-Bit Dynamic RAM                                   |        |       |                           |                                             |          |

|     | MK 4008P-6<br>MK 4007P     | 1024x1-Bit Dynamic RAM                                   | IV-2   | VI.   | PACKAGING                 |                                             |          |

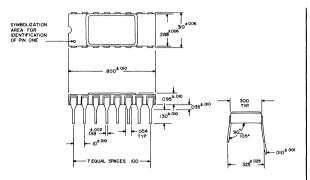

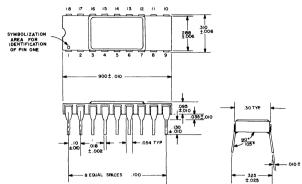

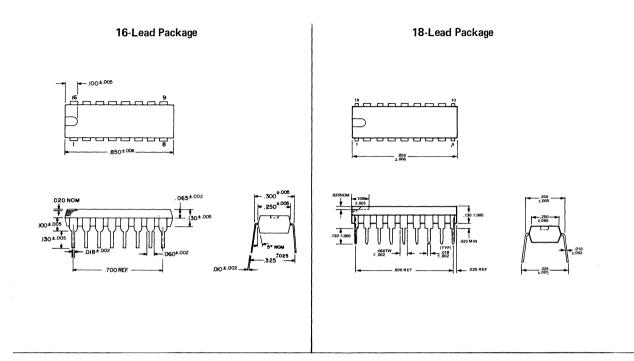

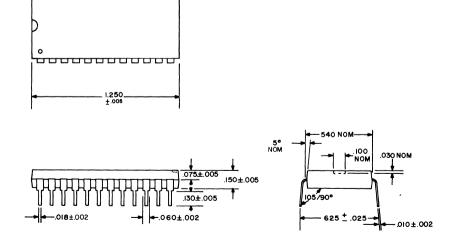

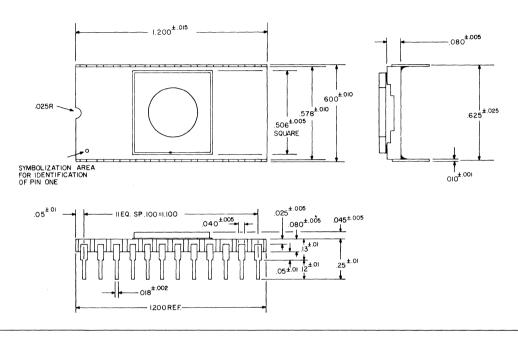

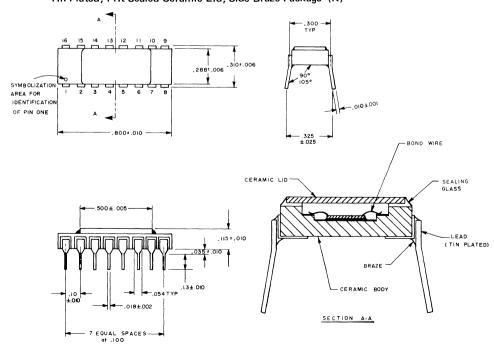

|     | MK 4007N                   | 256x1-Bit Static RAM                                     | IV-8   |       | Ceramic Dual-in-Line      | Hermetic Packaging                          | . VI-2   |

|     | MK 4007P-4<br>MK 4007N-4   | OFC. 1 Dit Ctatio DAM                                    | 11/10  |       | Plastic Dual-in-Line I    | Packaging                                   | . VI-3   |

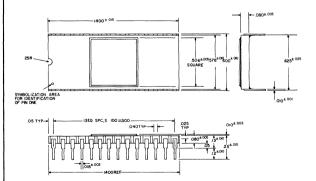

|     | MK 4102N                   | 256x1-Bit Static RAM                                     | IV-12  |       | Alternate Hermetic I      | Packaging                                   | . VI-4   |

|     | NAK 4100N 1                | 1 μs Access Time                                         | IV-13  | VII.  | RELIABILITY INF           | ORMATION                                    |          |

|     | MK 4102N-1                 | 1024x1-Bit Static RAM<br>450ns Access Time               | IV-13  | VIII. | MICROPROCESS              | ORS                                         |          |

|     | MK 4102N-11                | 1024x1-Bit Static RAM                                    |        |       |                           |                                             |          |

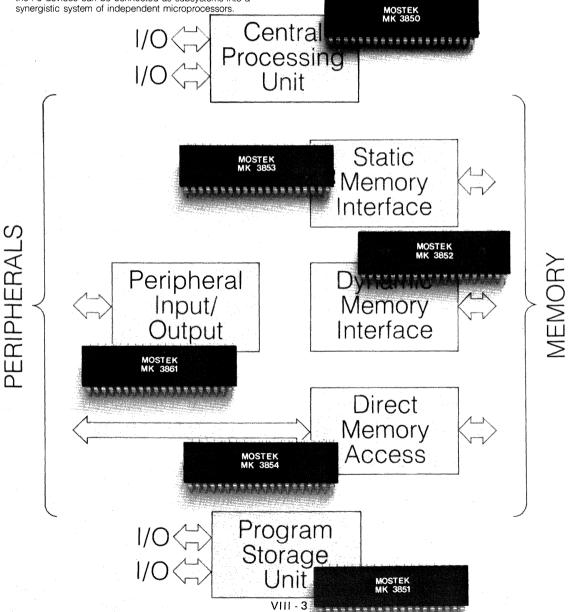

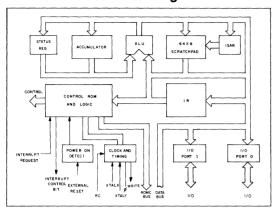

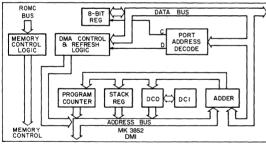

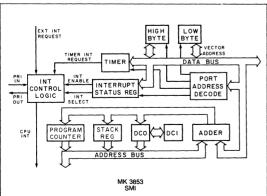

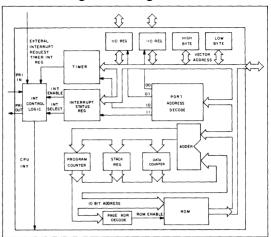

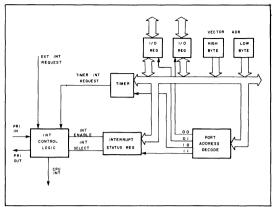

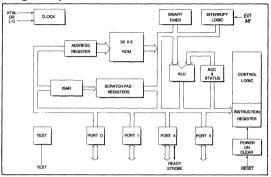

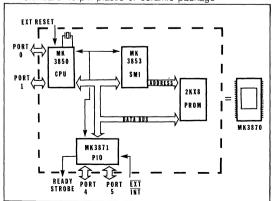

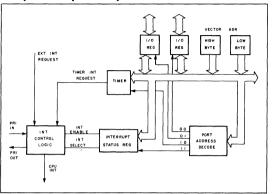

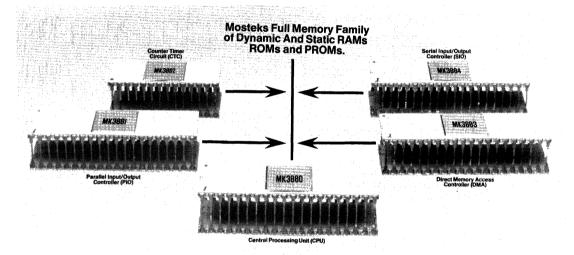

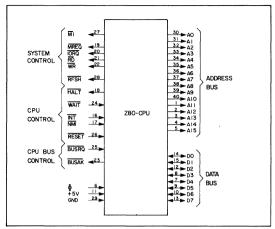

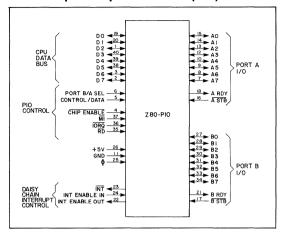

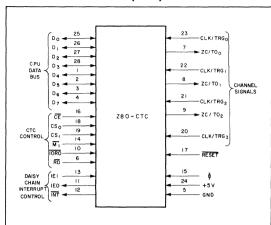

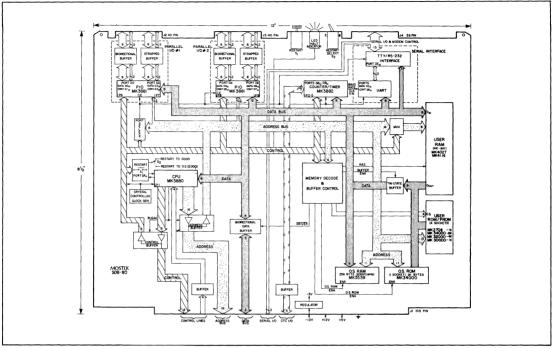

|     | MK 4102N-12                | 450ns Access Time                                        | IV-13  |       |                           | crocomputer. With low power                 | \ /III C |

|     | 17117 410217 12            | 1 μs Access Time                                         | IV-13  |       |                           | elivered in plastic                         | VIII-3   |

|     | 4K DYNAMIC RA              | .MS                                                      | IV-17  |       | The economical 387        | 0. A complete system on a                   | VIII-8   |

|     |                            |                                                          |        |       | - '                       |                                             | VIII C   |

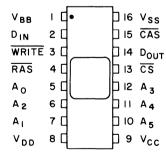

|     | MK 4027P-2                 | 4096x1-Bit Dynamic RAM<br>150ns Access Time              | IV-18  |       | With 8080A softwar        | ce Z80 Microcomputer.                       |          |

|     | MK 4027P-3                 | 4096x1-Bit Dynamic RAM                                   |        |       |                           | eatures                                     | VIII-9   |

|     | MK 4027N-3<br>MK 4027P-4   | 200ns Access Time                                        | IV-18  | IV    | INDLICTOR                 |                                             |          |

|     | MK 4027N-4                 | 250ns Access Time                                        | IV-18  | IX.   | INDUSTRIAL                |                                             |          |

|     | MK 4096P-6                 | 4096x1-Bit Dynamic RAM                                   |        | X.    | CONSUMER                  |                                             |          |

|     | MK 4096N-6                 | 250ns Access Time                                        | IV-29  | ×:    | DFFFDF                    |                                             |          |

|     | MK 4096P-16<br>MK 4096N-16 | 4096x1-Bit Dynamic RAM<br>300ns Access Time              | IV-29  | XI.   | REFERENCE                 |                                             |          |

|     | MK 4096P-11                | 4096x1-Bit Dynamic RAM                                   | 20     |       | Direct Replacement        | Guide                                       | XI-2     |

|     | MK 4096N-11                | 350ns Access Time                                        | IV-29  |       |                           | uide                                        |          |

|     | MK 4096P-15                | 4096x1-Bit Dynamic RAM                                   | 1//-36 |       |                           |                                             |          |

# SHIFT REGISTERS

# **DUAL 128-BIT STATIC SHIFT REGISTER**

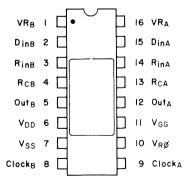

# MK 1002 P/N

# **FEATURES**

- Ion-implanted for full TTL/DTL compatibility no interface circuitry required

- ☐ Single-phase, TTL/DTL compatible clocks

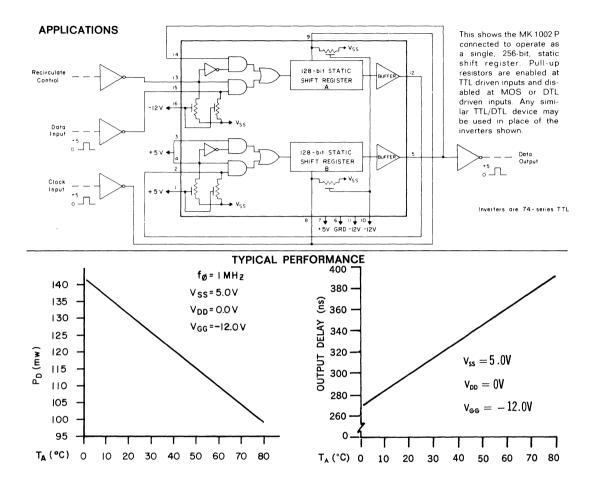

- □ Dual 128-bit static shift registers—256 bits total

- Dual sections have independent clocks

# DESCRIPTION

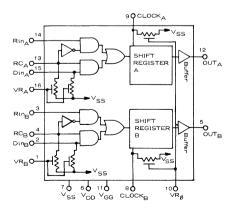

The MK 1002 is a P-channel MOS static shift register utilizing low threshold-voltage processing and ion-implantation to achieve full TTL/DTL compatibility. Each of the two independent 128 bit sections has a built-in clock generator to generate three internal clock phases from a single-phase TTL-level external input. In addition, each section has input logic for loading or recirculating data within the register. (See Functional Diagram.) The positive-logic Boolean expression for this action is:

OUT (delayed 128 bits) = (R<sub>C</sub>) (D<sub>IN</sub>) + (R<sub>C</sub>) (R<sub>IN</sub>)

- ☐ Recirculate logic built in

- □ DC to 1 MHz clock rates

- ☐ Low power dissipation—130 mW

- □ 16-pin dual-in-line package

The Data, Recirculate Control, and Clock inputs are provided with internal pull-up resistors to VSS (+5V) for use when driving from TTL. These resistors can be disabled when driving from circuitry with larger output-voltage swings, such as DTL. Enabling of pull-up resistors is accomplished by connecting the appropriate terminal to VGG; disabling by connecting to VSS. The Recirculate inputs are not provided with pull-up resistors since they are generally driven from MOS.

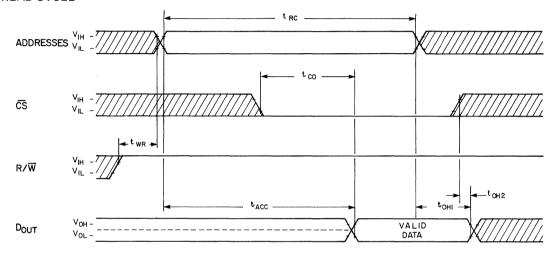

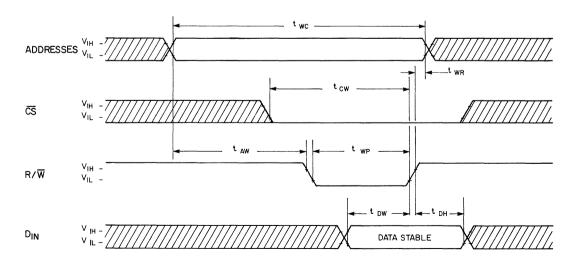

Shifting data into the register is accomplished while the Clock input is low. Output data appears following the positive-going Clock edge. Data in each register can be held indefinitely by maintaining the Clock input high.

# **FUNCTIONAL DIAGRAM**

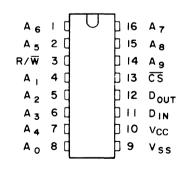

# PIN CONNECTIONS

### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage, VDD                  | V <sub>SS</sub> — 10.0 V        |

|--------------------------------------|---------------------------------|

| Supply Voltage, VGG                  |                                 |

| Voltage at any Input or Output       | . VSS + 0.3 V to VSS $-$ 10.0 V |

| Operating Free-Air Temperature Range | 0°C to +75°C                    |

| Storage Temperature Range (Ceramic)  |                                 |

| Storage Temperature Range (Plastic)  | 55°C to +125°C                  |

# **RECOMMENDED OPERATING CONDITIONS** $(0^{\circ}C \le T_A \le 75^{\circ}C)$

|              |                  | PARAMETER                     | MIN                | TYP          | MAX                | UNITS       | COMMENTS       |

|--------------|------------------|-------------------------------|--------------------|--------------|--------------------|-------------|----------------|

| E            | V <sub>ss</sub>  | Supply Voltage                | 4.75               | 5.0          | 5.25               | V           | $V_{DD} = 0 V$ |

| POWER        | V <sup>ee</sup>  | Supply Voltage <sup>(1)</sup> | —12.6              | <b>—12.0</b> | —11.4              | V           |                |

| ZI .         | V <sub>IL</sub>  | Input Voltage, Logic 0(2)     |                    | 0            | V <sub>ss</sub> —4 | V           |                |

| INPUTS       | V <sub>IH</sub>  | Input Voltage, Logic 1        | V <sub>ss</sub> —1 | 5.0          | V <sub>ss</sub>    | V           |                |

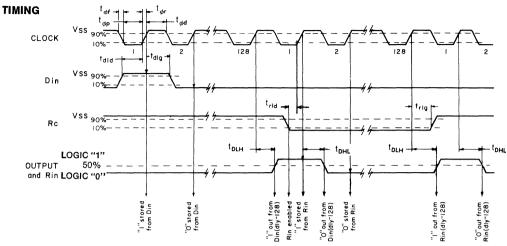

|              | f                | Clock Repetition Rate         | DC                 |              | 1                  | MHz         |                |

|              | t <sub>øp</sub>  | Clock Pulse Width             | 0.35               |              | 10                 | μS          |                |

|              | t <sub>ød</sub>  | Clock Pulse Delay             | 0.4                |              |                    | μS          | See            |

| INPUT TIMING | t <sub>ø</sub> r | Clock Pulse Risetime          | .010               |              | 0.2                | <b>μ</b> \$ | Timing         |

| Ē            | t <sub>øf</sub>  | Clock Pulse Falltime          | .010               |              | 0.2                | μS          | Diagram        |

| ₹            | t <sub>dld</sub> | Data Leadtime                 | 50                 |              |                    | ns          |                |

| =            | t <sub>dlg</sub> | Data Lagtime                  | 200                |              | }                  | ns          |                |

|              | t <sub>rld</sub> | Recirculate Control Leadtime  | 100                |              |                    | ns          |                |

|              | t <sub>tig</sub> | Recirculate Control Lagtime   | 300                |              |                    | ns          |                |

# **ELECTRICAL CHARACTERISTICS**

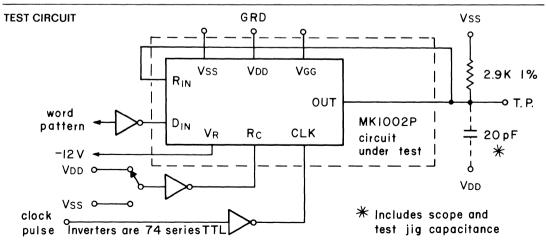

$(V_{SS}=+5\pm0.25V,V_{GG}=-12\pm0.6V,V_{DD}=0V,T_{A}=0^{\circ}C$  to  $+75^{\circ}C$ , using test circuit shown, unless otherwise noted.)

|                  |                     | PARAMETER                                                            | MIN        | TYP <sup>3</sup> | MAX        | UNITS                    | CONDITIONS                                                                                                                |

|------------------|---------------------|----------------------------------------------------------------------|------------|------------------|------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------|

| POWER            | I <sub>ss</sub>     | Power Supply Current, V <sub>ss</sub>                                |            | 14               | 25         | mA                       | $f_\phi = 1$ MHz Inputs & Outputs open                                                                                    |

| 2                | l <sub>ee</sub>     | Power Supply Current, V <sub>ee</sub>                                |            | 5                | 10         | mA                       |                                                                                                                           |

|                  | C <sub>i</sub>      | Input Capacitance, any Input                                         |            | 3                | 10         | pF                       | $V_i = V_{ss}$ , $f = 1 \text{ MHz}$<br>$T_A = 25^{\circ}\text{C}$                                                        |

| INPUTS           | I <sub>IL</sub>     | Input Current, Logic 0:<br>Resistors Disabled²<br>Resistors Enabled² | -0.3       |                  | 40<br>1.6  | μ <b>A</b><br>m <b>A</b> | $V_{I} = V_{SS} - 5V$ $V_{I} = +0.4V$                                                                                     |

| Ž                | I <sub>IH</sub>     | Input Current, Logic 1, Any Input                                    |            |                  | 40         | μΑ                       | $VR_A$ , $VR_B$ , $VR_\phi = V_{SS}$<br>$V_1 = V_{SS}$                                                                    |

|                  | 1 <sub>IR(on)</sub> | Input Current at Recirculate Inputs <sup>2</sup>                     |            |                  | <b> 40</b> | μΑ                       | $egin{aligned} VR_\mathtt{A}, VR_\mathtt{B}, VR_\phi &= V_\mathtt{GG} \ V_\mathtt{I} &= V_\mathtt{SS} - 5V \end{aligned}$ |

| OUTPUTS          | V <sub>OL</sub>     | Output Voltage, Logic 0 (3)                                          |            |                  | 0.4        | ٧                        | $I_L = -1.6 \text{ mA}$                                                                                                   |

| 150<br>TT        | V <sub>OH</sub>     | Output Voltage, Logic 1 (3)                                          | $V_{ss}-1$ |                  |            | V                        | $I_L = +100 \mu A$                                                                                                        |

|                  | t <sub>DLH</sub>    | Output Delay, Low to High (3)                                        |            |                  | 450        | ns                       | See Timing                                                                                                                |

| DYNAMIC<br>CHAR. | t <sub>DHL</sub>    | Output Delay, High to Low (3)                                        |            |                  | 450        | ns                       | Diagram and                                                                                                               |

| CH,              | t <sub>vor</sub>    | Output Voltage Rise Time (3)                                         | 1          | 100              | 150        | ns                       | Test                                                                                                                      |

|                  | t <sub>vof</sub>    | Output Voltage Fall Time (3)                                         |            | 100              | 150        | ns                       | Circuit                                                                                                                   |

### NOTES:

Other supply voltages are permissible providing that supply and input voltages are adjusted to maintain the same potential relative to Vss, e.g., Vss = OV, Vso = -5 ± 0.25V, Vso = -17 ± 0.85V.

MOS pull-up resistors to +5V are provided internally. These MOS resistors are enabled by connecting VRA, VRs and VRø to Vso, and disabled by connecting VRA, VRs and VRø to Vso. Pull-up resistors not provided at recirculate inputs.

At TA = 25°C.

The timing diagram applies to either section of the dual shift register. The test conditions for these waveforms are illustrated below. A logic "1" is defined as +5 V and a logic "0" is defined as OV

As long as  $R_c$  is at a "1",  $R_{in}$  is disabled and  $D_{in}$  is enabled. The data that is present at  $D_{in}$  while the clock is at "0" is shifted in and will be stored as the clock goes to a "1". This data must have been present  $t_{did}$  time prior to the clock "1" edge. The data must also remain in that same state for  $t_{dig}$  time after that edge. These times are necessary to insure proper data storage in the first register-cell.

On the clock "1" edge, data is shifted through the register causing bit 127 to be shifted to position 128. This cell's output is buffered and appears at the output in the same logic polarity that appeared at the input 128 clocks prior. This data appears within t<sub>od</sub> time of the clock "1" edge.

$R_{\text{in}}$  may be hardwired to the data output. When  $R_{\text{C}}$  is at a "0",  $R_{\text{in}}$  is enabled and  $D_{\text{in}}$  is disabled. Therefore, the output data will appear at the input of the first cell. When  $R_{\text{in}}$  is tied to the data output, the output delay will insure  $t_{\text{dig}}$  and  $t_{\text{did}}$  times.  $R_{\text{C}}$  "0" time must lead the clock "1" edge by  $t_{\text{rid}}$  time and must lag that edge by  $t_{\text{rig}}$  time to insure proper data storage when recirculate storage is desired.

# **OPERATING NOTES**

| Rc | R <sub>in</sub> | D <sub>in</sub> | DATA<br>ENTERED |

|----|-----------------|-----------------|-----------------|

| 1  | Х               | 1               | 1               |

| 1  | Х               | 0               | 0               |

| 0  | 1               | Х               | 1               |

| 0  | 0               | Х               | 0               |

$"1" = V_{ss} = +5V$

$\hbox{``0''}=V_{DD}=Grd$

X = No Effect

Output Logic: See Description.

# 320-BIT DYNAMIC SHIFT REGISTER

# MK 1007 P/N

# **FEATURES**

- ☐ Ion-Implanted for full TTL/DTL compatibility

- ☐ Single-phase, TTL/DTL compatible clock

- □ Internal pull-up resistors

- ☐ Clock Frequency 10 kHz to 2.5 MHz

- □ Built-in recirculate logic for each register

- □ Power Supplies: +5V and −12V

# DESCRIPTION

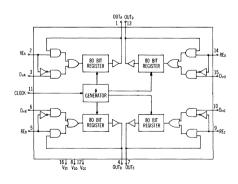

The MK 1007 P contains four separate 80-bit MOS dynamic shift registers on a single chip, using ion-implantation in conjunction with P-channel processing to achieve low threshold voltage and direct TTL/DTL compatibility. All logic inputs, including the single-phase Clock, can be driven directly from DTL or TTL logic. Pull-up resistors to +5V are provided for worst-case TTL inputs.

Each 80-bit register has independent inputs and outputs and a control input (RE) which allows external data to be shifted into the register (at logical 0) or data at the output to be recirculated into the register (at logical 1).

All four registers use a common (external) Clock input. With the Clock high (1), data is shifted into the registers. Following the negative-going edge of the Clock, data shifting is inhibited and output data appears. Output data is True, delayed 80 bits.

Since the MK 1007 P has zero lag-time requirements for data inputs, devices may be cascaded, i.e., the output of one device may be fed directly to the input of another device. All inputs are protected to prevent damage due to static charge accumulation.

# **FUNCTIONAL DIAGRAM**

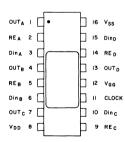

# PIN CONNECTIONS

# **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage, VDD                  | $V_{SS} + 0.3 V \text{ to } V_{SS} - 20 V$ |

|--------------------------------------|--------------------------------------------|

| Supply Voltage, VGG                  | $VSS + 0.3 V$ to $VSS - 20 V$              |

| Voltage at any Input or Output       | $VSS + 0.3 V$ to $VSS - 20 V$              |

| Operating Free-Air Temperature Range | 0°C to +75°C                               |

| Storage Temperature Range (Ceramic)  |                                            |

| Storage Temperature Range (Plastic)  |                                            |

# RECOMMENDED OPERATING CONDITIONS

$(0^{\circ}C \leq T_A \leq 75^{\circ}C)$

|        |                  | PARAMETER                        | MIN                   | TYP   | MAX             | UNITS | COMMENTS                      |

|--------|------------------|----------------------------------|-----------------------|-------|-----------------|-------|-------------------------------|

| 8      | V <sub>ss</sub>  | Supply Voltage                   | 4.75                  | 5.0   | 5.25            | ٧     | $V_{DD} = 0 \text{ V}$        |

| POWER  | V <sub>ee</sub>  | Supply Voltage(I)                | -12.6                 | -12.0 | -11.4           | V     |                               |

| INPUTS | V <sub>IL</sub>  | Logic "0" Voltage, any input     |                       | 0.0   | 0.8             | ٧     |                               |

| Z Z    | V <sub>IH</sub>  | Logic "1" Voltage, any input (2) | V <sub>ss</sub> - 1.5 | +5.0  | V <sub>ss</sub> | V     |                               |

|        | fφ               | Clock Repetition Rate            | .01                   |       | 2.5             | MHz   |                               |

|        | $t_{\phi_p}$     | Clock Pulse Width                | .150                  |       | 100             | μS    | NOTE: Total                   |

| 9      | $t_{\phi_d}$     | Clock Pulse Delay                | .150                  |       | 100             | μS    | permitted clock times will be |

| TIMING | $t_{\phi_r}$     | Clock Pulse Risetime             | .010                  |       | 5               | μS    | determined by                 |

| Ξ      | tφf              | Clock Pulse Falltime             | .010                  |       | 5               | μS    | clock frequency, $f_{\phi}$ . |

| INPUT  | t <sub>dld</sub> | Data Leadtime                    | 150                   |       |                 | ns    |                               |

|        | t <sub>dig</sub> | Data Lagtime                     | 0                     |       |                 | ns    |                               |

|        | t <sub>rid</sub> | Recirculate Control Leadtime     | 200                   |       |                 | ns    |                               |

|        | t <sub>rig</sub> | Recirculate Control Lagtime      | 50                    |       |                 | ns    |                               |

# **ELECTRICAL CHARACTERISTICS**

(Vss  $= +5 \pm 0.25$  V, Vee  $= -12 \pm 0.6$ V, VDD = 0 V, TA = 0°C to +75°C, unless otherwise specified.)

|               | PARAMETER         |                                                                                                            |                     | TYP(3)      | MAX          | UNITS    | CONDITIONS                                         |

|---------------|-------------------|------------------------------------------------------------------------------------------------------------|---------------------|-------------|--------------|----------|----------------------------------------------------|

| POWER         | I <sub>SS</sub>   | V <sub>ss</sub> Power Supply Current <sup>(4)(5)</sup> V <sub>GG</sub> Power Supply Current <sup>(5)</sup> |                     | 22.0<br>9.0 | 40.0<br>16.0 | mA<br>mA | $f_{\phi}=$ 2.5 MHz; outputs open                  |

| ·             | CiN               | Capacitance at Data,<br>RE, and Clock Inputs <sup>(5)</sup>                                                |                     | 3           | 6            | pF       | $V_1 = V_{SS}$ , f $\phi = 1$ MHz                  |

| INPUTS        | I <sub>IL</sub>   | Logic "0" Current, any input(5)                                                                            | 0.6                 | 1.1         | 1.6          | mA       | V <sub>i</sub> =0.4 V                              |

| _             |                   | Leakage Current, any input                                                                                 |                     |             | 1            | μΑ       | $V_1 = V_{SS} - 5.5V$ ; $V_{SS} = V_{DD} = V_{GG}$ |

|               | R <sub>IN</sub>   | Input Pullup Resistance(5)                                                                                 | 3.0                 |             | 8.4          | kΩ       | V <sub>I</sub> =0.4 V                              |

| OUT.          | V <sub>OL</sub>   | Logic "0" Output Voltage(5) Logic "1" Output Voltage(5)                                                    | V <sub>ss</sub> - 1 |             | 0.4          | V<br>V   | $I_L = -1.6 \text{ mA}$ $I_1 = +100 \mu \text{A}$  |

|               |                   | Output Delay, Low to High                                                                                  | V <sub>SS</sub> - I | 75          | 200          | ns       | η 100 μ/ ·                                         |

| DYN.<br>CHAR. | t <sub>DLH</sub>  | Output Delay, High to Low                                                                                  |                     | 75          | 200          | ns       | See Timing Diagrams                                |

| es .          | P <sub>D(1)</sub> | Power Dissipation <sup>(4)</sup>                                                                           |                     | 220         |              | mW       | $f\phi=2.5~\mathrm{MHz}$                           |

|               | P <sub>D(2)</sub> |                                                                                                            |                     | 195         |              | mW       | $f\phi = 1 \text{ MHz}$                            |

|               | P <sub>D(3)</sub> | Power Dissipation <sup>(4)</sup>                                                                           |                     | 170         |              | mW       | $f\phi = 10 \text{ kHz}$                           |

# NOTES:

(1) Other supply voltages are permissible providing that supply and input voltages are adjusted to maintain the same potential relative to V<sub>ss</sub>, e.g., V<sub>ss</sub> = 0 V, V<sub>oo</sub> = -5V, V<sub>ee</sub> = -17 V.

(2) Pull-up resistances to +5V are provided internally.

(3) Typical values at T<sub>A</sub>=25°C, V<sub>ss</sub> = +5.0 V, V<sub>oo</sub> = -12.0 V.

(4) I<sub>ss</sub> will increase a maximum of 1.6 mA for each input at logic "0."

(5) At: T<sub>A</sub>=25°C.

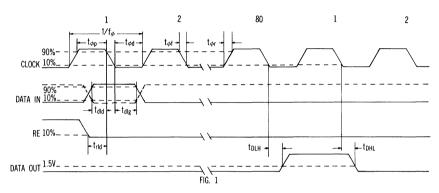

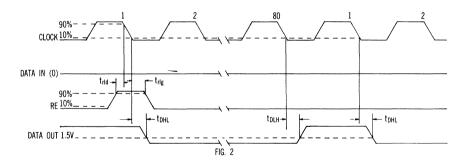

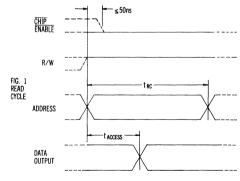

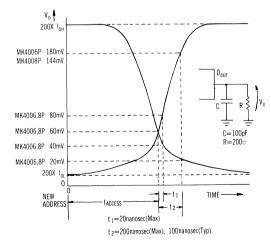

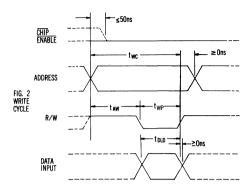

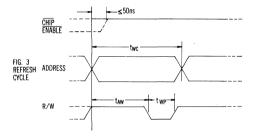

### TIMING

# **CONDITIONS:**

- 1. All timing relationships apply to any of the four registers.

- 2. Logic 0 is defined as  $V_{DD}$  or ground; logic 1 as  $V_{SS}$  or +5V.

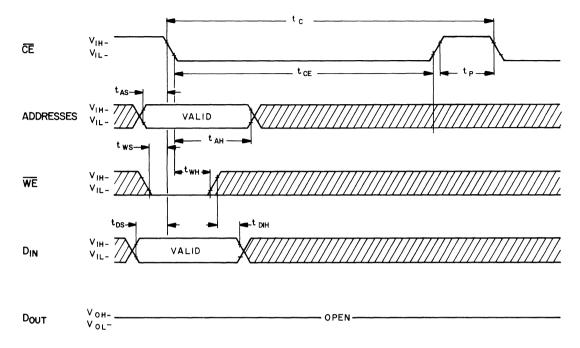

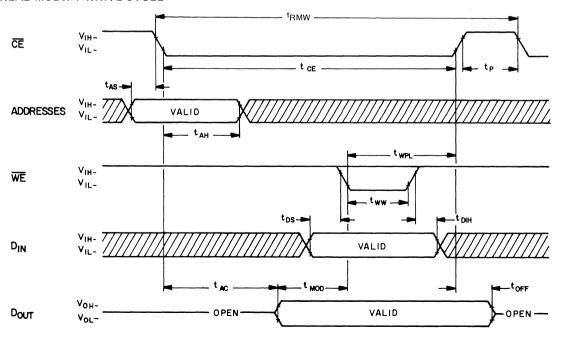

**SHIFT:** Fig. 1 illustrates shifting a logic 1 bit from the Data Input ( $D_{\rm in}$ ) through one of the 80-bit registers. RE (Recirculate Enable) at logic 0 enables  $D_{\rm in}$ . RE must go to logic 0 for  $t_{\rm rld}$  time (Recirculate Control Leadtime) prior to the Clock's negative edge, and must maintain that state at least until the Clock's negative edge ( $t_{\rm dlg}$ ) to insure proper data shifting. This data bit entered will appear 80 clock pulses later within Output Delay Time ( $t_{\rm p}$ ) of that Clock's negative edge.

**RECIRCULATE:** Fig. 2 illustrates recirculating a bit present at the output back through the register. RE must attain a logic 1 for  $t_{\rm rld}$  time (Recirculate Control Leadtime) prior to the Clock's negative edge, and must maintain that state at least until the Clock's negative edge  $(t_{\rm rlg})$  to insure proper data recirculation. The bit entered will appear 80 clocks later as shown.

### APPLICATIONS

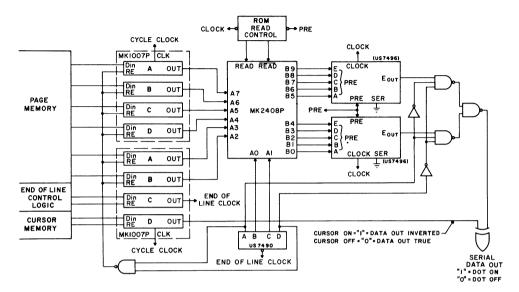

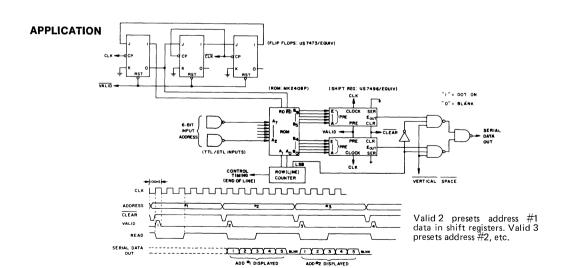

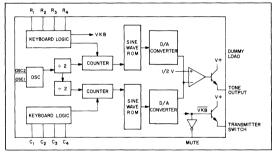

# LINE REFRESH MEMORY FOR CRT DISPLAY

This application shows the MK 1007 P used as the Line Refresh Memory, driving MOSTEK's MK 2408 P TTL-compatible character generator. The MK 1007 P receives new data from the Page Memory (which may also consist of MK 1007 P's) on the tenth row of any character line, this being the third vertical space between rows of characters. The MK 1007 P recirculates the character-address data as these characters are scanned and displayed on a CRT screen.

The decade counter selects the appropriate rows from the character generator which outputs two

rows of the addressed character at one time (see MK 2408 P data sheet), and also controls the multiplexed output of the character generator so that only one row of the addressed characters is displayed on any CRT horizontal sweep.

One stage of the MK 1007 P may be used to shift a single data bit, which may be used to determine the end of the horizontal sweep. Another stage may be used as a cursor control and, as shown above, may blank the cursored character dots while surrounding dots are on, to give a reverse image of that particular character.

# **OPERATING NOTES**

- Recirculate Enable (RE) = Logic 1 = output data recirculated.

- Output data (delayed 80 bits) maintains same logic state when RE = 1.

- 3. Recirculate Enable (RE) = Logic 0 = Data In  $(D_{in})$  enabled.

- Output data (delayed 80 bits) attains same logic state as D<sub>in</sub> when RE = 0.

- Output data follows the clock negative edge.

# **TEST CIRCUIT**

# **READ ONLY MEMORIES**

# MOSTEK

# 2240-BIT ROM CHARACTER GENERATORS

# MK 2300/ 2302 P/N

## **FEATURES**

- Ion-implantation processing for full TTL/DTL compatibility

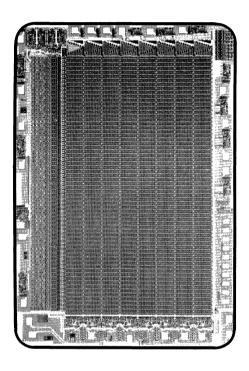

- 2240 bits of storage organized as 64 5x7 dot matrix characters with column-by-column output

- MK 2302 P is pre-programmed with ASCII encoding

- Internal counter provides clocked column selection

# DESCRIPTION

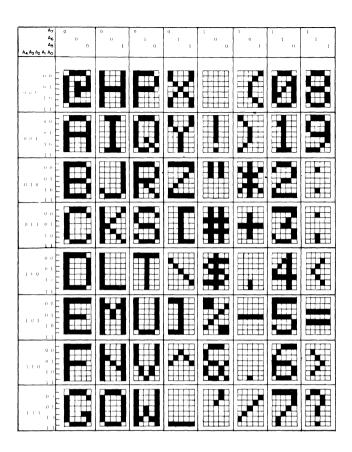

The MK 2300 P Series MOS, TTL/DTL-compatible read-only memories (ROMs) are designed specifically for dot-matrix character generation. Each ROM provides 2240 bits of programmable storage, organized as 64 characters each having 5 columns of 7 bits. A row output capability of 64 7x10 characters is possible, as illustrated on the back page.

Low threshold-voltage processing, utilizing ionimplantation, is used with P-channel, enhancementmode MOS technology to provide direct input/ output interface with TTL and DTL logic families. All inputs are protected to prevent damage from static charge accumulation.

The MK 2302 P is preprogrammed with ASCIIencoded characters (font shown on back page). Other ROMs in the series are programmed during manufacture to customer specifications by modification of a single mask.

Characters are selected by a six-bit binary word at the Character Address inputs. Each character consists of five columns, the columns selected by an internal

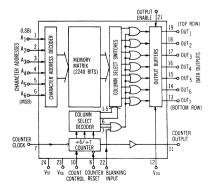

# **FUNCTIONAL DIAGRAM**

- Counter output for updating external character address registers

- Internal provision for one- or two-column intercharacter spacing

- Output enable and blanking capability

- $\square$  Operates from +5V and -12V supplies

counter which is clocked by the Counter Clock input. Column information appears sequentially beginning with the left-most column. Two additional intercharacter spacing columns are available, selectable for one or two spaces by the Count Control Input. During the spacing, the Data Outputs are high (+5V), or the "dot-off" condition. After the last space, the modulo counter automatically increments to the leftmost column.

Synchronizing other system components with the ROM is possible using the Counter Reset Input to reset the counter to the last intercharacter spacing column, or using the Counter Output which occurs only on the last spacing column.

The Blanking Input allows all Data Outputs to be driven high (+5V) without affecting any other ROM functions. The Output Enable input allows the outputs to be open-circuited for wire-ORing.

Memory operation is static; refresh clocks are not required to maintain output information. The Clock input is used only to select columns and need not be pulsed continuously.

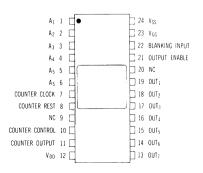

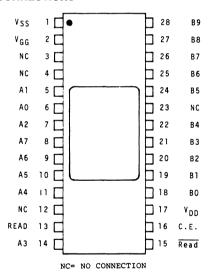

### PIN CONNECTIONS

NC = NO CONNECTION

# **ABSOLUTE MAXIMUM RATINGS**

| Voltage on any terminal relative to Vss | 1 + 0.3V to $-20V$               |

|-----------------------------------------|----------------------------------|

| Operating temperature range             | $0^{\circ}$ C to $+75^{\circ}$ C |

| Storage temperature (Ambient) Ceramic   | –65°C to + 150°C                 |

| Storage temperature (Ambient) Plastic   | $\dots$ –55°C to + 125°C         |

# RECOMMENDED OPERATING CONDITIONS ( $0^{\circ}C \le T_{A} \le 75^{\circ}C$ )

|                |                                                                                                                      | PARAMETER                                                                                                                                                  | MIN                       | TYP                  | MAX                 | UNITS                                   | COMMENTS                                                                                                                 |

|----------------|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------------------|---------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| POWER          | V <sub>SS</sub><br>V <sub>DD</sub><br>V <sub>GG</sub>                                                                | Supply voltage<br>Supply voltage<br>Supply voltage                                                                                                         | +4.75<br><br>-12.6        | +5.0<br>0.0<br>-12.0 | +5.25<br>—<br>—11.4 | V<br>V<br>V                             | See note 1                                                                                                               |

| INPUTS         | V <sub>in(0)</sub><br>V <sub>in(1)</sub><br>V <sub>in(cc)</sub>                                                      | Input voltage, logic "0" Input voltage, logic "1" Count Control input voltage, ÷ 6 ÷ 7                                                                     | Vss — 1.5<br>+ 4.75       | 12.0<br>+ 5.0        | +0.6<br>-11.4       | V V V                                   | See note 2 Count control input should be returned to $V_{GG}$ for $\div$ 6 operation, or $V_{SS}$ for $\div$ 7 operation |

| COUNTER TIMING | $\begin{aligned} &f_{clk}\\ &t_{clk(0)}\\ &t_{clk(1)}\\ &t_{(clk)}\\ &t_{f(clk)}\\ &t_{rp}\\ &t_{crd} \end{aligned}$ | Counter Clock input frequency Clock time at logic "0" Clock time at logic "1" Clock rise time Clock fall time Reset pulse width Clock-to-reset pulse delay | 0<br>2<br>2<br>1.0<br>0.4 |                      | 0.1<br>0.1          | kHz<br>μs<br>μs<br>μs<br>μs<br>μs<br>μs | See timing<br>diagrams<br>See note 4                                                                                     |

# **ELECTRICAL CHARACTERISTICS**

$(V_{SS} = +5.0V \pm 0.25V, V_{GG} = -12.0V \pm 0.6V, 0^{\circ}C \le T_{\Lambda} \le +75^{\circ}C,$  unless noted otherwise)

|                 | unless noted otherwise) |                                    |     |      |      |       |                                                                                                               |  |

|-----------------|-------------------------|------------------------------------|-----|------|------|-------|---------------------------------------------------------------------------------------------------------------|--|

|                 |                         | PARAMETER                          | MIN | TYP⁺ | MAX  | UNITS | CONDITIONS                                                                                                    |  |

| POW             | I <sub>ss</sub>         | Supply current (Vss)               |     | 20   | 40   | mA    | Outputs unconnected                                                                                           |  |

| ۵               | I <sub>GG</sub>         | Supply current (V <sub>GG</sub> )  |     | 20   | 40   | mA    | f <sub>c1k</sub> = 200 kHz                                                                                    |  |

| JTS             | C <sub>in</sub>         | Input capacitance                  |     |      | 10   | pF    | $V_{in} = V_{SS}$ , $f_{meas} = 1MHz$                                                                         |  |

| INPUTS          | l <sub>in</sub>         | Input leakage current              |     |      | 10   | μΑ    | $V_{in} = V_{SS}$ , Theat $IV_{in} = V_{SS} - 6V$ , $T_A = 25^{\circ}C$ note 2                                |  |

|                 | $V_{out(0)}$            | Output voltage, logical "0"        |     | 0.2  | 0.4  | V     | $I_{out} = 2.0 \text{ mA}$ (into output) See                                                                  |  |

| OUTPUTS         | V <sub>out(1)</sub>     |                                    | 2.4 |      |      | ٧     | $ \begin{array}{ll} I_{\text{out}} = 0.6 \text{ mA} & \text{note} \\ \text{(out of output)} & 3 \end{array} $ |  |

| 00              | lout                    | Data Output leakage current        | -10 |      | + 10 | μΑ    | $V_{SS} - 6V \le V_{out} \le V_{SS}$<br>$T_A = 25^{\circ}C$ (outputs disabled)                                |  |

| CHARACTERISTICS | t <sub>AO</sub>         | Address-to-output delay time       |     |      | 1    | μs    |                                                                                                               |  |

| IST             | tco                     | Clock-to-output delay time         | 1   |      | 1    | μs    | Rise and fall                                                                                                 |  |

| 띮               | tcco                    | Clock-to-counter output delay time |     |      | 1    | μs    | times included See timing                                                                                     |  |

| Ϋ́              | t <sub>BO</sub>         | Blanking/unblanking delay time     |     |      | 1    | μs    | in delay times diagrams                                                                                       |  |

| AR              | toeo                    | Output enable/disable delay time   |     |      | 1    | μs    |                                                                                                               |  |

| ᇴ               | tcRO                    | Counter reset delay time           |     |      | 1    | μs    | $R_L = 4 k\Omega$ to $V_{SS}$                                                                                 |  |

| ≌               | t <sub>CRCO</sub>       | Reset-to-counter output delay time |     |      | 1    | μs    | $C_L = 15 \text{ pF to } V_{DD}$                                                                              |  |

| Α¥              | t <sub>F</sub>          | Output fall time                   |     |      | 0.3  | μs    | T <sub>A</sub> = 25°C                                                                                         |  |

| DYNAMIC         | t <sub>R</sub>          | Output rise time                   |     |      | 0.3  | μs    |                                                                                                               |  |

<sup>\*</sup>Typical values apply at  $V_{55} = +5.0V$ ,  $V_{66} = -12.0V$ ,  $T_A = 25^{\circ}C$

NOTES: 1. Supply voltages shown are for operation in a TTL/DTL system. Other supply voltages may be used if  $V_{DD}$  and  $V_{GG}$  maintain the same relationship to  $V_{SS}$ , e.g.,  $V_{SS}$ = OV,  $V_{DD}$ = -5V,  $V_{GG}$  -17V. Input voltages would also need to be adjusted accordingly.

- 2. These parameters apply to the character address, counter clock, counter reset, blanking, and output enable inputs.

- 3. These parameters apply to both the data outputs and counter output.

- 4. The counter clock must not make a negative transition within the period tord, before or after a positive counter reset transition. The counter reset negative edge may occur any time.

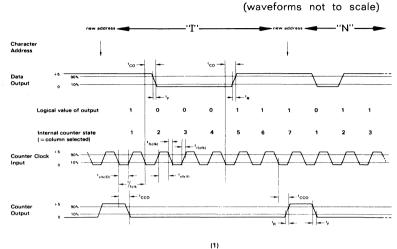

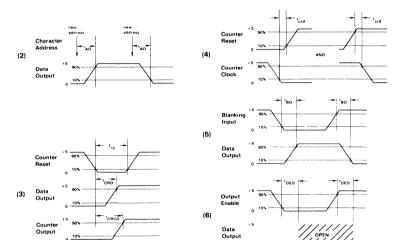

### TIMING

Timing diagram (1)\* shows the time relationships between character address, data output, counter clock, and counter output during typical operation of an MK 2300 P Series character generator. An output sequence from the MK 2302 P is shown to help clarify operation. This sequence can be seen from the top rows (OUT.) of the characters "I" and "N".

All timing relationships shown in diagram (1) apply to any other output or combination of characters as well.

Relevant input conditions assumed but not shown in timing diagram (1) are as follows:

Count Control, +5V Counter Reset, +5V Blanking Input, +5V Output Enable, +5V

Had the Count Control input been at -12V, the counter sequence would have been six positions instead of seven and the Counter Output would have been high during the sixth positions.

New character addresses are shown coinciding with the rising edge of the Counter Output waveform in diagram (1). This condition was selected to demonstrate use of the Counter Output to advance an external input register to a new character address. Character addresses can be changed at any other time as well. Timing diagram (2) depicts output response to a character address change when, for example, the counter is stationary in one of the five character column positions.

Timing diagrams (3) through (6) show timing relationships for the Counter Reset, Blanking Input, and Output Enable. The "open" condition in (6) implies that both the pull-up and pull-down devices in each data output push-pull buffer are turned off.

# **OPERATING NOTES**

The following table summarizes the MK 2300 P Series input control states and corresponding drive levels:

| Count Control  |      |

|----------------|------|

| <del>÷</del> 6 | -12V |

| <del>÷</del> 7 | + 5V |

| Counter Reset  |      |

| operate        | +5V  |

| reset          | 0V   |

| Blanking Input |      |

| unblank        | +5V  |

| blank*         | 0V   |

| Output Enable  |      |

| enable         | +5V  |

| disable**      | 0V   |

\*All data outputs high (+5V)

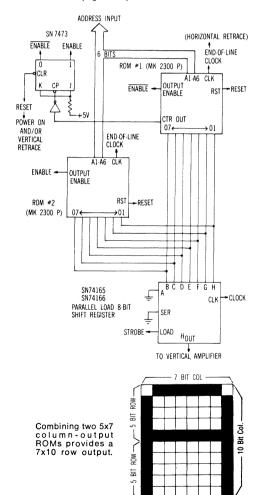

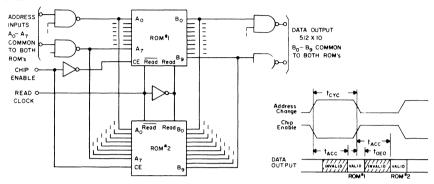

# APPLICATION: 7x10 CHARACTER GENERATOR

### ROM CODING

7x10 Non-Interlace Configuration: (As illustrated) For row-out (7-bit) horizontal raster-scan application, code ROM #1 for Rows 1 through 5; and ROM #2 for Rows 6 through 10.

7x10 Interlace (525-line): Code ROM #1 for Rows 1, 3, 5, 7, 9; Code ROM #2 for Rows 2, 4, 6, 8, 10. The Enable Flip-flop should be changed to clock only at vertical retrace time, thus allowing ROM #1 to be enabled for the 1st page sweep (262 ½ lines) and then allowing ROM #2 to be enabled for the interlaced 2nd page sweep of 262 ½ lines.

# MK 2302 P

Logic 1 = input @ +5VLogic 0 = input @ -0VOutput dot "on" = -0VOutput dot "off" = -5V

| A | A <sub>3</sub> | A <sub>2</sub> | A, | A <sub>6</sub> A <sub>5</sub> | 1 ( | 1          | 1 | 0 | 0 | 0 | 1 |

|---|----------------|----------------|----|-------------------------------|-----|------------|---|---|---|---|---|

| 0 | 0              | 0              | 0  |                               |     |            |   |   |   |   |   |

| 0 | 0              | 0              | 1  |                               |     |            |   |   |   |   |   |

| 0 | 0              | 1              | 0  |                               |     |            |   | = |   |   |   |

| 0 | 0              | 1              | 1  |                               |     |            |   |   |   |   |   |

| 0 | 1              | 0              | 0  |                               |     |            |   |   |   |   |   |

| 0 | 1              | 0              | 1  |                               |     |            |   | 8 |   |   |   |

| 0 | 1              | 1              | 0  |                               | 8   |            |   |   |   |   |   |

| 0 | 1              | 1              | 1  |                               |     |            |   |   |   |   |   |

| 1 | 0              | 0              | 0  |                               |     |            |   |   |   |   |   |

| 1 | 0              | 0              | 1  |                               |     |            |   |   |   |   |   |

| 1 | 0              | 1              | 0  |                               |     |            |   |   | Ī |   |   |

| 1 | 0              | 1              | 1  |                               |     | <b>=</b> H |   |   |   |   |   |

| 1 | 1              | 0              | 0  |                               |     |            |   |   |   |   |   |

| 1 | 1              | 0              | 1  |                               |     |            |   |   |   |   |   |

| 1 | 1              | 1              | 0  |                               |     |            |   |   |   |   |   |

| 1 | 1              | 1              | 1  |                               |     |            |   |   | ŀ |   |   |

- 7 Bit Row

# MOSTEK ROM PUNCHED-CARD CODING FORMAT'

| MK 2300 P      |                                                       | Fourth Card  |                                |  |  |  |

|----------------|-------------------------------------------------------|--------------|--------------------------------|--|--|--|

| Cols.          | Information Field                                     | 1-6          | Data Format3 "MOSTEK"          |  |  |  |

| First Card     |                                                       | 15-28        | Logic⁴— "Positive Logic" or    |  |  |  |

| 1-30           | Customer                                              | 35-57        | Verification Code <sup>5</sup> |  |  |  |

| 31-50<br>60-72 | Customer Part Number  Mostek Part Number <sup>2</sup> | Data Cards 4 |                                |  |  |  |

| 00 12          | Model Fart Hamber                                     | 1-6          | Binary Address                 |  |  |  |

| Second         | d Card                                                | 8-12         | First row of character         |  |  |  |

|                |                                                       | 14-18        | Second row of character        |  |  |  |

| 1-30           | Engineer at Customer Site                             | 20-24        | Third row of character         |  |  |  |

| 31-50          | Direct Phone Number for Engineer                      | 26-30        | Fourth row of character        |  |  |  |

|                |                                                       | 32-36        | Fifth row of character         |  |  |  |

| Third (        | Card                                                  | 38-42        | Sixth row of character         |  |  |  |

| 1-5<br>10-15   | Mostek Part Number <sup>1</sup>                       | 44-48        | Seventh row of character       |  |  |  |

Notes: 1. Assigned by Mostek Marketing Department; may be left blank.

- 2. Punched as 64x5x7.

- 3. "MOSTEK" format only is accepted on this part.

- 4. A dot "ON" should be coded as a "1".

- Punched as: (a) VERIFICATION HOLD i.e. the customer verification of the data as reproduced by MOSTEK is required prior to production of the ROM. To accomplish this MOSTEK supplies a copy of its Customer Verification Data Sheet (CVDS) to the customer.

- (b) VERIFICATION PROCESS i.e. the customer will receive a CVDS but production will begin prior to receipt of customer verification.

- (c) VERIFICATION NOT NEEDED i.e. the customer will not receive a CVDS and production will begin immediately.

# 2560x1 BIT STATIC ROM

# MK 2400 P

### **FEATURES**

- ☐ Ion-implanted for full TTL/DTL compatibility

- □ Chip enable permits wire-ORing

- Custom-programmed memory requires single mask modification

- □ 550 ns cycle time  $(0^{\circ} \le T_{A} \le 75^{\circ}C)$

- ☐ Static output storage latches

- Optional 3-bit, chip-select decoder available

- 2560 bits of storage, organized as 256 10-bit words

- □ Operates from +5V and −12V supplies

# DESCRIPTION

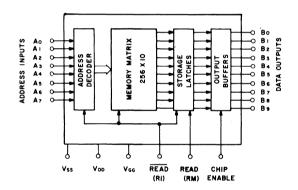

The MK 2400 P Series TTL/DTL-compatible MOS Read-Only Memories (ROM's) are designed for a wide range of general-purpose memory applications where large quantity bit storage is required. Each ROM provides 2560 bits of programmable storage, organized as 256 words of 10 bits each. Low threshold-voltage processing, utilizing ion implantation with P-channel enhancement-mode MOS technology, provides direct input/output interface with TTL and DTL logic.

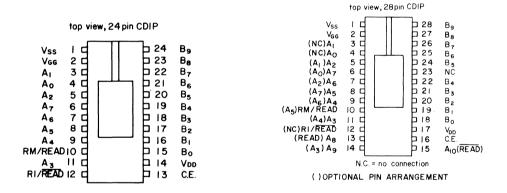

Programming is accomplished during manufacture by modification of a single mask, according to customer specifications. The MK 2400 P Series is available in either 24-lead or 28-lead ceramic dual-in-line packages. On the 28-pin ROM, an optional Chip Select Decoder may also be programmed according to customer specifications to provide a 3-bit Chip Select Code.

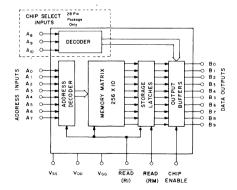

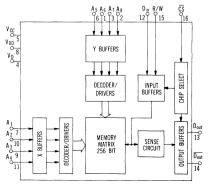

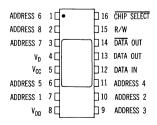

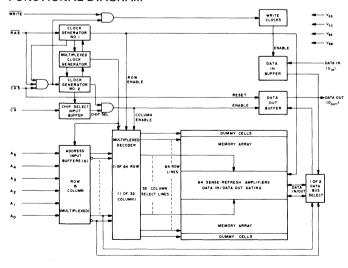

### **FUNCTIONAL DIAGRAM**

Operation involves transferring addressed information from the memory matrix into the storage latches using the READ and READ inputs (see Timing). Information stored in the latches will remain despite address changes or chip disabling until the READ and READ inputs are again cycled. READ and READ input signals may be generated from separate timing circuits if desired, or either may be the inverse of the other.

The Chip Enable input forces the normally pushpull output buffer stages to an open-circuit condition when disabling the chip. If desired, new data can be stored in the storage latches while the chip is disabled. When the chip is reenabled, this data would be present at the outputs.

All inputs are protected against static charge accumulation. Pull-up resistors on all inputs are available as a programmable option.

# **OPERATING NOTES**

| CHIP<br>ENABLE | READ | READ | OUTPUT |

|----------------|------|------|--------|

| 0              | Х    | Х    | Α      |

| 1              | 0    | 1    | В      |

| 1              | 1    | 0    | С      |

"1" =  $V_{SS}$  (+5V): "0" =  $V_{DD}$  (0V)

X = No effect on output

A = Output open-circuited

B = Output retains data last stored in latches

C = Output assumes state of addressed cells

| Voltage on any terminal relative to Vss | +0.3V to $-10V$                  |

|-----------------------------------------|----------------------------------|

| Operating temperature range             | $0^{\circ}$ C to $+75^{\circ}$ C |

| Storage temperature range               | 5°C to +150°C                    |

# RECOMMENDED OPERATING CONDITIONS ( $0^{\circ}C \leq T_A \leq 75^{\circ}C$ )

|              |                                                                                                          | PARAMETER                                                                                                                                                       | MIN                                  | TYP                  | MAX                      | UNITS                            | COMMENTS                                                                                   |

|--------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------|--------------------------|----------------------------------|--------------------------------------------------------------------------------------------|

| POWER        | V <sub>SS</sub><br>V <sub>DD</sub><br>V <sub>GG</sub>                                                    | Supply voltage<br>Supply voltage<br>Supply voltage                                                                                                              | +4.75<br><br>-12.6                   | +5.0<br>0.0<br>-12.0 | +5.25<br>—<br>—11.4      | \<br>\<br>\<br>\                 | See note 1                                                                                 |

| INPUTS       | ' '                                                                                                      | Input voltage, logic "0"<br>Input voltage, logic "1"                                                                                                            | V <sub>ss</sub> — 1.5                | 0<br>Vss             | +0.8                     | \<br>\<br>\                      | Pull-up resistors ( $\approx$ 5K $^{\sim}$ ) to $V_{SS}$ available as programmable option. |

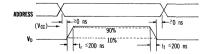

| INPUT TIMING | $\begin{array}{c} t_{cyc} \\ t_{Id} \\ t_{Ig1} \\ t_{Ig2} \\ t_{rd} \\ t_{rd} \\ t_r \\ t_f \end{array}$ | Address change cycle time Address to Read lead time Read lag time 1 Read lag time 2 Read pulse width Read pulse width Rise time, any input Fall time, any input | 550<br>250<br>05<br>05<br>300<br>0.3 |                      | .05<br>.05<br>100<br>100 | ns<br>ns<br>μs<br>μs<br>ns<br>ns | See<br>Timing<br>Section                                                                   |

# **ELECTRICAL CHARACTERISTICS**

(Vss = +5.0V  $\pm 0.25V$ , V<sub>GG</sub> = -12.0V  $\pm 0.6V$ , 0°C  $\leq$ T<sub>A</sub>  $\leq +75$ °C, unless noted otherwise. Pull-up resistors not programmed.)

|         | PARAMETER                                                                         |                                                                                                                                      |             | TYP*     | MAX                                           | UNITS                | CONDITIONS                                                                                                                                                                                                                                                                                            |

|---------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------|----------|-----------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER   | ı                                                                                 | Supply current (Vss)<br>Supply current (VGG)                                                                                         |             | 12<br>12 | 25<br>25                                      | mA<br>mA             | Outputs unconnected<br>See Note 2 and Note 3                                                                                                                                                                                                                                                          |

| INPUTS  | C <sub>in</sub>                                                                   | Input capacitance<br>Input leakage current                                                                                           |             | 5        | 10<br>10                                      | pF<br>μA             |                                                                                                                                                                                                                                                                                                       |

| OUTPUTS | 1 '                                                                               | Output voltage, logical "0" Output voltage, logical "1" Output leakage current                                                       | 2.4<br>- 10 |          | 0.4                                           | V<br>V<br>μΑ         | $\begin{array}{ll} I_{\text{out}} = 1.6 \text{ mA (into output)} & See \\ I_{\text{out}} = 0.4 \text{ mA} & 3 \\ \text{(out of output)} & \text{and} \\ V_{\text{SS}} - 6V \leq V_{\text{out}} \leq V_{\text{SS}} & \#1 \\ T_{\text{A}} = 25^{\circ}\text{C} & \text{(outputs disabled)} \end{array}$ |

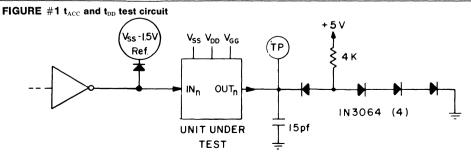

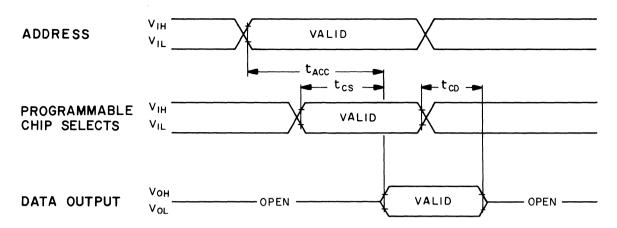

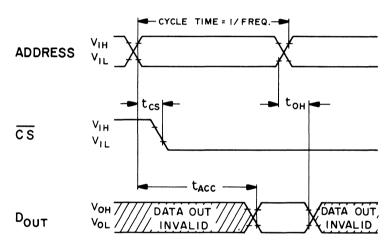

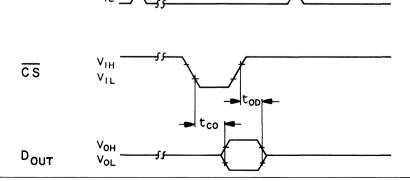

| DYNAMIC | t <sub>ACC</sub> t <sub>OD</sub> t <sub>OEO</sub> t <sub>CS</sub> t <sub>CD</sub> | Address-to-output access time Output delay time Output enable/disable time Chip Select to Output Delay Chip Deselect to Output Delay |             | 125      | 600<br>350<br>300<br><b>600</b><br><b>600</b> | ns<br>ns<br>ns<br>ns | $\begin{array}{l} t_{\rm id} = 250 ns \\ t_{\rm ig} = 0 \\ t_{\rm ig2} = 0 \\ \text{See note 4} \end{array}  \begin{array}{l} \text{See timing} \\ \text{Section} \\ \text{and Figure } \#1 \end{array}$                                                                                              |

<sup>\*</sup>Typical values apply at  $V_{SS} = +5.0V$ ,  $V_{GG} = -12.0V$ ,  $T_A = 25$ °C

NOTES: 1. Supply voltages shown are for operation in a TTL/DTL system. Other supply voltages may be used if  $V_{0D}$  and  $V_{66}$  maintain the same relationship to  $V_{55}$ , e.g.,  $V_{55} = 0V$ ,  $V_{0D} = -5V$ ,  $V_{66} = -17V$ . Input voltages would also need to be adjusted accordingly.

<sup>2.</sup> Max measurements at 0°C. (MOS supply currents increase as temperature decreases.) Iss will increase 1.6mA (max) for each input at logic 0 when pull-up resistors are programmed.

<sup>3.</sup> Unit operated at minimum specified cycle time.

<sup>4.</sup> The outputs become open circuited when disabled or deselected. As shown in Fig. 1, an output with a "1" expected out does not transition through the 1.5V point when enabled (selected) or disabled (deselected); this is true because the TTL equivalent load pulls the open-circuited output to approximately 2 volts.

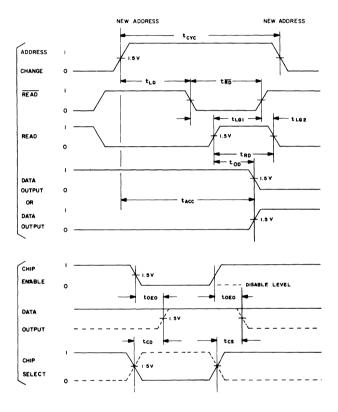

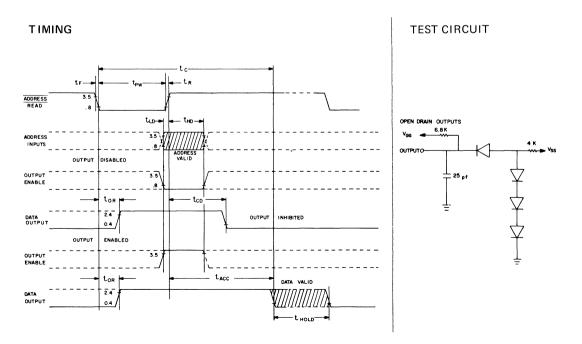

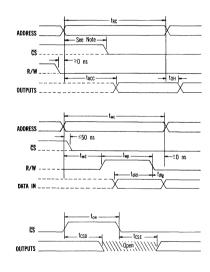

# **TIMING**

Notes:

- 1. All times are referenced to the 1.5V point relative to  $V_{\text{DD}}$  (ground) except rise and fall time measurements.

- 2. Chip enable =  $V_{SS}$  for all measurements except when measuring  $T_{\text{OEO}}$ .

- 3. Logic 0 is defined as  $V_{\text{DD}}$  or ground; logic 1 as  $V_{\text{SS}}$  or  $+5\text{V}_{\cdot}$

# INTERNAL FUNCTION OF READ/ READ SIGNALS

Set up time, tid, allows the input address to propagate through the address decoder and memory matrix prior to READ logic 0 time. As indicated above, READ at a logic 0 internally disables the input address so that an external address change may occur without affecting the location previously selected. The latches are also readied to receive new data which is enabled from the matrix when READ is at a logic 1. Data is set in the latches when READ is allowed to rise back to its logic 1 state. In actual use, the READ rising and falling edges can precede the falling and rising edges of READ, respectively, as implied by the specification of negative read lag times. This allows a very flexible timing relation between the two pulses, in that either input can be the inversion of the other or both may be generated from separate timing circuits.

Output data appears following the rise of the READ pulse but correct output data will not appear until READ has gone low. For this reason, READ is shown preceding READ even though other relationships are allowed. If READ is made to precede READ, delay time, top, should be referenced to the fall of READ rather than as shown.

The chip is disabled by applying a logical 0 to the chip enable input, forcing the outputs to an open-circuit condition. The output data present at the time of disable will again be present upon re-enabling unless a new read cycle was initiated for a different address while the chip was disabled, in which case the new data would be present at the outputs.

The programmable 3-bit chip select timing would be the same as the address inputs.

NOTE: Wave forms are not to scale.

# **APPLICATIONS**

Application shows wire-Or'ing for expansion to a 512 X 10 memory. Further expansion is possible by 1 of N decoding to the Chip Enable input (or with the optional 3-bit decoder) while maintaining the time relationships shown.  $t_{\rm cyc}$  should include the desired data-valid time. Interface devices may be TTL or DTL.

# **PIN CONNECTIONS**

# **PIN CONNECTIONS**

# MOSTEK ROM PUNCHED-CARD CODING FORMATI

| IVIIV ETU      |                                                         |        |                                  |

|----------------|---------------------------------------------------------|--------|----------------------------------|

| Cols.          | Information Field                                       |        | "Negative Logic"                 |

| First Ca       | ard                                                     | 35-57  | Verification Code <sup>7</sup>   |

| 1-30           | Customer                                                | 60-74  | Package Choice®                  |

| 31-50<br>60-72 | Customer Part Number<br>Mostek Part Number <sup>2</sup> | Data C | ards                             |

|                |                                                         | 1-3    | Decimal Address                  |

| Second         | l Card                                                  | 5      | Output B9                        |

| 1-30           | Engineer at Customer Site                               | 6      | Output B8                        |

| 31-50          | Direct Phone Number for Engineer                        | 7      | Output B7                        |

|                |                                                         | 8      | Output B6                        |

| Third C        | Card                                                    | 9      | Output B5                        |

| 1-5            | Mostek Part Number <sup>2</sup>                         | 10     | Output B4                        |

| 10-16          | Organization <sup>3</sup>                               | 11     | Output B3                        |

| 29             | A8 <sup>4</sup>                                         | 12     | Output B2                        |

| 30             | A9⁴                                                     | 13     | Output B1                        |

| 31             | A10⁴                                                    | 14     | Output B0                        |

| 32             | Pull-up Resistor⁵                                       | 16     | Octal Equivalent of: B99         |

|                | •                                                       | 17     | Octal Equivalent of: B8, B7, B69 |

| Fourth         | Card                                                    | 18     | Octal Equivalent of: B5, B4, B39 |

| 0-6            | Data Format⁴ — "MOSTEK"                                 | 19     | Octal Equivalent of: B2, B1, B09 |

| 15-28          | Logic — "Positive Logic" or                             |        |                                  |

Notes: 1. Positive or negative logic formats are accepted as noted in the fourth card.

- 2. Assigned by Mostek Marketing Department; may be left blank.

- 3. Punched as 0256x10.

- 4. A "0" indicates the chip is enabled by a logic 0, a "1" indicates it is enabled by a logic 1, and a "2" indicates a "Don't Care" condition.

- 5. A "1" indicates pull-ups; a "0" indicates no pull-ups.

- 6. "MOSTEK" format only is accepted on this part.

- 7. Punched as: (a) VERIFICATION HOLD i.e. customer verification of the data as reproduced by MOSTEK is required prior to production of the ROM. To accomplish this MOSTEK supplies a copy of its Customer Verification Data Sheet (CVDS) to the customer.

- (b) VERIFICATION PROCESS i.e. the customer will receive a CVDS but production will begin prior to receipt of customer verification.

- (c) VERIFICATION NOT NEEDED i.e. the customer will not receive a CVDS and production will begin immediately.

- 8. "24 PIN", "28 PIN STANDARD", or "28 PIN OPTIONAL" (left justified to column 60).

- The octal parity check is created by breaking up the output word into groups of three from right to left and creating a base 8 (octal) number in place of these groups. For example the output word 1010011110 would be separated into groups 1/010/011/110 and the resulting octal equivalent number is 1236.

# 2560x1 ROM CHARACTER GENERATOR

# **MK 2408 P**

# DESCRIPTION

The MK 2408 P is a pre-programmed member of the MK 2400 P Series. It is programmed as a dot-matrix character generator (64 characters) with ASCII encoded inputs and row (5-bit) outputs. The MK 2408 P outputs two rows at the same time. Row 1 is available at outputs B9 (left), B8, B7, B6, and B5 (right) while row 2 is available at outputs B4 (left), B3, B2, B1, and B0 (right). Row 3 is available at B9 through B5 while row 4 is available at B4 through B0. Row 5 and row 6 are available at B9 through B5 and B4 through B0. Row 5 and row 6 are available at B9 through B5 and B4 through B0. Row selection is determined by the address combination of bits A0 and A1.

The MK 2408 P meets and operates by the specifications outlined in the MK 2400 P Series data sheet (DS-24001270-2)

The example in Figure 1 demonstrates the correspondence of the device outputs and row select sequence to the 7 x 5 dot-matrix font. The complete character font patterns (truth table) are illustrated on the back. A logic 1 or a DOT represents an input or output voltage equal to Vss (+5V) and a logic 0 or a blank represents a voltage equal to Vop (OV). The eighth row outputs (B4 through B0 when inputs A1 and A0 equal logic 1) are not illustrated since in each case they are equal to all 0's.

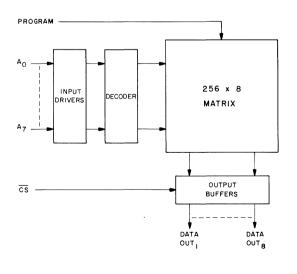

### **FUNCTIONAL DIAGRAM**

### PIN CONNECTIONS

| <u>A1</u> | <u>A0</u> | B9<br><u>B4</u> | B8<br>B3 | B7<br>B2 | B6<br>B1 | B5<br>B0 |       |                  |

|-----------|-----------|-----------------|----------|----------|----------|----------|-------|------------------|

| 0         | 0 _       | 1               | 0        | 0        | 0        | 1        | B9-B5 |                  |

|           | _         | 1               | 1        | 0        | 1        | 1        | B4-B0 | A7 = 0           |

| 0         | 1         | 1               | 0        | 1        | 0        | 1        | B9-B5 | A6 = 0<br>A5 = 1 |

|           |           | 1               | 0        | 1        | 0        | 1        | B4-B0 | A3 - 1           |

| 1         | 0 _       | 1               | 0        | 0        | 0        | 1        | B9-B5 | A4 = 1           |

|           |           | 1               | 0        | 0        | 0        | 1        | B4-B0 | A3 = 0           |

| 1         | 1         | 1               | 0        | 0        | 0        | 1        | B9-B5 | A2 = 1           |

|           | _         | 0               | 0        | 0        | 0        | 0        | B4-B0 |                  |

|           |           |                 | F        | IGURI    | 2 1      |          |       |                  |

# **CODING & CHARACTER FONTS**

# 4096x1 BIT STATIC ROM

# MK 2500/2600 P

### **FEATURES**

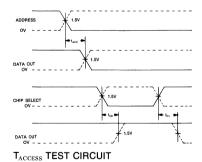

- $\hfill\Box$  High-speed, static operation 400 nsec. typical access time

- □ Active input pull-ups provide worst-case TTL compatibility

- Push-pull outputs provide three output states: one, zero, and open

- □ Ion-implantation for constant current loads and lower power

- ☐ Standard power supplies: +5V, -12V

- ☐ MK 2500 P is pin-for-pin replacement for National 5232

- ☐ MK 2600 P is pin-for-pin replacement for Fairchild 3514

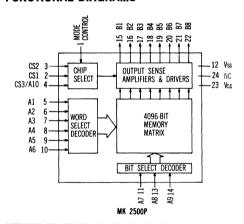

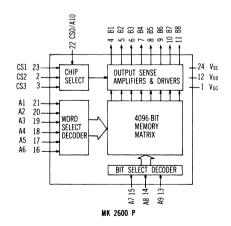

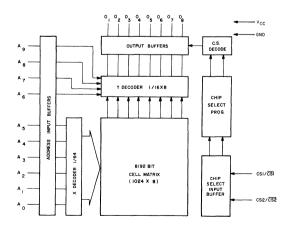

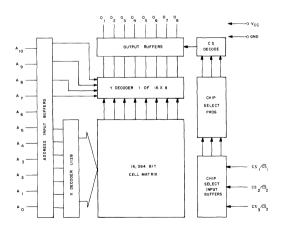

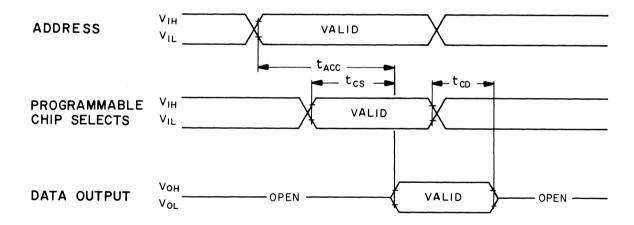

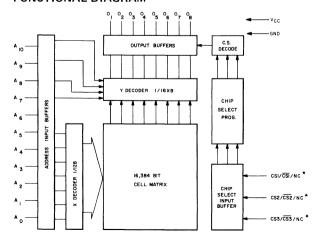

### DESCRIPTION

The MK 2500 P and MK 2600 P series of TTL/DTL compatible MOS read-only memories (ROMs) are designed to store 4096 bits of information by programming one mask pattern. The word and bit organization of these ROM series is either 512W X 8B or 1024W X 4B.

The MK 2500/2600 P series has push-pull outputs that can be in one of three states: logic one, logic zero, or open or unselected state. This, plus the programmable Chip Selects, enables the use of sev-

eral ROMS in parallel with no external components. Since the ROM is a static device, no clocks are required, making the MK 2500/2600 P series of ROMS very versatile and easy to use.

Low threshold-voltage processing, utilizing ion-implantation, is used with P-channel, enhancement-mode MOS technology to provide direct input/output interfacing with TTL and DTL logic families. All inputs are protected to prevent damage from static charge accumulation.

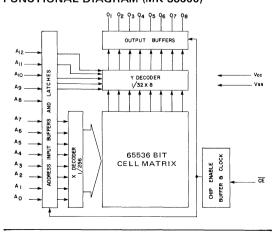

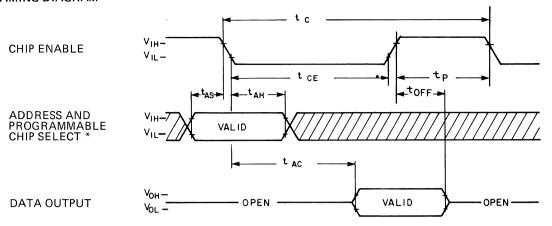

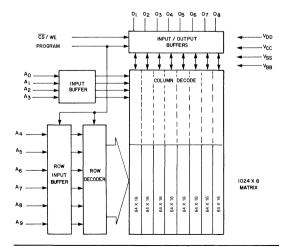

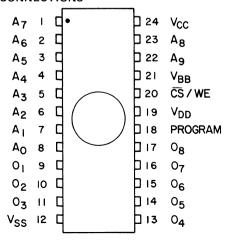

### **FUNCTIONAL DIAGRAMS**

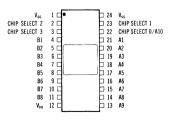

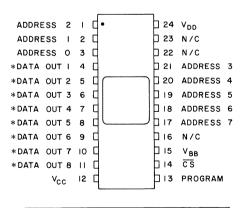

## PIN CONNECTIONS

# MK 2500 P MODE CONTROL 1 0 24 V<sub>LL</sub> CHIP SELECT 1 2 2 3 V<sub>G</sub>

# MK 2600 P

# **ABSOLUTE MAXIMUM RATINGS**

| Voltage on Any Terminal Relative to Vss (except Vee)            | +0.3V to -10V  |

|-----------------------------------------------------------------|----------------|

| Voltage on V <sub>GG</sub> Terminal Relative to V <sub>SS</sub> | ++0.3V to -20V |

| Operating Temperature Range (Ambient)                           |                |

| Storage Temperature Range (Ambient)                             |                |

# RECOMMENDED OPERATING CONDITIONS

$(0^{\circ}C \leq T_{\Lambda} \leq 70^{\circ}C)$

|                 | PARAMETER                | MIN                  | TYP   | MAX   | UNITS | NOTES  |

|-----------------|--------------------------|----------------------|-------|-------|-------|--------|

| V <sub>ss</sub> | Supply Voltage           | +4.75                | +5.0  | +5.25 | V     |        |

| $V_{DD}$        | Supply Voltage           |                      | 0.0   |       | V     | Note 1 |

| $V^{ee}$        | Supply Voltage           | -11.4                | -12.0 | -12.6 | ٧     |        |

| V <sub>IL</sub> | Input Voltage, Logic "0" |                      |       | +0.8  | ٧     |        |

| $V_{IH}$        | Input Voltage, Logic "1" | V <sub>ss</sub> -1.5 |       |       | V     | Note 2 |

| $V_{IH}$        | Input Voltage, Logic "1" | 2.4                  |       |       | V     | Note 3 |

# **ELECTRICAL CHARACTERISTICS**

(V<sub>SS</sub> =+5.0V  $\pm$  5%; V<sub>DD</sub> = 0 V; V<sub>GG</sub> =-12V  $\pm$  5%; 0°C  $\leq$  T<sub>A</sub>  $\leq$  70°C dnless noted otherwise)

|                     | PARAMETER                                                              | MIN | ТҮР  | MAX              | UNITS                    | NOTES                                                       |

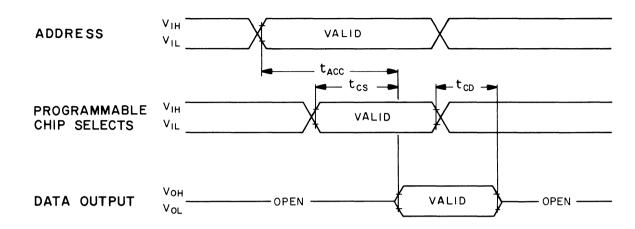

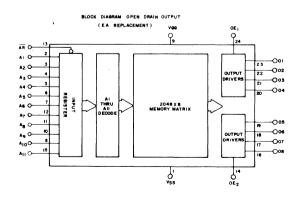

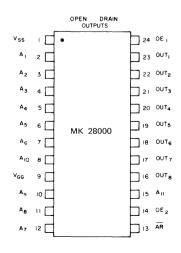

|---------------------|------------------------------------------------------------------------|-----|------|------------------|--------------------------|-------------------------------------------------------------|