# 8XC196Kx, 8XC196Jx, 87C196CA Microcontroller Family User's Manual

Includes

8XC196KQ,

8XC196KR,

8XC196KS,

8XC196KT,

8XC196JQ,

8XC196JR,

8XC196JT,

8XC196JV,

87C196CA

# 8XC196Kx, 8XC196Jx, 87C196CA Microcontroller Family User's Manual

Includes 8XC196KQ, 8XC196KR, 8XC196KS, 8XC196KT, 8XC196JQ, 8XC196JR, 8XC196JT, 8XC196JV, 87C196CA

June 1995 Order Number 272258-002

Information in this document is provided solely to enable use of Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products.

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local Intel sales office or your distributor to obtain the latest specifications before placing your product order.

MDS is an ordering code only and is not used as a product name or trademark of Intel Corporation.

Intel Corporation and Intel's FASTPATH are not affiliated with Kinetics, a division of Excelan, Inc. or its FASTPATH trademark or products.

\*Other brands and names are the property of their respective owners.

Additional copies of this document or other Intel literature may be obtained from:

Intel Corporation Literature Sales P.O. Box 7641 Mt. Prospect, IL 60056-7641 or call 1-800-879-4683

© INTEL CORPORATION, 1996

# intel<sub>®</sub>

| CHAP           |                                                                                |      |

|----------------|--------------------------------------------------------------------------------|------|

| GU             | IDE TO THIS MANUAL                                                             |      |

| 1.1            | MANUAL CONTENTS                                                                |      |

| 1.2            | NOTATIONAL CONVENTIONS AND TERMINOLOGY                                         | 1-3  |

| 1.3            | RELATED DOCUMENTS                                                              | 1-5  |

| 1.4            | ELECTRONIC SUPPORT SYSTEMS                                                     | 1-8  |

| 1.4.1          | FaxBack Service                                                                | 1-8  |

| 1.4.2          |                                                                                | 1-9  |

|                | .2.1 How to Find MCS <sup>®</sup> 96 Microcontroller Files on the BBS          |      |

|                | .2.2 How to Find <i>Ap</i> BUILDER Software and Hypertext Documents on the BBS |      |

| 1.4.3          |                                                                                |      |

| 1.4.4          |                                                                                |      |

| 1.5            | TECHNICAL SUPPORT                                                              |      |

| 1.6            | PRODUCT LITERATURE                                                             |      |

| 1.7            | TRAINING CLASSES                                                               | 1-11 |

| CHAP           |                                                                                |      |

| AR             | CHITECTURAL OVERVIEW                                                           |      |

| 2.1            | TYPICAL APPLICATIONS                                                           |      |

| 2.2            | DEVICE FEATURES                                                                |      |

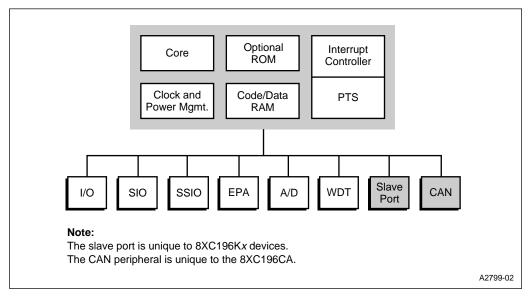

| 2.3            | BLOCK DIAGRAM                                                                  |      |

| 2.3.1          |                                                                                |      |

| 2.3.2          |                                                                                |      |

| 2.3.3          | 3                                                                              |      |

|                | .3.1 Code Execution                                                            |      |

| _              | .3.2 Instruction Format                                                        |      |

| 2.3.4<br>2.3.5 | ,                                                                              |      |

|                | Interrupt ServiceINTERNAL TIMING                                               |      |

| 2.4            |                                                                                |      |

| 2.5            | INTERNAL PERIPHERALS                                                           |      |

| 2.5.1<br>2.5.2 |                                                                                |      |

| 2.5.2          |                                                                                |      |

| 2.5.3          |                                                                                |      |

| 2.5.4          | • • • • • • • • • • • • • • • • • • • •                                        |      |

| 2.5.6          |                                                                                |      |

| 2.5.7          |                                                                                |      |

| 2.5.8          |                                                                                |      |

| 2.6            | SPECIAL OPERATING MODES                                                        |      |

| 2.6.1          |                                                                                |      |

|                |                                                                                |      |

| 2.6.2 | 2 Testing the Printed Circuit Board                        | 2-12 |

|-------|------------------------------------------------------------|------|

| 2.6.3 | Programming the Nonvolatile Memory                         | 2-12 |

| 2.7   | DESIGN CONSIDERATIONS FOR 87C196CA DEVICES                 | 2-13 |

| 2.8   | DESIGN CONSIDERATIONS FOR 8XC196JQ, JR, JT, AND JV DEVICES | 2-14 |

| CHAP  | PTER 3                                                     |      |

| PR    | OGRAMMING CONSIDERATIONS                                   |      |

| 3.1   | OVERVIEW OF THE INSTRUCTION SET                            | 3-1  |

| 3.1.1 | BIT Operands                                               | 3-2  |

| 3.1.2 | Part Operands                                              | 3-2  |

| 3.1.3 | SHORT-INTEGER Operands                                     | 3-2  |

| 3.1.4 | WORD Operands                                              | 3-2  |

| 3.1.5 | •                                                          |      |

| 3.1.6 | ·                                                          |      |

| 3.1.7 | LONG-INTEGER Operands                                      | 3-4  |

| 3.1.8 | Converting Operands                                        | 3-4  |

| 3.1.9 |                                                            |      |

| 3.1.1 | 0 Floating Point Operations                                | 3-4  |

| 3.2   | ADDRESSING MODES                                           | 3-5  |

| 3.2.1 |                                                            |      |

| 3.2.2 | •                                                          |      |

| 3.2.3 | •                                                          |      |

| 3.2   | .3.1 Indirect Addressing with Autoincrement                |      |

| 3.2   | .3.2 Indirect Addressing with the Stack Pointer            |      |

| 3.2.4 | 3                                                          |      |

|       | .4.1 Short-indexed Addressing                              |      |

|       | .4.2 Long-indexed Addressing                               |      |

| 3.2   | .4.3 Zero-indexed Addressing                               |      |

| 3.3   | ASSEMBLY LANGUAGE ADDRESSING MODE SELECTIONS               |      |

| 3.3.1 | 3                                                          |      |

| 3.3.2 | 3                                                          |      |

| 3.4   | SOFTWARE STANDARDS AND CONVENTIONS                         | 3-9  |

| 3.4.1 |                                                            |      |

| 3.4.2 | 2 Addressing 32-bit Operands                               | 3-10 |

| 3.4.3 | B Linking Subroutines                                      | 3-10 |

| 3.5   | SOFTWARE PROTECTION FEATURES AND GUIDELINES                | 3-11 |

| СНАР  | TER 4                                                      |      |

| ME    | MORY PARTITIONS                                            |      |

| 4.1   | MEMORY PARTITIONS                                          |      |

| 4.1.1 | ,                                                          |      |

| 4.1.2 | -9                                                         |      |

| 4.1.3 |                                                            |      |

| 4.1.4 | Special-purpose Memory                                     | 4-3  |

| 4.1.4.1 | Reserved Memory Locations                  | 4-4          |

|---------|--------------------------------------------|--------------|

| 4.1.4.2 | 2 Interrupt and PTS Vectors                | 4-4          |

| 4.1.4.3 | B Security Key                             | 4-4          |

| 4.1.4.4 | Chip Configuration Bytes (CCBs)            | 4-4          |

| 4.1.5   | Special-function Registers (SFRs)          | 4-5          |

| 4.1.5.1 |                                            |              |

| 4.1.5.2 | Peripheral SFRs                            | 4-6          |

| 4.1.6   | Internal RAM (Code RAM)                    | 4-10         |

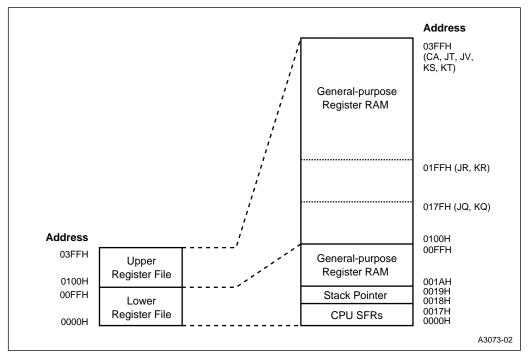

| 4.1.7   | Register File                              | 4-10         |

| 4.1.7.1 | General-purpose Register RAM               | 4-12         |

| 4.1.7.2 | (,                                         | 4-12         |

| 4.1.7.3 | B CPU Special-function Registers (SFRs)    | 4-13         |

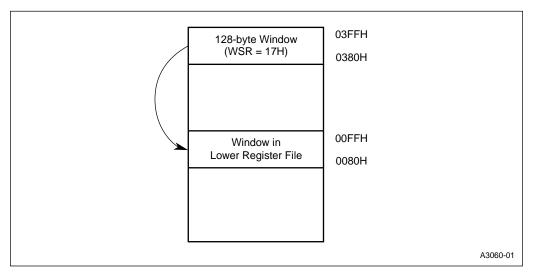

| 4.2 W   | INDOWING                                   | 4-13         |

| 4.2.1   | Selecting a Window                         | 4-14         |

| 4.2.2   | Addressing a Location Through a Window     | 4-17         |

| 4.2.2.1 | 32-byte Windowing Example                  | 4-20         |

| 4.2.2.2 | 2 64-byte Windowing Example                | 4-20         |

| 4.2.2.3 |                                            | 4-20         |

| 4.2.2.4 | ''                                         |              |

| 4.2.2.5 | 3 - 3                                      |              |

| 4.2.3   | Windowing and Addressing Modes             | 4-23         |

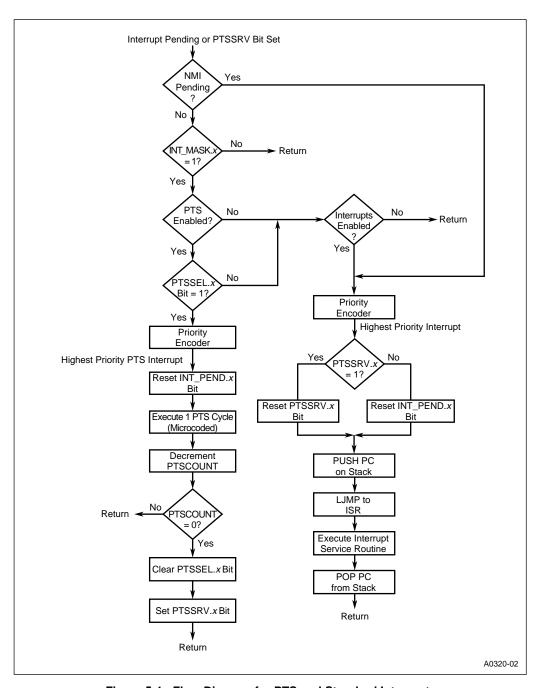

| _       | DARD AND PTS INTERRUPTS<br>VERVIEW         | 5-1          |

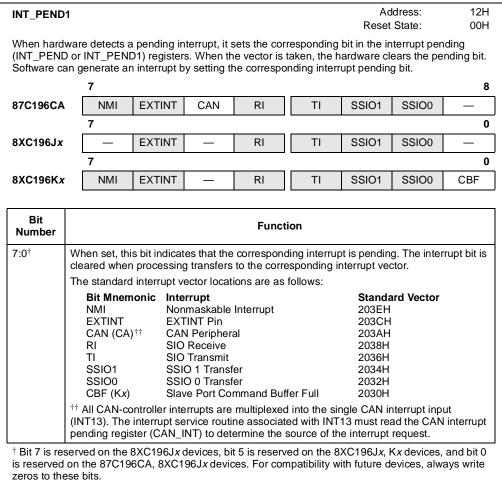

| 5.2 IN  | ITERRUPT SIGNALS AND REGISTERS             | 5-3          |

| 5.3 IN  | ITERRUPT SOURCES AND PRIORITIES            | 5-4          |

| 5.3.1   | Special Interrupts                         |              |

| 5.3.1.1 | ·                                          |              |

| 5.3.1.2 |                                            |              |

| 5.3.1.3 | 8 NMI                                      | 5-6          |

| 5.3.2   | External Interrupt Pins                    | 5-6          |

| 5.3.3   | Multiplexed Interrupt Sources              | 5-7          |

| 5.3.4   | End-of-PTS Interrupts                      | 5-7          |

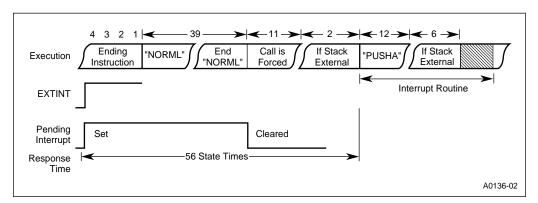

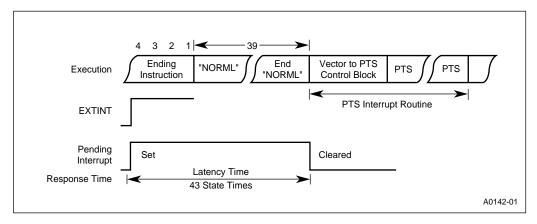

| 5.4 IN  | ITERRUPT LATENCY                           | 5-7          |

| 5.4.1   | Situations that Increase Interrupt Latency |              |

| 5.4.2   | Calculating Latency                        |              |

| 5.4.2.1 | · ·                                        |              |

| 5.4.2.2 | ·                                          |              |

| 5.5 PF  | ROGRAMMING THE INTERRUPTS                  |              |

| 5.5.1   | Programming the Multiplexed Interrupts     |              |

| 5.5.2   | Modifying Interrupt Priorities             |              |

| 5.5.3   |                                            |              |

|         | , ,                                        |              |

| 5.5.3.1 | Determining the Source of an Interrupt     | 5-16         |

|         | Determining the Source of an Interrupt     | 5-16<br>5-16 |

| 5.6.1   | Specifying the PTS Count                                 | 5-19 |

|---------|----------------------------------------------------------|------|

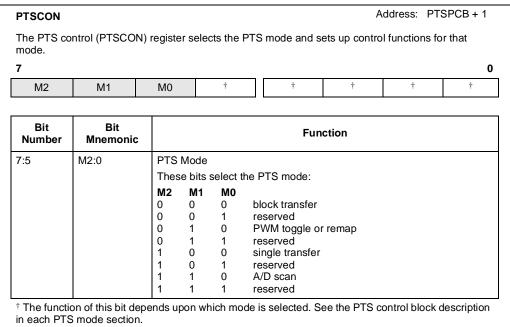

| 5.6.2   | Selecting the PTS Mode                                   | 5-21 |

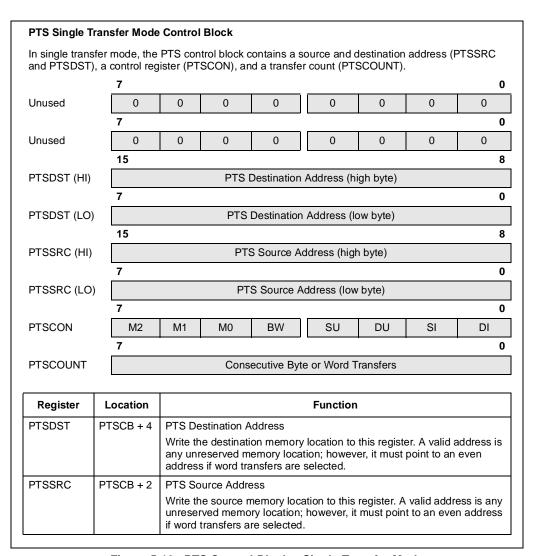

| 5.6.3   | Single Transfer Mode                                     | 5-21 |

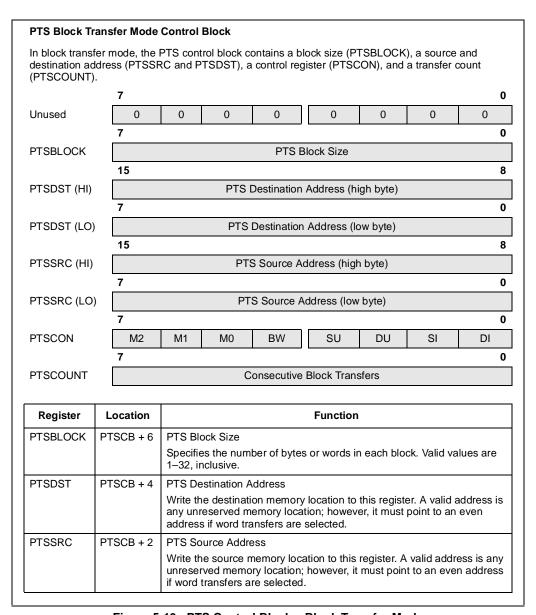

| 5.6.4   | Block Transfer Mode                                      | 5-24 |

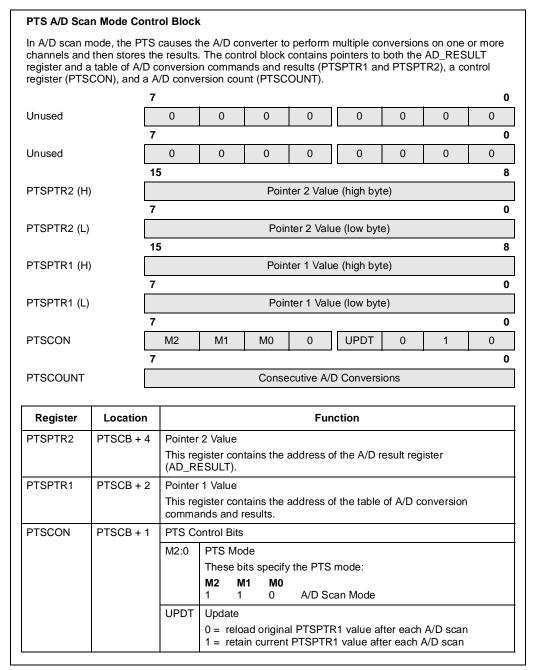

| 5.6.5   | A/D Scan Mode                                            | 5-26 |

| 5.6.5.1 |                                                          |      |

| 5.6.5.2 |                                                          |      |

| 5.6.5.3 | · · · · · · · · · · · · · · · · · · ·                    |      |

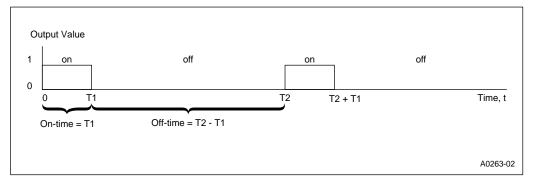

| 5.6.6   | PWM Modes                                                |      |

| 5.6.6.1 | 33                                                       |      |

| 5.6.6.2 | PWM Remap Mode Example                                   | 5-37 |

| CHAPTE  |                                                          |      |

| I/O PC  |                                                          |      |

|         | PORTS OVERVIEW                                           |      |

| 6.2 IN  | PUT-ONLY PORT 0                                          |      |

| 6.2.1   | Standard Input-only Port Operation                       | 6-2  |

| 6.2.2   | Standard Input-only Port Considerations                  | 6-3  |

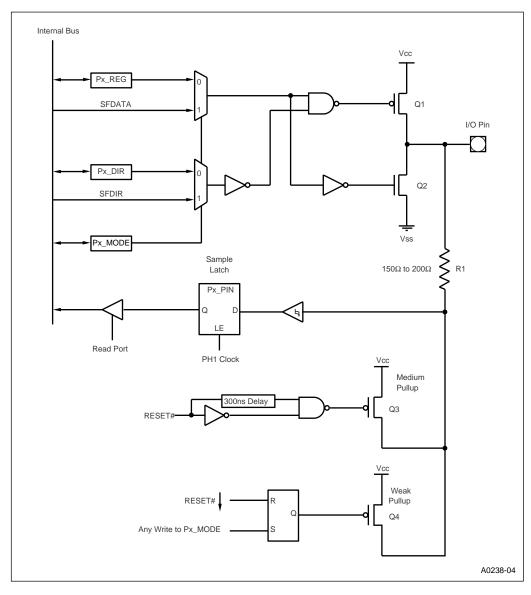

| 6.3 Bl  | DIRECTIONAL PORTS 1, 2, 5, AND 6                         | 6-4  |

| 6.3.1   | Bidirectional Port Operation                             | 6-6  |

| 6.3.2   | Bidirectional Port Pin Configurations                    | 6-10 |

| 6.3.3   | Bidirectional Port Pin Configuration Example             | 6-11 |

| 6.3.4   | Bidirectional Port Considerations                        | 6-12 |

| 6.3.5   | Design Considerations for External Interrupt Inputs      | 6-15 |

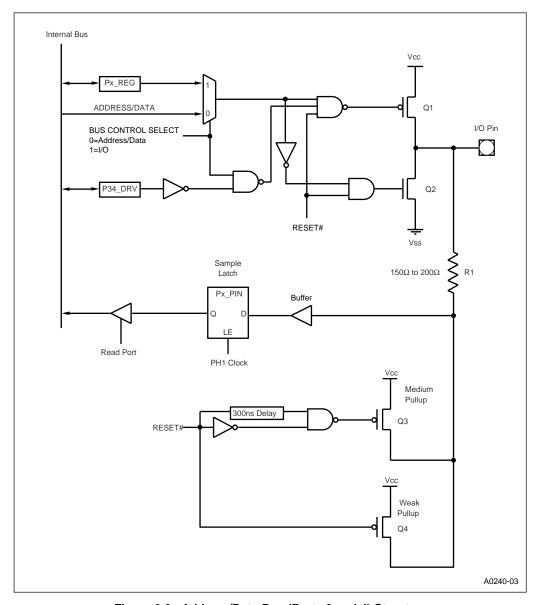

| 6.4 Bl  | DIRECTIONAL PORTS 3 AND 4 (ADDRESS/DATA BUS)             | 6-15 |

| 6.4.1   | Bidirectional Ports 3 and 4 (Address/Data Bus) Operation |      |

| 6.4.2   | Using Ports 3 and 4 as I/O                               |      |

| 6.4.3   | Design Considerations for Ports 3 and 4                  |      |

| CHAPTE  | R 7                                                      |      |

|         | L I/O (SIO) PORT                                         |      |

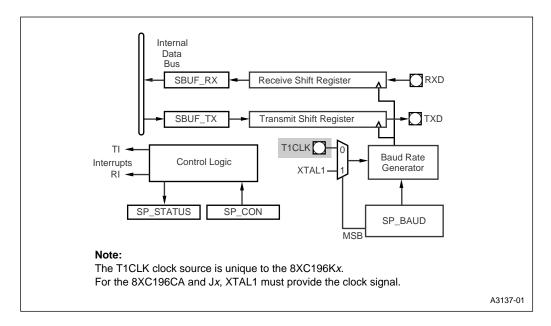

|         | ERIAL I/O (SIO) PORT FUNCTIONAL OVERVIEW                 |      |

| 7.2 SI  | ERIAL I/O PORT SIGNALS AND REGISTERS                     | 7-2  |

| 7.3 SI  | ERIAL PORT MODES                                         | 7-4  |

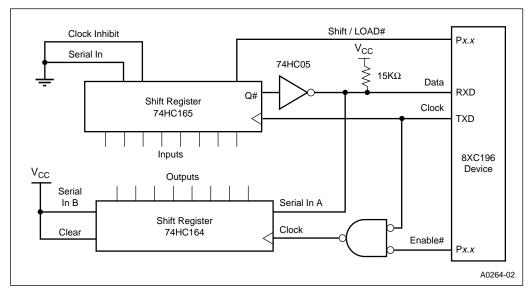

| 7.3.1   | Synchronous Mode (Mode 0)                                | 7-4  |

| 7.3.2   | Asynchronous Modes (Modes 1, 2, and 3)                   |      |

| 7.3.2.1 | Mode 1                                                   | 7-6  |

| 7.3.2.2 |                                                          |      |

| 7.3.2.3 |                                                          |      |

| 7.3.2.4 | •                                                        |      |

| 7.3.2.5 |                                                          |      |

|         | ROGRAMMING THE SERIAL PORT                               |      |

| 7.4.1   | Configuring the Serial Port Pins                         |      |

| 7.4.2   | Programming the Control Register                         | 7-8  |

| 7.4.3        | Programming the Baud Rate and Clock Source                     | 7-10 |

|--------------|----------------------------------------------------------------|------|

| 7.4.4        | Enabling the Serial Port Interrupts                            | 7-12 |

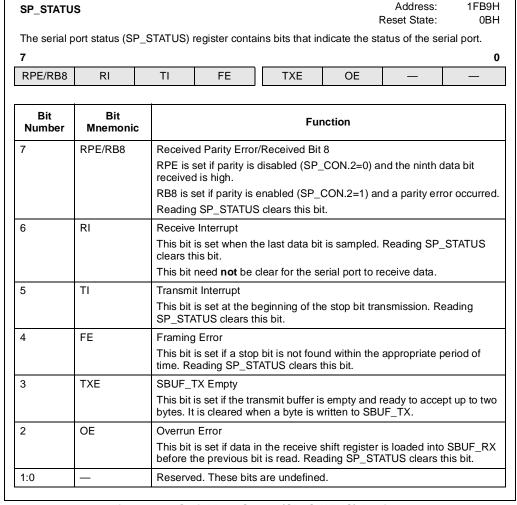

| 7.4.5        | Determining Serial Port Status                                 | 7-13 |

| 7.5          | PROGRAMMING EXAMPLE USING AN INTERRUPT-DRIVEN ROUTINE          | 7-14 |

| CHAP         |                                                                |      |

| SYN          | NCHRONOUS SERIAL I/O (SSIO) PORT                               |      |

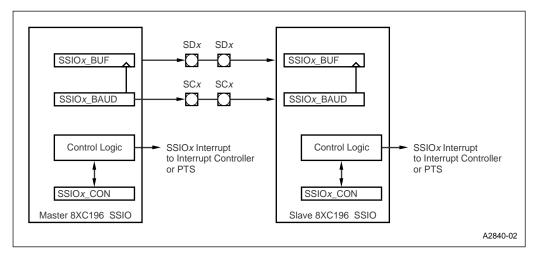

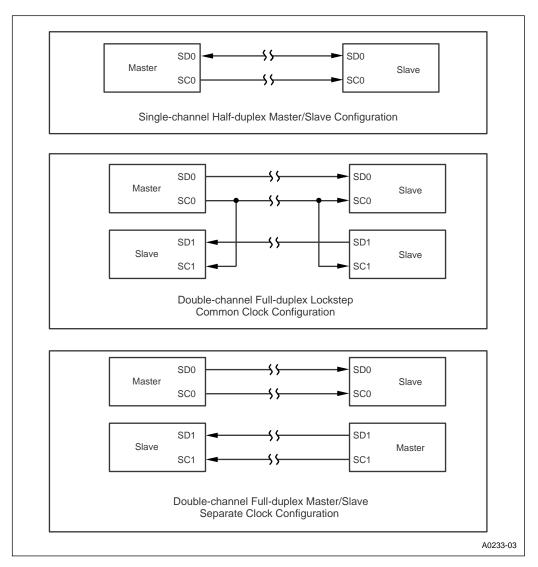

| 8.1          | SYNCHRONOUS SERIAL I/O (SSIO) PORT FUNCTIONAL OVERVIEW         |      |

| 8.2          | SSIO PORT SIGNALS AND REGISTERS                                | 8-2  |

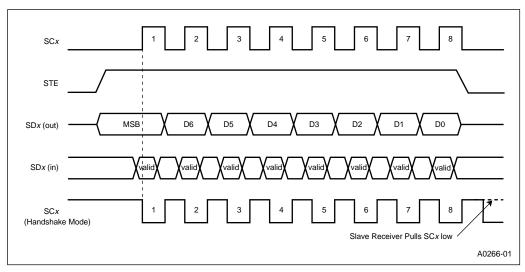

| 8.3          | SSIO OPERATION                                                 |      |

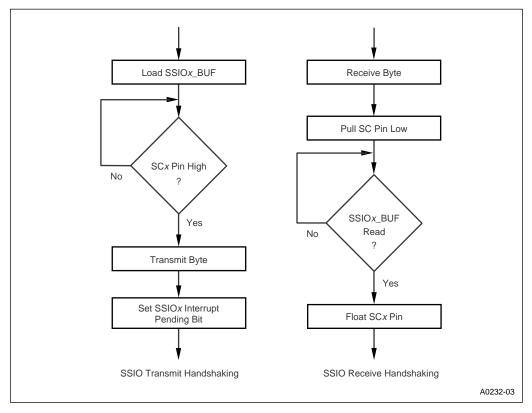

| 8.4          | SSIO HANDSHAKING                                               |      |

| 8.4.1        | SSIO Handshaking Configuration                                 |      |

| 8.4.2        | 3 - 1 - 1 - 3 - 1 - 1 - 1                                      |      |

| 8.5          | PROGRAMMING THE SSIO PORT                                      |      |

| 8.5.1        | Configuring the SSIO Port Pins                                 |      |

| 8.5.2        | Programming the Baud Rate and Enabling the Baud-rate Generator |      |

| 8.5.3        | 3                                                              |      |

| 8.5.4        | Enabling the SSIO Interrupts                                   |      |

| 8.5.5        | 3                                                              |      |

| 8.6          | PROGRAMMING CONSIDERATIONS                                     |      |

| 8.7          | PROGRAMMING EXAMPLE                                            | 8-15 |

| CHAP         | TER 9<br>AVE PORT                                              |      |

| 9.1          | SLAVE PORT FUNCTIONAL OVERVIEW                                 | 0.2  |

| 9.1          | SLAVE PORT SIGNALS AND REGISTERS                               |      |

|              | HARDWARE CONNECTIONS                                           |      |

| 9.3          |                                                                |      |

| 9.4<br>9.4.1 | SLAVE PORT MODES                                               |      |

| 9.4.1        | •                                                              |      |

| 9.4.         | •                                                              |      |

| 9.4.         | <del>-</del>                                                   |      |

| 9.4.2        |                                                                |      |

| 9.4.         | =                                                              |      |

| 9.4.         |                                                                |      |

| 9.4.         | 3                                                              |      |

| 9.5          | CONFIGURING THE SLAVE PORT                                     |      |

| 9.5.1        | Programming the Slave Port Control Register (SLP_CON)          |      |

| 9.5.2        | 3                                                              |      |

| 9.6          | DETERMINING SLAVE PORT STATUS                                  |      |

| 9.7          | USING STATUS BITS TO SYNCHRONIZE MASTER AND SLAVE              | 9-16 |

| CHAPTER 10                                                            |       |

|-----------------------------------------------------------------------|-------|

| EVENT PROCESSOR ARRAY (EPA)                                           | 40.4  |

| 10.1 EPA FUNCTIONAL OVERVIEW                                          |       |

| 10.2 EPA AND TIMER/COUNTER SIGNALS AND REGISTERS                      |       |

| 10.3 TIMER/COUNTER FUNCTIONAL OVERVIEW                                |       |

| 10.3.1 Cascade Mode (Timer 2 Only)                                    |       |

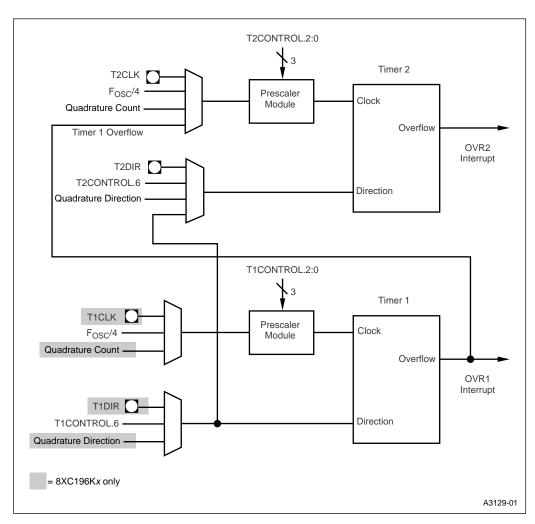

| 10.3.2 Quadrature Clocking Mode                                       |       |

| 10.4 EPA CHANNEL FUNCTIONAL OVERVIEW                                  |       |

| 10.4.1 Operating in Capture Mode                                      |       |

| 10.4.1.1 Handling EPA Overruns                                        |       |

| 10.4.2 Operating in Compare Mode                                      |       |

| 10.4.2.2 Generating a Low-speed PWM Output                            | 10-14 |

| 10.4.2.3 Generating a High-speed PWM Output                           |       |

| 10.4.2.4 Generating the Highest-speed PWM Output                      |       |

| 10.5 PROGRAMMING THE EPA AND TIMER/COUNTERS                           |       |

| 10.5.1 Configuring the EPA and Timer/Counter Port Pins                |       |

| 10.5.2 Programming the Timers                                         |       |

| 10.5.3 Programming the Capture/Compare Channels                       |       |

| 10.5.4 Programming the Compare-only Channels                          |       |

| 10.6 ENABLING THE EPA INTERRUPTS                                      |       |

| 10.7 DETERMINING EVENT STATUS                                         |       |

| 10.8 SERVICING THE MULTIPLEXED EPA INTERRUPT WITH SOFTV               |       |

| 10.8.1 Using the TIJMP Instruction to Reduce Interrupt Service Overhe |       |

| 10.9 PROGRAMMING EXAMPLES FOR EPA CHANNELS                            |       |

| 10.9.1 EPA Compare Event Program                                      |       |

| 10.9.2 EPA Capture Event Program                                      |       |

| 10.9.3 EPA PWM Output Program                                         |       |

| CHAPTER 11                                                            |       |

| ANALOG-TO-DIGITAL CONVERTER                                           |       |

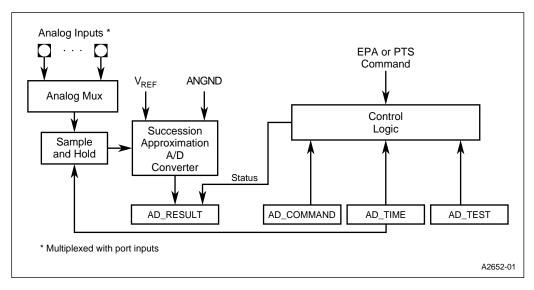

| 11.1 A/D CONVERTER FUNCTIONAL OVERVIEW                                | 11-1  |

| 11.2 A/D CONVERTER SIGNALS AND REGISTERS                              |       |

| 11.3 A/D CONVERTER OPERATION                                          |       |

| 11.4 PROGRAMMING THE A/D CONVERTER                                    |       |

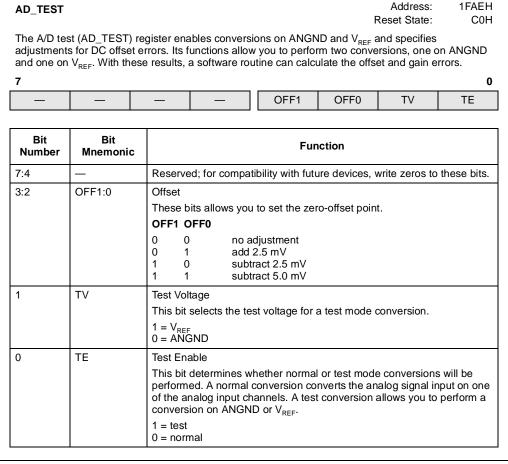

| 11.4.1 Programming the A/D Test Register                              |       |

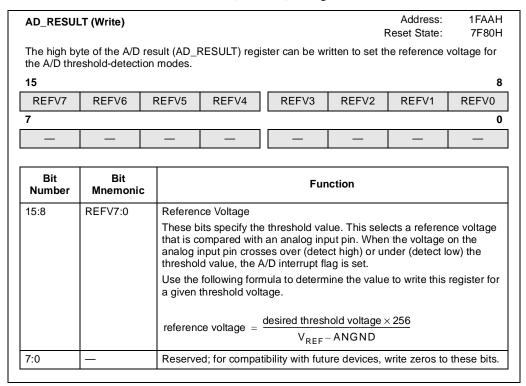

| 11.4.2 Programming the A/D Result Register (for Threshold Detection   |       |

| 11.4.3 Programming the A/D Time Register                              |       |

| 11.4.4 Programming the A/D Command Register                           |       |

| 11.4.5 Enabling the A/D Interrupt                                     |       |

| 11.5 DETERMINING A/D STATUS AND CONVERSION RESULTS                    |       |

| 11.6 DESIGN CONSIDERATIONS                                            |       |

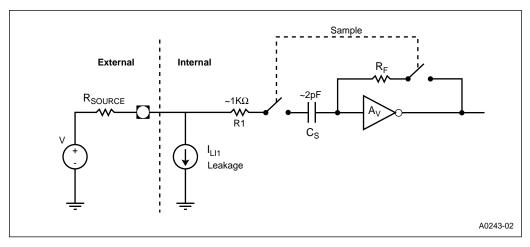

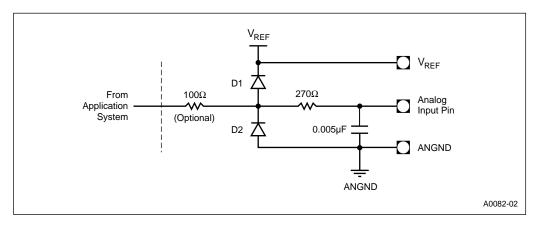

| 11.6.1 Decigning External Interface Circuitry                         | _     |

| 11-12 |

|-------|

| 11-13 |

| 11-13 |

| 11-14 |

| 11-14 |

|       |

|       |

| 12-1  |

| 12-3  |

| 12-4  |

| 12-5  |

| 12-5  |

| 12-6  |

| 12-6  |

| 12-7  |

| 12-9  |

| 12-10 |

| 12-12 |

| 12-13 |

| 12-13 |

| 12-15 |

| 12-16 |

| 12-18 |

| 12-20 |

| 12-21 |

| 12-22 |

| 12-23 |

| 12-23 |

| 12-23 |

| 12-23 |

| 12-29 |

| 12-32 |

| 12-35 |

| 12-41 |

| 12-41 |

| 12-41 |

| 12-41 |

|       |

|       |

| 13-1  |

| 13-2  |

| 13-2  |

|       |

| 13.2  | APPLYING AND REMOVING POWER                                       | 13-4  |

|-------|-------------------------------------------------------------------|-------|

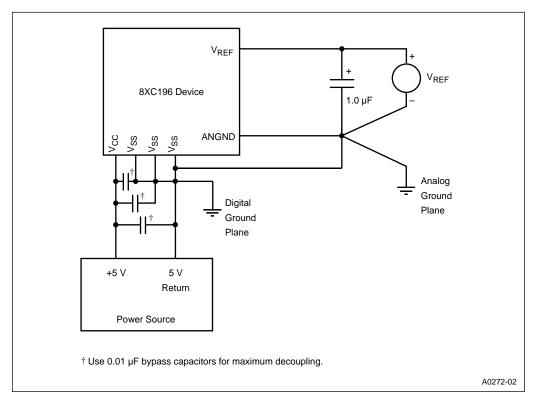

| 13.3  | NOISE PROTECTION TIPS                                             | 13-4  |

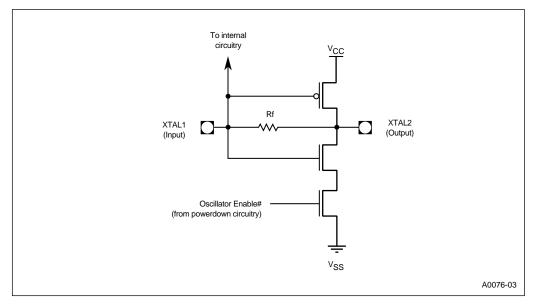

| 13.4  | PROVIDING THE CLOCK                                               | 13-5  |

| 13.4. | 9 1                                                               |       |

| 13.4. | 2 Using a Ceramic Resonator Instead of a Crystal Oscillator       | 13-7  |

| 13.4. |                                                                   |       |

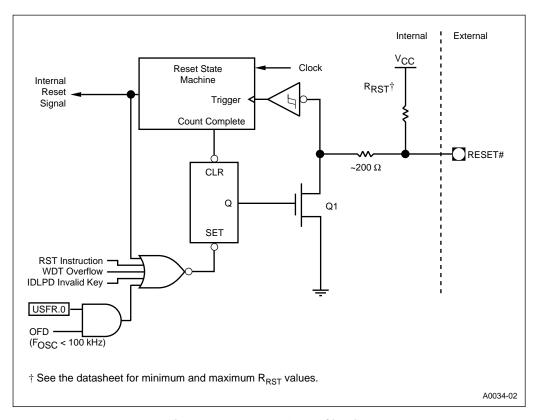

| 13.5  | RESETTING THE DEVICE                                              | 13-8  |

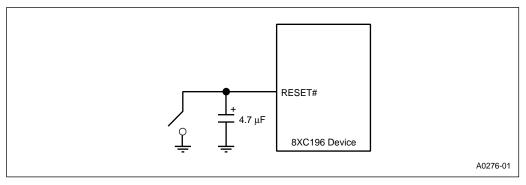

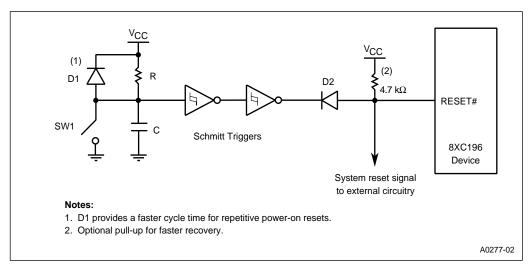

| 13.5. | 1 Generating an External Reset                                    | 13-10 |

| 13.5. | 2 Issuing the Reset (RST) Instruction                             | 13-12 |

| 13.5. | 3 Issuing an Illegal IDLPD Key Operand                            | 13-12 |

| 13.5. | 4 Enabling the Watchdog Timer                                     | 13-12 |

| 13.5. | 5 Detecting Oscillator Failure                                    | 13-12 |

| CHAP  | TER 14                                                            |       |

|       | ECIAL OPERATING MODES                                             |       |

| 14.1  | SPECIAL OPERATING MODE SIGNALS AND REGISTERS                      |       |

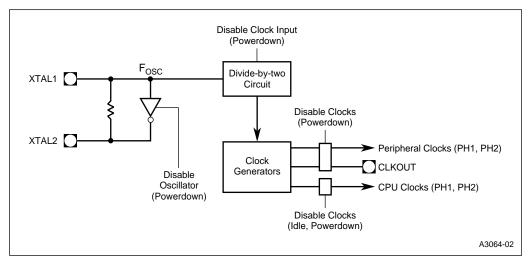

| 14.2  | REDUCING POWER CONSUMPTION                                        |       |

| 14.3  | IDLE MODE                                                         |       |

| 14.4  | POWERDOWN MODE                                                    |       |

| 14.4. | 3                                                                 |       |

| 14.4. |                                                                   |       |

| 14.4. |                                                                   |       |

|       | 4.3.1 Driving the V <sub>pp</sub> Pin Low                         |       |

|       | 4.3.2 Generating a Hardware Reset                                 |       |

|       | 4.3.4 Selecting the External Interrupt Signal                     |       |

|       | 4.3.4 Selecting R <sub>1</sub> and C <sub>1</sub>                 |       |

| 14.5  | ONCE MODE                                                         | _     |

| 14.5. |                                                                   |       |

| 14.6  | RESERVED TEST MODES                                               | 14-10 |

| -     | TER 15                                                            |       |

|       | ERFACING WITH EXTERNAL MEMORY                                     | 45.4  |

| 15.1  | EXTERNAL MEMORY INTERFACE SIGNALS                                 |       |

| 15.2  | CHIP CONFIGURATION REGISTERS AND CHIP CONFIGURATION BYTES $\dots$ |       |

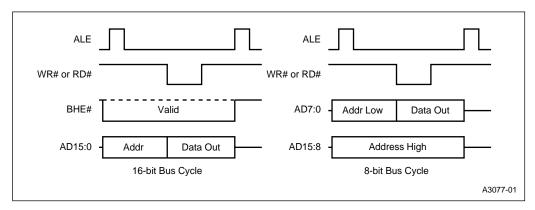

| 15.3  | BUS WIDTH AND MULTIPLEXING                                        |       |

| 15.3. | 9 - 1                                                             |       |

| 15.3. | 3.                                                                |       |

| 15.3. | - · · · · · · · · · · · · · · · · · · ·                           |       |

| 15.4  | WAIT STATES (READY CONTROL)                                       |       |

| 15.5  | BUS-HOLD PROTOCOL (8XC196KQ, KR, KS, KT ONLY)                     |       |

| 15.5. | 3                                                                 |       |

| 15.5. | 37                                                                |       |

| 15.5. | 3 Hold Latency (8XC196Kx Only)                                    | 15-19 |

| 15.5.4 Regaining Bus Control (8XC196Kx Only)                      | 15-20   |

|-------------------------------------------------------------------|---------|

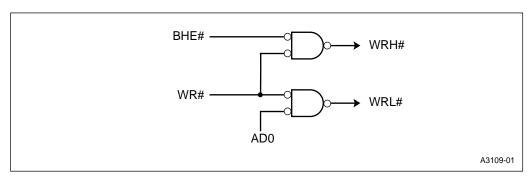

| 15.6 BUS-CONTROL MODES                                            | 15-20   |

| 15.6.1 Standard Bus-control Mode                                  | 15-20   |

| 15.6.2 Write Strobe Mode                                          | 15-24   |

| 15.6.3 Address Valid Strobe Mode                                  | 15-26   |

| 15.6.4 Address Valid with Write Strobe Mode                       | 15-29   |

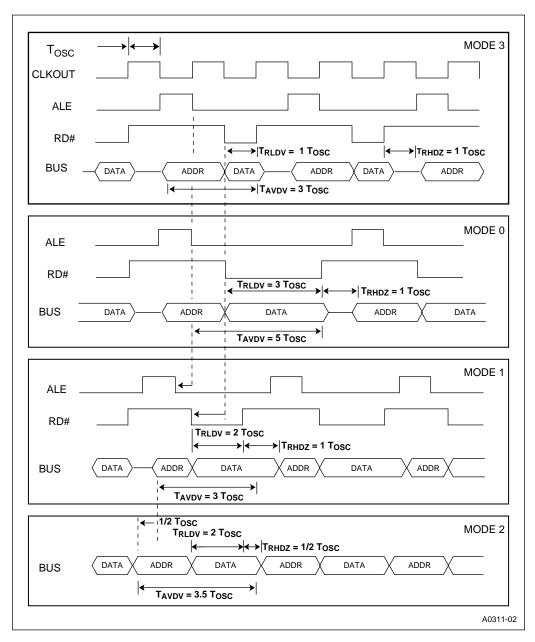

| 15.7 BUS TIMING MODES (8XC196KS, KT ONLY)                         | 15-30   |

| 15.7.1 Mode 3, Standard Mode                                      |         |

| 15.7.2 Mode 0, Standard Timing with One Automatic Wait State      | 15-32   |

| 15.7.3 Mode 1, Long Read/Write Mode                               | 15-32   |

| 15.7.4 Mode 2, Long Read/Write with Early Address                 | 15-33   |

| 15.7.5 Design Considerations                                      | 15-34   |

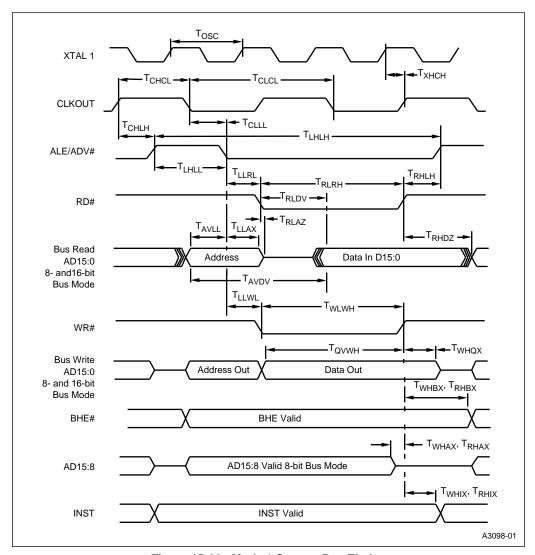

| 15.8 SYSTEM BUS AC TIMING SPECIFICATIONS                          | 15-36   |

| CHAPTER 16                                                        |         |

| PROGRAMMING THE NONVOLATILE MEMORY                                |         |

| 16.1 PROGRAMMING METHODS                                          | 16-2    |

| 16.2 OTPROM MEMORY MAP                                            | 16-2    |

| 16.3 SECURITY FEATURES                                            | 16-3    |

| 16.3.1 Controlling Access to Internal Memory                      | 16-4    |

| 16.3.1.1 Controlling Access to the OTPROM During Normal Operation |         |

| 16.3.1.2 Controlling Access to the OTPROM During Programming Mo   | des16-5 |

| 16.3.2 Controlling Fetches from External Memory                   |         |

| 16.3.3 Enabling the Oscillator Failure Detection Circuitry        |         |

| 16.4 PROGRAMMING PULSE WIDTH                                      |         |

| 16.5 MODIFIED QUICK-PULSE ALGORITHM                               | 16-10   |

| 16.6 PROGRAMMING MODE PINS                                        | 16-11   |

| 16.7 ENTERING PROGRAMMING MODES                                   | 16-14   |

| 16.7.1 Selecting the Programming Mode                             | 16-14   |

| 16.7.2 Power-up and Power-down Sequences                          | 16-14   |

| 16.7.2.1 Power-up Sequence                                        |         |

| 16.7.2.2 Power-down Sequence                                      |         |

| 16.8 SLAVE PROGRAMMING MODE                                       |         |

| 16.8.1 Reading the Signature Word and Programming Voltages        |         |

| 16.8.2 Slave Programming Circuit and Memory Map                   |         |

| 16.8.3 Operating Environment                                      |         |

| 16.8.4 Slave Programming Routines                                 |         |

| 16.8.5 Timing Mnemonics                                           |         |

| 16.9 AUTO PROGRAMMING MODE                                        |         |

| 16.9.1 Auto Programming Circuit and Memory Map                    |         |

| 16.9.2 Operating Environment                                      |         |

| 16.9.3 Auto Programming Routine                                   |         |

| 16.9.4 Auto Programming Procedure                                 | 16-30   |

| 16.9.5          | ROM-dump Mode                                            | 16-31 |

|-----------------|----------------------------------------------------------|-------|

| 16.10 S         | ERIAL PORT PROGRAMMING MODE                              | 16-32 |

| 16.10.1         | Serial Port Programming Circuit and Memory Map           | 16-32 |

| 16.10.2         | Changing Serial Port Programming Defaults                | 16-34 |

| 16.10.3         | Executing Programs from Internal RAM                     | 16-35 |

| 16.10.4         | Reduced Instruction Set Monitor (RISM)                   | 16-35 |

| 16.10.5         | RISM Command Descriptions                                | 16-36 |

|                 | RISM Command Examples                                    |       |

| 16.10           | .6.1 Example 1 — Programming the PPW                     | 16-39 |

|                 | .6.2 Example 2 — Reading OTPROM Contents                 |       |

|                 | .6.3 Example 3 — Loading a Program into Internal RAM     |       |

|                 | 6.4 Example 4 — Setting the PC and Executing the Program |       |

|                 | .6.5 Writing to OTPROM with Examples 3 and 4             |       |

| 16.11 F         | UN-TIME PROGRAMMING                                      | 16-44 |

| APPENI<br>INSTI | DIX A<br>RUCTION SET REFERENCE                           |       |

| APPENE          | DIX B<br>AL DESCRIPTIONS                                 |       |

|                 | IGNAL NAME CHANGES                                       | D 1   |

|                 |                                                          |       |

|                 | UNCTIONAL GROUPINGS OF SIGNALS                           |       |

|                 | SIGNAL DESCRIPTIONS                                      |       |

| B.4 D           | DEFAULT CONDITIONS                                       | B-19  |

| APPENI<br>REGI  | DIX C<br>STERS                                           |       |

| GLOSSA          | ARY                                                      |       |

**INDEX**

| Figure |                                                        | Page |

|--------|--------------------------------------------------------|------|

| 2-1    | 8XC196Kx Block Diagram                                 | 2-3  |

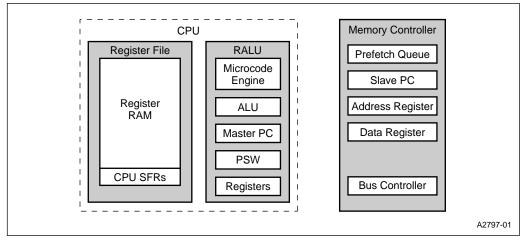

| 2-2    | Block Diagram of the Core                              |      |

| 2-3    | Clock Circuitry                                        | 2-7  |

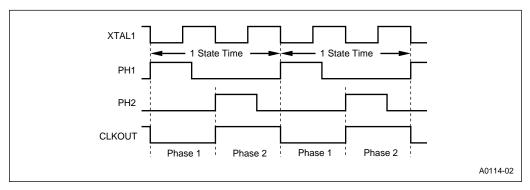

| 2-4    | Internal Clock Phases                                  | 2-8  |

| 4-1    | Register File Memory Map                               | 4-11 |

| 4-2    | Windowing                                              | 4-14 |

| 4-3    | Window Selection Register (WSR)                        | 4-15 |

| 5-1    | Flow Diagram for PTS and Standard Interrupts           | 5-2  |

| 5-2    | Standard Interrupt Response Time                       | 5-9  |

| 5-3    | PTS Interrupt Response Time                            | 5-10 |

| 5-4    | PTS Select (PTSSEL) Register                           | 5-12 |

| 5-5    | Interrupt Mask (INT_MASK) Register                     | 5-13 |

| 5-6    | Interrupt Mask 1 (INT_MASK1) Register                  | 5-14 |

| 5-7    | Interrupt Pending (INT_PEND) Register                  | 5-17 |

| 5-8    | Interrupt Pending 1 (INT_PEND1) Register               | 5-18 |

| 5-9    | PTS Control Blocks                                     | 5-19 |

| 5-10   | PTS Service (PTSSRV) Register                          | 5-20 |

| 5-11   | PTS Mode Selection Bits (PTSCON Bits 7:5)              | 5-21 |

| 5-12   | PTS Control Block - Single Transfer Mode               | 5-22 |

| 5-13   | PTS Control Block - Block Transfer Mode                | 5-25 |

| 5-14   | PTS Control Block – A/D Scan Mode                      | 5-27 |

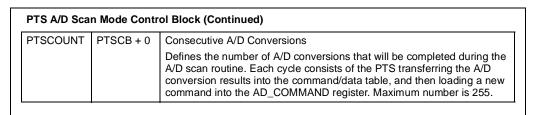

| 5-15   | A Generic PWM Waveform                                 |      |

| 5-16   | PTS Control Block – PWM Toggle Mode                    |      |

| 5-17   | EPA and PTS Operations for the PWM Toggle Mode Example | 5-36 |

| 5-18   | PTS Control Block - PWM Remap Mode                     | 5-39 |

| 5-19   | EPA and PTS Operations for the PWM Remap Mode Example  | 5-41 |

| 6-1    | Standard Input-only Port Structure                     | 6-3  |

| 6-2    | Bidirectional Port Structure                           | 6-8  |

| 6-3    | Address/Data Bus (Ports 3 and 4) Structure             |      |

| 7-1    | SIO Block Diagram                                      |      |

| 7-2    | Typical Shift Register Circuit for Mode 0              | 7-5  |

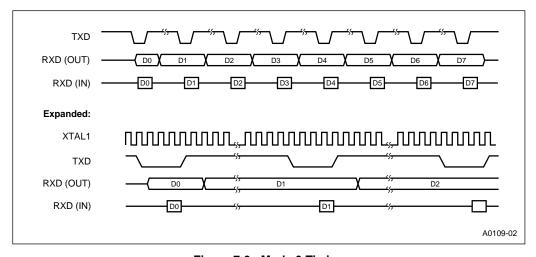

| 7-3    | Mode 0 Timing                                          |      |

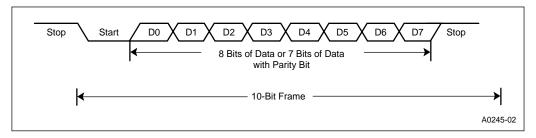

| 7-4    | Serial Port Frames for Mode 1                          |      |

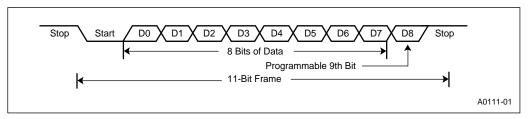

| 7-5    | Serial Port Frames in Mode 2 and 3                     |      |

| 7-6    | Serial Port Control (SP_CON) Register                  |      |

| 7-7    | Serial Port Baud Rate (SP_BAUD) Register               |      |

| 7-8    | Serial Port Status (SP_STATUS) Register                |      |

| 8-1    | SSIO Block Diagram                                     |      |

| 8-2    | SSIO Operating Modes                                   |      |

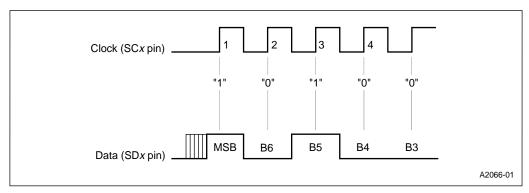

| 8-3    | SSIO Transmit/Receive Timings                          |      |

| 8-4    | SSIO Handshaking Flow Diagram                          |      |

| 8-5    | Synchronous Serial Port Baud (SSIO_BAUD) Register      |      |

| 8-6    | Synchronous Serial Control x (SSIOx_CON) Registers     |      |

| 8-7    | Variable-width MSB in SSIO Transmissions               | 8-14 |

|        |                                                        |      |

| Figure |                                                          | Page  |

|--------|----------------------------------------------------------|-------|

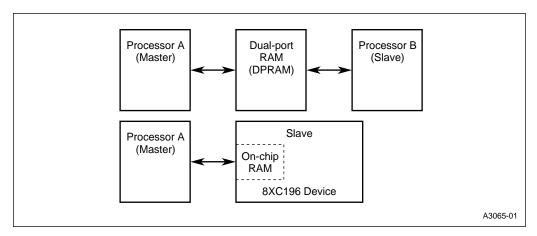

| 9-1    | DPRAM vs Slave-Port Solution                             | 9-2   |

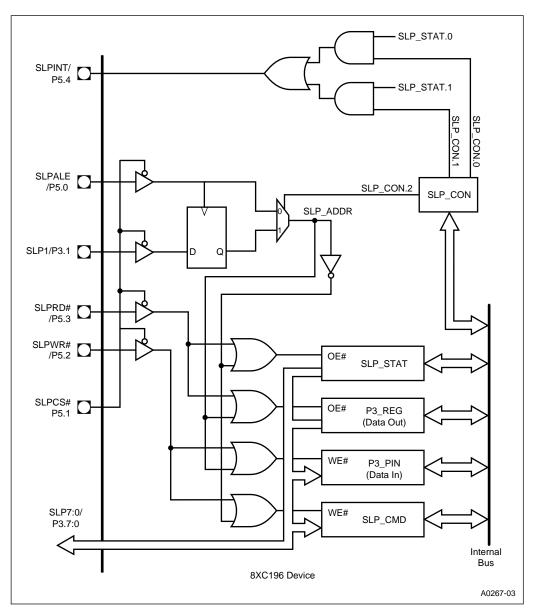

| 9-2    | Slave Port Block Diagram                                 | 9-3   |

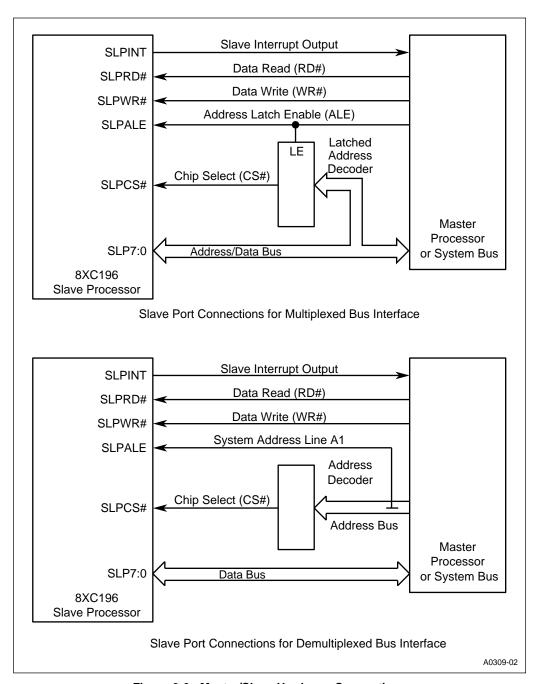

| 9-3    | Master/Slave Hardware Connections                        | 9-7   |

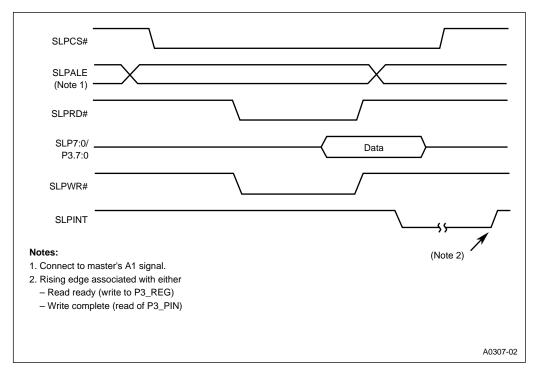

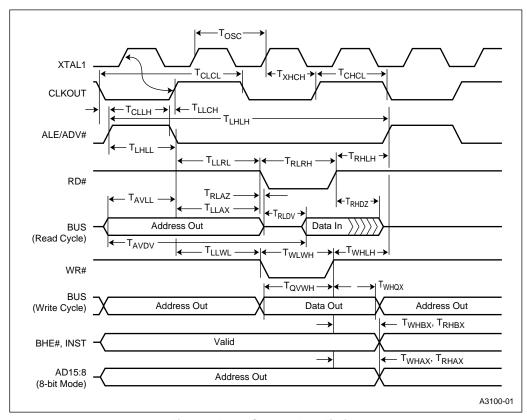

| 9-4    | Standard Slave Mode Timings (Demultiplexed Bus)          | 9-10  |

| 9-5    | Standard or Shared Memory Mode Timings (Multiplexed Bus) | 9-13  |

| 9-6    | Slave Port Control (SLP_CON) Register                    |       |

| 9-7    | Slave Port Status (SLP_STAT) Register                    | 9-17  |

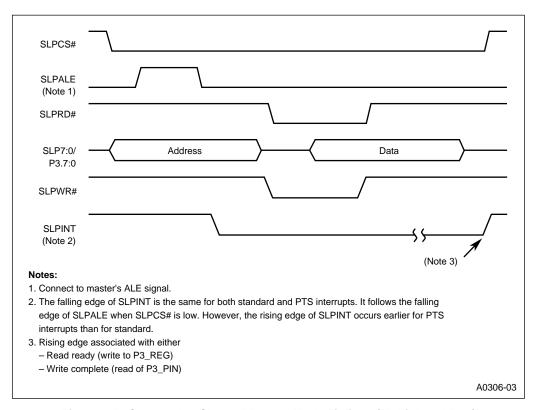

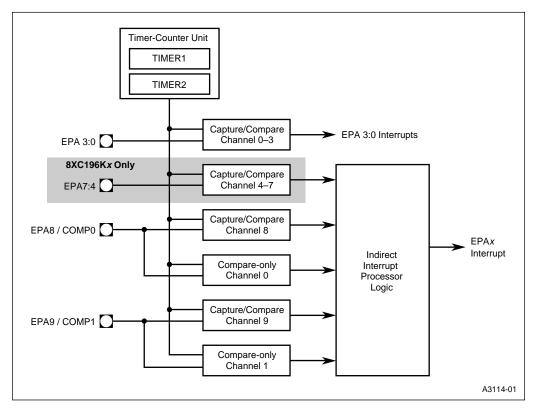

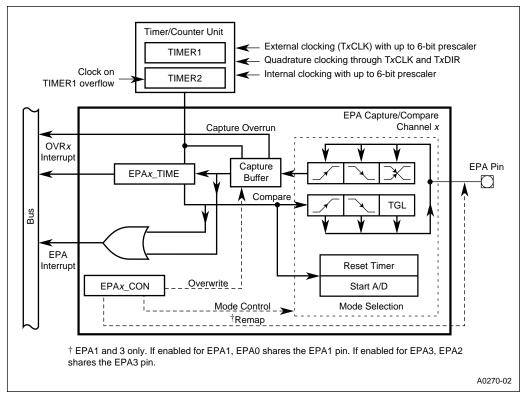

| 10-1   | EPA Block Diagram                                        | 10-2  |

| 10-2   | EPA Timer/Counters                                       | 10-6  |

| 10-3   | Quadrature Mode Interface                                | 10-8  |

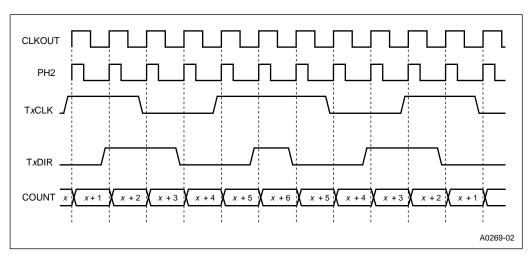

| 10-4   | Quadrature Mode Timing and Count                         | 10-9  |

| 10-5   | A Single EPA Capture/Compare Channel                     | 10-10 |

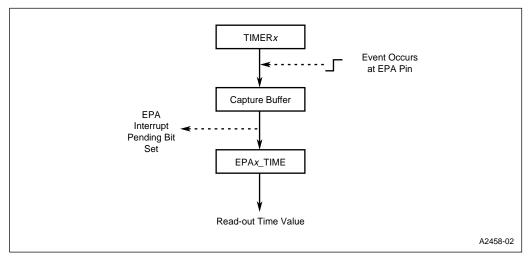

| 10-6   | EPA Simplified Input-Capture Structure                   | 10-11 |

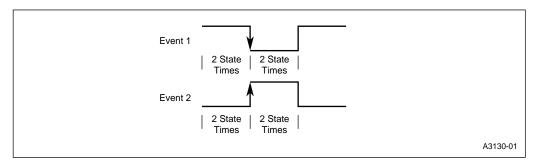

| 10-7   | Valid EPA Input Events                                   |       |

| 10-8   | Timer 1 Control (T1CONTROL) Register                     | 10-18 |

| 10-9   | Timer 2 Control (T2CONTROL) Register                     | 10-19 |

| 10-10  | EPA Control (EPAx_CON) Registers                         | 10-21 |

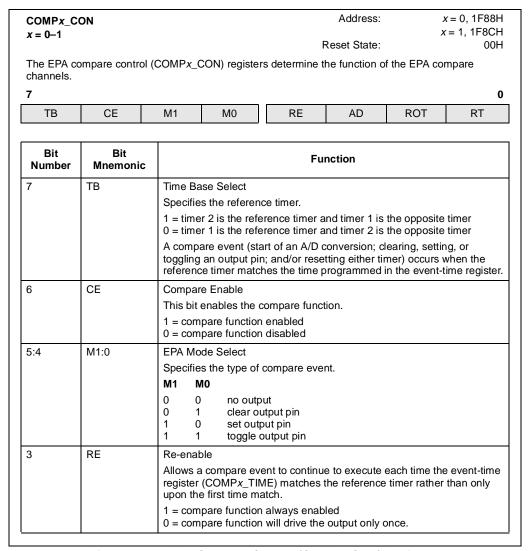

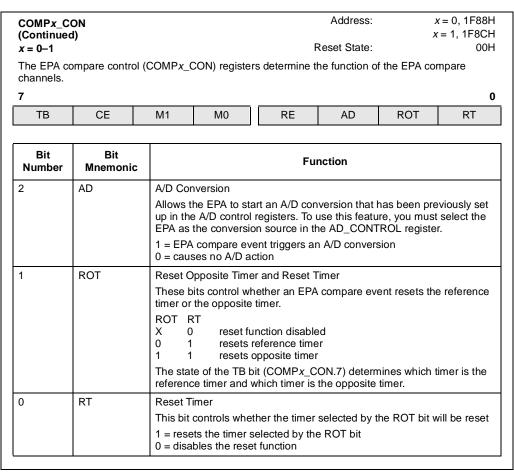

| 10-11  | EPA Compare Control (COMPx_CON) Registers                | 10-25 |

| 10-12  | EPA Interrupt Mask (EPA_MASK) Register                   | 10-27 |

| 10-13  | EPA Interrupt Mask 1 (EPA_MASK1) Register                |       |

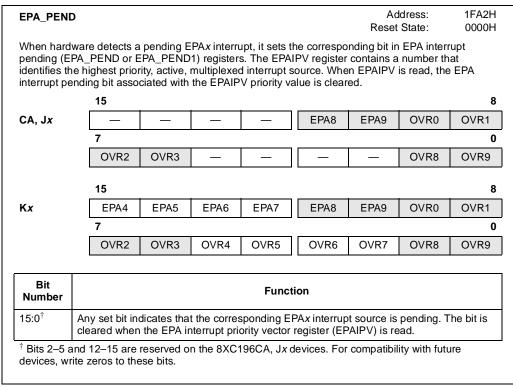

| 10-14  | EPA Interrupt Pending (EPA_PEND) Register                | 10-28 |

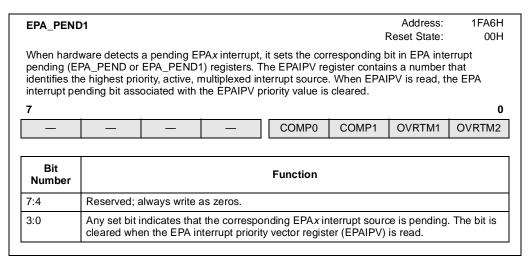

| 10-15  | EPA Interrupt Pending 1 (EPA_PEND1) Registers            |       |

| 10-16  | EPA Interrupt Priority Vector Register (EPAIPV)          |       |

| 11-1   | A/D Converter Block Diagram                              |       |

| 11-2   | A/D Test (AD_TEST) Register                              |       |

| 11-3   | A/D Result (AD_RESULT) Register — Write Format           |       |

| 11-4   | A/D Time (AD_TIME) Register                              |       |

| 11-5   | A/D Command (AD_COMMAND) Register                        |       |

| 11-6   | A/D Result (AD_RESULT) Register — Read Format            |       |

| 11-7   | Idealized A/D Sampling Circuitry                         |       |

| 11-8   | Suggested A/D Input Circuit                              |       |

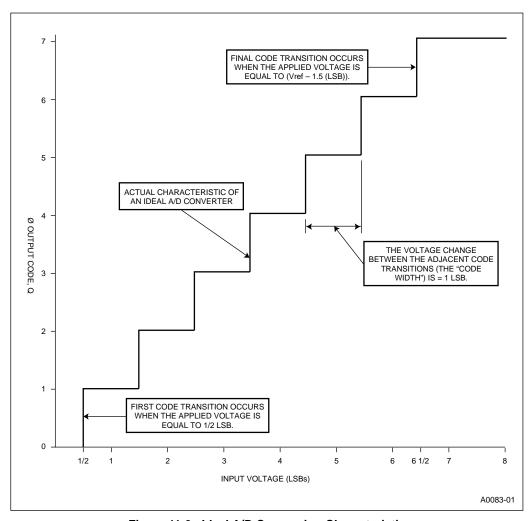

| 11-9   | Ideal A/D Conversion Characteristic                      |       |

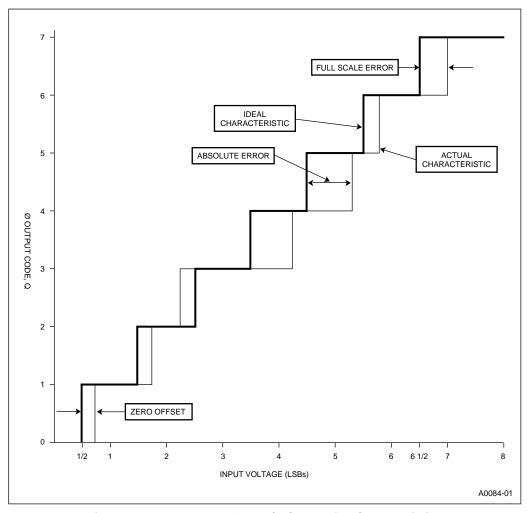

| 11-10  | Actual and Ideal A/D Conversion Characteristics          |       |

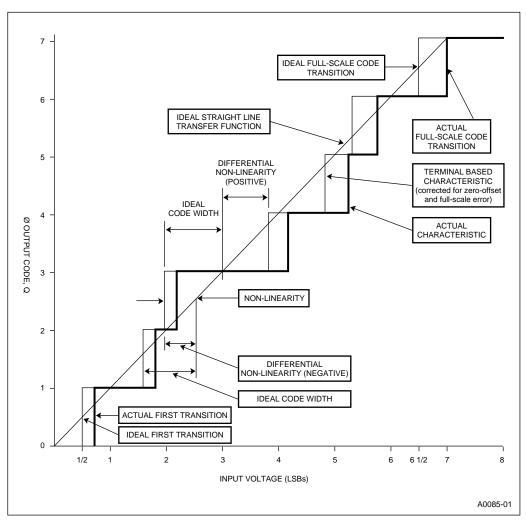

| 11-11  | Terminal-based A/D Conversion Characteristic             |       |

| 12-1   | A System Using CAN Controllers                           |       |

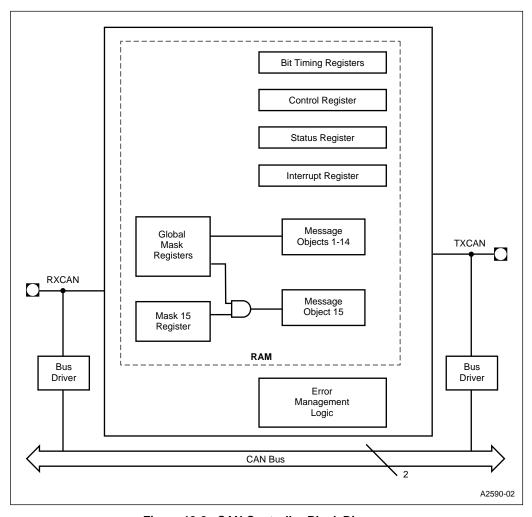

| 12-2   | CAN Controller Block Diagram                             |       |

| 12-3   | CAN Message Frames                                       |       |

| 12-4   | A Bit Time as Specified by the CAN Protocol              |       |

| 12-5   | A Bit Time as Implemented in the CAN Controller          |       |

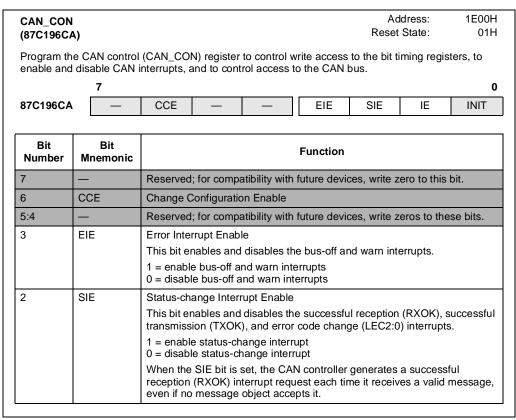

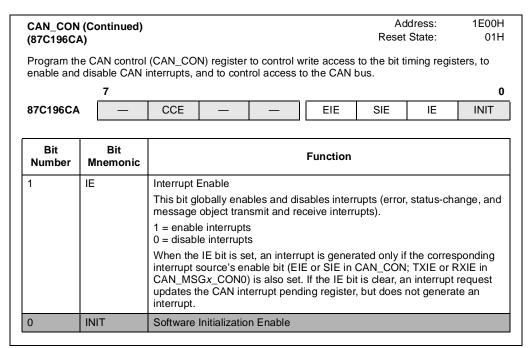

| 12-6   | CAN Control (CAN_CON) Register                           |       |

| 12-7   | CAN Bit Timing 0 (CAN_BTIME0) Register                   |       |

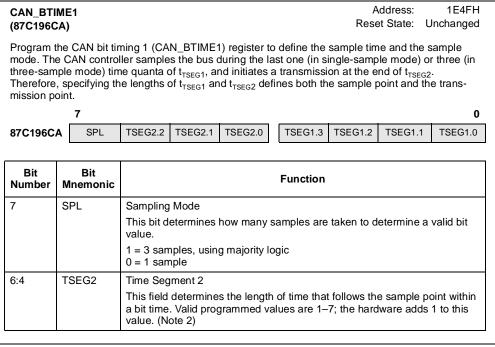

| 12-8   | CAN Bit Timing 1 (CAN_BTIME1) Register                   |       |

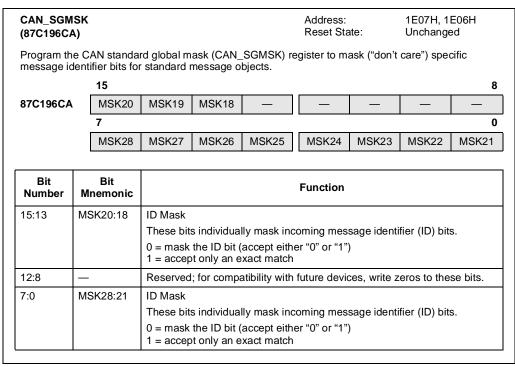

| 12-9   | CAN Standard Global Mask (CAN_SGMSK) Register            |       |

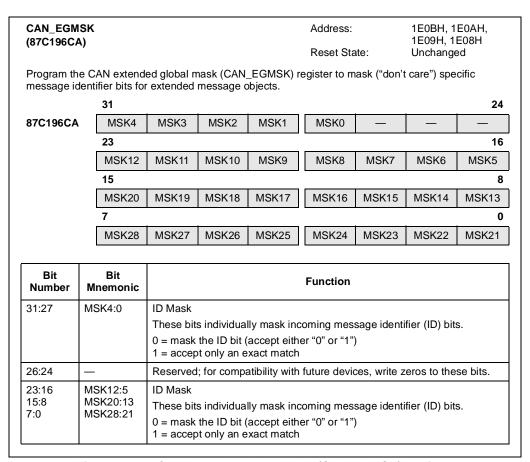

| 12-10  | CAN Extended Global Mask (CAN_EGMSK) Register            | 12-19 |

| Figure |                                                                    | Page  |

|--------|--------------------------------------------------------------------|-------|

| 12-11  | CAN Message 15 Mask (CAN_MSK15) Register                           | 12-20 |

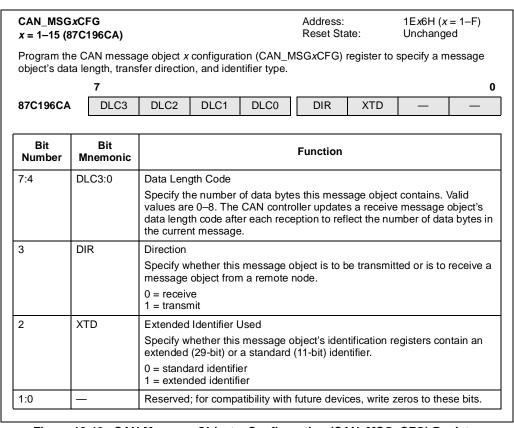

| 12-12  | CAN Message Object x Configuration (CAN_MSGxCFG) Register          | 12-21 |

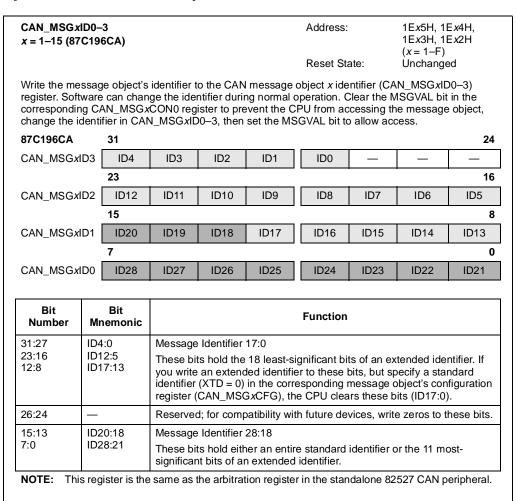

| 12-13  | CAN Message Object x Identifier (CAN_MSGxID0-3) Register           |       |

| 12-14  | CAN Message Object x Control 0 (CAN_MSGxCON0) Register             | 12-24 |

| 12-15  | CAN Message Object x Control 1 (CAN_MSGxCON1) Register             | 12-26 |

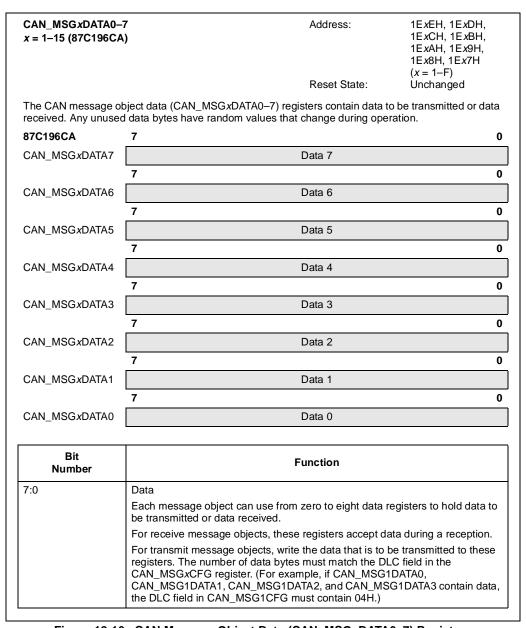

| 12-16  | CAN Message Object Data (CAN_MSGxDATA0-7) Registers                | 12-28 |

| 12-17  | CAN Control (CAN_CON) Register                                     | 12-29 |

| 12-18  | CAN Message Object x Control 0 (CAN_MSGxCON0) Register             | 12-31 |

| 12-19  | CAN Interrupt Pending (CAN_INT) Register                           | 12-32 |

| 12-20  | CAN Status (CAN_STAT) Register                                     |       |

| 12-21  | CAN Message Object x Control 0 (CAN_MSGxCON0) Register             | 12-34 |

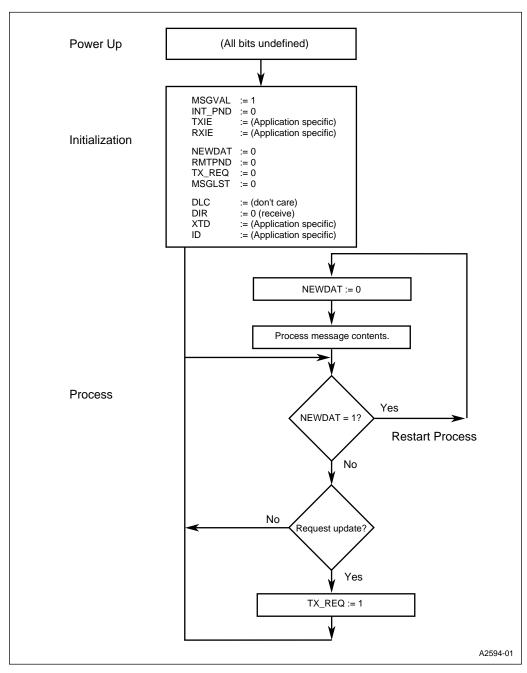

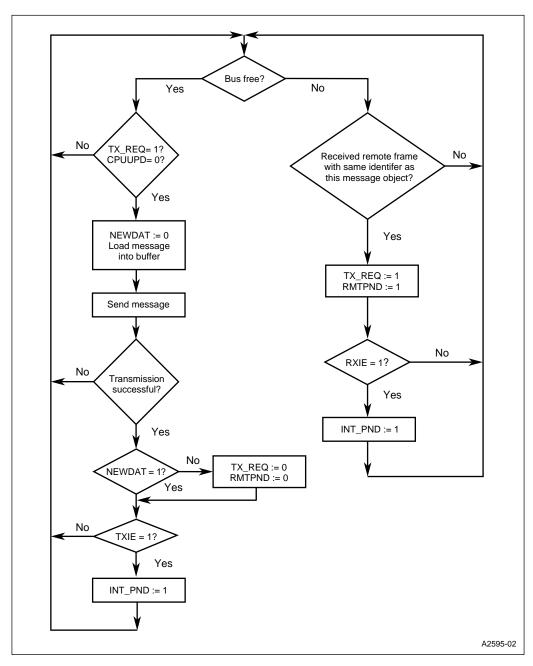

| 12-22  | Receiving a Message for Message Objects 1–14 — CPU Flow            | 12-36 |

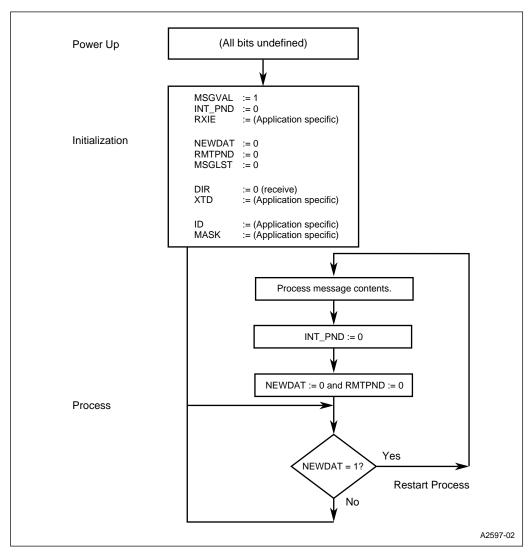

| 12-23  | Receiving a Message for Message Object 15 — CPU Flow               | 12-37 |

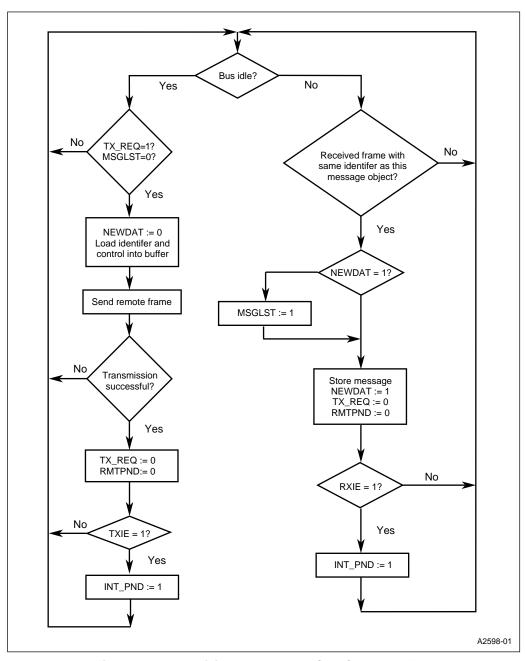

| 12-24  | Receiving a Message — CAN Controller Flow                          |       |

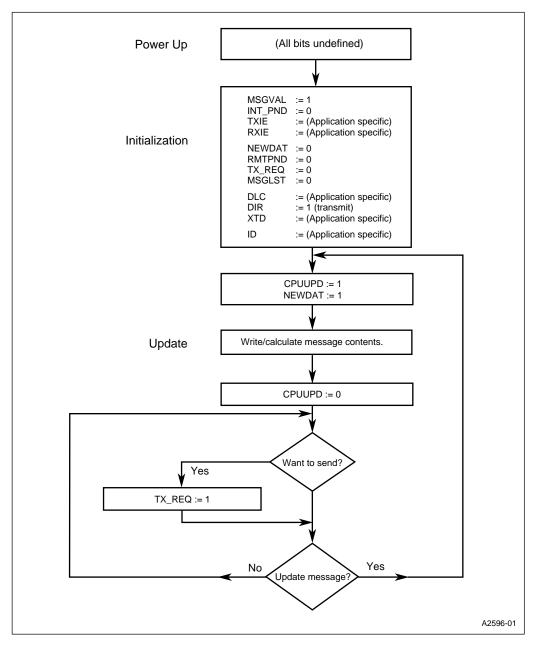

| 12-25  | Transmitting a Message — CPU Flow                                  | 12-39 |

| 12-26  | Transmitting a Message — CAN Controller Flow                       | 12-40 |

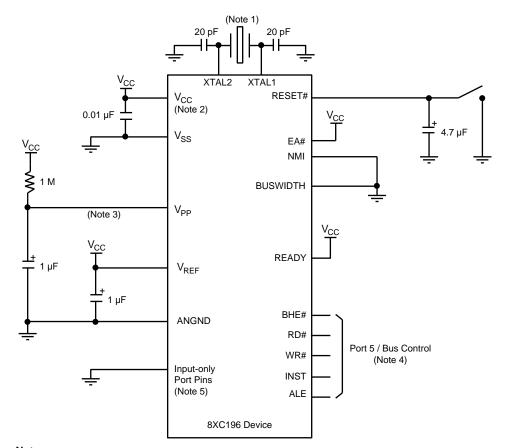

| 13-1   | Minimum Hardware Connections                                       | 13-3  |

| 13-2   | Power and Return Connections                                       | 13-4  |

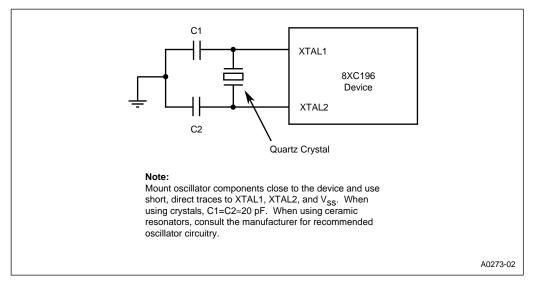

| 13-3   | On-chip Oscillator Circuit                                         | 13-6  |

| 13-4   | External Crystal Connections                                       |       |

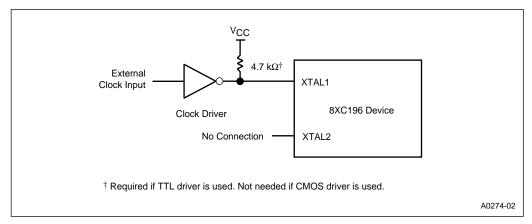

| 13-5   | External Clock Connections                                         |       |

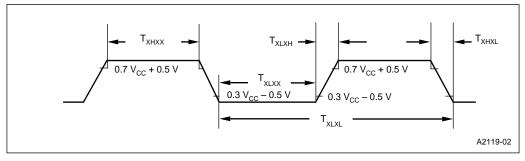

| 13-6   | External Clock Drive Waveforms                                     | 13-8  |

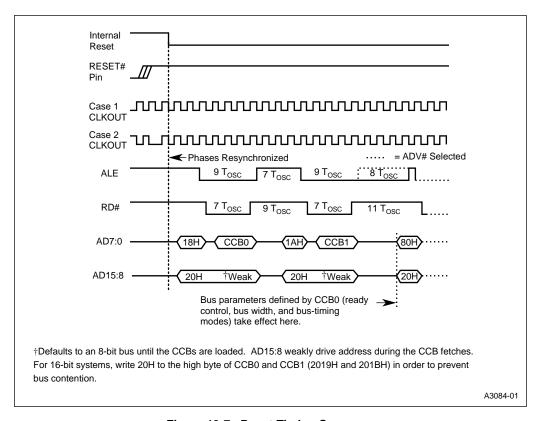

| 13-7   | Reset Timing Sequence                                              | 13-9  |

| 13-8   | Internal Reset Circuitry                                           | 13-10 |

| 13-9   | Minimum Reset Circuit                                              | 13-11 |

| 13-10  | Example System Reset Circuit                                       | 13-11 |

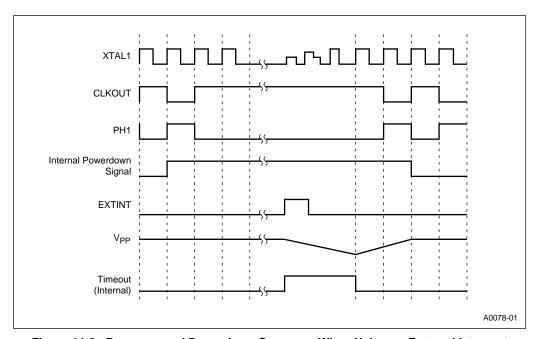

| 14-1   | Clock Control During Power-saving Modes                            | 14-3  |

| 14-2   | Power-up and Powerdown Sequence When Using an External Interrupt   | 14-6  |

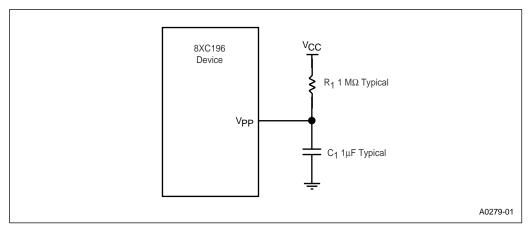

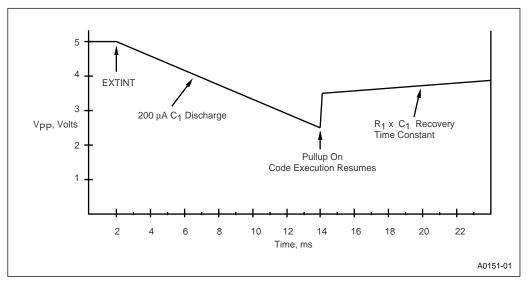

| 14-3   | External RC Circuit                                                |       |

| 14-4   | Typical Voltage on the V <sub>PP</sub> Pin While Exiting Powerdown | 14-8  |

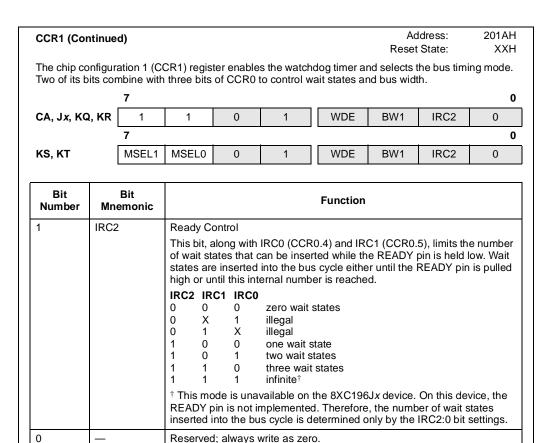

| 15-1   | Chip Configuration 0 (CCR0) Register                               | 15-5  |

| 15-2   | Chip Configuration 1 (CCR1) Register                               | 15-7  |

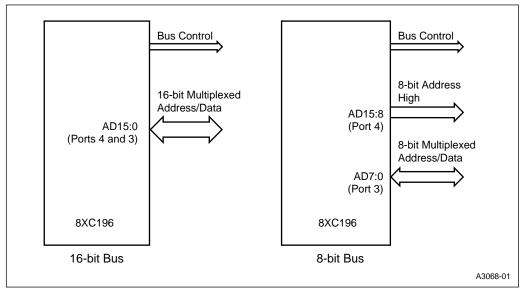

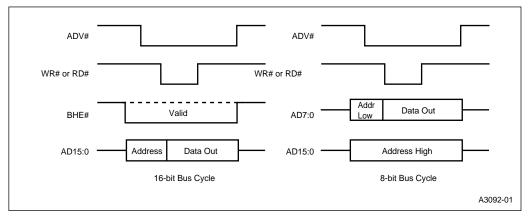

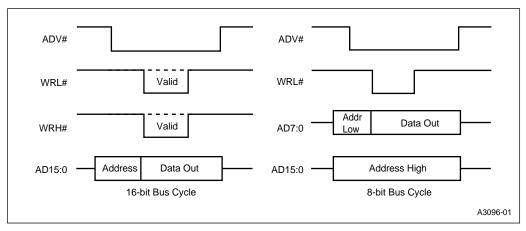

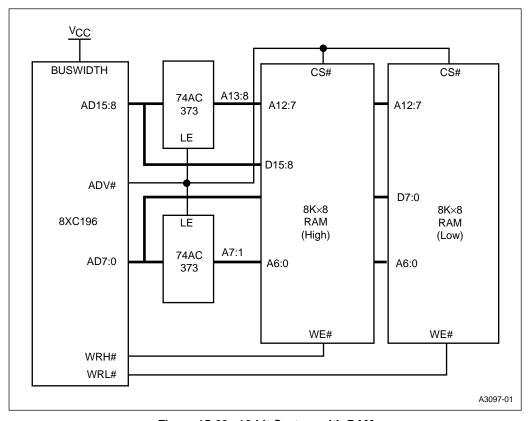

| 15-3   | Multiplexing and Bus Width Options                                 | 15-9  |

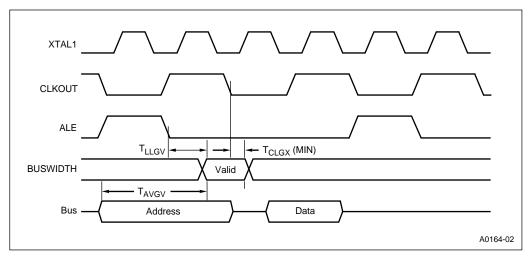

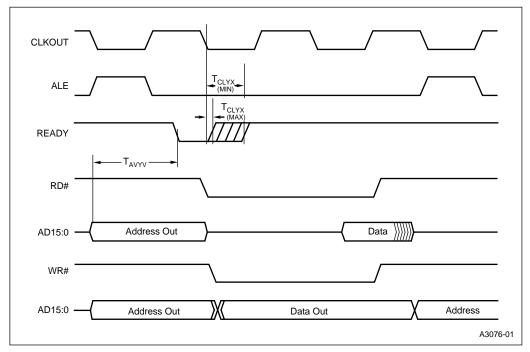

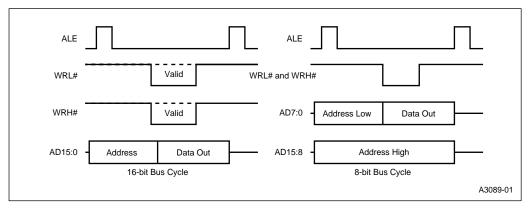

| 15-4   | BUSWIDTH Timing Diagram                                            | 15-10 |

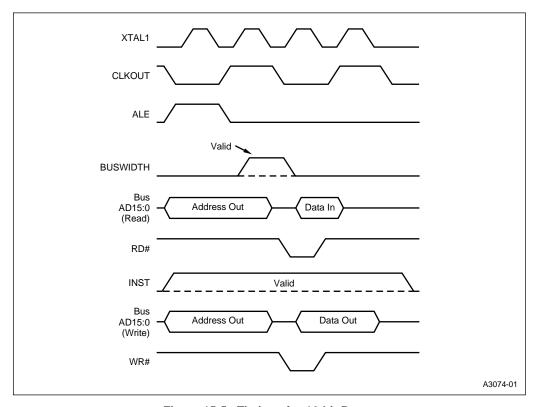

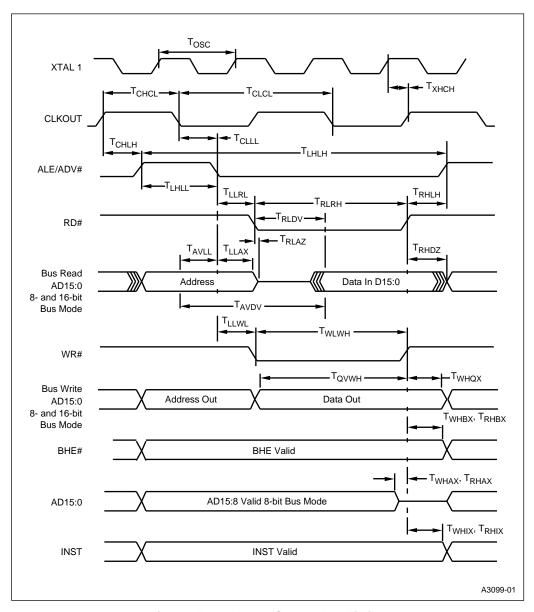

| 15-5   | Timings for 16-bit Buses                                           | 15-12 |

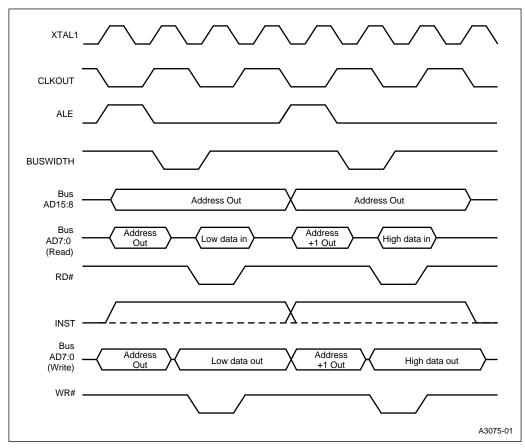

| 15-6   | Timings for 8-bit Buses                                            | 15-14 |

| 15-7   | READY Timing Diagram                                               | 15-16 |

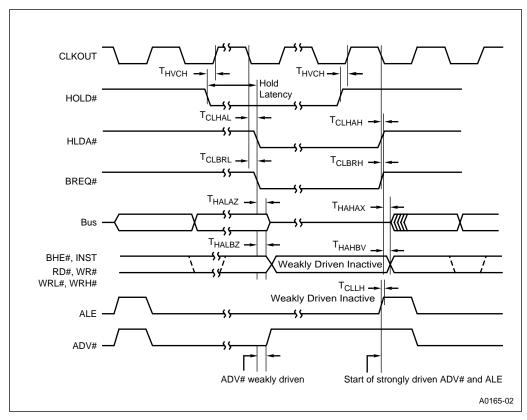

| 15-8   | HOLD#, HLDA# Timing                                                | 15-17 |

| 15-9   | Standard Bus Control                                               |       |

| 15-10  | Decoding WRL# and WRH#                                             |       |

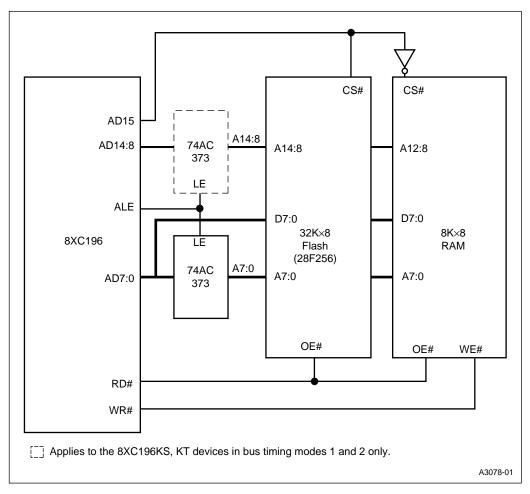

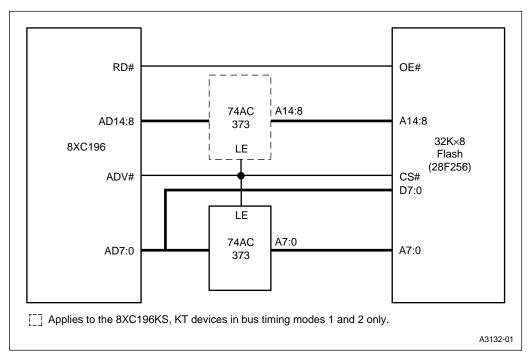

| 15-11  | 8-bit System with Flash and RAM                                    | 15-22 |

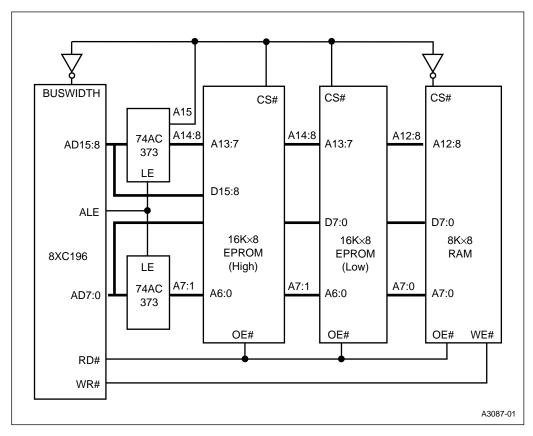

| 15-12  | 16-bit System with Dynamic Bus Width                               | 15-23 |

| 15-13  | Write Strobe Mode                                                  |       |

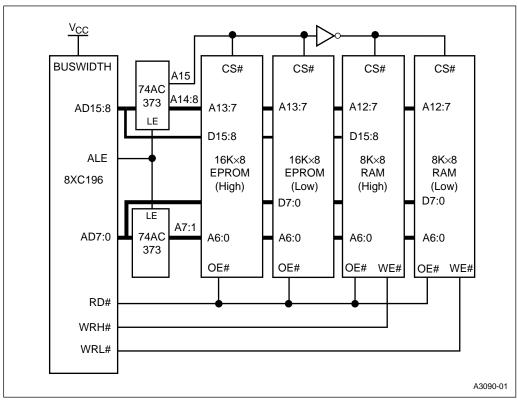

| 15-14  | 16-bit System with Single-byte Writes to RAM                       | 15-25 |

|        |                                                                    |       |

| Figure |                                                  | Page  |

|--------|--------------------------------------------------|-------|

| 15-15  | Address Valid Strobe Mode                        | 15-26 |

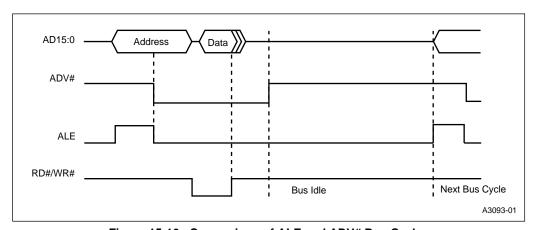

| 15-16  | Comparison of ALE and ADV# Bus Cycles            | 15-26 |

| 15-17  | 8-bit System with Flash                          | 15-27 |

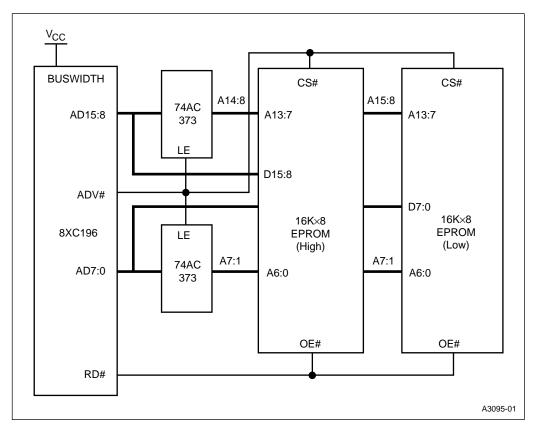

| 15-18  | 16-bit System with EPROM                         | 15-28 |

| 15-19  | Timings of Address Valid with Write Strobe Mode  | 15-29 |

| 15-20  | 16-bit System with RAM                           |       |

| 15-21  | Modes 0, 1, 2, and 3 Timings                     | 15-31 |

| 15-22  | Mode 1 System Bus Timing                         | 15-33 |

| 15-23  | Mode 2 System Bus Timing                         | 15-35 |

| 15-24  | System Bus Timing                                | 15-36 |

| 16-1   | Unerasable PROM (USFR) Register                  | 16-7  |

| 16-2   | Programming Pulse Width Register (PPW or SP_PPW) | 16-9  |

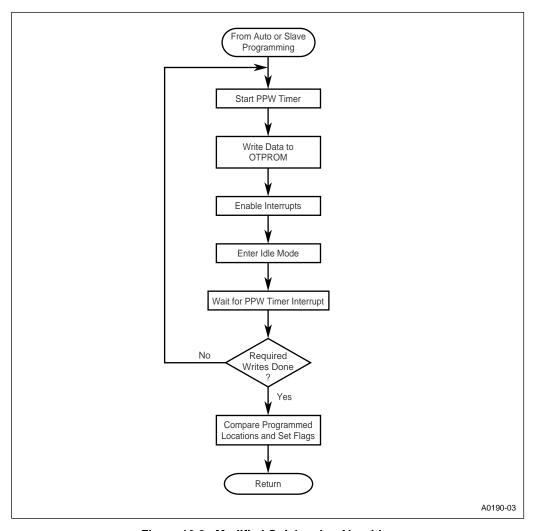

| 16-3   | Modified Quick-pulse Algorithm                   | 16-10 |

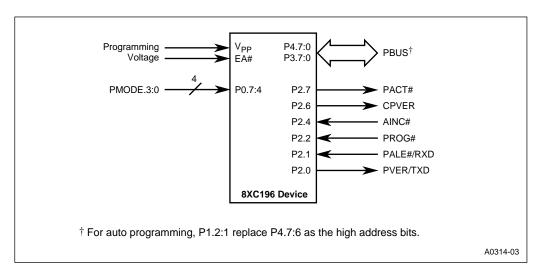

| 16-4   | Pin Functions in Programming Modes               | 16-11 |

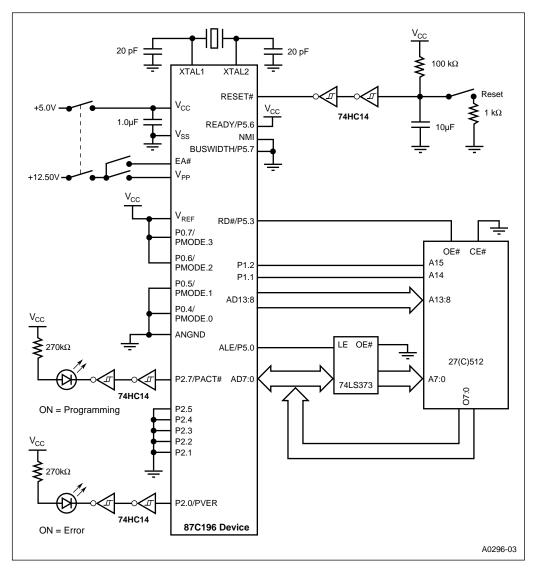

| 16-5   | Slave Programming Circuit                        | 16-17 |

| 16-6   | Chip Configuration Registers (CCRs)              | 16-19 |

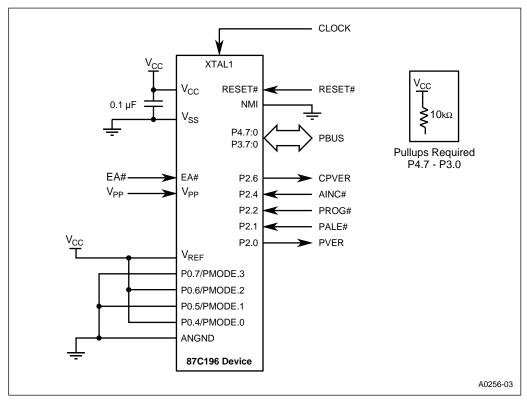

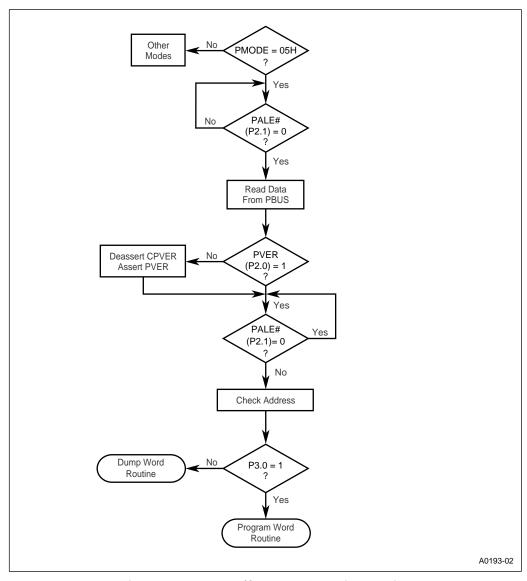

| 16-7   | Address/Command Decoding Routine                 | 16-21 |

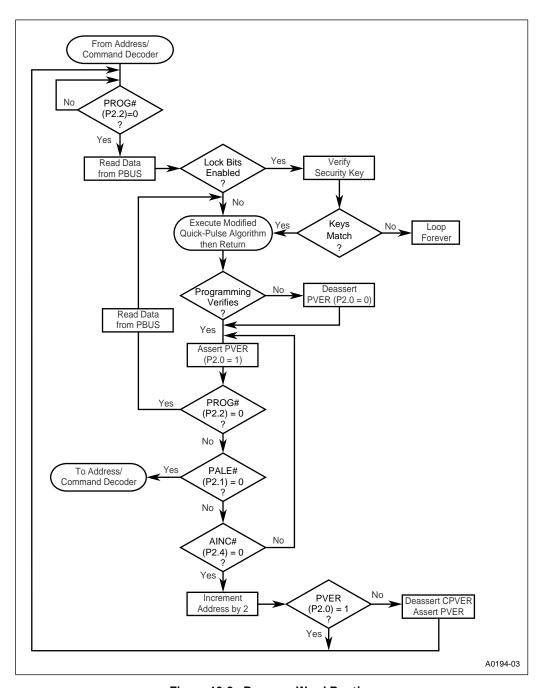

| 16-8   | Program Word Routine                             | 16-22 |

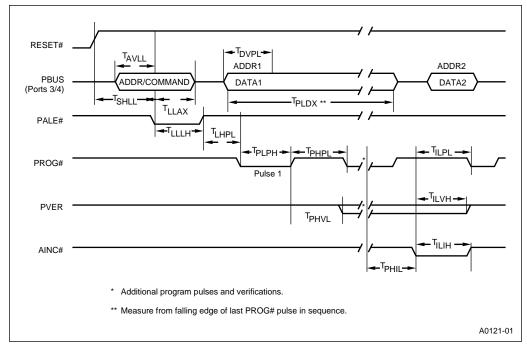

| 16-9   | Program Word Waveform                            | 16-23 |

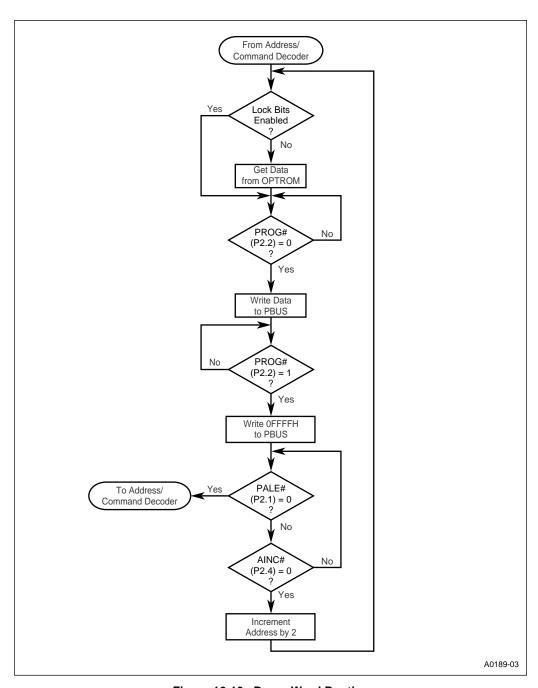

| 16-10  | Dump Word Routine                                | 16-24 |

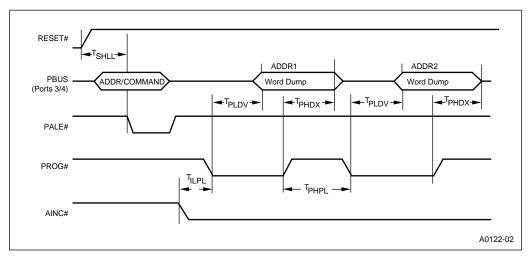

| 16-11  | Dump Word Waveform                               | 16-25 |

| 16-12  | Auto Programming Circuit for 8XC196Kx Devices    | 16-27 |

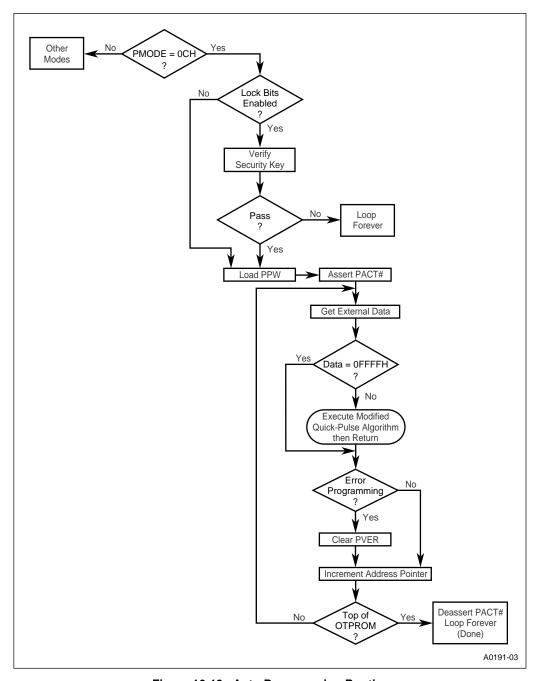

| 16-13  | Auto Programming Routine                         | 16-29 |

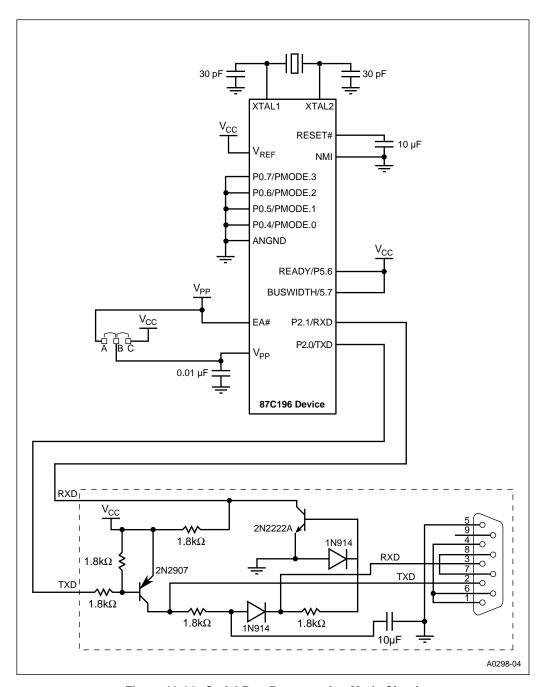

| 16-14  | Serial Port Programming Mode Circuit             | 16-33 |

| 16-15  | Run-time Programming Code Example                | 16-45 |

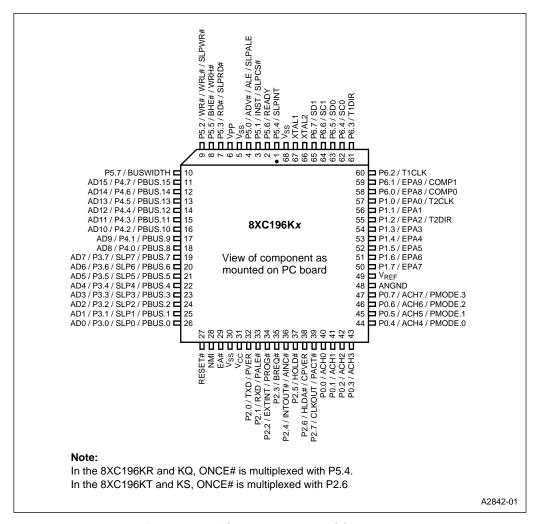

| B-1    | 8XC196Kx 68-lead PLCC Package                    | B-3   |

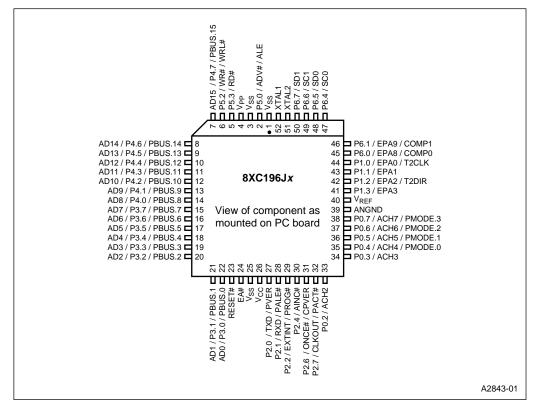

| B-2    | 8XC196Jx 52-lead PLCC Package                    | B-5   |

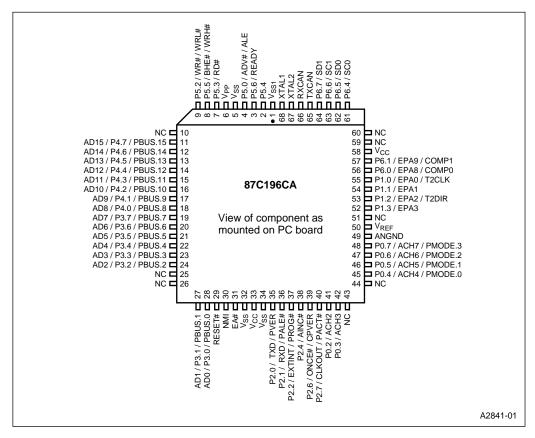

| B-3    | 87C196CA 68-lead PLCC Package                    | B-7   |

|        |                                                  |       |

| Table |                                                                   | Page |

|-------|-------------------------------------------------------------------|------|

| 1-1   | Handbooks and Product Information                                 | 1-6  |

| 1-2   | Application Notes, Application Briefs, and Article Reprints       | 1-6  |

| 1-3   | MCS® 96 Microcontroller Datasheets (Commercial/Express)           |      |

| 1-4   | MCS® 96 Microcontroller Datasheets (Automotive)                   | 1-7  |

| 1-5   | MCS® 96 Microcontroller Quick References                          |      |

| 2-1   | Features of the 8XC196Kx, Jx, CA Product Family                   | 2-2  |

| 2-2   | State Times at Various Frequencies                                | 2-8  |

| 2-3   | Unsupported Functions in 87C196CA Devices                         | 2-13 |

| 2-4   | Unsupported Functions in 8XC196Jx Devices                         | 2-14 |

| 3-1   | Operand Type Definitions                                          | 3-1  |

| 3-2   | Equivalent Operand Types for Assembly and C Programming Languages | 3-2  |

| 3-3   | Definition of Temporary Registers                                 | 3-6  |

| 4-1   | Memory Map                                                        | 4-2  |

| 4-2   | Special-purpose Memory Addresses                                  | 4-3  |

| 4-3   | Memory-mapped SFRs                                                | 4-5  |

| 4-4   | Peripheral SFRs                                                   | 4-7  |

| 4-5   | CAN Peripheral SFRs — 8XC196CA Only                               | 4-8  |

| 4-6   | Register File Memory Addresses                                    | 4-11 |

| 4-7   | CPU SFRs                                                          | 4-13 |

| 4-8   | Selecting a Window of Peripheral SFRs                             | 4-16 |

| 4-9   | Selecting a Window of the Upper Register File                     | 4-16 |

| 4-10  | Selecting a Window of Upper Register RAM — 8XC196JV Only          | 4-17 |

| 4-11  | Windows                                                           | 4-18 |

| 4-12  | Windowed Base Addresses                                           | 4-20 |

| 5-1   | Interrupt Signals                                                 | 5-3  |

| 5-2   | Interrupt and PTS Control and Status Registers                    | 5-3  |

| 5-3   | Interrupt Sources, Vectors, and Priorities                        | 5-5  |

| 5-4   | Execution Times for PTS Cycles                                    |      |

| 5-5   | Single Transfer Mode PTSCB                                        |      |

| 5-6   | Block Transfer Mode PTSCB                                         |      |

| 5-7   | A/D Scan Mode Command/Data Table                                  |      |

| 5-8   | Command/Data Table (Example 1)                                    |      |

| 5-9   | A/D Scan Mode PTSCB (Example 1)                                   |      |

| 5-10  | Command/Data Table (Example 2)                                    |      |

| 5-11  | A/D Scan Mode PTSCB (Example 2)                                   |      |

| 5-12  | Comparison of PWM Modes                                           |      |

| 5-13  | PWM Toggle Mode PTSCB                                             |      |

| 5-14  | PWM Remap Mode PTSCB                                              |      |

| 6-1   | Device I/O Ports                                                  |      |

| 6-2   | Standard Input-only Port Pins                                     |      |

| 6-3   | Input-only Port Registers                                         |      |

| 6-4   | Bidirectional Port Pins                                           |      |

| 6-5   | Bidirectional Port Control and Status Registers                   |      |

| 6-6   | Logic Table for Bidirectional Ports in I/O Mode                   | 6-9  |

| Table |                                                              | Page  |

|-------|--------------------------------------------------------------|-------|

| 6-7   | Logic Table for Bidirectional Ports in Special-function Mode | 6-9   |

| 6-8   | Control Register Values for Each Configuration               | 6-11  |

| 6-9   | Port Configuration Example                                   |       |

| 6-10  | Port Pin States After Reset and After Example Code Execution | 6-12  |

| 6-11  | Ports 3 and 4 Pins                                           | 6-16  |

| 6-12  | Ports 3 and 4 Control and Status Registers                   | 6-16  |

| 6-13  | Logic Table for Ports 3 and 4 as I/O                         | 6-18  |

| 7-1   | Serial Port Signals                                          | 7-2   |

| 7-2   | Serial Port Control and Status Registers                     |       |

| 7-3   | SP_BAUD Values When Using XTAL1 at 16 MHz                    | 7-12  |

| 8-1   | SSIO Port Signals                                            | 8-2   |

| 8-2   | SSIO Port Control and Status Registers                       |       |

| 8-3   | Common SSIO_BAUD Values at 16 MHz                            | 8-9   |

| 9-1   | Slave Port Signals                                           | 9-4   |

| 9-2   | Slave Port Control and Status Registers                      | 9-4   |

| 9-3   | Master and Slave Interconnections                            | 9-6   |

| 10-1  | EPA Channels                                                 | 10-1  |

| 10-2  | EPA and Timer/Counter Signals                                |       |

| 10-3  | EPA Control and Status Registers                             | 10-3  |

| 10-4  | Quadrature Mode Truth Table                                  | 10-8  |

| 10-5  | Action Taken when a Valid Edge Occurs                        | 10-12 |

| 10-6  | Example Control Register Settings and EPA Operations         | 10-20 |

| 10-7  | EPAIPV Interrupt Priority Values                             |       |

| 11-1  | A/D Converter Pins                                           |       |

| 11-2  | A/D Control and Status Registers                             | 11-2  |

| 12-1  | CAN Controller Signals                                       |       |

| 12-2  | Control and Status Registers                                 |       |

| 12-3  | CAN Controller Address Map                                   | 12-5  |

| 12-4  | Message Object Structure                                     | 12-6  |

| 12-5  | Effect of Masking on Message Identifiers                     |       |

| 12-6  | Standard Message Frame                                       | 12-8  |

| 12-7  | Extended Message Frame                                       |       |

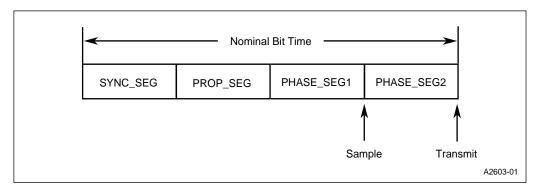

| 12-8  | CAN Protocol Bit Time Segments                               | 12-10 |

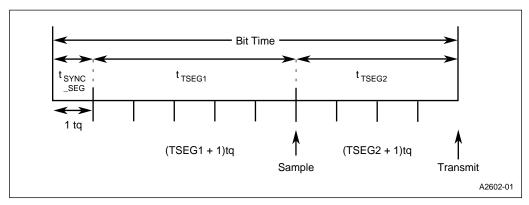

| 12-9  | CAN Controller Bit Time Segments                             | 12-11 |

| 12-10 | Bit Timing Relationships                                     | 12-12 |

| 12-11 | Bit Timing Requirements for Synchronization                  | 12-17 |

| 12-12 | Control Register Bit-pair Interpretation                     | 12-23 |

| 12-13 | Cross-reference for Register Bits Shown in Flowcharts        | 12-35 |

| 12-14 | Register Values Following Reset                              | 12-41 |

| 13-1  | Minimum Required Signals                                     | 13-1  |

| 13-2  | I/O Port Configuration Guide                                 | 13-2  |

| 14-1  | Operating Mode Control Signals                               | 14-1  |

| 14-2  | Operating Mode Control and Status Registers                  | 14-2  |

| 14-3  | ONCE# Pin Alternate Functions                                | 14-9  |

| Table |                                                                        | Page  |

|-------|------------------------------------------------------------------------|-------|

| 14-4  | Test-mode-entry Pins                                                   | 14-10 |

| 15-1  | External Memory Interface Signals                                      |       |

| 15-2  | READY Signal Timing Definitions                                        | 15-16 |

| 15-3  | HOLD#, HLDA# Timing Definitions                                        | 15-18 |

| 15-4  | Maximum Hold Latency                                                   | 15-19 |

| 15-5  | Bus-control Mode                                                       |       |

| 15-6  | Modes 0, 1, 2, and 3 Timing Comparisons                                | 15-32 |

| 15-7  | AC Timing Symbol Definitions                                           |       |

| 15-8  | AC Timing Definitions                                                  | 15-37 |

| 16-1  | OTPROM Sizes for 87C196Kx, Jx, CA Devices                              | 16-1  |

| 16-2  | 87C196Kx OTPROM Memory Map                                             | 16-3  |

| 16-3  | Memory Protection for Normal Operating Mode                            | 16-4  |

| 16-4  | Memory Protection Options for Programming Modes                        | 16-5  |

| 16-5  | UPROM Programming Values and Locations for Slave Mode                  | 16-8  |

| 16-6  | Pin Descriptions                                                       |       |

| 16-7  | PMODE Values                                                           | 16-14 |

| 16-8  | Device Signature Word and Programming Voltages                         | 16-16 |

| 16-9  | Slave Programming Mode Memory Map                                      |       |

| 16-10 | Timing Mnemonics                                                       |       |

| 16-11 | Auto Programming Memory Map                                            |       |

| 16-12 | Serial Port Programming Mode Memory Map                                |       |

| 16-13 | Serial Port Programming Default Values and Locations                   |       |

| 16-14 | User Program Register Values and Test ROM Locations                    |       |

| 16-15 | RISM Command Descriptions                                              |       |

| A-1   | Opcode Map (Left Half)                                                 |       |

| A-1   | Opcode Map (Right Half)                                                |       |

| A-2   | Processor Status Word (PSW) Flags                                      |       |

| A-3   | Effect of PSW Flags or Specified Bits on Conditional Jump Instructions |       |

| A-4   | PSW Flag Setting Symbols                                               |       |

| A-5   | Operand Variables                                                      |       |

| A-6   | Instruction Set                                                        | A-7   |

| A-7   | Instruction Opcodes                                                    | A-42  |

| A-8   | Instruction Lengths and Hexadecimal Opcodes                            |       |

| A-9   | Instruction Execution Times (in State Times)                           | A-54  |

| B-1   | Signal Name Changes                                                    | B-1   |

| B-2   | 8XC196Kx Signals Arranged by Functional Categories                     | B-2   |

| B-3   | 8XC196Jx Signals Arranged by Functional Categories                     | B-4   |

| B-4   | 87C196CA Signals Arranged by Functional Categories                     |       |

| B-5   | Description of Columns of Table B-6                                    | B-8   |

| B-6   | Signal Descriptions                                                    | B-8   |

| B-7   | Definition of Status Symbols                                           |       |

| B-8   | 8XC196Kx Pin Status                                                    | B-20  |

| B-9   | 8XC196Jx Pin Status                                                    | B-21  |

| B-10  | 87C196CA Pin Status                                                    | B-22  |

| Table |                                                       | Page |

|-------|-------------------------------------------------------|------|

| C-1   | Modules and Related Registers                         |      |

| C-2   | Register Name, Address, and Reset Status              |      |

| C-3   | CAN_EGMSK Addresses and Reset Values                  | C-15 |

| C-4   | CAN_MSGxCFG Addresses and Reset Values                | C-17 |

| C-5   | CAN_MSGxCON0 Addresses and Reset Values               | C-19 |

| C-6   | CAN_MSGxCON1 Addresses and Reset Values               | C-21 |

| C-7   | CAN_MSGxDATA0-7 Addresses                             | C-23 |

| C-8   | CAN_MSGxID0-3 Addresses                               | C-25 |

| C-9   | CAN_MSK15 Addresses and Reset Values                  | C-26 |

| C-10  | COMPx_CON Addresses and Reset Values                  | C-34 |

| C-11  | COMPx_TIME Addresses and Reset Values                 | C-35 |

| C-12  | EPAx_CON Addresses and Reset Values                   | C-43 |

| C-13  | EPAx_TIME Addresses and Reset Values                  | C-44 |

| C-14  | EPA Interrupt Priority Vectors                        |      |

| C-15  | Px_DIR Addresses and Reset Values                     | C-51 |

| C-16  | Px_MODE Addresses and Reset Values                    |      |

| C-17  | Special-function Signals for Ports 1, 2, 5, 6         | C-53 |

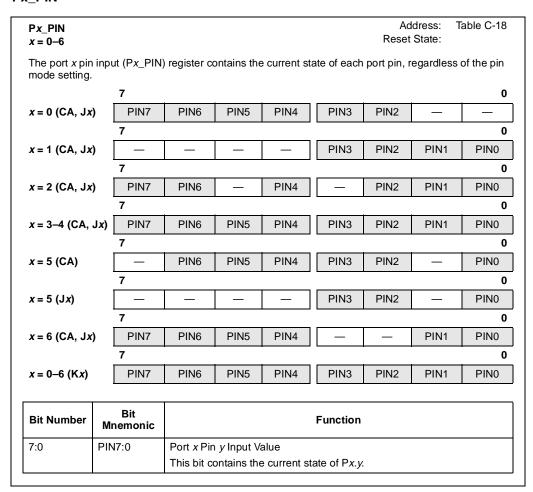

| C-18  | Px_PIN Addresses and Reset Values                     | C-54 |

| C-19  | Px_REG Addresses and Reset Values                     |      |

| C-20  | Common SSIO_BAUD Values at 16 MHz                     |      |

| C-21  | SSIOx_BUF Addresses and Reset Values                  | C-72 |

| C-22  | SSIOx_CON Addresses and Reset Values                  |      |

| C-23  | TIMERx Addresses and Reset Values                     |      |

| C-24  | WSR Settings and Direct Addresses for Windowable SFRs | C-80 |

intel®

# 1

# **Guide to This Manual**

# CHAPTER 1 GUIDE TO THIS MANUAL

This manual describes the 8XC196Kx, Jx, CA family of embedded microcontrollers. It is intended for use by both software and hardware designers familiar with the principles of microcontrollers. This chapter describes what you'll find in this manual, lists other documents that may be useful, and explains how to access the support services we provide to help you complete your design.

#### 1.1 MANUAL CONTENTS

This manual contains several chapters and appendixes, a glossary, and an index. This chapter, Chapter 1, provides an overview of the manual. This section summarizes the contents of the remaining chapters and appendixes. The remainder of this chapter describes notational conventions and terminology used throughout the manual, provides references to related documentation, describes customer support services, and explains how to access information and assistance.

**Chapter 2** — **Architectural Overview** — provides an overview of the device hardware. It describes the core, internal timing, internal peripherals, and special operating modes.

**Chapter 3** — **Programming Consider Ations** — provides an overview of the instruction set, describes general standards and conventions, and defines the operand types and addressing modes supported by the MCS<sup>®</sup> 96 microcontroller family. (For additional information about the instruction set, see Appendix A.)

**Chapter 4** — **Memory Partitions** — describes the addressable memory space of the device. It describes the memory partitions, explains how to use windows to increase the amount of memory that can be accessed with register-direct (8-bit) instructions, and provides examples of memory configurations.

**Chapter 5** — **Standard and PTS Interrupts** — describes the interrupt control circuitry, priority scheme, and timing for standard and peripheral transaction server (PTS) interrupts. It also explains interrupt programming and control.

**Chapter 6** — **I/O Ports** — describes the input/output ports and explains how to configure the ports for input, output, or special functions.

**Chapter 7** — **Serial I/O (SIO) Port** — describes the asynchronous/synchronous serial I/O (SIO) port and explains how to program it.

**Chapter 8** — **Synchronous Serial I/O (SSIO) Port** — describes the synchronous serial I/O (SSIO) port and explains how to program it.

**Chapter 9** — **Slave Port** — describes the slave port of the 8XC196Kx and explains how to program it. Chapter 6, "I/O Ports," explains how to configure port 3 to serve as the slave port. This chapter discusses additional configurations specific to the slave port function and describes how to use the slave port for interprocessor communication.

Chapter 10 — Event Processor Array (EPA) — describes the event processor array, a timer/counter-based, high-speed input/output unit. It describes the timer/counters and explains how to program the EPA and how to use the EPA to produce pulse-width modulated (PWM) outputs.

**Chapter 11** — **Analog-to-digital Converter** — provides an overview of the analog-to-digital (A/D) converter and describes how to program the converter, read the conversion results, and interface with external circuitry.

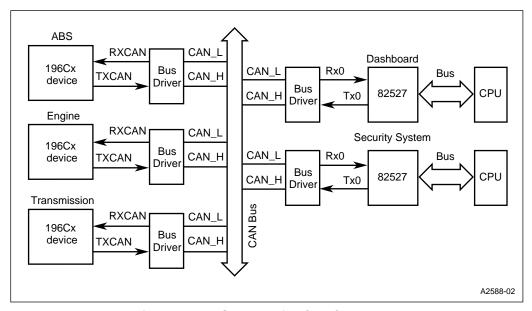

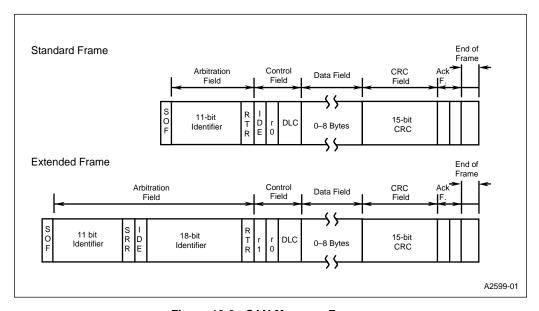

Chapter 12 — CAN Serial Communications Controller — describes the 8XC196CA's integrated CAN controller and explains how to configure it. This integrated peripheral is similar to Intel's standalone 82527 CAN serial communications controller, supporting both the standard and extended message frames specified by the CAN 2.0 protocol parts A and B.

**Chapter 13** — **Minimum Hardware Considerations** — describes options for providing the basic requirements for device operation within a system, discusses other hardware considerations, and describes device reset options.

**Chapter 14** — **Special Operating Modes** — provides an overview of the idle, powerdown, and on-circuit emulation (ONCE) modes and describes how to enter and exit each mode.

Chapter 15 — Interfacing with External Memory — lists the external memory signals and describes the registers that control the external memory interface. It discusses the bus width and memory configurations, the bus-hold protocol, write-control modes, and internal wait states and ready control. Finally, it provides timing information for the system bus.

Chapter 16 — Programming the Nonvolatile Memory — provides recommended circuits, the corresponding memory maps, and flow diagrams. It also provides procedures for auto programming, and describes the commands used for serial port programming.

**Appendix A** — **Instruction Set Reference** — provides reference information for the instruction set. It describes each instruction; defines the program status word (PSW) flags; shows the relationships between instructions and PSW flags; and lists hexadecimal opcodes, instruction lengths, and execution times. (For additional information about the instruction set, see Chapter 3, "Programming ConsiderAtions.")

**Appendix B** — **Signal Descriptions** — provides reference information for the device pins, including descriptions of the pin functions, reset status of the I/O and control pins, and package pin assignments.

#### **GUIDE TO THIS MANUAL**

**Appendix C** — **Registers** — provides a compilation of all device registers arranged alphabetically by register mnemonic. It also includes tables that list the windowed direct addresses for all SFRs in each possible window.

**Glossary** — defines terms with special meaning used throughout this manual.

**Index** — lists key topics with page number references.

### 1.2 NOTATIONAL CONVENTIONS AND TERMINOLOGY

The following notations and terminology are used throughout this manual. The Glossary defines other terms with special meanings.

#

The pound symbol (#) has either of two meanings, depending on the context. When used with a signal name, the symbol means that the signal is active low. When used in an instruction, the symbol prefixes an immediate value in immediate addressing mode.

**Assert and Deassert**

The terms *assert* and *deassert* refer to the act of making a signal active (enabled) and inactive (disabled), respectively. The active polarity (high/low) is defined by the signal name. Active-low signals are designated by a pound symbol (#) suffix; active-high signals have no suffix. To assert RD# is to drive it low; to assert ALE is to drive it high; to deassert RD# is to drive it high; to deassert ALE is to drive it low.

Clear and Set

The terms *clear* and *set* refer to the value of a bit or the act of giving it a value. If a bit is clear, its value is "0"; clearing a bit gives it a "0" value. If a bit is set, its value is "1"; setting a bit gives it a "1" value.

**Instructions**

Instruction mnemonics are shown in upper case to avoid confusion. You may use either upper case or lower case.

italics

Italics identify variables and introduce new terminology. The context in which italics are used distinguishes between the two possible meanings.

Variables in registers and signal names are commonly represented by x and y, where x represents the first variable and y represents the second variable. For example, in register  $Px\_MODE.y$ , x represents the variable that identifies the specific port, and y represents the register bit variable [7:0]. Variables must be replaced with the correct values when configuring or programming registers or identifying signals.

**Register Names**

Numbers Hexadecimal numbers are represented by a string of hexadecimal

digits followed by the character H. Decimal and binary numbers are represented by their customary notations. (That is, 255 is a decimal number and 1111 1111 is a binary number. In some cases, the letter B

is appended to binary numbers for clarity.)

**Register Bits** Bit locations are indexed by 7:0 (or 15:0), where bit 0 is the least-

significant bit and bit 7 (or 15) is the most-significant bit. An individual bit is represented by the register name, followed by a period and the bit number. For example, WSR.7 is bit 7 of the

window selection register. In some discussions, bit names are used.

Register mnemonics are shown in upper case. For example, TIMER2 is the timer 2 register; timer 2 is the timer. A register name containing a lowercase italic character represents more than one register. For example, the x in Px\_REG indicates that the register name refers to

any of the port data registers.

**Reserved Bits** Certain bits are described as *reserved* bits. In illustrations, reserved

bits are indicated with a dash (—). These bits are not used in this device, but they may be used in future implementations. To help ensure that a current software design is compatible with future implementations, reserved bits should be cleared (given a value of "0") or

left in their default states, unless otherwise noted.

**Signal Names** Signal names are shown in upper case. When several signals share a

common name, an individual signal is represented by the signal name followed by a number. For example, the EPA signals are named EPA0, EPA1, EPA2, etc. Port pins are represented by the port abbreviation, a period, and the pin number (e.g., P1.0, P1.1). A pound

symbol (#) appended to a signal name identifies an active-low signal.

#### Units of Measure

The following abbreviations are used to represent units of measure:

A amps, amperes DCV direct current volts

Kbytes kilobytes KΩ kilo-ohms

mA milliamps, milliamperes

Mbytes megabytes

MHz megahertz

ms milliseconds

mW milliwatts

ns nanoseconds

pF picofarads

W watts

V volts

μA microamps, microamperes

$\begin{array}{ll} \mu F & \text{microfarads} \\ \mu s & \text{microseconds} \\ \mu W & \text{microwatts} \end{array}$

X

Uppercase X (no italics) represents an unknown value or an immaterial ("don't care") state or condition. The value may be either binary or hexadecimal, depending on the context. For example, 2XAFH (hex) indicates that bits 11:8 are unknown; 10XX in binary context indicates that the two LSBs are unknown.

### 1.3 RELATED DOCUMENTS

The tables in this section list additional documents that you may find useful in designing systems incorporating MCS 96 microcontrollers. These are not comprehensive lists, but are a representative sample of relevant documents. For a complete list of available printed documents, please order the literature catalog (order number 210621). To order documents, please call the Intel literature center for your area (telephone numbers are listed on page 1-11).

Intel's *ApBUILDER* software, hypertext manuals and datasheets, and electronic versions of application notes and code examples are also available from the BBS (see "Bulletin Board System (BBS)" on page 1-9). New information is available first from FaxBack and the BBS. Refer to "Electronic Support Systems" on page 1-8 for details.

Table 1-1. Handbooks and Product Information

| Title and Description                                                                                                                                                                                                                                                                                                                                          | Order Number |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Intel Embedded Quick Reference Guide                                                                                                                                                                                                                                                                                                                           | 272439       |

| Solutions for Embedded Applications Guide                                                                                                                                                                                                                                                                                                                      | 240691       |

| Data on Demand fact sheet                                                                                                                                                                                                                                                                                                                                      | 240952       |

| Data on Demand annual subscription (6 issues; Windows* version) Complete set of Intel handbooks on CD-ROM.                                                                                                                                                                                                                                                     | 240897       |

| Handbook Set — handbooks and product overview  Complete set of Intel's product line handbooks. Contains datasheets, application notes, article reprints and other design information on microprocessors, peripherals, embedded controllers, memory components, single-board computers, microcommunications, software development tools, and operating systems. | 231003       |

| Automotive Products † Application notes and article reprints on topics including the MCS 51 and MCS 96 microcontrollers. Documents in this handbook discuss hardware and software implementations and present helpful design techniques.                                                                                                                       | 231792       |

| Embedded Applications handbook (2 volume set) † Data sheets, architecture descriptions, and application ntoes on topics including flash memory devices, networking chips, and MCS 51 and MCS 96 microcontrollers. Documents in this handbook discuss hardware and software implementations and present helpful design techniques.                              | 270648       |

| Embedded Microcontrollers †  Data sheets and architecture descriptions for Intel's three industry-standard microcontrollers, the MCS <sup>®</sup> 48, MCS 51, and MCS 96 microcontrollers.                                                                                                                                                                     | 270646       |

| Peripheral Components † Comprehensive information on Intel's peripheral components, including datasheets, application notes, and technical briefs.                                                                                                                                                                                                             | 296467       |

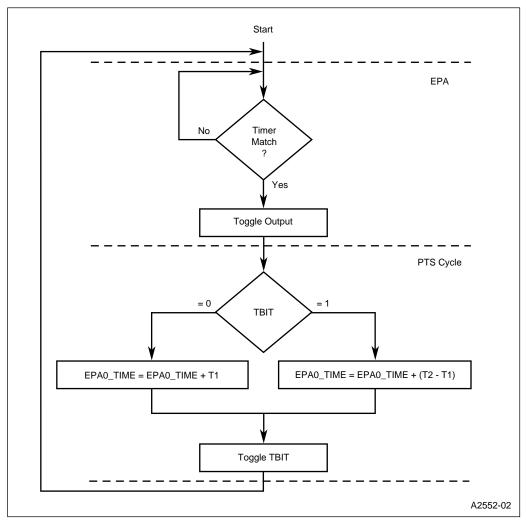

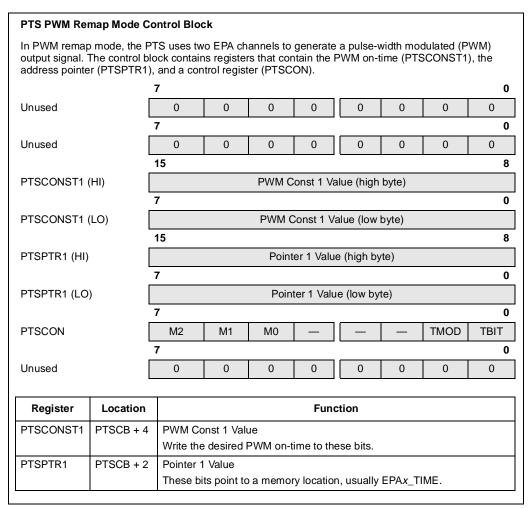

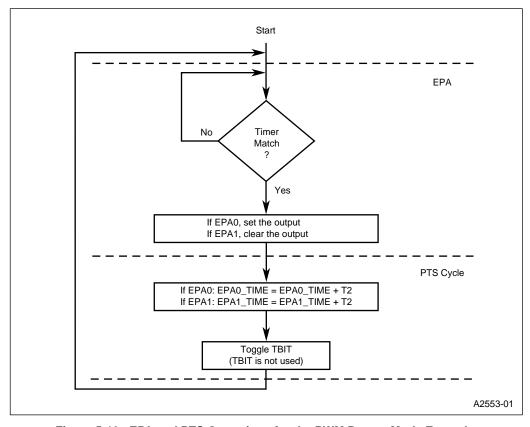

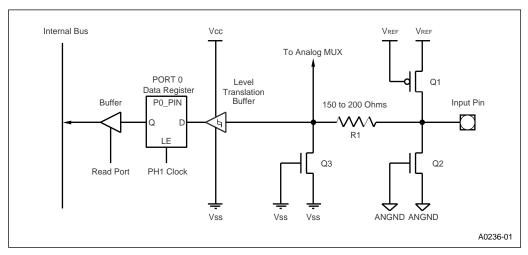

| Flash Memory (2 volume set) †  A collection of data sheets and application notes devoted to techniques and information to help design semiconductor memory into an application or system.                                                                                                                                                                      | 210830       |