**Flash Memory Products**

1990 Data Book/Handbook

Advanced Micro Devices

# Advanced Micro Devices Flash Memory Products

1990 Data Book/Handbook

© 1990 Advanced Micro Devices, Inc.

Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics.

| This publication neither states nor implies any warranty of any kind, including but not limited to implied warrants of merchantability or fitness for a particular application. AMD assumes no responsibility for the use of any circuitry other than the circuitry in an AMD product.                                                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The information in this publication is believed to be accurate in all respects at the time of publication, but is subject to change without notice. AMD assumes no responsibility for any errors or omissions, and disclaims responsibility for any consequences resulting from the use of the information included herein. Additionally, AMD assumes no responsibility for the functioning of undescribed features or parameters. |

|                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Trademarks                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Flasherase <sup>TM</sup> and Flashrite <sup>TM</sup> are trademarks of Advanced Micro Devices, Inc.                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                    |

This is your design Handbook for AMD's family of Flash memories. Included are data sheets and application notes that provide a detailed explanation of how to design this family into your new memory systems. When you use our devices you obtain the quality and reliability that you have come to expect from our EPROM and E<sup>2</sup>PROM product lines.

AMD is the only Flash memory supplier that is also a major manufacturer of both EPROM and E²PROM technologies. This experience base is transferred directly to our Flash memory family. This synergy is important because Flash memories were actually born out of a marriage of these two technologies. AMD also offers the highest performance and density of Flash memories available in the industry. By using less silicon than our competitors we are also positioned to be the lowest cost producer in the industry.

Flash memories are not just a new approach to non-volatile storage media. They actually offer you a more competitive way to do business. Flash memories increase your ability to bring products to market sooner. Also, you can cost effectively update systems already in the field with the latest firmware revisions that you are currently shipping. They even allow you to respond immediately to changing market demands by configuring generic hardware systems just prior to shipment. In addition, Flash memories can be used as removable media for the new exploding markets of miniaturized portable equipment and computers.

We are very excited about this Flash memory family. As you read through this handbook I think you will share this feeling.

Rich Forte

Vice President

High Performance Memory Division

7.426

### **TABLE OF CONTENTS**

| Product Se | lector Guidevii                                                                  |

|------------|----------------------------------------------------------------------------------|

| Chapter 1  | An Introduction to Flash Memory 1–1                                              |

| Chapter 2  | Advantages of AMD's 12.0 V Flash Memory Family 2-1                               |

| Chapter 3  | Considerations for In-System Program 3–1                                         |

| Chapter 4  | Generation and Control of V <sub>PP</sub> Programming Voltage for Flash Memories |

| Chapter 5  | Data Sheets                                                                      |

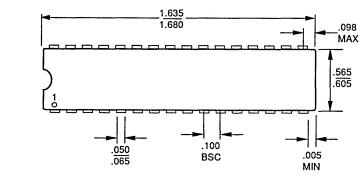

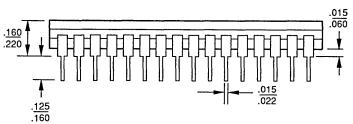

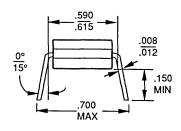

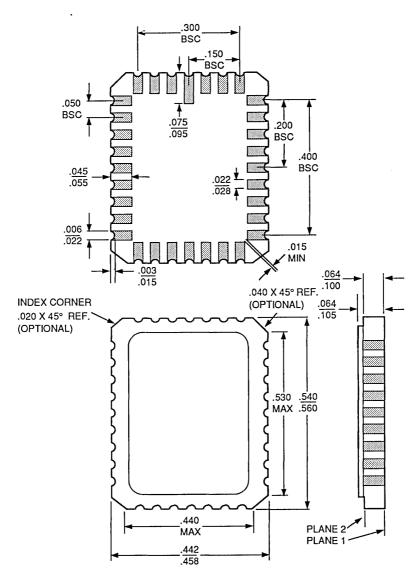

| Chapter 6  | Physical Dimensions                                                              |

### **Product Selector Guide**

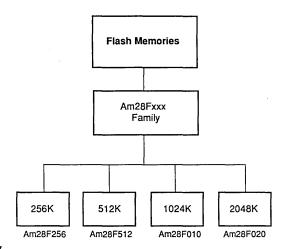

#### Am28Fxxx Family

| Part<br>Number               | Organization       | Access<br>Time (ns) | Temp<br>Range¹  | Package<br>Type <sup>2</sup> | Pin<br>Count<br>(DIP/LCC, PLCC) | Supply<br>Voltage      |

|------------------------------|--------------------|---------------------|-----------------|------------------------------|---------------------------------|------------------------|

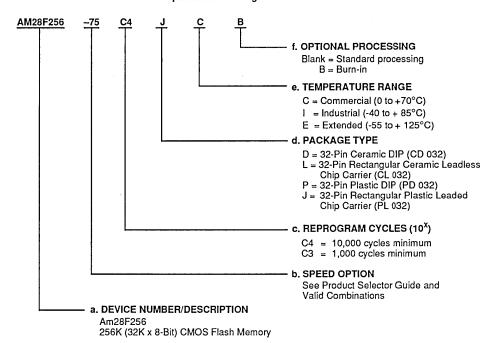

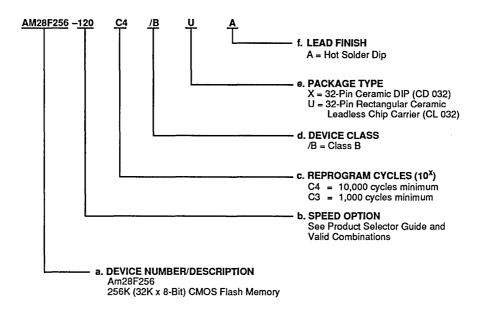

| Am28F256-75                  | 32K x 8            | 70                  | C, I            | D, L, P, J                   | 32/32                           | 5 V ± 5%               |

| Am28F256-95<br>Am28F256-90   | 32K x 8<br>32K x 8 | 90<br>90            | C, I<br>C, I, E | D, L, P, J<br>D, L, P, J     | 32/32<br>32/32                  | 5 V ± 5%<br>5 V ± 10%  |

| Am28F256-120                 | 32K x 8            | 120                 | C, I, E, M      | D, L, P, J                   | 32/32                           | 5 V ± 10%              |

| Am28F256-150                 | 32K x 8            | 150                 | C, I, E, M      | D, L, P, J                   | 32/32                           | 5 V ± 10%              |

| Am28F256-200                 | 32K x 8            | 200                 | C, I, E, M      | D, L, P, J                   | 32/32                           | 5 V ± 10%              |

| Am28F512-75                  | 64K x 8            | 70                  | C. I            | D, L, P, J                   | 32/32                           | 5 V ± 5%               |

| Am28F512-95                  | 64K x 8            | 90                  | C, I            | D, L, P, J                   | 32/32                           | 5 V ± 5%               |

| m28F512-90                   | 64K x 8            | 90                  | C, I, E         | D, L, P, J                   | 32/32                           | 5 V ± 10%              |

| Am28F512-120                 | 64K x 8            | 120                 | C, I, E, M      | D, L, P, J                   | 32/32                           | 5 V ± 10%              |

| Am28F512-150<br>Am28F512-200 | 64K x 8<br>64K x 8 | 150<br>200          | C, I, E, M      | D, L, P, J                   | 32/32<br>32/32                  | 5 V ± 10%<br>5 V ± 10% |

| Am28F512-200                 | 64K X 8            | 200                 | C, I, E, M      | D, L, P, J                   | 32/32                           | 5 V ± 10%              |

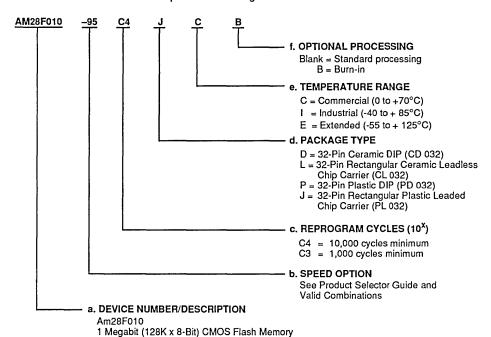

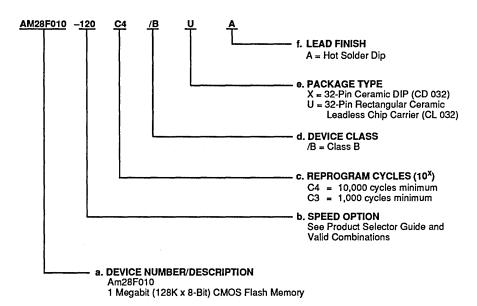

| Am28F010-95                  | 128K x 8           | 90                  | C, I _          | D, L, P, J                   | 32/32                           | 5 V ± 5%               |

| Am28F010-90                  | 128K x 8           | 90                  | C, I, E         | D, L, P, J                   | 32/32                           | 5 V ± 10%              |

| Am28F010-120                 | 128K x 8           | 120                 | C, I, E, M      | D, L, P, J                   | 32/32                           | 5 V ± 10%              |

| Am28F010-150                 | 128K x 8           | 150                 | C, I, E, M      | D, L, P, J                   | 32/32                           | 5 V ± 10%              |

| Am28F010-200                 | 128K x 8           | 200                 | C, I, E, M      | D, L, P, J                   | 32/32                           | 5 V ± 10%              |

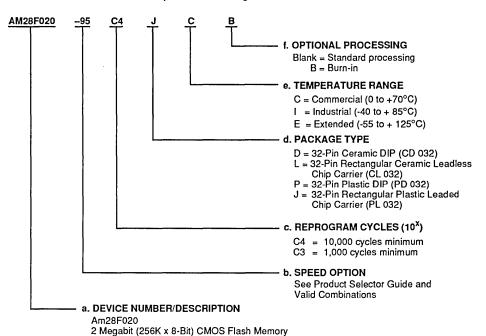

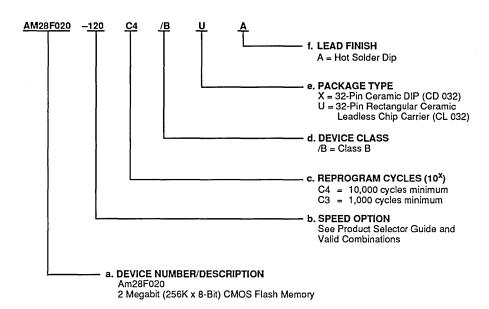

| Am28F020-95                  | 256K x 8           | 90                  | C, I            | D, L, P, J                   | 32/32                           | 5 V ± 5%               |

| Am28F020-90                  | 256K x 8           | 90                  | C, I, E         | D, L, P, J                   | 32/32                           | 5 V ± 10%              |

| Am28F020-120                 | 256K x 8           | 120                 | C, I, E, M      | D, L, P, J                   | 32/32                           | 5 V ± 10%              |

| Am28F020-150                 | 256K x 8           | 150                 | C, I, E, M      | D, L, P, J                   | 32/32                           | 5 V ± 10%              |

| Am28F020-200                 | 256K x 8           | 200                 | C, I, E, M      | D, L, P, J                   | 32/32                           | 5 V ± 10%              |

#### Notes:

- <sup>1</sup> Temp Range

- C = Commercial (0° to +70°C)

I = Industrial (-40° to +85°)

E = Extended Commercial (-55° to +125°C)

M = Military (-55° to +125°C most products available in both APL and DESC versions)

- C = Ceramic DIP

L = Rectangular Ceramic Leadless Chip Carrier

P = Plastic DIP

J = Rectangular Plastic Leaded Chip Carrier

<sup>2</sup> Package Type

# CHAPTER 1 An Introduction to Flash Memory

| What is Flash Memory 1–                                                         |

|---------------------------------------------------------------------------------|

| Where will Flash Memories be Used?                                              |

| Why is Flash Memory Cost Effective 1–                                           |

| 12.0 V Flash vs. UV EPROM 1-                                                    |

| 12.0 V Flash vs. E <sup>2</sup> PROM, 5.0 V – only Flash, and SRAM & Battery 1– |

| 12.0 V Flash vs. DRAM & Disk Drive                                              |

| How do Flash Memories Lower My Total System Cost?                               |

| In-System Updates1-                                                             |

| Manufacturing Efficiency                                                        |

| Time to Market 1–                                                               |

| Efficient Inventory Control                                                     |

| Field Service Savings1-                                                         |

### **An Introduction to Flash Memory**

#### WHAT IS FLASH MEMORY?

Flash memories are the most cost effective non-volatile alternative for high density memory applications that require in-system reprogramming.

Flash memory is born out of a marriage of EPROM and E²PROM technology. Accordingly, Flash memories incorporate the best characteristics of both devices. Flash memories are erased electrically just like E²PROMs. However, Flash memories erase the entire chip at once. This is similar to UV EPROM. Unlike E²PROM, Flash memories do not allow data to be changed on a byte by byte basis. In addition, the Am28Fxxx family of Flash memories uses a separate 12.0 V  $\pm 5\%$  programming power supply for both program and erase operations. Absolute write protection is provided when the 12.0 V supply is disabled.

The Am28F010 one Megabit Flash memory can be completely reprogrammed in less than five seconds. Reprogramming includes both the erase and programming operations. This is even faster than a standard E²PROM. In addition, Flash devices eliminate the need for expensive windowed packages, unplugging devices from sockets during code changes, and the 15–20 minutes required for EPROM erasure using ultraviolet light. Since Flash memories are available in plastic packages they are ideal for todays automatic manufacturing lines.

Table One compares the basic features of U.V. EPROM, Flash memories, and E<sup>2</sup>PROMs.

| Parameter                         | UV EPROM               | Flash                 | E <sup>2</sup> PROM  |

|-----------------------------------|------------------------|-----------------------|----------------------|

| Erase                             | UV Chip Erase          | Electrical Chip Erase | Electricl Byte Erase |

| Program                           | Per Byte               | Per Byte              | Per Byte             |

| Program<br>Voltage                | 12.5 V                 | 12.0 V                | 5.0 V                |

| Programming<br>Method             | External<br>Programmer | In-system             | In-system            |

| Reprogramming<br>Time (1 Megabit) | 15 – 20<br>Minutes     | 5 Seconds             | 10 Seconds           |

Table 1

#### WHERE WILL FLASH MEMORIES BE USED?

Flash memories can be used in a wide variety of applications that today are implemented with EPROM, E<sup>2</sup>PROM, SRAM & Battery, or DRAM & Disk memory systems.

#### WHY IS FLASH MEMORY COST EFFECTIVE?

In order to answer this question, the total cost of reprogramming a non-volatile memory system must be considered. There are two components of the cost structure associated with in-system reprogramming. They are the device cost and the cost of updating memory contents in-system.

The following sections illustrate the advantage of AMD's Flash memory family versus today's alternative non-volatile memories.

#### 12.0 V Flash vs. UV EPROM

Although the current device cost of Flash memories is greater than UV EPROM, soon they will be priced at only a multiple of 1.2 times UV EPROM. The cost savings of performing in-system reprogramming with Flash memories greatly outweighs any device level cost advantage of UV EPROM. The cost savings of a Flash memory system is greatly magnified if in-system updates are repeatedly performed. The key difference as shown in table 2 is in the cost of updating memory contents.

When the code of a UV EPROM is updated the device must be removed from a socket and either erased for 15–20 minutes, reprogrammed, and then replaced, or just replaced with an entirely new device containing the updated code. This method of updating memory contents is extremely labor intensive wherever it is performed, at the prototype stage, on the manufacturing line, or especially if it is required when a system is in the field. The reoccuring cost of a service call today exceeds \$150. Logistics of implementing manual code changes are complicated if they are to be transparent to the system user. The down time associated with replacing EPROMs is reflected in the end user's loss of productivity.

In addition, when system disassembly occurs in the field to replace EPROM based code storage it impacts the overall system in two ways. First, system design may compromise the most efficient use of board layout space. The placement of the EPROM device and its socket is dictated by ease of access and replacement when the system is disassembled. Second, whenever systems are disassembled the integrity of its reliability as shipped from the factory may be jeopardized. Frequently, system disassembly causes damage to boards and components. In addition, system recalibration may be required after reassembly.

Flash memories offer a superior solution. Reprogramming memory contents can be conveniently accomplished electrically in the resident system. Typically it takes only one second to erase an entire Flash memory device and only seconds to program the entire array. Memory contents may be updated in a number of ways. Reprogramming can be accomplished remotely via the communication abilities of the target system such as modem, Integrated Services Digital Networks (ISDN), or if it is part of a networked system. Updates may also be performed using existing disk drive capability. The updated code may also be distributed via floppy disks and downloaded with just a few simple strokes on the keypad.

### 12.0 V Flash vs. E<sup>2</sup>PROM, 5.0 V – only Flash, and SRAM & Battery

The cost of updating memory contents for each of these alternatives is essentially equivalent. Again, existing communication links can be used. A nominal cost is assigned for this procedure as listed in table 2. In this comparison the primary advantage of AMD's Flash solution is in the device cost. AMD's Flash memories will continue to parallel the density of UV EPROMs while costing only slightly more than them. This is due to the use of our EPROM-like single transistor memory cell. Because these other devices use multiple transistor memory cells, they will be hard pressed to match the future increases in device density and the inherent cost-per-bit advantage of 12.0 V Flash memories.

Since at least 60% of a memory chip is comprised of the actual memory array, any alternative to the single transistor memory cell will suffer from limits of increasing chip density, incur a 2-4x increase in silicon real estate, and have a higher manufacturing cost structure. Today's 5.0 V-only Flash memories are really only watered down versions of standard E<sup>2</sup>PROMs. They use complex, multiple transistor memory cells similar to E<sup>2</sup>PROMs. This approach to Flash memories still uses charge pumps to raise internal voltages up to 18 volts and greater. This severely stresses the memory's tunnel oxide. In part, this explains the lower endurance capability of these types of devices. 5.0 V only Flash devices have at least an order of magnitude lower cycling endurance than 12.0 V Flash memory.

In addition, non-volatile 12.0 V Flash memories are not burdened by the reliability concern of battery backed SRAMs. Why try and predict battery failure? Flash memories exhibit the time tested data retention characteristics of EPROM memory devices. There is no need for battery holders or system design compromises that permit access to the battery for replacement. Batteries are also susceptible to environmental effects of temperature and mechanical shock and vibration.

#### 12.0 V Flash vs. DRAM & Disk Drive

The new explosive growth markets of miniature portable equipment and computers along with the associated need for transportable non-volatile memory will be another driving factor for Flash memories. This will establish Flash memories as the new memory of choice. Flash offers immediate access (instant-on) to application programs without the download time associated with transfering application code from hard disk to system memory; code is executable directly from the memory. Data files may be written and altered using the Flash memory as a rewritable storage medium. A much smaller form fit and weight factor is achieved with solid state memory versus a mechanical disk drive. Power consumption is substantially reduced and reliability increased due to the greater lifetime achieved in environmentally extreme conditions.

Table Two summarizes these issues.

Table 2

| Device                               | Device Cost<br>(256 K Density) | Update Cost | Total Cost      |

|--------------------------------------|--------------------------------|-------------|-----------------|

| EPROM                                | \$2.00                         | \$150.00    | \$152.00        |

| E <sup>2</sup> PROM                  | \$20.00                        | \$8.00      | \$28.00         |

| SRAM &<br>Battery                    | \$18.00                        | \$8.00      | \$26.00         |

| 5.0 V Flash                          | \$10.00 - 20.00                | \$8.00      | \$18.00 – 28.00 |

| Flash &<br>V <sub>PP</sub> Circuitry | \$5.00<br>\$3.00               | \$8.00      | \$16.00         |

### HOW DO FLASH MEMORIES LOWER MY TOTAL SYSTEM COST?

#### **In-System Updates**

Flash memories provide immediate dividends as soon as they are reprogrammed. Code prototype time is significantly reduced because Flash memories can be updated with new code in a manner of seconds. Updates can occur on the prototype board without any disassembly. This eliminates the time required to unplug, UV erase, reprogram, and replace EPROMs.

#### **Manufacturing Efficiency**

Manufacturing processes are simplified by using Flash memories. Board level diagnostics, final system test, and customer specific configuration code can all be downloaded into the Flash memory electrically on the assembly line. Devices may be soldered directly to the system board. This eliminates the need to disassemble the system and replace socketed devices.

#### **Time To Market**

Today being first to market often separates the winners from the also rans. Since Flash memories are reprogrammable in-system, final system code is not absolutely a necessary requirement prior to shipment. As refinements and updates are made, each previously

shipped system can be updated conveniently and cost effectively. Thus your entire product line can always be as up-to-date as your newest systems rolling out the factory door.

#### **Efficient Inventory Control**

Accurate product mix forecasting is an elusive capability. Changing market conditions that deviate from even the best forecasts have real world impact on a business unit's ability to be responsive to customer demands and meet quarterly goals. Flash memories offer an innovative solution to this issue. Generic hardware systems can be planned and built without exact knowledge of final product mix. Various models of one hardware platform may be configured with customer specific code prior to shipment.

This allows you to create a more flexible and cost effective finished goods inventory. You can now respond immediately to changing market demand as soon as marketing information is available.

#### Field Service Savings

The prohibitive costs associated with a field service call are now a thing of the past. When updates to system code or system reconfiguration is necessary, these costly service calls may be replaced with remote updates or by distributing floppy disks with new data. In this way, systems can also be reprogrammed when usage is at a minimum. The procedures required to keep all systems up to date now become transparent to the actual end user. In addition, system reliability is not compromised when remote updates are performed. System disassembly is not required. This also eliminates handling, ESD, and component damage issues.

### CHAPTER 2 Advantages of AMD's 12.0 V Flash Memory Family

| AMD's Flash Memories Create a Defacto Industry Standard        | 2–2 |

|----------------------------------------------------------------|-----|

| Flash Memory Technology is Evolutionary                        | 2–2 |

| Programming Endurance                                          | 2–3 |

| Manufacturing Efficiency                                       | 2–3 |

| Zero Wait State Sytems                                         | 2-4 |

| Inadvertant Write Protection                                   | 2-4 |

| Efficient Programming Algorithms Also Guarantee Data Retention | 2–4 |

| Generating VPP Programming Voltages                            | 2-4 |

## Advantages of AMD's 12.0 V Flash Memory Family

### AMD'S FLASH MEMORIES CREATE A DEFACTO INDUSTRY STANDARD

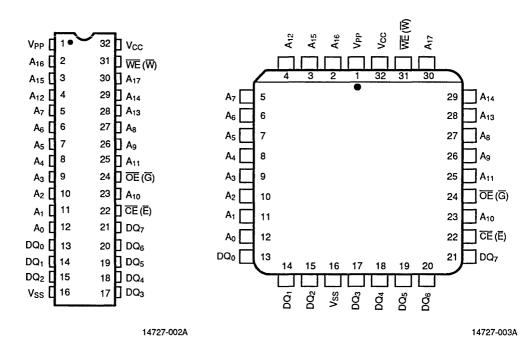

AMD is the first company to address the issue of device compatibility. In the world of Flash memories today, no two device offerings can be used as 100% compatible alternate sources of supply. While 32-pin pinouts are assigned for Flash E<sup>2</sup>PROMs, programming software standards do not exist. This is one of the major issues that must be addressed in order to fuel the widespread use of Flash memories.

AMD is leading the way to promote a defacto industry standard pinout and software for Flash memories. AMD's approach allows our device to be used as a 100% alternate source with the Intel Flash memories. Our devices are 100% compatible with the Intel type of software commands while providing us the flexibility to enhance our device features. These enhancements are a natural extension of our years of experience in the E2PROM business.

The market acceptance of Flash memories is now accelerated by the availability of 100% software and pinout compatible devices from the two largest U.S. suppliers of non-volatile memories.

#### FLASH MEMORY TECHNOLOGY IS EVOLUTIONARY

AMD is the only Flash memory supplier that is also a major manufacturer of both EPROM and E<sup>2</sup>PROM technologies. We have transferred this experience base directly to our Flash memory technology and manufacturing process. This synergy is important because Flash memories were actually born out of a marriage of these two technologies.

We build our Flash memories on our state of the art  $1.0~\mu M$  CMOS technology on the same high volume manufacturing line used for our current EPROM and E²PROM devices. This provides the basis for our steep learning curve that will bring the cost of our 12.0 V Flash memories to within just a slight premium over UV EPROM devices.

Our many years of experience in E<sup>2</sup>PROM design and our understanding of the issues relating to in-system write operations are incorporated into our Flash memory family. In addition, the many years of manufacturing experience and constant refinements to our thin film tunnel oxide provide immediate benefits to our Flash family.

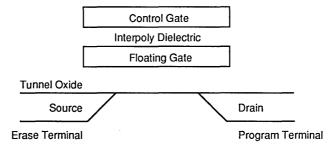

Figure 1. The AMD Flash Memory Cell

The AMD Single Transistor Memory Cell

#### AMD's Flash Memory Technology

This section illustrates the fundamentals of AMD's Flash memory technology. AMD's Flash memory technology is very similar to that of our UV EPROM. The main difference is associated with the erase mechanism of Fowler-Nordheim tuneling.

#### **Program Operations**

AMD's Flash memories transfer and store charge on a floating gate in a manner similar to EPROM. This provides data retention that is equivalent to that of EPROM devices. The device is programed by raising the control gate and drain terminal to a high voltage. The source terminal is grounded:

The voltage potential across the channel attracts channel electrons from the source area toward the drain. At the drain region, some of these channel electrons become "hot." The high voltage on the control gate attracts the "hot" electrons from drain area across the thin oxide where they are trapped on the floating gate.

#### The Programmed State

The electrons stored on the floating gate creates an electric field which turns off the memory transistor and represents a logic zero.

#### **Erase Operations**

The Flash memory cell removes charge from the floating gate like an E<sup>2</sup>PROM. The Fowler-Nordheim tuneling mechanism is used for erase operations. High voltage is applied to the source terminal while the control gate is grounded. This voltage potential causes the stored charge on the floating gate to tunnel through the thin oxide and into the source terminal. During the erase operation high voltage is applied to the source terminals of every memory cell at once. This produces the bulk erase characteristics of Flash memory.

#### The Erased State

Without the presence of electrons on the floating gate, the transistor is conductive and represents a logic one.

#### PROGRAMMING ENDURANCE

AMD's Flash memory technology incorporates the traditional EPROM programming mechanism of hot electron injection and the standard E²PROM erase mechanism of Fowler-Nordheim tunneling. AMD achieves the highest level of endurance capability by performing each of the program and erase operations on separate terminals of the memory cell. This is because programming and erase methods employ different charge transfer mechanisms. This way the memory cell can be optimized for each separate mechanism. In addition, the V<sub>PP</sub> voltage used for program and erase operations is lower than the voltages used by traditional E²PROMs. This significantly lowers the stress on the tunnel oxide during erase operations and hence extends the cycling capability of the tunnel oxide by orders of magnitude.

#### MANUFACTURING EFFICIENCY

AMD also leads the industry as the most cost efficient manufacturer of non-volatile memories. Our EPROM experience base again offers immediate benefits to our Flash family. We continue to the lead the competition with the smallest Flash memory chips. Thus, we are positioned to be the lowest cost Flash memory supplier in the industry. This not only ensures our viability as a long term supplier but also ensures you of a ready supply of product.

#### **ZERO WAIT STATE SYSTEMS**

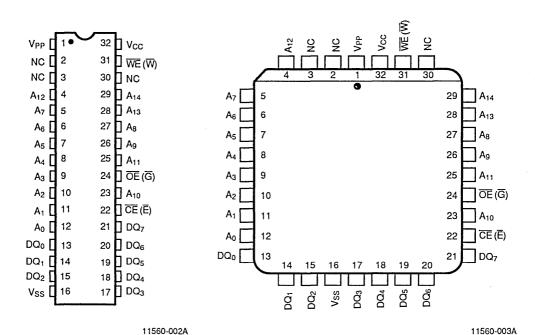

AMD's Flash memories let you take full advantage of your high performance microprocessor systems. Our devices lead the industry with the fastest access times available. AMD's Am28F256 and Am28F512 devices are available at 70ns and our Am28F010 one Megabit device is available at 90ns. These devices operate at typically twice the performance of our competitors. Again, this advantage is a direct result of AMD's high performance EPROM leadership.

#### **INADVERTANT WRITE PROTECTION**

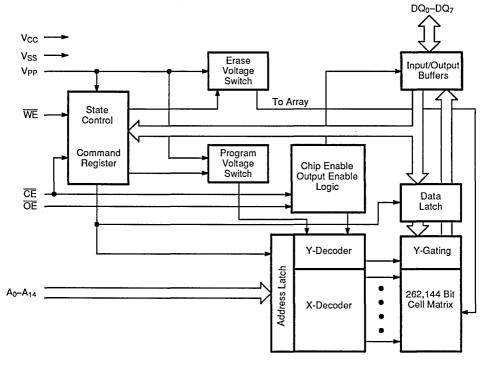

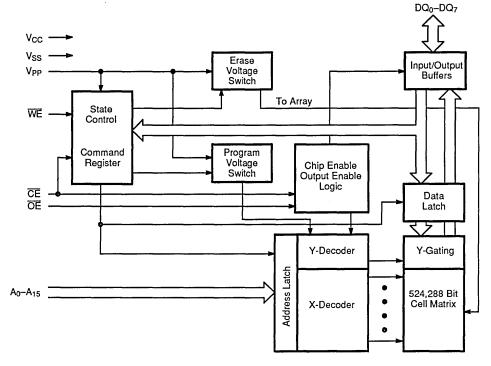

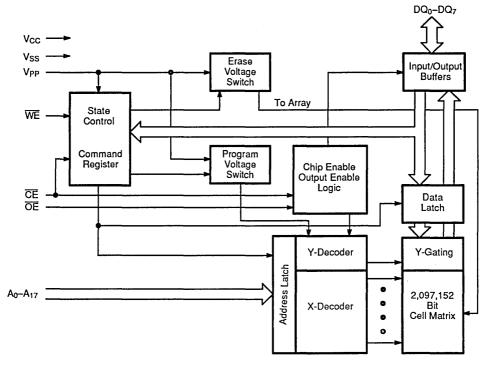

The AMD Flash memory incorporates an on-chip state machine to determine the operating mode of the device. The state machine is accessed only via the on chip command register. In turn, the command register is only enabled when the 12.0 V V<sub>PP</sub> voltage is active. Without the V<sub>PP</sub> voltage, memory contents can not be altered.

The command register is manipulated by a combination of three control pins. The only condition valid for a write operation is when  $\overline{OE}$  is high and both  $\overline{CE}$  and  $\overline{WE}$  are low. Any other state is considered a non-write state. Data can not be transferred from the command register to the state machine if a non-write state condition exists.

The state machine requires a sequence of two-cycle bus commands to change the "state" of the Flash memory device. Should an improper sequence of commands be issued to the device it will interpret these as "illegal" commands and safely reset to the read only mode and terminate any current operation. The two-cycle bus commands tend to eliminate the potential for inadvertent writes should system glitches occur. It is unlikely that the proper sequence and timing of these glitches would resemble actual valid commands. This is an advantage over other approaches to Flash memories that simply use control pins to initiate write operations.

In addition, during system power transitions the Flash memory device automatically resets to the read mode. The command register may also be effectively locked out of transfering any commands to the state machine by tying the  $\overline{\text{WE}}$  pin to the device  $V_{\text{CC}}$  pin. Thus,  $\overline{\text{WE}}$  will always be in a non-write configuration until driven low by the system write control line.

Please refer to application note AN-101 for details regarding this issue.

### EFFICIENT PROGRAMMING ALGORITHMS ALSO GUARANTEE DATA RETENTION

AMD's Flash memory programming algorithms use an interactive approach to adequately program and erase the device with a minimal number of pulses.

We guarantee data retention by using a similar margin verify concept employed by EPROM programming algorithms. During the verify mode an internally generated margin verify voltage is applied to each addressed memory location. The verify voltage is generated internally on chip from the static 12.0 V V<sub>PP</sub> supply. In this way, data retention is guaranteed to equal that of EPROM memories.

#### GENERATING Vpp PROGRAMMING VOLTAGES

In many of today's systems a regulated 12.0 V supply is available. If this is not the case, there are many alternatives for generating this voltage. They vary from DC/DC or analog convertors that can pump up 5.0 V from the system  $V_{\rm CC}$  to the regulated 12.0 V  $V_{\rm PP}$  supply. In addition, there are many DC/DC convertors that take higher incoming voltages and step them down to the regulated  $V_{\rm PP}$  output voltage.

The cost of implementing the voltage generation typically costs less than a fraction of the Flash memory itself and best of all it can be amortized over the entire Flash memory array. Many of these solutions offer enough programming current to program and erase four (4) devices in parallel. This would be sufficient for many of today's 32-bit word sytems.

Please refer to application note AN-102 for details regarding this issue.

# CHAPTER 3 AN-101 Considerations for In-System Program

| Basic Principles                                      |

|-------------------------------------------------------|

| Read Only Memory                                      |

| Command Register 3-2                                  |

| Overview of Erase/Program Operations                  |

| Considerations for In-System Programming Applications |

| V <sub>PP</sub> Generation and Control                |

| V <sub>PP</sub> Layout and Circuitry 3–4              |

| Device Decoupling 3–5                                 |

| System Initialization                                 |

| Data Protection                                       |

| Auto Select Command                                   |

| Programming In-System 3–6                             |

| Data Change Sequence                                  |

| Multiple Memory Arrays 3–6                            |

| Parallel Device Erasure                               |

| for Two Devices                                       |

### **Considerations for In-System Programming**

AN-101

#### **BASIC PRINCIPLES**

AMD Flash memories use 100% TTL-level control inputs to manage the command register. Erase and reprogramming operations use a fixed 12.0 V  $\pm$ 0.6 V power supply.

#### **Read Only Memory**

Without high V<sub>PP</sub> voltage, the Flash memory functions as a read only memory and operates like a standard EPROM. The control inputs still manage traditional read, standby, output disable, and Auto select modes.

#### **Command Register**

The command register is enabled only when high voltage is applied to the  $V_{pp}$  pin. The erase and reprogramming operations are only accessed via the register. Two-cycle commands are required for erase and reprogramming operations. In addition, the traditional read, standby, output disable, and Auto select modes are available via the register.

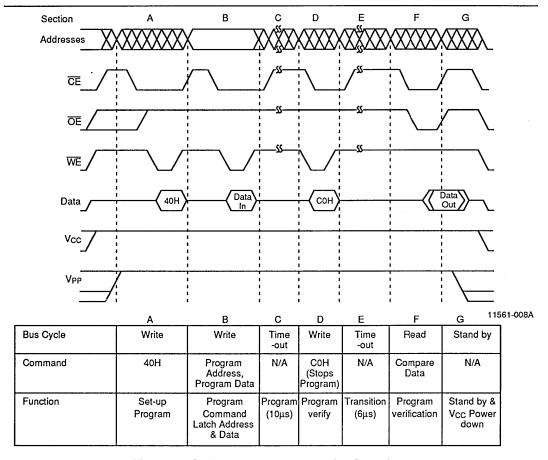

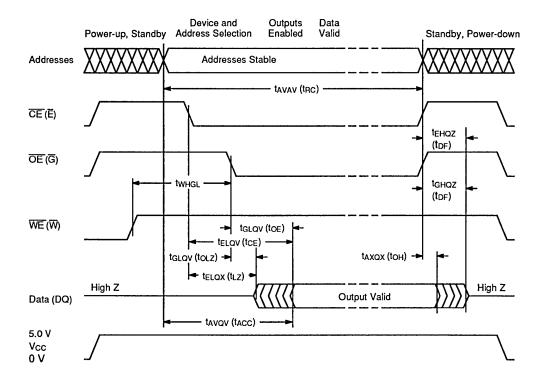

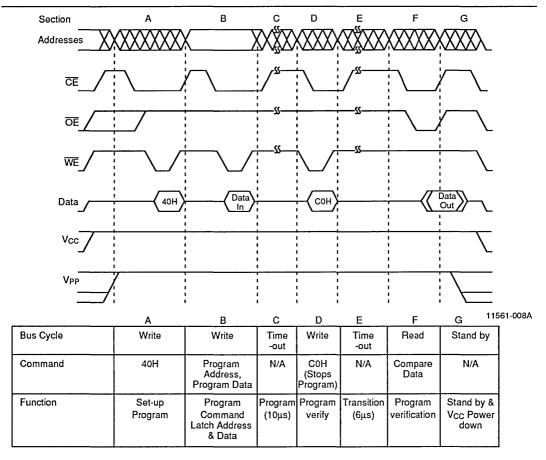

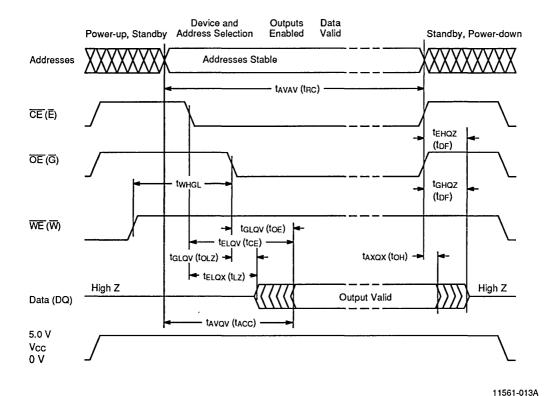

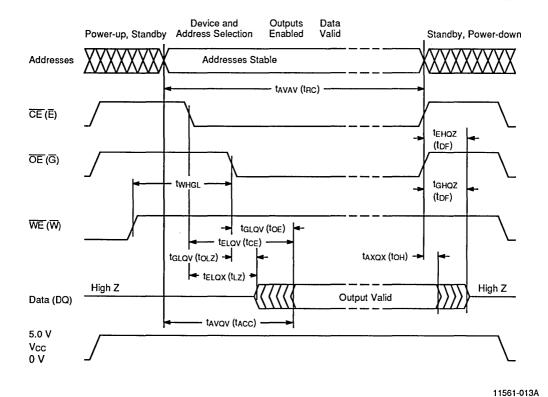

The AMD Flash memory command register is written using standard microprocessor write timings. The register controls an internal state machine that manages all device operations.

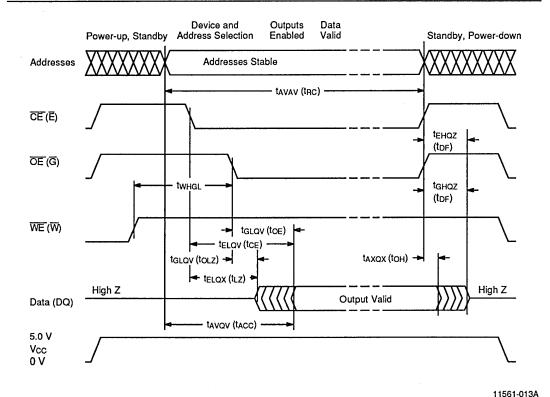

For system design simplification, the AMD's Flash memory is designed to support either WE or CE controlled writes. During a system write cycle, addresses are latched on the falling edge of WE or CE, whichever occurs last. Data is latched on the rising edge of WE or CE, whichever occurs first. All setup and hold times are with respect to the WE signal. To simplify the following discussion, the WE pin is used as the write cycle control pin throughout the rest of this text.

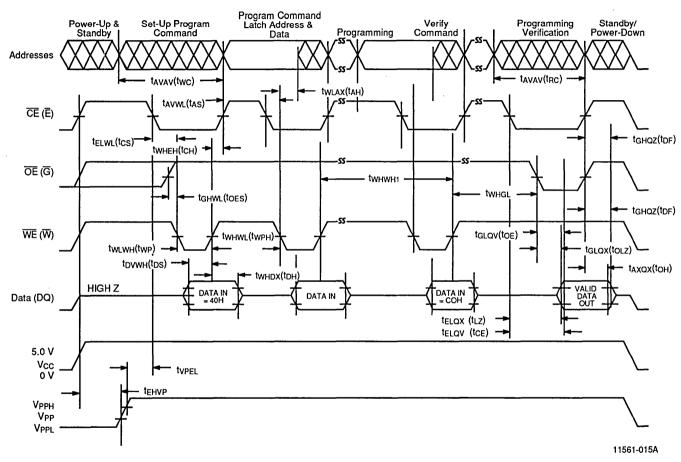

#### Overview of Erase/Program Operations

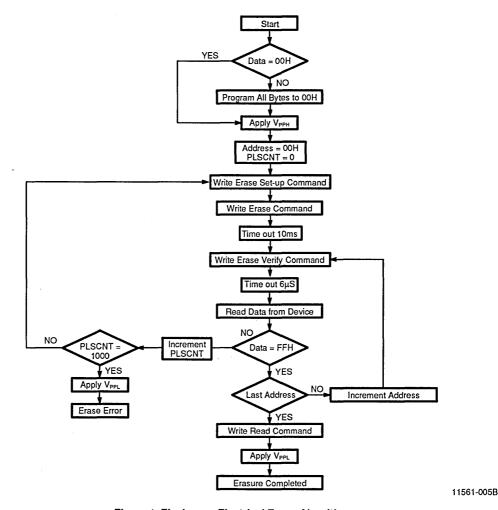

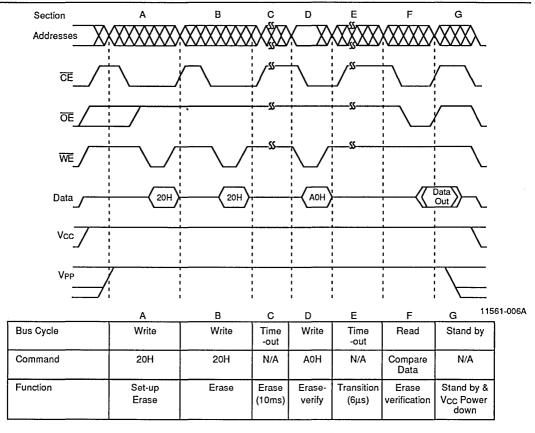

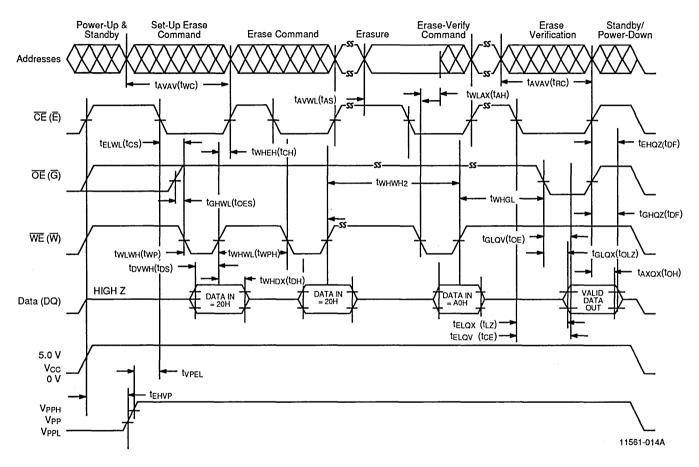

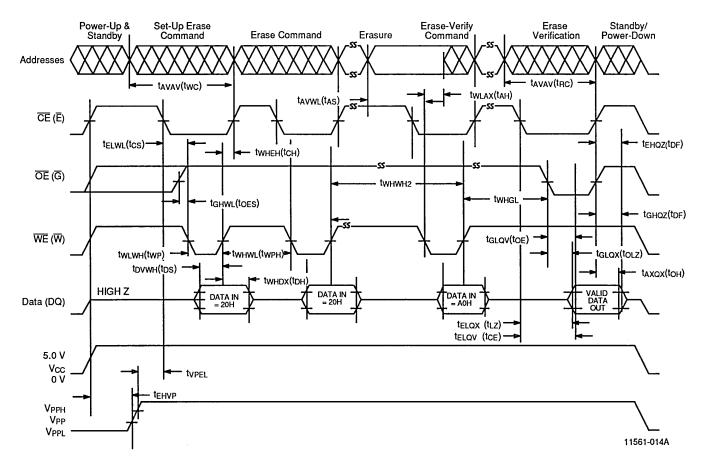

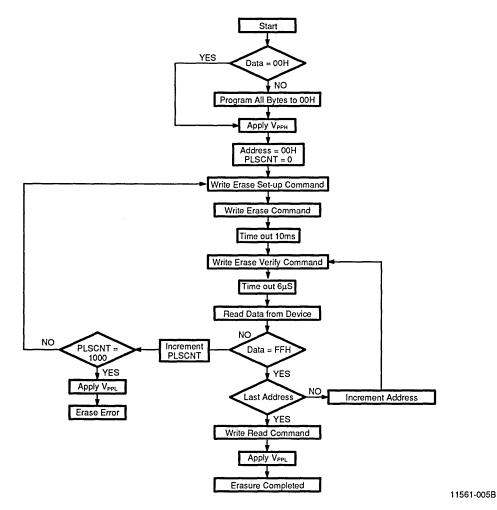

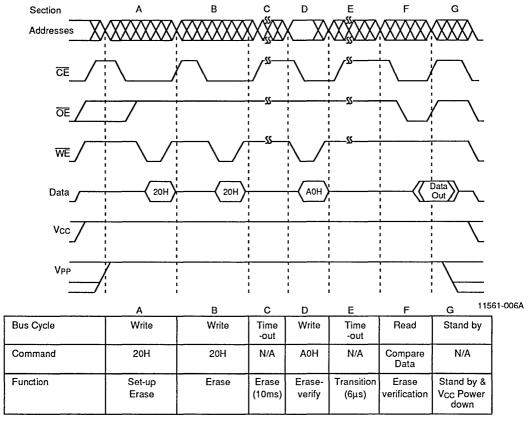

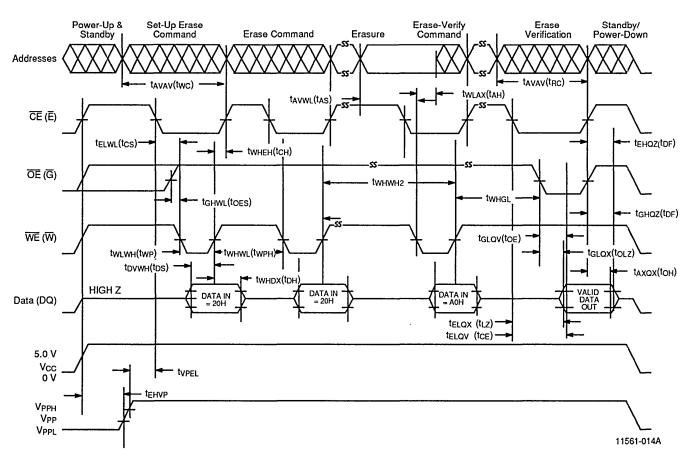

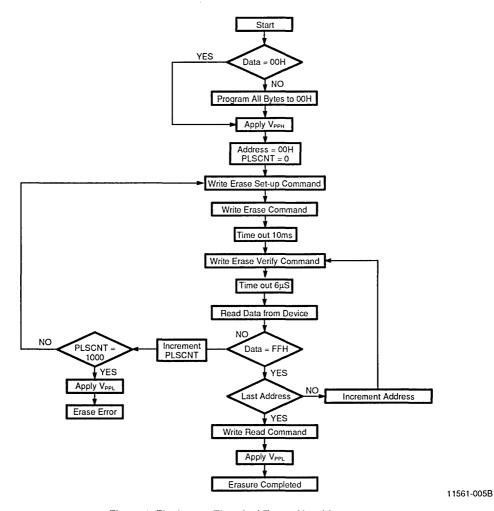

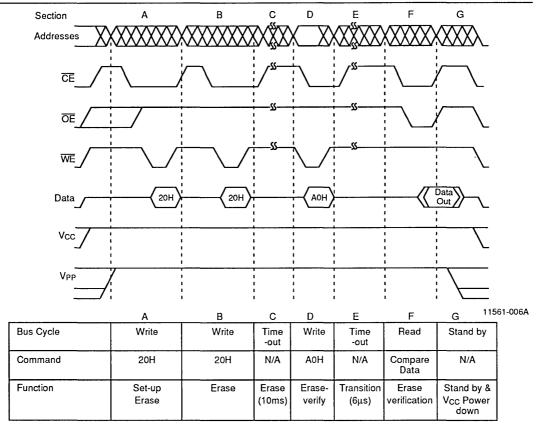

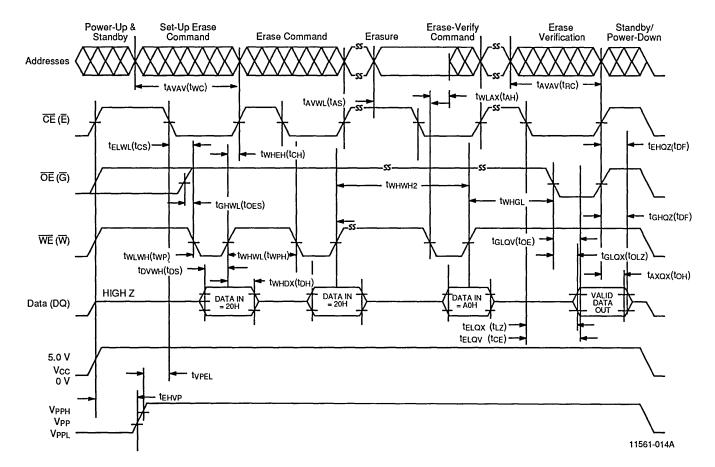

#### Erase Sequence

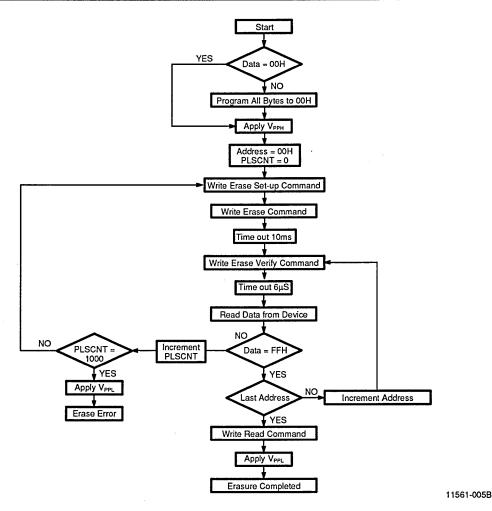

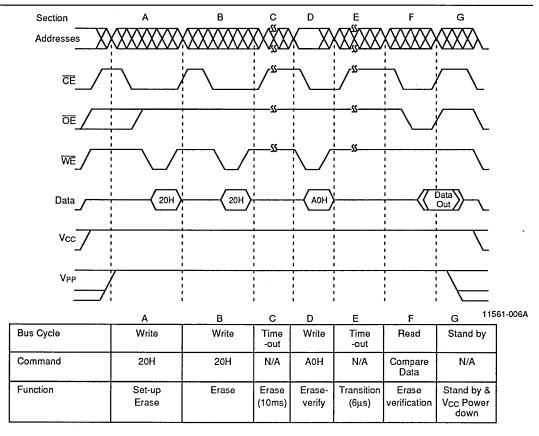

A multiple step command sequence is required to erase the Flash device (a two-cycle Erase command and repeated one cycle verify commands).

#### Note:

The Flash memory array must be completely programmed prior to erasure. Refer to the Flasherase $^{\rm TM}$  Algorithm.

Erase Set-up: Write the Erase/Erase Set-up command to the command register.

- Erase: Write the Erase/Erase Set-up command to the command register again. The second command initiates the erase operation. Time-out the erase pulse width.

- 3. Erase-verify: Write the Erase-verify command to the command register. This command terminates the erase operation. After the erase operation, each byte of the array must be verified. Address information must be supplied with the Erase-verify command. This command verifies the margin and outputs the addressed byte in order to compare the array data with FFH data (Byte erased). After successful data verification the Erase-verify command is written again with new address information. Each byte of the array is sequentially verified in this manner.

If data of the addressed location is not verified, the Erase sequence is repeated until the entire array is successfully verified or the sequence is repeated 1000 times.

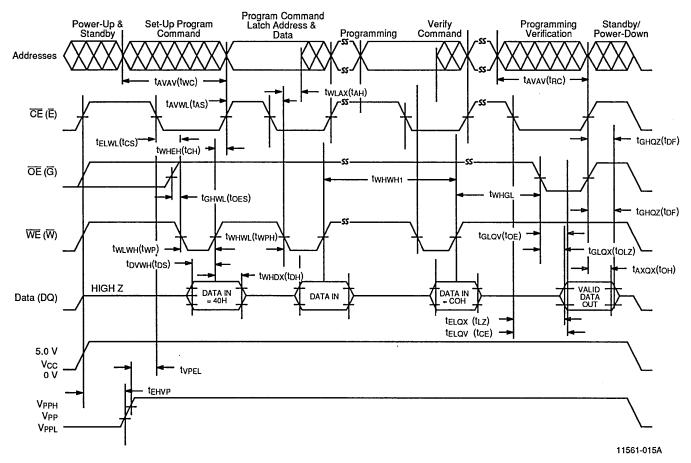

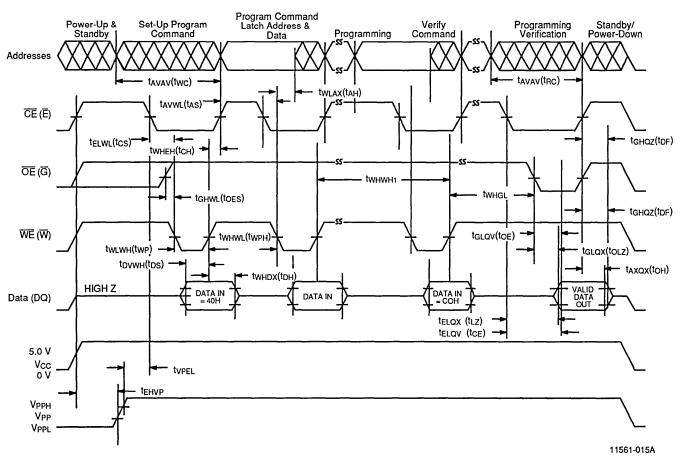

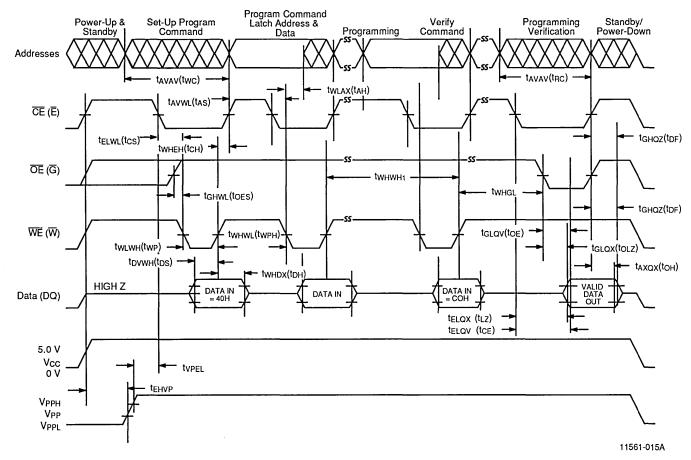

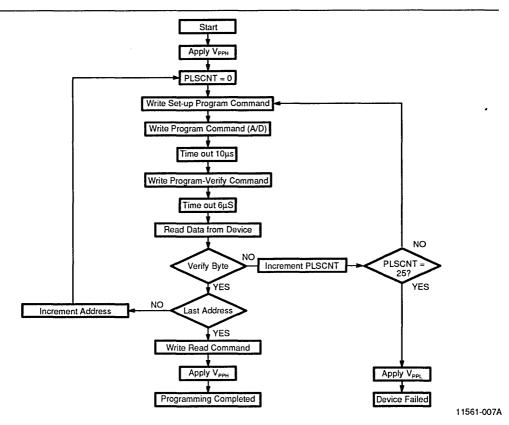

#### Programming Sequence

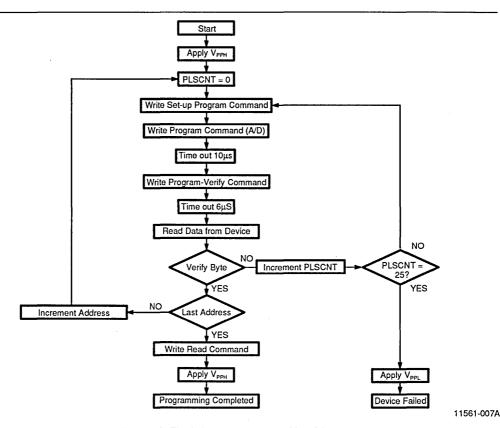

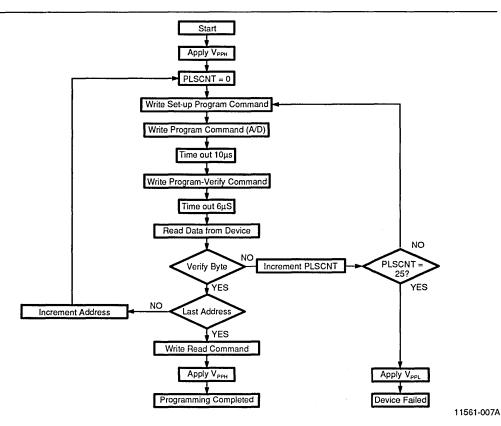

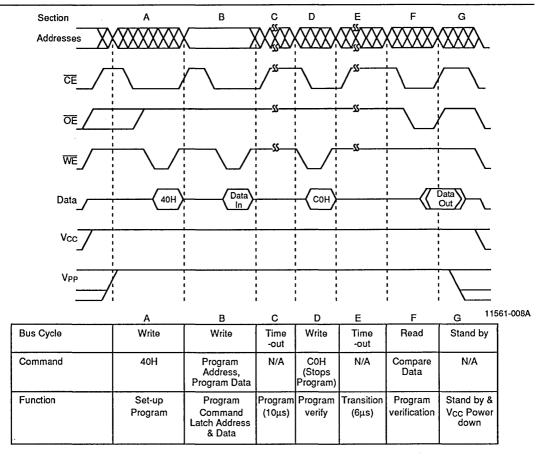

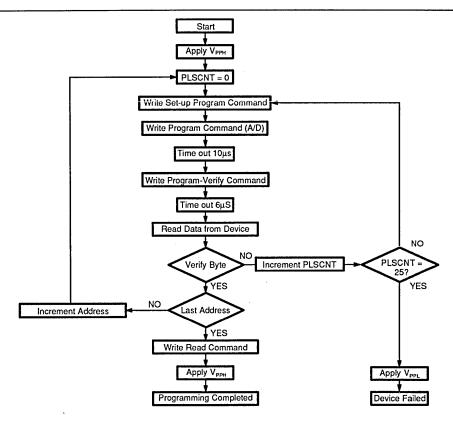

A three-step command sequence (a two-cycle Program command and one-cycle verify command) is required to program a byte of the Flash array. Refer to the Flashrite<sup>™</sup> Algorithm.

- Program Set-up: Write the Program/Program Setup command to the command register.

- Program: Write the Program/Program Set-up command to the command register with the appropriate Address and Data. Time-out the program pulse width.

- 3. Program-verify: Write the Program-verify command to the command register. This command terminates the programming operation. In addition, this command verifies the margin and outputs the byte just programmed in order to compare the array data with the original data programmed. After successful data verification, the programming sequence is initiated again for the next byte address to be programmed.

If data is not verified, the Program sequence is repeated until a successful comparison is verified or the sequence is repeated 25 times per byte.

### CONSIDERATIONS FOR IN-SYSTEM PROGRAMMING APPLICATIONS

#### V<sub>pp</sub> Generation and Control

Constant  $V_{pp}$  voltage of 12.0 V  $\pm 0.6$  V is required for erase and programming operations. Parallel device reprogramming (either 16-bit or 32-bit data words) requires 30 mA of current for each device in the Flash memory array.

V<sub>PP</sub> voltage can be generated in a number of ways:

- 1. Use analog circuitry to pump 5 V to V<sub>PP</sub> Voltage

- Use DC/DC, monolithic convertor to pump 5 V to V<sub>PP</sub> Voltage.

- Hardwire V<sub>PP</sub> Voltage to the Flash Device

- 4. Umbilical Cord Programming

It is important to maintain the specified  $V_{pp}$  voltages when reprogramming the Flash memory device. All internal device voltages are generated from the  $V_{pp}$  reference. Inappropriate  $V_{pp}$  voltage may impair device performance. Internal voltages do not exceed that of external  $V_{pp}$ .

Unlike other approaches to Flash memories, AMD's devices actually verify margin for each byte during erase and programming operations. This is accomplished during the Erase-verify and Program-verify operations respectively. During these operations, the appropriate margin-verify voltages are internally tapped off of the  $V_{\rm pp}$  voltage via the command register and internal  $V_{\rm pp}$  circuitry. This allows for Erase/Erase-verify and Program/Program-verify operations to be performed with static  $V_{\rm CG}$  (5 V) and  $V_{\rm pp}$  (12 V) voltages.

#### V<sub>pp</sub> Supply

Use analog circuitry to Pump 5 V to V<sub>pp</sub> Voltage.

See Application Note AN-102 on  $V_{\rm pp}$  Generation and Control for circuit schematics and more detailed discussions.

2. Use DC/DC Monolithic Convertor to Pump 5.0 V to  $V_{\rm pp}$ .

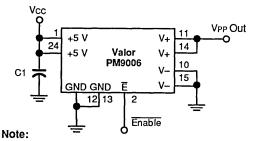

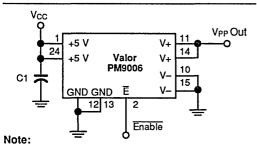

A monolithic DC/DC convertor from Valor Electronics, the PM9006, is appropriate for the digital world to supply the 12.0 V  $\pm 0.6$  V  $V_{pp}$  voltage. The  $V_{pp}$  voltage is generated on a chip using the standard system  $V_{CC}$  (5.0 V) voltage. Standard TTL commands are used to disable the 12.0 V output supply when programming or erasing operations are not intended. The enable  $(\overline{E})$  function provides absolute write protection to guarantee against inadvertent program or erasure. Flash memory

contents cannot be altered without the active 12.0 V  $\rm V_{\rm pp}$  supply. The enable pin also saves system power when the DC/DC convertor is not required. The PM9006 has a minimum efficiency of 50% at full load. The PM9006 comes in a 24-pin package.

The Valor PM9006 provides a controlled 12.0 V output that is regulated within the  $\pm 5\%$  ( $\pm 0.6$  V)  $V_{pp}$  specification. The standard system  $V_{CC}$  (5.0 V) supply is converted to the  $V_{pp}$  (12.0 V) supply by the DC/DC convertor. The voltage transitions are smooth and protect against destructive positive or negative overshoot.

The PM9006 can supply 165 mA of current at the regulated 12.0 V  $\pm 0.6$  V output. The 5.0 V  $\pm 0.5$  V DC input supply of the DC/DC convertor uses a maximum of 840 mA of input current. The Am28F010 specifies a maximum V\_{PP} current of 30 mA for either the erase or program operations. Actual current required for these operations is substantially lower than this. Given the maximum V\_{PP} current of 30 mA for each device, four (4) Am28F010 may be programmed and erased in parallel with one PM9006 device. The PM9006 V\_{PP} supply current = 165 mA - 4 x 30 mA of V\_{PP} current required for the Flash memory array = 45 mA of additional current available from the DC/DC convertor.

Parallel programming and erasure allows for the most efficient method to reprogram x16 or x32 bit data words. Refer to application note AN-101 for parallel program and erase flow charts.

#### Board Level Resets

System designs should not allow the Flash device to perform any programming or erase operations when the CPU does not have control of the Flash device. Some designs incorporate board level reset circuitry that suspends operation of the local CPU if the  $V_{\rm CC}$  level falls below a predetermined value (such as 4.6 V). If this is the case, the reset circuitry should also disable the  $V_{\rm pp}$  power supply whenever the CPU is held in reset.

If the local CPU is forced into reset mode while it is programming or erasing the Flash device, the system reset circuit should also terminate that operation. To accomplish this, the PM9006's enable pin should be driven high whenever the reset circuitry is active. Drive the chip enable pin of the PM9006 with the logical OR of the reset circuitry's output signal and the chip enable control line to the PM9006. This will disable the  $\rm V_{pp}$  supply and hence termiante any programming or erase operation. The Flash device automatically resets to the read mode when  $\rm V_{pp}$  is disabled.

Please reference the PM9006 data sheet for complete details of device operation. One method of implementing the PM9006 DC/DC convertor is illustrated on page four.

Pins 3 through 9 and 16 through 23 are not internally connected to the device and do not need to be driven.

#### Generate and Control 12.0 V

#### Hardwire V<sub>PP</sub> Voltage to the Flash Device.

Typically this approach is used in the most cost sensitive applications. Regulated 12.0 V supplies are commonly available in many systems.

When  $V_{CC} = 0$  V, the  $V_{PP}$  voltage is internally disabled from the device. Memory contents cannot be altered. The Flash device automatically resets to the read mode when  $V_{CC}$  rises above 2 V. This occurs even when  $V_{PP} = 12$  V.

Power Supply sequencing is not required.

The device will only respond to the correct sequence of commands in order to change the state of the Flash memory from Read mode to any other mode. In addition, the three control pins must be in their correct state  $(\overline{CE} = \text{Low}, \overline{OE} = \text{High}, \text{ and } \overline{WE} = \text{Low})$  in order to accept a command from the data bus.

A number of additional procedures are available to further prevent inadvertent writes should system glitches occur during system/device power transitions:

- Hold any control pin (CE, OE, or WE) in a non-write condition. This disables the device from executing a write operation. Please refer to following example.

- Any "illegal" command (an illegal command is one that is not defined in the AMD Flash Memory data sheet under the section – Command Definitions) written to the Flash device will automatically terminate any operation and reset the device to the Read Mode.

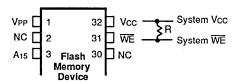

#### 4. Umbilical Cord Programming

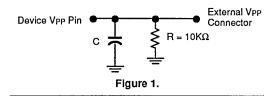

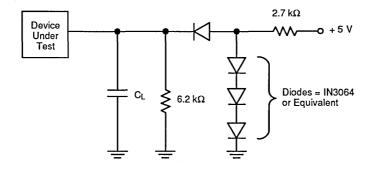

Many applications perform system updates using the umbilical cord or edge connector programming method. The external programming equipment supplies the 12.0 V  $\pm 0.6$  V  $V_{pp}$  voltage. When the umbilical cord is disconnected, be aware that electrostatic discharge may build up on the floating  $V_{pp}$  pin. To prevent this

#### Example:

Holding WE in a non-write condition during power transitions.

In systems where the  $\overline{V_{PP}}$  pin is to be connected directly to the +12 V supply,  $\overline{WE}$  should be held in a non-write state during power supply transitions. This will prevent against inadvertent write conditions. One way to achieve this is by pulling  $\overline{WE}$  up to Vcc via a 2.7 K Ohm resistor.

During power supply transitions, VPP voltage is internally disabled from the Flash device until Vcc rises above 2 V. In addition, the Flash device automatically resets to the read mode as Vcc rises above 2 V. The WE pin will be pulled up (VIH = 2 V) via the 2.7 K Ohm resistor as Vcc rises. When write enable is at VIH the command register is internally disabled from the internal state machine of the Flash device. When the command register is disabled, data commands can not be transferred to the state machine. Therefore the state of the Flash device will not be altered from the read mode. Access to the command register will be prevented until the WE line is driven to a logic level low by the system write control.

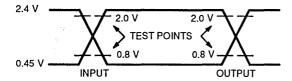

Note: VIH Min. = 2.0 V R = 2.7 K

problem, tie the  $V_{pp}$  pin to ground via a large (10K  $\Omega$ ) pull-up resistor and a capacitor.

#### **V<sub>DD</sub>** Layout and Circuitry

Be aware that AC current is a component of DC power switching characteristics. Design the printed circuit board traces handling this current to accommodate high frequency.

**Printed Circuit Board Trace Layout:** Use a single ground plane to eliminate potential loops. Keep all inductive impedances at a minimum on all high current traces.

${

m V_{pp}}$  Regulator Circuitry Layout: Locate the  ${

m V_{pp}}$  generation circuitry as close to the Flash memory array as possible. In addition, minimize lead lengths of the network. To help prevent noise from being picked up in feedback loops, locate all resistors and capacitors as close to the  ${

m V_{pp}}$  network as possible. In order to prevent input ground loops, use separate returns for input and output capacitors.

#### **Device Decoupling**

#### evice Decoupling

*i*tching  $\overline{\text{CE}}$  inputs for memory selection causes nsient current peaks at the Flash device. The Flash emory devices should be decoupled with the propriate capacitance.

Connect a 0.1  $\mu$ F ceramic capacitor between  $V_{cc}$  and  $V_{ss}$  and one between  $V_{pp}$  and  $V_{ss}$ . The capacitors should be placed as close to each device as possible.

In addition, connect a 4.7  $\mu$ F electrolytic capacitor between V<sub>cc</sub> and V<sub>ss</sub> on the memory arrays' power supply. Do this for each set of eight memory devices. This bulk capacitor will maintain even voltage to the memory array.

#### ystem Initialization

uring remote code updates the possibility that the immunication link could be disrupted during a reproamming sequence exists. Should this occur, the state the Flash device (Erased, Partially Programmed, c.) may not be known. Bootcode should always reset e Flash memory as part of the initialization sequence. Iso, status flags should be read to determine the state the Flash device upon reset.

ystems that are designed for remote updates should ontain the following as at least a subset of the ootcode program:

In-system reprogramming routines for Flash,

Standard initialization and diagnostic routines,

A set of communication routines,

s part of the boot code. The boot code can be cost ffectively stored in an AMD ExpressROM™ as a eparate memory device.

is with any logic device, the Reset command initializes ne Flash memory to a known state: the Read mode. his is accomplished by writing the Reset command wice in succession to the Flash device. This should ccur in the first part of the system initialization routine.

irst we will discuss resetting the Flash device as part of he initialization sequence. Then we will discuss the use of reprogramming flags to keep track of the state of the flash device after remote updates (i.e., does the nemory content contain valid data).

#### nterrupt Sequences

nterrupt sequences should always reset the Flash levice as the first part of any routine. In addition, it is advisable to disable the  $V_{\rm pp}$  voltage during interrupts. The Reset command should be written twice in a row to

all Flash devices as part of the interrupt sequence. This resets the Flash device to the Read mode. Reset the Flash device as the initial commands of any routine. This procedure is also relevant should a software or hardware reset occur while the system is in the process of reprogramming the Flash memory. By including the consecutive reset command sequence in the bootcode the erase or program operations will be terminated when the system reboots.

Hardware resets may be implemented by connecting the reset signal directly to an interrupt controller. The software interrupt sequence to reset the Flash memory is then executed by the controller.

#### Data Transmission

In order to guarantee accurate data updates, reprogramming protocols may include echo techniques or error-free transmission algorithms.

The echo technique is a straight forward approach to verify transmission of accurate data. The remote system sends back the Flash memory instructions (i.e. Set-up Erase/Erase) to the host system. The remote system waits for a confirmation of the instruction prior to execution. Once the memory array is reprogrammed, the remote system transmits the data to the host for verification. Upon confirmation the remote system programs the Data Valid word. This concept is explained in the Data Valid section.

#### Handshaking

Communication protocols for the host system in charge of remote updates should require a status check from the target system prior to sending reprogramming commands. If the system indicates it is available, the appropriate command is issued by the host system. Should the remote system indicate it is not available the host may break the communication link and wait for a request to reconnect later. Handshaking protocols are recommended in applications where system downtime is not acceptable to accommodate reprogramming routines.

#### Data Valid Flags

Once the Flash memory and other system components have been reset the system should check for the validity of data contained in the Flash memory devices. This is an issue when the system resets or the communication link is disrupted during remote reprogramming routines.

The system should check the Flash device for valid data upon initialization.

The Data Valid flag is a data word that is the final word programmed into the Flash array. This word is pro-

ray. The Data Valid word will not be programmed if the memory array data is invalid or the communication link was disrupted during a reprogramming sequence. During system initialization the CPU will look for the Data Valid word. If it is not programmed, the system will recognize that the Flash memory is not programmed with accurate data. The Flash memory must be accurately programmed before the system initialization routine can be completed.

#### **Data Protection**

Because AMD's Flash memories are designed to be reprogrammed in-system AMD has incorporated a number of data protection methods against inadvertent erase or program.

#### Software

AMD's Flash Memories require a two-cycle Write command to initiate either the erase or program operations. Refer to the Set-up Erase/Erase or Set-up Program/ Program commands. These commands drive an internal state machine that controls the device operation. The state machine is designed to expect the first Write cycle command to be a set-up command. Set-up commands will not alter the memory data. Successful execution of the appropriate second Write cycle command will initiate the erase or program operations.

#### Control Inputs

AMD's Flash memory devices require that  $\overline{OE} = V_{IH}$  and  $\overline{CE} = \overline{WE} = V_{IL}$  in order to load the register with a command. If any pin is not in the correct state a write cycle cannot be initiated.

#### V<sub>PP</sub> Voltage

AMD's Flash device is designed to disable the command register whenever  $V_{pp}$  falls below  $V_{cc}+2\ V.$  When  $V_{cc}=0\ V$ , the command register internally disables the  $V_{pp}$  voltage from the device. When  $V_{pp}=12\ V,$  the Flash device resets to the Read mode when  $V_{cc}$  rises above 2 V. When the command register is disabled, the memory array contents cannot be altered.

Power supply sequencing is not required.

#### **AUTO SELECT COMMAND**

Flash memories can be programmed in-system or in a standard PROM programmer. The device may be soldered to the circuit board upon receipt of shipment and programmed in-system. Alternatively, the device may initially be programmed in a PROM programmer prior to soldering the device to the board.

#### **Programming In-System**

AMD's Flash memories are designed for use in applications where the local CPU alters memory contents. Accordingly, manufacturer and device codes must be accessible while the device resides in the target system. PROM programmers typically access the signature codes by raising A<sub>9</sub> to a high voltage. However, multiplexing high voltage onto the address lines is not a generally desired system design practice.

AMD's Flash memories contain an Auto select operation to supplement traditional PROM programming methodology. The operation is initiated by writing either 80H or 90H into the command register. Following this command, a Read cycle from address 0000H retrieves the manufacturer code of 01H. A Read cycle from address 0001H returns the appropriate device code. To terminate the operation, it is necessary to write another valid command into the register.

#### Data Change Sequence

Flash memories perform data change cycles differently than full-featured E<sup>2</sup>PROMs. Flash memories must always be completely programmed prior to erasure. This ensures against over-erasure, because all bytes are erased from the fully programmed state.

A data change sequence will include the following:

- Program the entire array to 00H data using the Flashrite™ Algorithm.

- Bulk-Erase the entire device using AMD's Flashrite™ Algorithm.

- Program the array with the appropriate data pattern using AMD's Flashrite<sup>™</sup> Algorithm.

As long as the user follows AMD's Flasherase™ and Flashrite™ Algorithms, the device will not over-erase.

#### **MULTIPLE MEMORY ARRAYS**

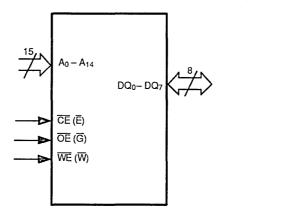

Many applications require multi-memory device arrays. AMD's Flash memories provide the standard  $\overline{OE}$  and  $\overline{CE}$  device control inputs. These two controls allow for specific selection of one memory device in an array and help prevent the potential for bus contention. Because all non-selected memories may be left in standby mode, the memory arrays' power dissipation is maintained at its lowest level.

The  $\overline{\text{CE}}$  control pins should be driven by the outputs of an address decoder. The system's memory Read and Write signal should control the  $\overline{\text{OE}}$  and  $\overline{\text{WE}}$  controls of the memory array respectively.

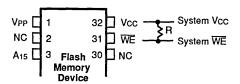

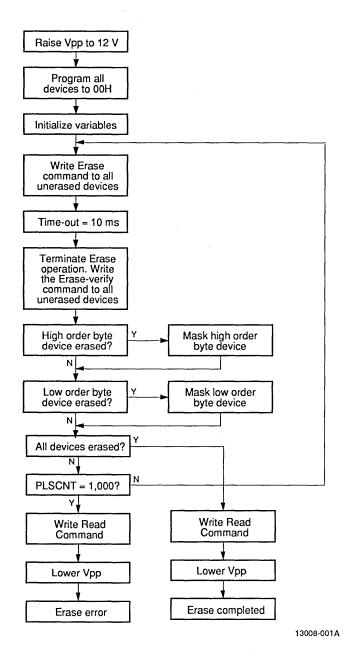

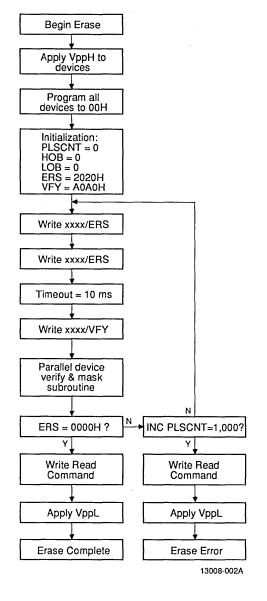

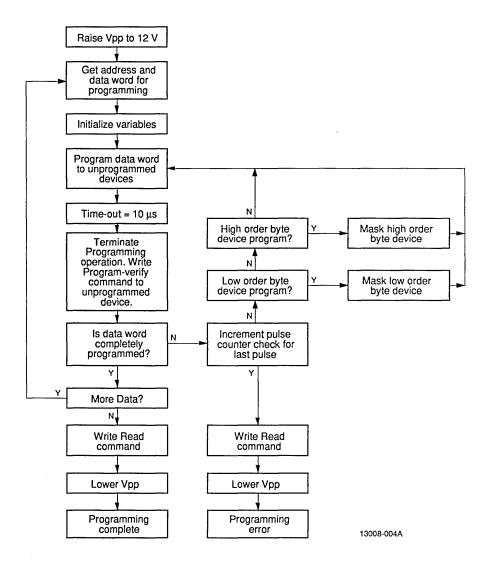

#### PARALLEL DEVICE ERASURE—OVERVIEW

#### PARALLEL DEVICE ERASURE FLOW CHART

#### Activity

Allow  $V_{PP}$  to stabilize.

Follow Flashrite programming algorithm.

Initialize Erase Variables:

PLSCNT = Pulse Counter

HOB = High Order Address Byte

LOB = Low Order Address Byte

ERS = Erase Command

VFY = Erase-verify Command

xxxx = Address do not care. Write Erase Set-up command.

Initiate erase pulse.

Duration of erase pulse.

Erase-verify command terminates the erase pulse.

See Parallel Device Erasure subroutine. Each device is independently verified. The command is masked by the Read command (00H) for all devices that are completely erased.

ERS = 0000H when all devices are erased.

Reset devices for read operation.

$V_{\rm pp} L$  deactivates the command register. Device is in the Read Only Mode.

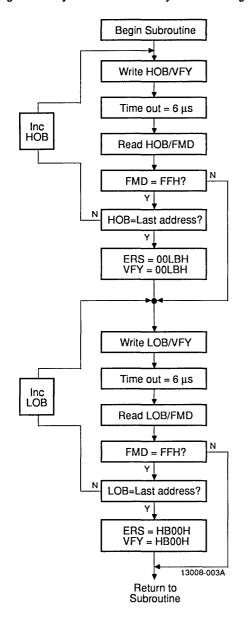

#### PARALLEL DEVICE ERASURE—SUBROUTINE

High Order Byte and Low Order Byte Device Program Verify and Mask Subroutine.

#### Activity

The Subroutine verifies each device independently and masks the completely erased device from further erasure.

#### Verify High Order Byte Device:

Addresses are latched (HOB) on Erase-verify command.

Internal margin verify voltages are tapped from external 12 V  $V_{pp}$  for proper byte verification.

Read HOB from previously latched Address. FMD = Flash Memory Data.

Compare Flash Memory Data to FFH. If verified, then compare next high order byte address. If invalid, then Jump to low order byte device.

If all addresses of the high order byte device are verified, mask the Erase and Verify commands with the Read command, (00H). Low order byte (LB) device commands are not altered.

#### Verify Low Order Byte:

Addresses are latched (LOB) on verify command.

Internal margin verify voltages are tapped from external 12 V  $V_{_{\rm PP}}$  for proper byte verification.

Read LOB from previously latched address. FMD = Flash Memory Data.

Compare Flash Memory Data to FFH. If verified, then compare next low order byte address. If invalid, return to main parallel erase flow for next erase pulse.

If all addresses of the low order byte device are verified, mask the erase and verify command with the read command (00H). High order byte (HB) device commands are not altered.

#### **Parallel Device Erasure**

A bank of Flash memories may be erased in parallel. This reduces total erase time when compared to erasing each device individually. Each Flash memory may erase at different rates. Therefore each device must be verified separately after every erase pulse. Once a device has successfully completed erasure do not issue

the erase command again to that device. Issue the Read command 00H to the erased device. The Erase command sequence may be issued to each of the remaining devices that have not erased yet. In addition to the address verify register required for each device you will need an erase complete flag for each device.

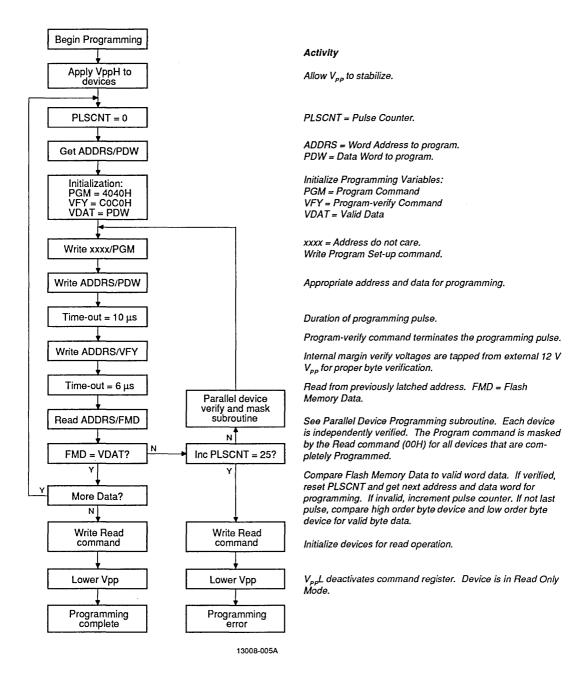

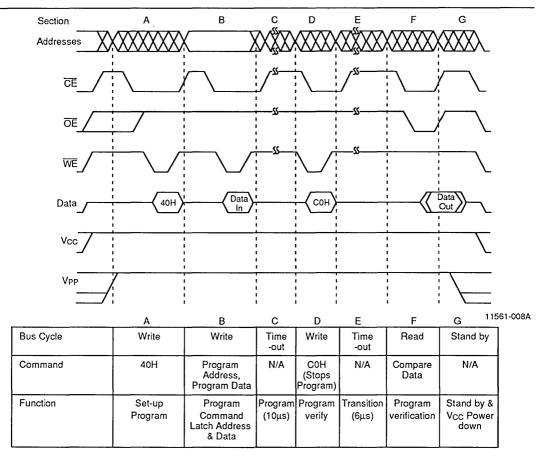

#### PARALLEL DEVICE PROGRAMMING - OVERVIEW

#### PARALLEL DEVICE PROGRAMMING FLOW CHART

### **Example: Parallel Erasure and Programming for Two Devices**

#### Parallel Erasure

The erase sequence will be followed as usual. The CPU will issue word commands. The erase word command is 2020H. Each device is independently verified and the address of the last verified byte per device is stored in separate registers. When one of the erase flags is active, indicating that a particular device has successfully completed erasure the CPU will change the command for that device from Erase to Read. This effectively masks the erased device from further erasure.

Should the high order byte device verify first, the next erase command will be 0020H. The low order byte device erases on each subsequent erase command until verified. The high order byte device remains in Read mode. During verification, write the erase verify command of 00A0H. This will enable the low order byte device for verify operations and maintains the erased high order byte device in Read mode.

#### Parallel Programming

The program sequence will be followed as usual. The CPU will issue word commands. The program word command is 4040H. Each device is independently verified. When one of the program flags is active, indicating that a particular device has successfully completed programming, the CPU will change the command for that device from Program to Read. This effectively masks the programmed device from further programming.

Should the high order byte device verify first, the next program command will be 0040H. The low order byte device programs on each subsequent program command until verified. The high order byte device remains in Read mode. During verification, write the program verify command of 00C0H. This will enable the low order byte device for verify operations and maintains the programmed high order byte device in Read mode.

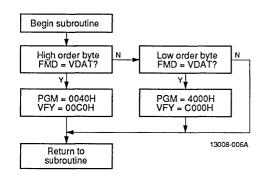

#### PARALLEL DEVICE PROGRAMMING - SUBROUTINE

#### High Order Byte and Low Order Byte Device Erase-verify and Mask Routine

This Subroutine verifies the high order and low order bytes independently. If either byte verifies, all commands are masked from that device.

The program command and program data are changed to a read command (00H) and null data (FFH) respectively.

The Program-verify command is changed to a Read command (00H).

#### Notes:

- During programming operations the FFH data is a null condition.

- If the high order byte verifies, then that byte is masked from further Program/Program-verify operations. The low order byte (LB) commands are not changed.

- If the low order byte verifies, then that byte is masked from further Program/Program-verify operations. The high order byte (HB)

commands are not changed.

# CHAPTER 4 AN-102 Generation and Control of V<sub>PP</sub> Programming Voltage for Flash Memories

| Introduction                                                                          |

|---------------------------------------------------------------------------------------|

| V <sub>PP</sub> Trace and Circuitry 4-2                                               |

| Device Decoupling4-2                                                                  |

| Hardwire V <sub>PP</sub> Voltage to the Flash Device 4–2                              |

| Umbilical Cord Programming 4–3                                                        |

| Vcc (5.0 V) to V <sub>PP</sub> (12.0 V) DC/DC Converter                               |

| Pump 5 V to V <sub>PP</sub> Voltage with Analog Circuitry                             |

| The Starter Kit: VPP Generation and Control 4-4                                       |

| Transmission Line Effects of Printed Circuit Board Traces on V <sub>PP</sub> Voltages |

## Generation and Control of VPP Programming Voltage for Flash Memories

AN-102

#### INTRODUCTION

Constant VPP voltage of 12.0 V  $\pm 0.6$  V is required for erase and programming operations. Parallel device reprogramming (either 16-bit or 32-bit data words) requires 30 mA of current for each device in the Flash memory array.

VPP voltage may be generated in a number of ways. Each of these options will be discussed during the text.

- 1. Hardwire VPP Voltage to the Flash Device.

- 2. Umbilical Cord Type Programming.

- 3. Use DC/DC Convertor to pump 5 V to VPP Voltage.

- 4. Pump 5 V to VPP Voltage with Analog Circuitry.

It is important to maintain the specified VPP voltages when programming the Flash memory device. All internal device voltages are generated from the VPP reference. Inappropriate VPP voltage may impair device performance. Internal voltages do not exceed that of external VPP.

Unlike other approaches to Flash memories, AMD's devices actually verify margin for each byte during erase and programming operations. This is accomplished during the Erase-verify and Program-verify operations respectively. During these operations, the appropriate margin-verify voltages are internally tapped off of the VPP voltage via the command register and internal VPP circuitry. This allows for Erase/Erase-verify and Program/Program-verify operations to be performed with static Vcc (5 V) and VPP (12 V) voltages.

Before proceeding, a few comments regarding basic design philosophy should be mentioned. Please make note of these comments for any of the VPP generation methods implemented.

#### **VPP Trace and Circuitry**

Be aware that AC current is a component of DC power switching characteristics. Design the printed circuit board traces handling this current to accommodate high frequency.

#### **Printed Circuit Board Trace Layout**

Use a single ground plane to eliminate potential loops. Keep all inductive impedances at a minimum on all high current traces.

#### **VPP Regulator Circuitry Layout**

Locate the V<sub>PP</sub> generation circuitry as close to the Flash memory array as possible. In addition, minimize lead lengths of the network. To help prevent noise from being picked up in feedback loops, locate all resistors and capacitors as close to the VPP network as possible. In order to prevent input ground loops, use separate returns for input and output capacitors.

#### **Device Decoupling**

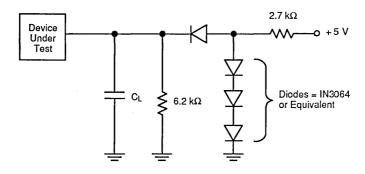

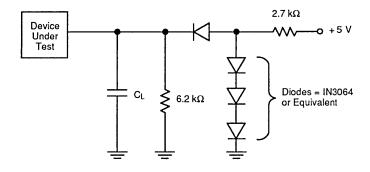

Switching  $\overline{\text{CE}}$  inputs for memory selection causes transient current peaks at the Flash device. The Flash memory devices should be decoupled with the appropriate capacitance from these transients.

- Connect 0.1µF ceramic capacitor between Vcc and Vss and one between Vpp and Vss. The capacitors should be placed as close to each device as possible.

- In addition, connect 4.7µF electrolytic capacitor between Vcc and Vss on the memory array's power supply. Do this for each set of eight memory devices. this bulk capacitor will maintain even voltage to the memory array.

### 1. HARDWIRE V<sub>PP</sub> VOLTAGE TO THE FLASH DEVICE

Typically this approach is used in the most cost sensitive applications. Regulated 12.0 V supplies are commonly available in many systems.

When Vcc = 0 V, the Vpp voltage is internally disabled from the device. Memory contents cannot be altered. The Flash device automatically resets to the read mode when Vcc rises above 2 V. This occurs even when Vpp = 12 V.

Power supply sequencing is not required.

The device will only respond to the correct sequence of commands in order to change the state of the Flash memory from Read mode to any other mode. In addition, the three control pins must be in their correct state  $(\overline{CE} = \text{Low}, \overline{OE} = \text{High and } \overline{WE} = \text{Low})$  in order to accept a command from the data bus.

A number of additional procedures are available to further prevent inadvertent writes should system glitches occur during system/device power transitions.

- Hold any control pin (CE, OE, or WE) in a non-write condition. This disables the device from executing any write operation (see example on the next page).

- Any "illegal" command (an illegal command is one that is not defined in the AMD Flash data sheet under the section – Command Definitions) written to the Flash device will automatically terminate any operation and reset the device to the Read Mode.

#### Example:

Holding WE in a non-write condition during power transitions.

In systems where the  $\overline{V_{PP}}$  pin is to be connected directly to the +12 V supply,  $\overline{WE}$  should be held in a non-write state during power supply transitions. This will prevent against inadvertent write conditions. One way to achieve this is by pulling  $\overline{WE}$  up to Vcc via a 2.7 K Ohm resistor.

During power supply transitions, VPP voltage is internally disabled from the Flash device until Vcc rises above 2 V. In addition, the Flash device automatically resets to the read mode as Vcc rises above 2 V. The  $\overline{WE}$  pin will be pulled up (VIH = 2 V) via the 2.7 K Ohm resistor as Vcc rises. When write enable is at VIH the command register is internally disabled from the internal state machine of the Flash device. When the command register is disabled, data commands can not be transferred to the state machine. Therefore the state of the Flash device will not be altered from the read mode. Access to the command register will be prevented until the  $\overline{WE}$  line is driven to a logic level low by the system write control.

Note: VIH Min. = 2.0 V R = 2.7 K

#### 2. UMBILICAL CORD PROGRAMMING

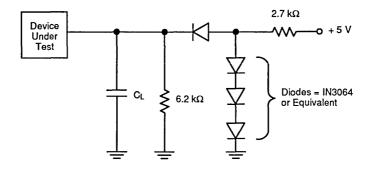

Many applications perform system updates using the umbilical cord or edge connector programming method. The external programming equipment supplies the 12.0 V  $\pm$  0.6 V VPP voltage. When the umbilical cord is disconnected, be aware that electrostatic discharge may build up on the floating VPP pin. To prevent against this problem, tie the VPP pin to ground via a large (10K $\Omega$ ) pull-up resistor and a capacitor (see Figure 1).

### 3. Vcc (5.0 V) to Vpp (12.0 V) DC/DC Convertor

A monolithic DC/DC convertor from Valor Electronics, the PM9006, is appropriate for the digital world to supply the 12.0 V  $\pm 0.6$  V VPP voltage. The VPP voltage is generated on chip using the standard system Vcc (5.0 V) voltage. Standard TTL commands are used to disable the 12.0 V output supply when programming or erasing operations are not intended. The enable (E) function provides absolute write protection to guarantee against inadvertent program or erasure. Flash memory contentscannot be altered without the active 12.0 V VPP supply. The enable pin also saves system power when DC/DC convertor is not required. The PM9006 has a minimum efficiency of 50% at full load. The PM9006 comes in a 24-pin package.

The Valor PM9006 provides a controlled 12.0 V output that is regulated within the  $\pm 5\%$  ( $\pm 0.6$  V) V<sub>PP</sub> specification. The standard system V<sub>CC</sub> (5.0 V) supply is converted to the V<sub>PP</sub> (12.0 V) supply by the DC/DC convertor. The voltage transitions are smooth and protect against destructive positive or negative overshoot.

The PM9006 can supply 165 mA of current at the regulated 12.0 V  $\pm$ 0.6 V output. The 5.0 V  $\pm$ 0.5 V DC input supply of the DC/DC convertor uses a maximum of 840 mA of input current. The Am28F010 specifies a maximum VPP current of 30 mA for either the erase or program operations. Actual current required for these operations is substantially lower than this. Given the maximum VPP current of 30 mA for each device, four(4) Am28F010 may be programmed and erased in parallel with one PM9006 device. The PM9006 VPP supply current = 165 mA - 4 x 30 mA of VPP current required for the Flash memory array = 45 mA of additional current available from the DC/DC convertor.

Parallel programming and erasure allows for the most efficient method to reprogram x16 or x32-bit data words. Refer to application note AN-101 for parallel program and erasue flow charts.

#### **Board Level Resets**

System designs should not allow the Flash device to perform any programming or erase operations when the CPU does not have control of the Flash device. Some designs incorporate board level reset circuitry that suspends operation of the local CPU if the Vcc level falls below a predetermined value (such as 4.6 V). If this is the case, the reset circuitry should also disable the VPP power supply whenever the CPU is held in reset.

If the local CPU is forced into reset mode while it is programming or erasing the Flash device, the system reset circuit should also terminate that operation. To accomplish this, the PM9006's enable pin should be driven high whenever the reset circuitry is active. Drive the chip enable pin of the PM9006 with the logical OR of the reset circuit's output signal and the chip enable control line to the PM9006. This will disable the VPP supply and hence terminate any programming or erase operation. The Flash device automatically resets to the read mode when VPP is disabled.

#### Note:

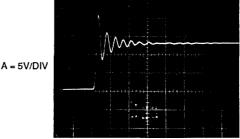

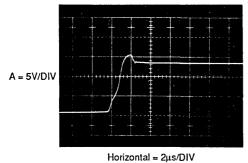

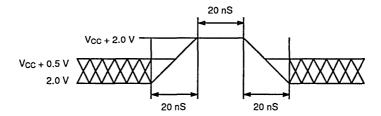

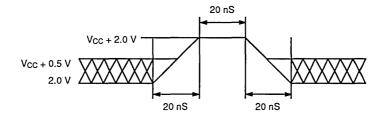

The circuit of Figure 2 will not spuriously overshoot during power-up or power-down. This prevents destruction of the device due to voltages that exceed specification. Vpp outputs are predictable and controllable during power supply transitions as a result of the referenced circuit designs. The compensation of the LT1072 causes a very overdamped pulse response. In addition, the control loops of the circuit are functioning even at low supply voltages. Thus the control loop is active before the memory circuits settle and prevents uncontrolled Vpp pulse outputs.

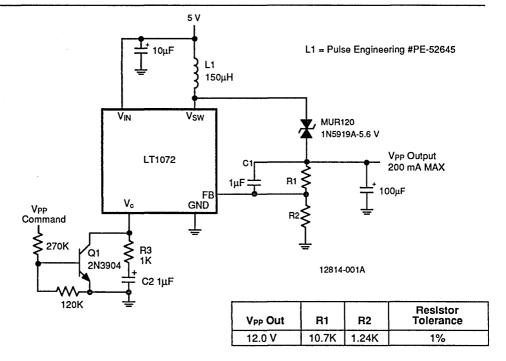

Figure 2. Basic Flash Memory VPP Programming Voltage Supply

Please reference the PM9006 data sheet for complete details of device operation. One method of implementing the PM9006 DC/DC convertor is illustrated below.

Pins 3 through 9 and 16 through 23 are not internally connected to the device and do not need to be driven.

#### Generate and Control 12.0 V

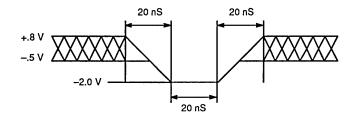

### 4. PUMP 5 V TO V<sub>PP</sub> VOLTAGE WITH ANALOG CIRCUITRY

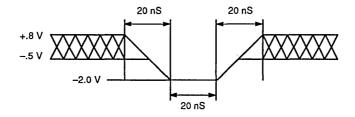

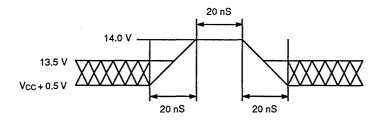

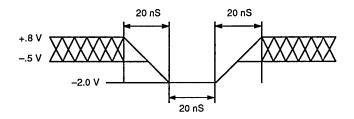

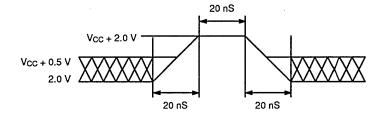

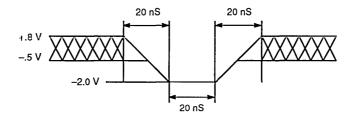

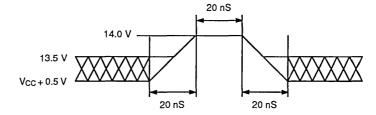

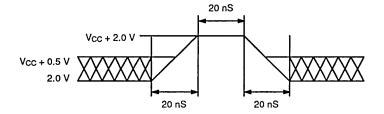

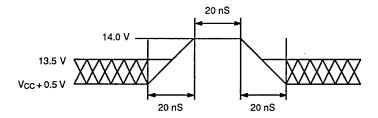

Flash memories require a V<sub>PP</sub> voltage of 12.0 V  $\pm 0.6$  V. It is important to note that V<sub>PP</sub> voltage must be maintained within the device specification for reliable operation. V<sub>PP</sub> voltages that exceed 14 V for 20 ns or longer are likely to destroy the device. Thus, we need to carefully control the high voltage programming circuitry. It should be noted that proper design of the V<sub>PP</sub> circuitry eliminates the issues of device destruction due to appli-

cation of voltages outside of the specified operating range. In addition, it is preferable to control the  $V_{PP}$  voltage with a 5.0 V logic command.

### The Starter Kit: VPP Generation and Control

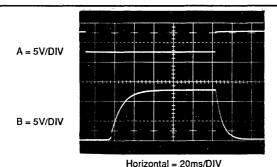

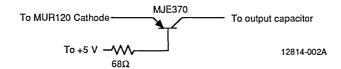

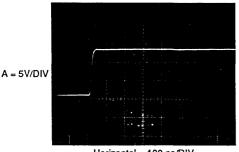

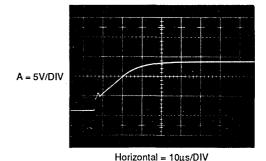

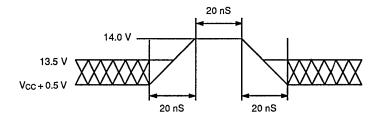

The basic circuit described in Figure 2 satisfies just about all V<sub>PP</sub> requirements for Flash memories. High voltage is produced by driving the V<sub>PP</sub> command low. The low V<sub>PP</sub> command (Trace A, Figure 3) activates the LT1072 switching regulator to drive L1. The resistor net-

work of R1 and R2 provides the DC feedback. C1, R3 and C2 control the AC roll-off. Trace B illustrates the resulting  $V_{PP}$  voltage that rises smoothly to the required level. The values specified for R1 and R2 determine the 12.0 V output. Leave the 5.6 V zener in the circuit in order to return the output to 0 V when the  $V_{PP}$  command goes high. When a 4.5 V minimum output is desired the zener may be omitted. Circuit trimming requirements

are eliminated due to the tight internal references of the LT1072. Only precision resistors are required.

The table in Figure 4 gives additional information required to provide greater power output from the referenced circuit. The synchronous switch option of Figure 4 may replace the zener and eliminate its power dissipation.

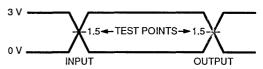

Figure 3. Waveforms for Basic Flash Programming Supply

Power Options for Basic VPP Generator

| Output<br>Current | Соит   | Regulator | Inductor | Zener                                         |

|-------------------|--------|-----------|----------|-----------------------------------------------|

| 400mA             | 200 μF | LT1071    | PE-52645 | 1N5339A<br>or<br>Synchronous<br>Switch Option |