## **405EP**PPC405EP Embedded Processor

Preliminary User's Manual

# PPC405EP Embedded Processor User's Manual

Applied Micro Circuits Corporation 6290 Sequence Dr., San Diego, CA 92121

Phone: (858) 450-9333 — (800) 755-2622 — Fax: (858) 450-9885

http://www.amcc.com

AMCC reserves the right to make changes to its products, its datasheets, or related documentation, without notice and warrants its products solely pursuant to its terms and conditions of sale, only to substantially comply with the latest available datasheet. Please consult AMCC's Term and Conditions of Sale for its warranties and other terms, conditions and limitations. AMCC may discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information is current. AMCC does not assume any liability arising out of the application or use of any product or circuit described herein, neither does it convey any license under its patent rights nor the rights of others. AMCC reserves the right to ship devices of higher grade in place of those of lower grade.

AMCC SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

AMCC is a registered Trademark of Applied Micro Circuits Corporation. Copyright © 2007 Applied Micro Circuits Corporation.

#### **Table of Contents**

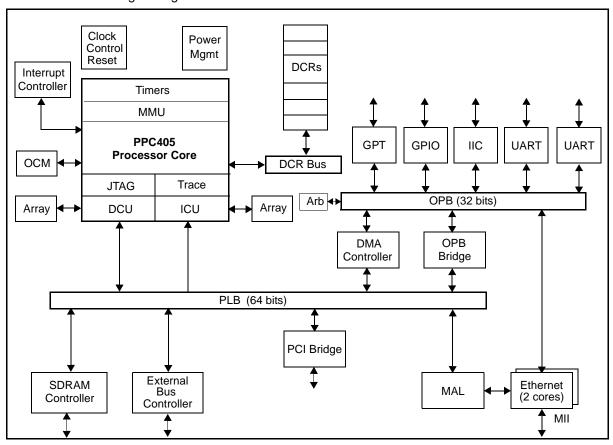

| Chapter 1. Overview1                                  | 1-43 |

|-------------------------------------------------------|------|

| PPC405EP Features                                     | 1-44 |

| Bus and Peripheral Features                           | 1-44 |

| PowerPC 405 Processor Core Features                   |      |

| PowerPC Architecture                                  |      |

| The PPC405EP as a PowerPC Implementation              |      |

| RISC Processor Core Organization                      |      |

| Instruction and Data Cache Controllers                | 1-47 |

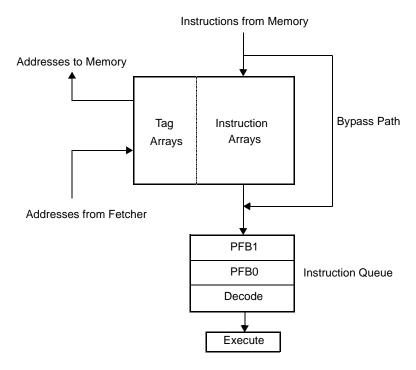

| Instruction Cache Unit                                |      |

| Data Cache Unit                                       |      |

| Memory Management Unit                                |      |

| Timer Facilities                                      |      |

| Debug                                                 |      |

| Development Tool Support                              |      |

| Debug Modes                                           |      |

| Processor Core Interfaces                             |      |

| Processor Local Bus                                   |      |

| Device Control Register Bus                           |      |

| Clock and Power Management                            |      |

| JTAG                                                  |      |

| Interrupts                                            |      |

| On-Chip Memory                                        |      |

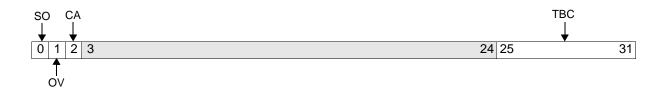

| Processor Core Programming Model                      |      |

| Data Types                                            |      |

| Processor Core Register Set Summary                   |      |

| General Purpose Registers                             |      |

| Special Purpose Registers                             |      |

| Machine State Register                                |      |

| Condition Register                                    |      |

| Device Control Registers                              |      |

| Memory-Mapped I/O Registers                           |      |

| Addressing Modes                                      |      |

| · ·                                                   |      |

| Chapter 2. On-Chip Buses1                             |      |

| Processor Local Bus                                   | 1-53 |

| PLB Features                                          |      |

| PLB Masters and Slaves                                | 1-54 |

| PLB Master Assignments                                |      |

| PLB Transfer Protocol                                 |      |

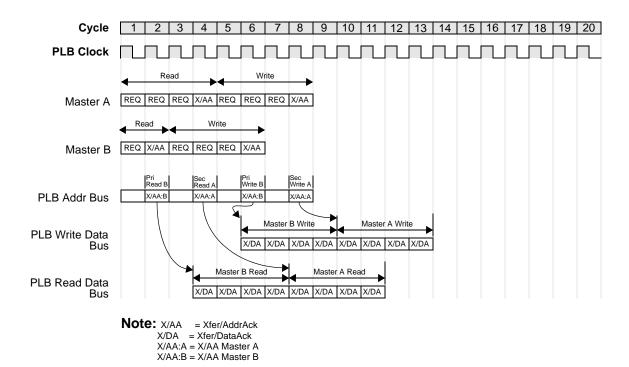

| Overlapped PLB Transfers                              | 1-55 |

| PLB Arbiter Registers                                 |      |

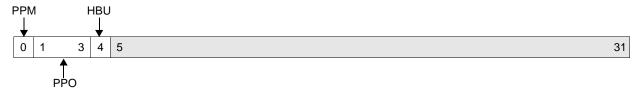

| PLB Arbiter Control Register (PLB0_ACR)               |      |

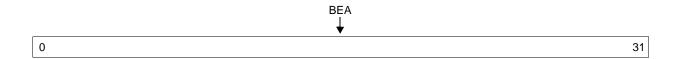

| PLB Error Address Register (PLB0_BEAR)                | 1-57 |

| PLB Error Status Register (PLB0_BESR)                 | 1-58 |

| PLB to OPB Bridge Registers                           |      |

| Bridge Error Address Register (POB0_BEAR)             |      |

| Bridge Error Status Registers (POB0_BESR0-POB0_BESR1) | 1-60 |

| On-Chip Peripheral Bus                                | 1-62 |

| OPB Features                                          | 1-62 |

| OPB Master Assignments                                | 1-63 |

| OPB Arbiter Registers                                 |      |

| OPB Arbiter Control Register (OPBA0 CR)               | 1-63 |

| OPB Arbiter Priority Register (OPBA0_PR)                              | 1    | -64 |

|-----------------------------------------------------------------------|------|-----|

| Chapter 3. Programming Model                                          | . 1- | 67  |

| User and Privileged Programming Models                                | 1    | -67 |

| Memory Organization and Addressing                                    |      |     |

| Physical Address Map                                                  |      |     |

| Storage Attributes                                                    |      |     |

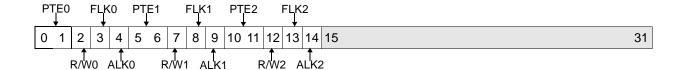

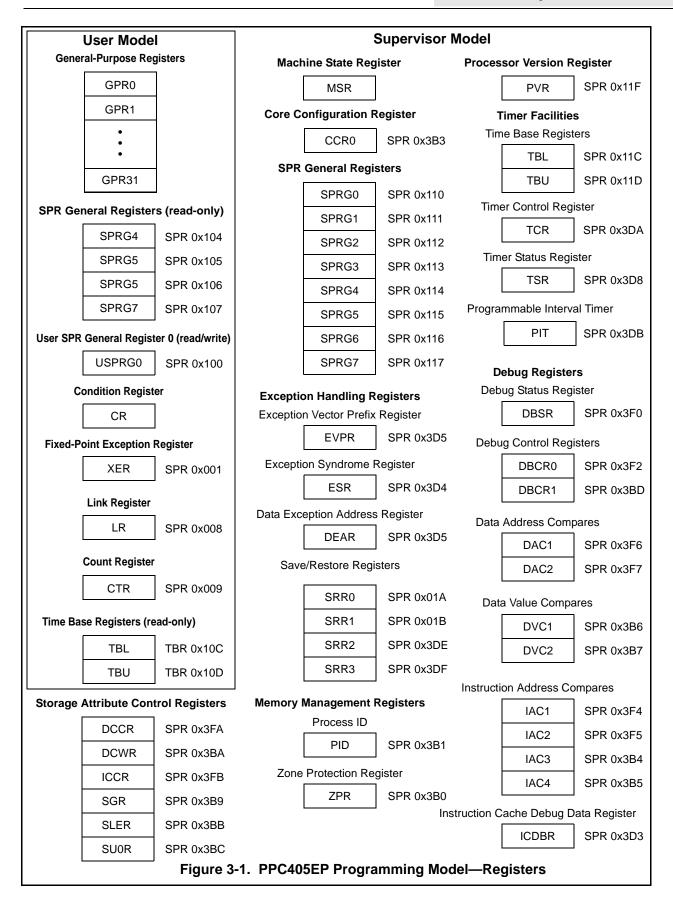

| Registers                                                             |      |     |

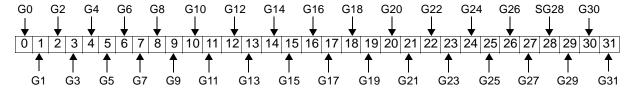

| General Purpose Registers (R0-R31)                                    |      |     |

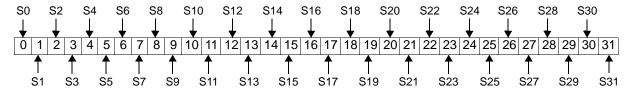

| Special Purpose Registers                                             |      |     |

| Count Register (CTR)                                                  |      |     |

| Link Register (LR)                                                    |      |     |

| Fixed Point Exception Register (XER)                                  |      |     |

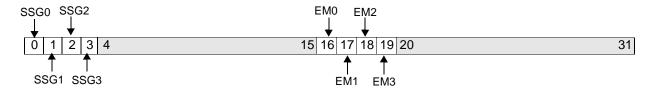

| Special Purpose Register General (SPRG0–SPRG7)                        |      |     |

| Processor Version Register (PVR)                                      |      |     |

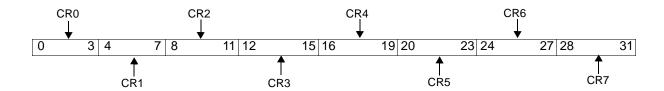

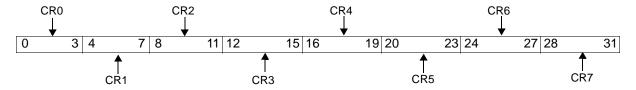

| Condition Register (CR)                                               |      |     |

| CR Fields after Compare Instructions                                  |      |     |

| The CR0 Field                                                         |      |     |

| The Time Base                                                         |      |     |

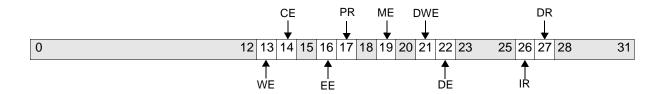

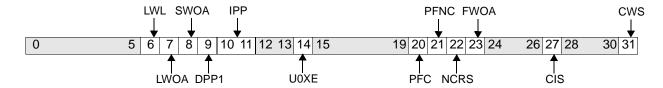

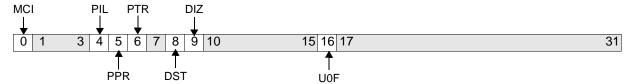

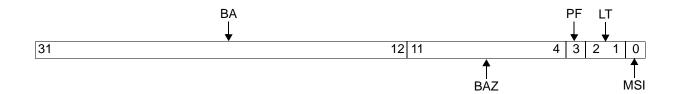

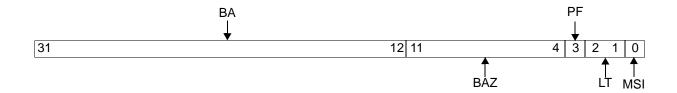

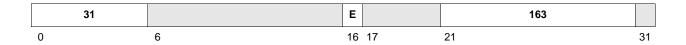

| Machine State Register (MSR)                                          |      |     |

| Device Control Registers                                              |      |     |

| Directly Accessed DCRs                                                |      |     |

| Indirectly Accessed DCRs                                              |      |     |

| Memory-Mapped Input/Output Registers                                  |      |     |

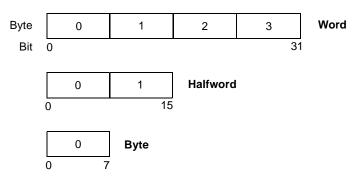

| Data Types and Alignment                                              |      |     |

| Alignment for Storage Reference and Cache Control Instructions        |      |     |

| Alignment and Endian Operation                                        |      |     |

| Summary of Instructions Causing Alignment Exceptions                  | . 1  | -90 |

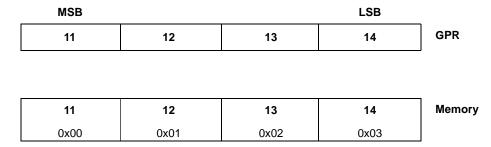

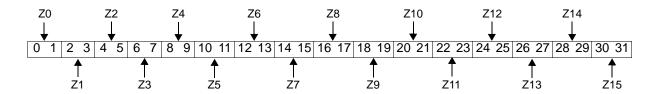

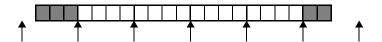

| Byte Ordering                                                         |      |     |

| Structure Mapping Examples                                            |      |     |

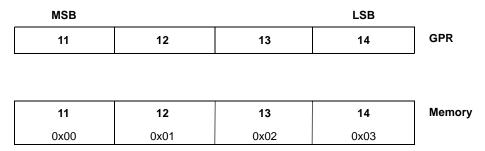

| Big Endian Mapping                                                    |      |     |

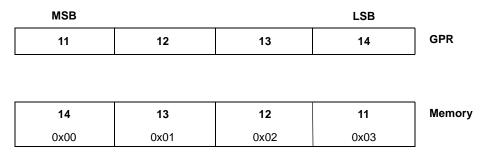

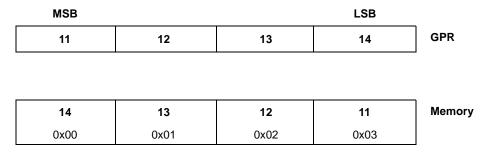

| Little Endian Mapping                                                 |      |     |

| Support for Little Endian Byte Ordering                               |      |     |

| Endian (E) Storage Attribute                                          |      |     |

| Fetching Instructions from Little Endian Storage Regions              |      |     |

| Accessing Data in Little Endian Storage Regions                       |      |     |

| PowerPC Byte-Reverse Instructions                                     |      |     |

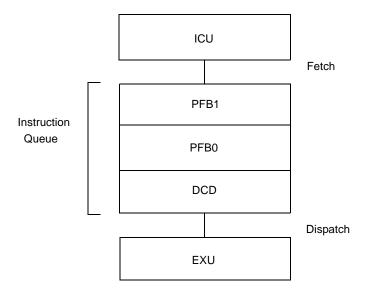

| Instruction Processing                                                |      |     |

| Branch Processing                                                     |      |     |

| Unconditional Branch Target Addressing Options                        |      |     |

| Conditional Branch Target Addressing Options                          |      |     |

| Conditional Branch Condition Register Testing                         |      |     |

| BO Field on Conditional Branches                                      |      |     |

| Branch Prediction                                                     |      |     |

|                                                                       |      |     |

| Speculative Accesses                                                  |      |     |

| Prefetch Distance Down an Unresolved Branch Path                      |      |     |

| Prefetch of Branches to the CTR and Branches to the LR                |      |     |

|                                                                       |      |     |

| Preventing Inappropriate Speculative Accesses                         |      |     |

| Fetching Past an Interrupt-Causing or Interrupt-Returning Instruction |      |     |

| Fetching Past tw or twi Instructions                                  |      |     |

| Fetching Past an Unconditional Branch                                 |      |     |

| Suggested Locations of Memory-Mapped Hardware                         |      |     |

| Summary                                                               |      |     |

| Privileged Mode Operation                                             |      |     |

| MSR Bits and Exception Handling                                       |      |     |

| Privileged Instructions                                               | 1-1  | 104 |

| Privileged SPRs                                                  | 1-104   |

|------------------------------------------------------------------|---------|

| Privileged DCRs                                                  |         |

| Synchronization                                                  |         |

| Context Synchronization                                          |         |

| Execution Synchronization                                        |         |

| Storage Synchronization                                          |         |

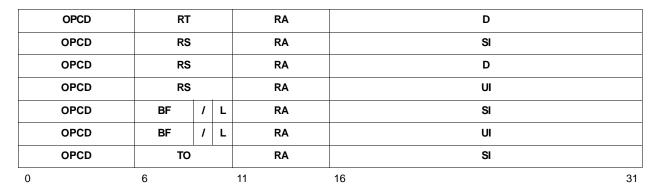

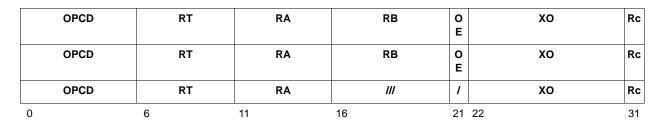

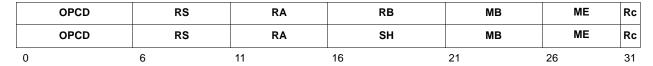

| Instruction Set                                                  |         |

| Instructions Specific to the IBM PowerPC Embedded Environment    |         |

| Storage Reference Instructions                                   |         |

| Arithmetic Instructions                                          |         |

| Logical Instructions                                             |         |

| Compare Instructions                                             |         |

| Branch Instructions                                              |         |

| CR Logical Instructions                                          |         |

| Rotate Instructions                                              |         |

| Shift Instructions                                               | 1-113   |

| Cache Management Instructions                                    |         |

| Interrupt Control Instructions                                   |         |

| TLB Management Instructions                                      |         |

| Processor Management Instructions                                |         |

| Extended Mnemonics                                               |         |

| Chapter 4. Cache Operations                                      | 1_117   |

|                                                                  |         |

| ICU Organization                                                 |         |

| ICU Operations                                                   |         |

| Instruction Cachability Control                                  |         |

| Instruction Cache Synonyms                                       |         |

| ICU Coherency                                                    |         |

| DCU Organization                                                 |         |

| DCU Operations                                                   |         |

| DCU Write Strategies                                             |         |

| DCU Load and Store Strategies                                    |         |

| Data Cachability Control                                         |         |

| DCU Coherency                                                    |         |

| Cache Instructions                                               |         |

| ICU Instructions                                                 |         |

| DCU Instructions                                                 |         |

| Cache Control and Debugging Features                             |         |

| CCR0 Programming Guidelines                                      |         |

| ICU Debugging                                                    |         |

| DCU Debugging                                                    |         |

| DCU Performance                                                  |         |

| Pipeline Stalls                                                  |         |

| Cache Operation Priorities                                       |         |

| Simultaneous Cache Operations                                    |         |

| Sequential Cache Operations                                      |         |

| Chapter 5. On-Chip Memory                                        | . 1-135 |

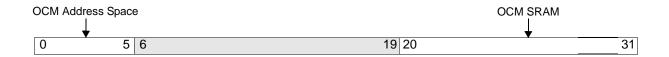

| OCM Addressing                                                   | 1-136   |

| OCM Programming Guidelines                                       |         |

| Store Data Bypass Behavior and Memory Coherency                  | 1-137   |

| Registers                                                        |         |

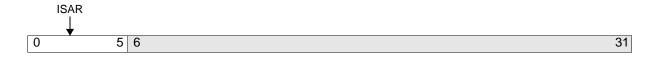

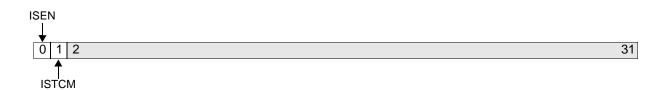

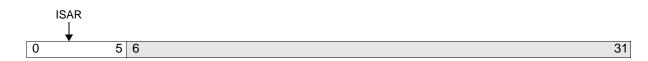

| OCM Instruction-Side Address Range Compare Register (OCM0_ISARC) |         |

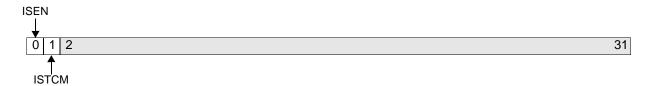

| OCM Instruction-Side Control Register (OCM0_ISCNTL)              |         |

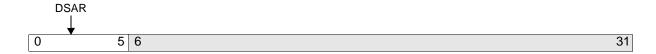

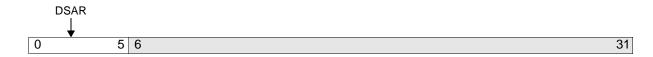

| OCM Data-Side Address Range Compare Register (OCM0_DSARC)        |         |

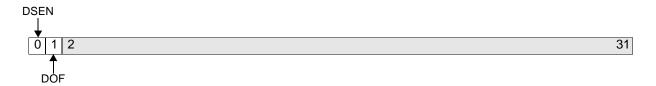

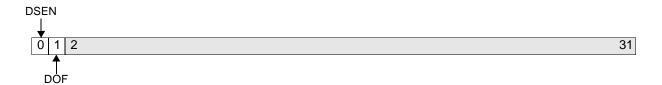

| OCM Data-Side Control Register (OCM0_DSCNTL)                     | 1-141   |

| Chapter 6. Memory Management                     | 1-143  |

|--------------------------------------------------|--------|

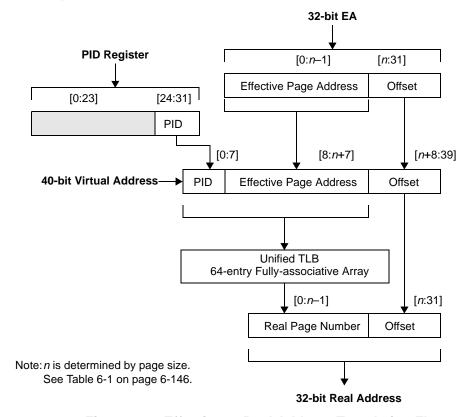

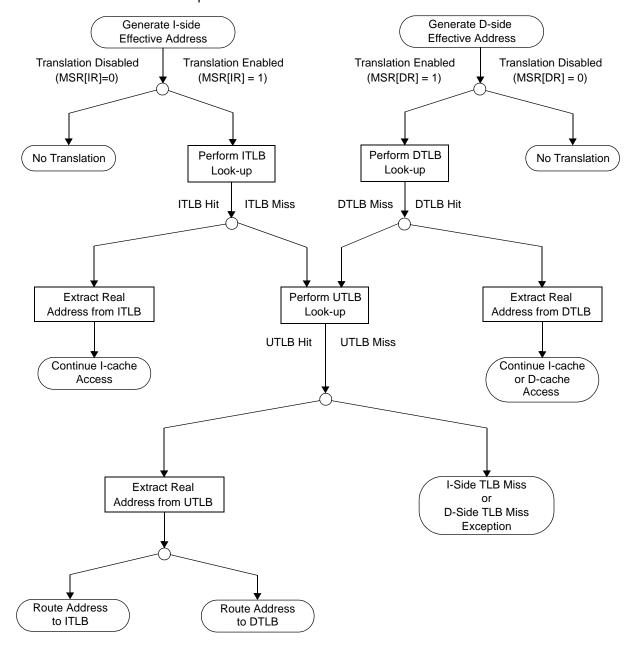

| MMU Overview                                     | 1-143  |

| Address Translation                              | 1-143  |

| Translation Lookaside Buffer (TLB)               | 1-144  |

| Unified TLB                                      |        |

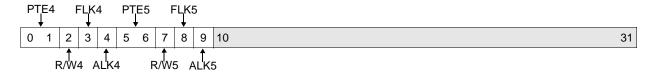

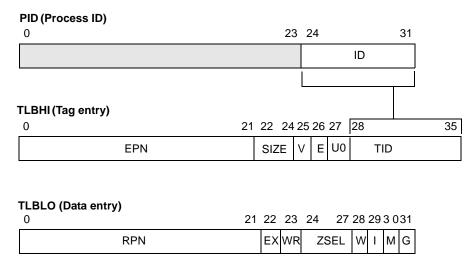

| TLB Fields                                       | 1-145  |

| Page Identification Fields                       |        |

| Translation Field                                |        |

| Access Control Fields                            |        |

| Storage Attribute Fields                         |        |

| Shadow Instruction TLB                           |        |

| ITLB Accesses                                    |        |

| Shadow Data TLB                                  |        |

| 1 DTLB Accesses                                  |        |

| Shadow TLB Consistency                           |        |

| TLB-Related Interrupts                           |        |

| Data Storage Interrupt                           |        |

| Instruction Storage Interrupt                    |        |

| Data TLB Miss Interrupt                          |        |

| Instruction TLB Miss Interrupt                   |        |

| TLB Management                                   |        |

| TLB Search Instructions (tlbsx/tlbsx.)           |        |

| TLB Read/Write Instructions (tlbre/tlbwe)        |        |

| TLB Invalidate Instruction (tlbia)               |        |

| TLB Sync Instruction (tlbsync)                   |        |

| Recording Page References and Changes            | 1-153  |

| Access Protection                                |        |

| Access Protection Mechanisms in the TLB          |        |

| General Access Protection                        |        |

| Execute Permissions                              |        |

| Write Permissions                                |        |

| Zone Protection                                  |        |

| Access Protection for Cache Control Instructions |        |

| Access Protection for String Instructions        |        |

| Real-Mode Storage Attribute Control              |        |

| Storage Attribute Control Registers              |        |

| Data Cache Write-through Register (DCWR)         |        |

| Data Cache Cachability Register (DCCR)           |        |

| Instruction Cache Cachability Register (ICCR)    |        |

| Storage Guarded Register (SGR)                   |        |

| Storage User-defined 0 Register (SU0R)           |        |

| Storage Little-Endian Register (SLER)            | .1-160 |

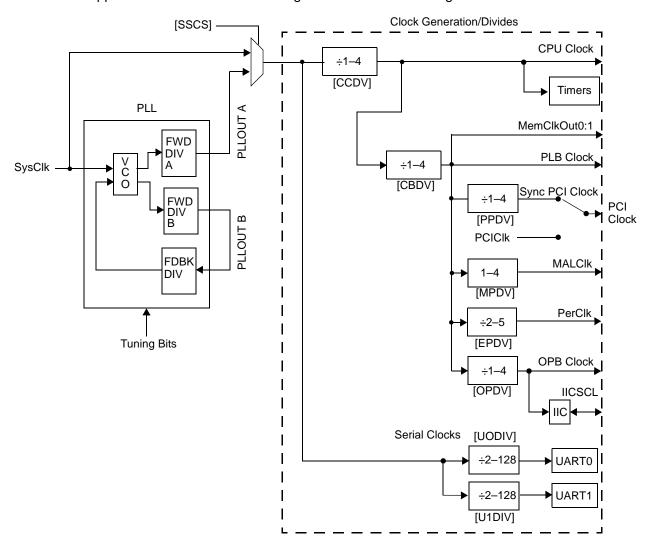

| Chapter 7. Clocking                              | 1-163  |

| Input Reference Clock (SysClk)                   | 1-163  |

| PLL Overview                                     |        |

| Software Clock Configuration After Reset         |        |

| PCI Clocking                                     |        |

| PCI Adapter Applications                         |        |

| Serial Port Clocking                             |        |

| Clocking Registers                               |        |

| Boot Control Register (CPC0_BOOT)                |        |

| EMAC to PHY Control Register (CPC0_EPCTL)        |        |

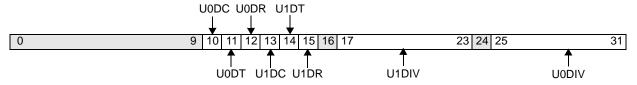

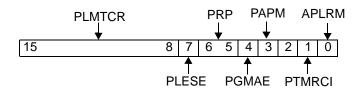

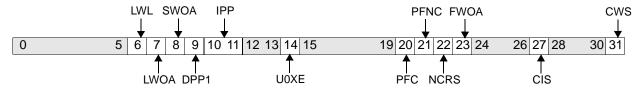

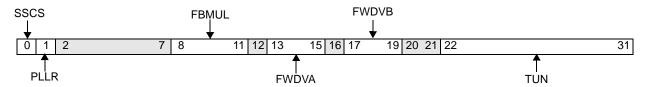

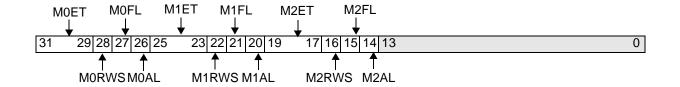

| PLL Mode Register 0 (CPC0_PLLMR0)                |        |

| PLL Mode Register 1 (CPC0_PLLMR1)                |        |

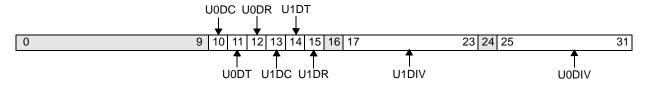

| UART Control Register (CPC0_UCR)                 |        |

| Chapter 8. Reset and Initialization                                  | 1-175          |

|----------------------------------------------------------------------|----------------|

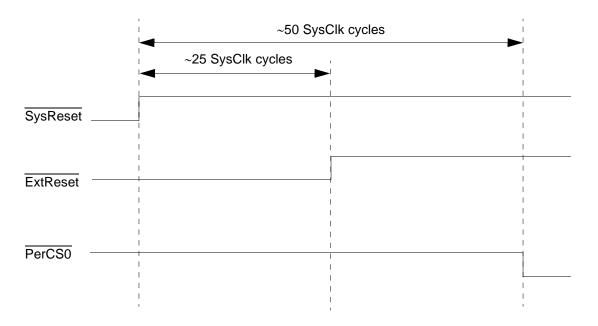

| Reset Signals                                                        | 1-175          |

| Reset Types                                                          | 1-175          |

| Core Reset                                                           |                |

| Chip Reset                                                           |                |

| System Reset                                                         |                |

| PCI Power Management Initiated Resets                                |                |

| Processor Initiated Resets                                           |                |

| Software Reset of the PCI Interface                                  |                |

| Processor State After Reset                                          |                |

| Machine State Register Contents after Reset                          |                |

| Contents of Special Purpose Registers after Reset                    |                |

| DCR Contents after Reset                                             |                |

| MMIO Register Contents After Reset                                   |                |

| PPC405EP Chip Initialization                                         |                |

| OCM Initialization                                                   |                |

| Initializing Instruction-Side OCM                                    |                |

| Initializing Data-Side OCM                                           |                |

| UIC Initialization                                                   |                |

| PPC405EP Initial Processor Sequencing                                |                |

| Initialization Requirements                                          |                |

| Initialization Code Example                                          |                |

| Chapter 9. Pin Strapping and Sharing                                 | 1-195          |

| Pin Strapping                                                        |                |

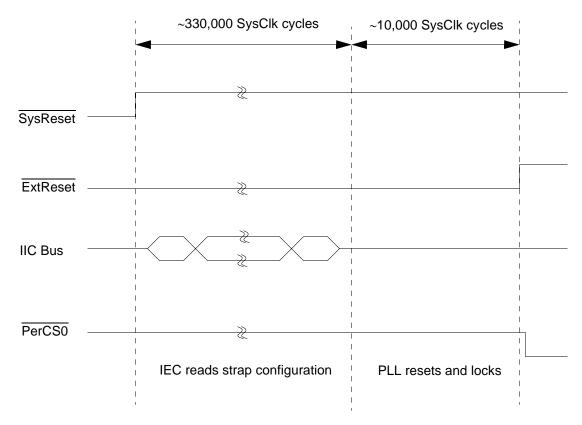

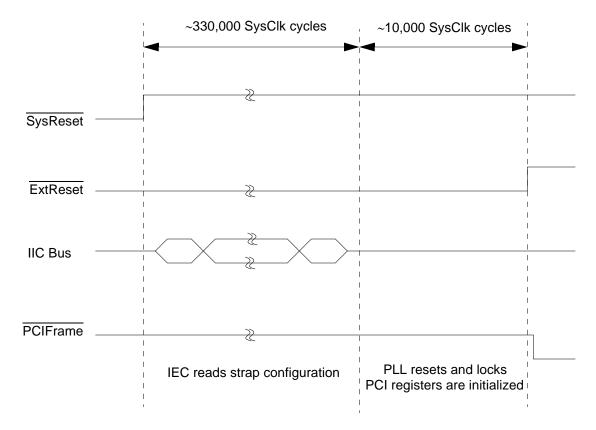

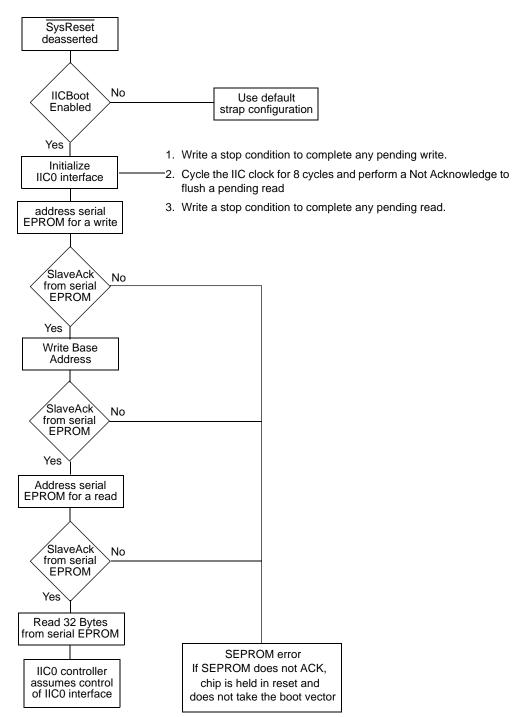

| IIC serial EPROM controller (IEC) Operation                          |                |

| Pin Strapping Registers                                              |                |

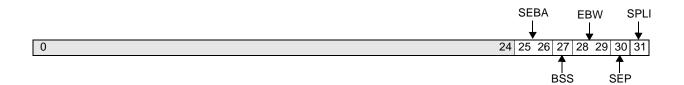

| Boot Control Register (CPC0_BOOT)                                    |                |

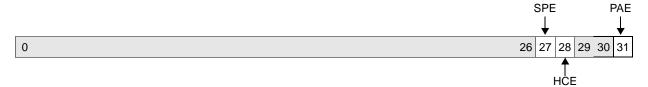

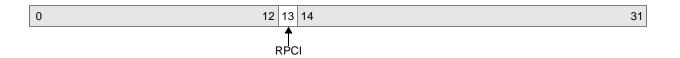

| PCI Bootstrap Control Register (CPC0_PCI)                            |                |

| Pin Sharing                                                          | 1-201          |

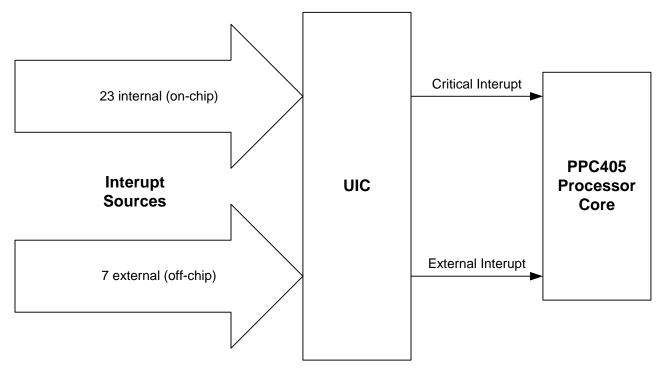

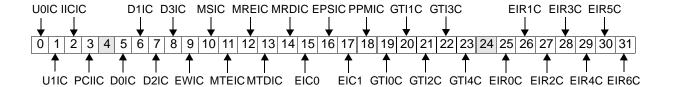

| Chapter 10. Interrupt Controller Operations                          | 1-203          |

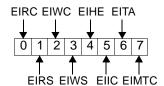

| UIC Overview                                                         | 1-203          |

| UIC Features                                                         | 1-204          |

| UIC Interrupt Assignments                                            | 1-204          |

| Interrupt Programmability                                            | 1-205          |

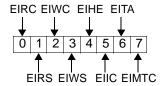

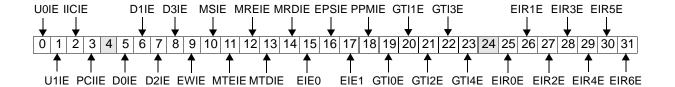

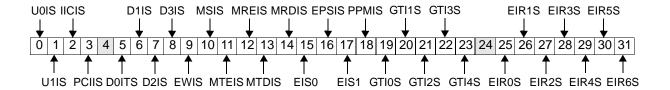

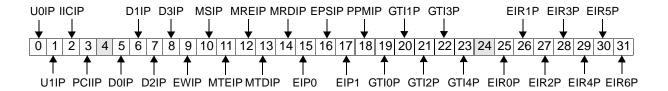

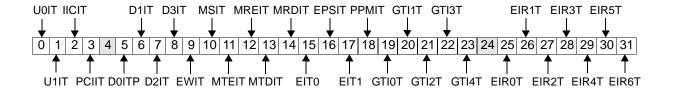

| UIC Registers                                                        |                |

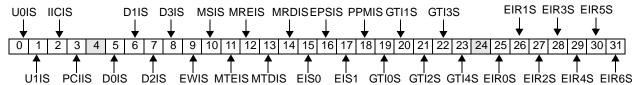

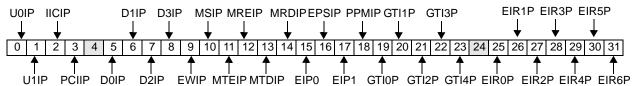

| UIC Status Register (UIC0_SR)                                        |                |

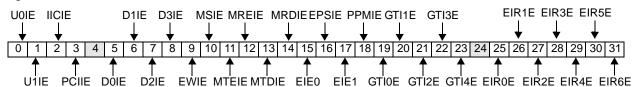

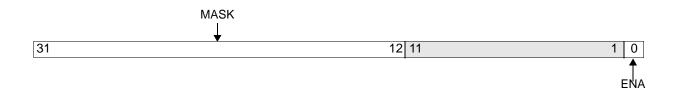

| UIC Enable Register (UIC0_ER)                                        |                |

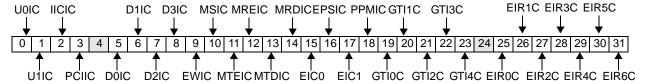

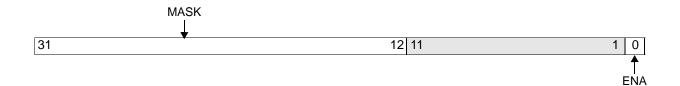

| UIC Critical Register (UIC0_CR)                                      |                |

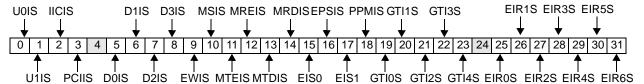

| UIC Polarity Register (UIC0_PR)                                      |                |

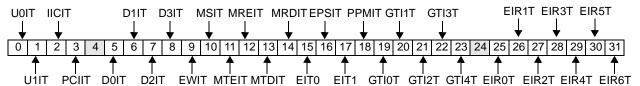

| UIC Trigger Register (UIC0_TR)                                       |                |

| UIC Masked Status Register (UICO_MSR)                                |                |

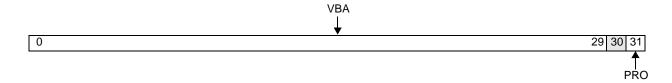

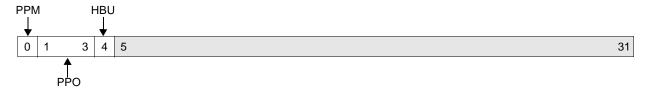

| UIC Vector Configuration Register (UIC0_VCR)                         |                |

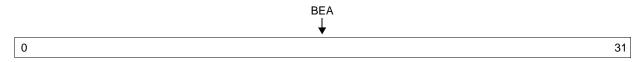

| UIC Vector Register (UIC0_VR)                                        |                |

| Using the Value in UICO_VR as a Vector Address or Entry Table Lookup |                |

| Vector Generation Scenarios                                          |                |

| Interrupt Handling in the Processor Core                             |                |

| Architectural Definitions and Behavior                               |                |

| Behavior of the PPC405EP Implementation                              |                |

| Interrupt Handling Priorities                                        |                |

| Consequent Interrupts                                                |                |

| General Interrupt Handling Registers                                 |                |

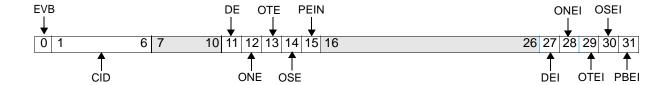

| Machine State Register (MSR)                                         |                |

| Save/Restore Registers 0 and 1 (SRR0–SRR1)                           |                |

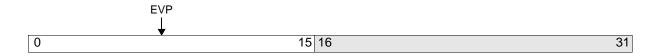

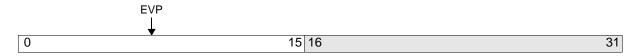

| Exception Vector Prefix Register (EVPR)                              |                |

| LAUUPUUI YUUUI IUIIA NEYISIEI (LYIN)                                 | 1 <u>-</u> ∠31 |

| Exception Syndrome Register (ESR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 1-232                                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Exception Address Register (DEAR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                  |

| Critical Input Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 1-234                                                                                                                                                                          |

| Machine Check Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                  |

| Instruction Machine Check Handling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                  |

| Data Machine Check Handling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1-236                                                                                                                                                                            |

| Data Storage Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                  |

| Instruction Storage Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 1-237                                                                                                                                                                          |

| External Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1-238                                                                                                                                                                            |

| External Interrupt Handling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1-238                                                                                                                                                                            |

| Alignment Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 1-239                                                                                                                                                                          |

| Program Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 1-239                                                                                                                                                                          |

| System Call Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 1-240                                                                                                                                                                          |

| Programmable Interval Timer (PIT) Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1-241                                                                                                                                                                            |

| Fixed Interval Timer (FIT) Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 1-241                                                                                                                                                                          |

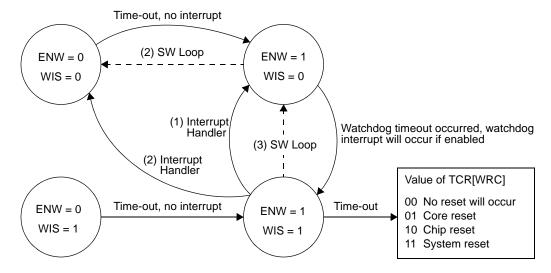

| Watchdog Timer Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 1-242                                                                                                                                                                          |

| Data TLB Miss Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 1-243                                                                                                                                                                          |

| Instruction TLB Miss Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 1-243                                                                                                                                                                          |

| Debug Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 1-244                                                                                                                                                                          |

| Chapter 11. Timer Facilities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1-245                                                                                                                                                                            |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                  |

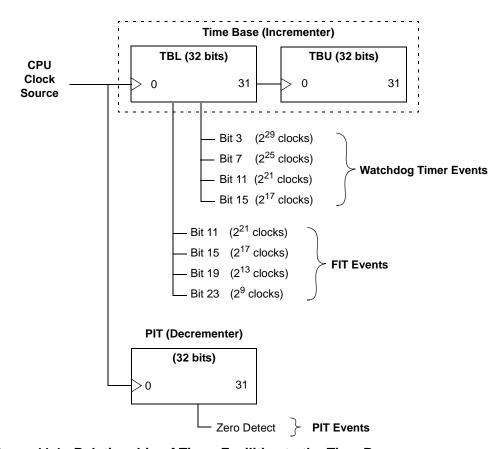

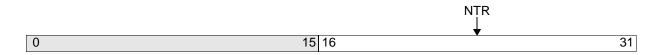

| Time Base                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                  |

| Reading the Time Base                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                  |

| Writing the Time Base                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                  |

| Programmable Interval Timer (PIT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                  |

| Fixed Interval Timer (FIT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                  |

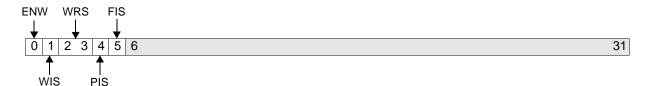

| Watchdog Timer Timer Status Register (TSR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                  |

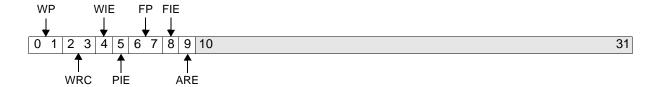

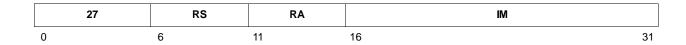

| Timer Control Register (TCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                  |

| Tiller Cultion Register (TCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1-200                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4 OEE                                                                                                                                                                            |

| Chapter 12. General Purpose Timers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                  |

| Chapter 12. General Purpose Timers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1-255                                                                                                                                                                            |

| Chapter 12. General Purpose Timers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 1-255<br>. 1-255                                                                                                                                                               |

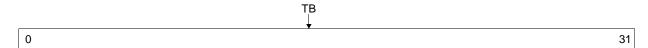

| Chapter 12. General Purpose Timers  GPT Features  GPT Operations  Time Base Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 1-255<br>. 1-255<br>. 1-255                                                                                                                                                    |

| Chapter 12. General Purpose Timers  GPT Features  GPT Operations  Time Base Counter  Compare Timers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 1-255<br>. 1-255<br>. 1-255<br>. 1-256                                                                                                                                         |

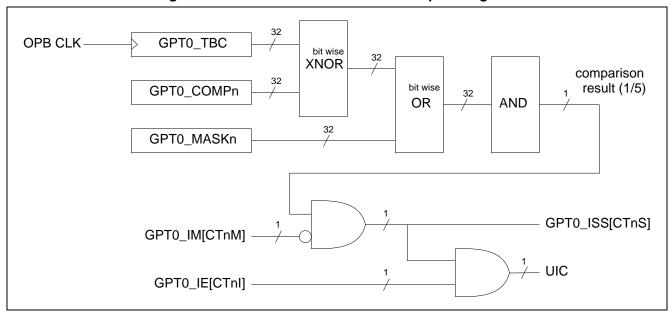

| Chapter 12. General Purpose Timers  GPT Features  GPT Operations  Time Base Counter  Compare Timers  Compare Timers Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1-255<br>1-255<br>1-255<br>1-256<br>1-256                                                                                                                                        |

| Chapter 12. General Purpose Timers  GPT Features  GPT Operations  Time Base Counter  Compare Timers  Compare Timers Interrupt  GPT Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1-255<br>1-255<br>1-255<br>1-256<br>1-256                                                                                                                                        |

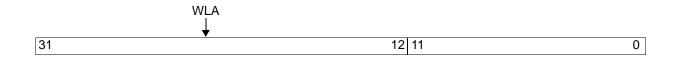

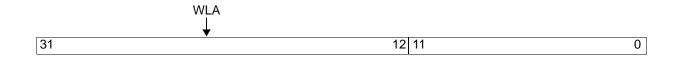

| Chapter 12. General Purpose Timers  GPT Features  GPT Operations  Time Base Counter  Compare Timers  Compare Timers Interrupt  GPT Registers  GPT Time Base Counter Register (GPT0_TBC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1-255<br>1-255<br>1-255<br>1-256<br>1-256<br>1-257                                                                                                                               |

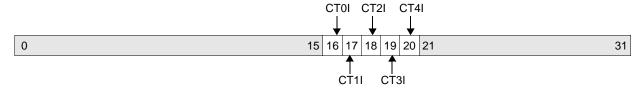

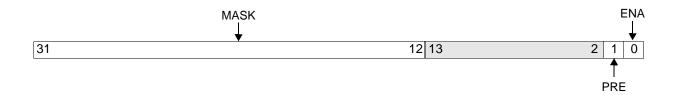

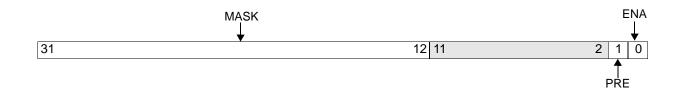

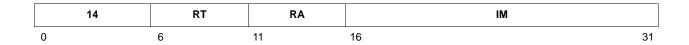

| Chapter 12. General Purpose Timers  GPT Features  GPT Operations  Time Base Counter  Compare Timers  Compare Timers Interrupt  GPT Registers  GPT Time Base Counter Register (GPT0_TBC)  GPT Interrupt Mask Register (GPT0_IM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1-255<br>1-255<br>1-256<br>1-256<br>1-257<br>1-257<br>1-258                                                                                                                      |

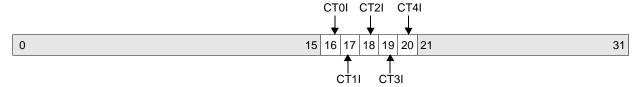

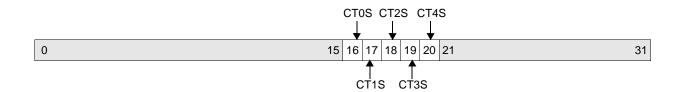

| Chapter 12. General Purpose Timers  GPT Features  GPT Operations  Time Base Counter  Compare Timers  Compare Timers Interrupt  GPT Registers  GPT Time Base Counter Register (GPT0_TBC)  GPT Interrupt Mask Register (GPT0_IM)  GPT Interrupt Status Register (GPT0_ISS and GPT0_ISC)                                                                                                                                                                                                                                                                                                                                                                                                                        | 1-255<br>1-255<br>1-256<br>1-256<br>1-257<br>1-257<br>1-258<br>1-259                                                                                                             |

| Chapter 12. General Purpose Timers  GPT Features  GPT Operations  Time Base Counter  Compare Timers  Compare Timers Interrupt  GPT Registers  GPT Time Base Counter Register (GPT0_TBC)  GPT Interrupt Mask Register (GPT0_IM)  GPT Interrupt Status Register (GPT0_ISS and GPT0_ISC)  GPT Interrupt Enable Register (GPT0_IE)                                                                                                                                                                                                                                                                                                                                                                               | 1-255<br>1-255<br>1-256<br>1-256<br>1-257<br>1-257<br>1-258<br>1-259<br>1-260                                                                                                    |

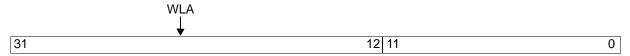

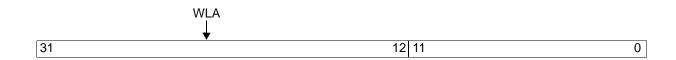

| Chapter 12. General Purpose Timers  GPT Features  GPT Operations  Time Base Counter  Compare Timers  Compare Timers Interrupt  GPT Registers  GPT Time Base Counter Register (GPT0_TBC)  GPT Interrupt Mask Register (GPT0_IM)  GPT Interrupt Status Register (GPT0_ISS and GPT0_ISC)  GPT Interrupt Enable Register (GPT0_IE)  GPT Compare Timer Registers (GPT0_COMP0 - GPT0_COMP4)                                                                                                                                                                                                                                                                                                                        | 1-255<br>1-255<br>1-256<br>1-256<br>1-257<br>1-257<br>1-258<br>1-259<br>1-260                                                                                                    |

| Chapter 12. General Purpose Timers  GPT Features  GPT Operations  Time Base Counter  Compare Timers  Compare Timers Interrupt  GPT Registers  GPT Time Base Counter Register (GPT0_TBC)  GPT Interrupt Mask Register (GPT0_IM)  GPT Interrupt Status Register (GPT0_ISS and GPT0_ISC)  GPT Interrupt Enable Register (GPT0_IE)                                                                                                                                                                                                                                                                                                                                                                               | 1-255<br>1-255<br>1-256<br>1-256<br>1-257<br>1-257<br>1-258<br>1-259<br>1-260                                                                                                    |

| Chapter 12. General Purpose Timers  GPT Features  GPT Operations  Time Base Counter  Compare Timers  Compare Timers Interrupt  GPT Registers  GPT Time Base Counter Register (GPT0_TBC)  GPT Interrupt Mask Register (GPT0_IM)  GPT Interrupt Status Register (GPT0_ISS and GPT0_ISC)  GPT Interrupt Enable Register (GPT0_IE)  GPT Compare Timer Registers (GPT0_COMP0 - GPT0_COMP4)                                                                                                                                                                                                                                                                                                                        | 1-255<br>1-255<br>1-256<br>1-256<br>1-257<br>1-257<br>1-258<br>1-259<br>1-260<br>1-261                                                                                           |

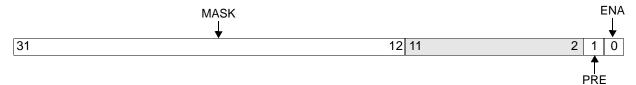

| Chapter 12. General Purpose Timers  GPT Features  GPT Operations  Time Base Counter  Compare Timers  Compare Timers Interrupt  GPT Registers  GPT Time Base Counter Register (GPT0_TBC)  GPT Interrupt Mask Register (GPT0_IM)  GPT Interrupt Status Register (GPT0_ISS and GPT0_ISC)  GPT Interrupt Enable Register (GPT0_IE)  GPT Compare Timer Registers (GPT0_COMP0 - GPT0_COMP4)  GPT Compare Mask Registers (GPT0_MASK0 - GPT0_MASK4)  Chapter 13. Debugging                                                                                                                                                                                                                                           | 1-255<br>1-255<br>1-256<br>1-256<br>1-257<br>1-257<br>1-258<br>1-259<br>1-260<br>1-261<br>1-261                                                                                  |

| Chapter 12. General Purpose Timers  GPT Features  GPT Operations  Time Base Counter  Compare Timers  Compare Timers Interrupt  GPT Registers  GPT Time Base Counter Register (GPT0_TBC)  GPT Interrupt Mask Register (GPT0_IM)  GPT Interrupt Status Register (GPT0_ISS and GPT0_ISC)  GPT Interrupt Enable Register (GPT0_IE)  GPT Compare Timer Registers (GPT0_COMP0 - GPT0_COMP4)  GPT Compare Mask Registers (GPT0_MASK0 - GPT0_MASK4)  Chapter 13. Debugging  Development Tool Support                                                                                                                                                                                                                 | 1-255<br>1-255<br>1-256<br>1-256<br>1-257<br>1-257<br>1-258<br>1-259<br>1-260<br>1-261<br>1-261<br>2-262                                                                         |

| Chapter 12. General Purpose Timers  GPT Features  GPT Operations  Time Base Counter  Compare Timers  Compare Timers Interrupt  GPT Registers  GPT Time Base Counter Register (GPT0_TBC)  GPT Interrupt Mask Register (GPT0_IM)  GPT Interrupt Status Register (GPT0_ISS and GPT0_ISC)  GPT Interrupt Enable Register (GPT0_IE)  GPT Compare Timer Registers (GPT0_COMP0 - GPT0_COMP4)  GPT Compare Mask Registers (GPT0_MASK0 - GPT0_MASK4)  Chapter 13. Debugging  Development Tool Support  Debug Interfaces                                                                                                                                                                                               | 1-255<br>1-255<br>1-256<br>1-256<br>1-257<br>1-257<br>1-258<br>1-259<br>1-260<br>1-261<br>1-261<br>2-262<br>2-262                                                                |

| Chapter 12. General Purpose Timers  GPT Features  GPT Operations  Time Base Counter  Compare Timers  Compare Timers Interrupt  GPT Registers  GPT Time Base Counter Register (GPT0_TBC)  GPT Interrupt Mask Register (GPT0_IM)  GPT Interrupt Status Register (GPT0_ISS and GPT0_ISC)  GPT Interrupt Enable Register (GPT0_IE)  GPT Compare Timer Registers (GPT0_COMP0 - GPT0_COMP4)  GPT Compare Mask Registers (GPT0_MASK0 - GPT0_MASK4)  Chapter 13. Debugging  Development Tool Support  Debug Interfaces  IEEE 1149.1 Test Access Port (JTAG Debug Port)                                                                                                                                               | 1-255<br>1-255<br>1-256<br>1-256<br>1-257<br>1-257<br>1-258<br>1-259<br>1-260<br>1-261<br>1-261<br>2-262<br>2-262<br>2-262                                                       |

| Chapter 12. General Purpose Timers  GPT Features  GPT Operations  Time Base Counter  Compare Timers  Compare Timers Interrupt  GPT Registers  GPT Time Base Counter Register (GPT0_TBC)  GPT Interrupt Mask Register (GPT0_IM)  GPT Interrupt Status Register (GPT0_ISS and GPT0_ISC)  GPT Interrupt Enable Register (GPT0_IE)  GPT Compare Timer Registers (GPT0_COMP0 - GPT0_COMP4)  GPT Compare Mask Registers (GPT0_MASK0 - GPT0_MASK4)  Chapter 13. Debugging  Development Tool Support  Debug Interfaces  IEEE 1149.1 Test Access Port (JTAG Debug Port)  JTAG Connector                                                                                                                               | 1-255<br>1-255<br>1-256<br>1-256<br>1-257<br>1-257<br>1-258<br>1-259<br>1-260<br>1-261<br>1-261<br>2-262<br>2-262<br>2-262<br>2-262                                              |

| Chapter 12. General Purpose Timers  GPT Features  GPT Operations  Time Base Counter  Compare Timers  Compare Timers Interrupt  GPT Registers  GPT Time Base Counter Register (GPT0_TBC)  GPT Interrupt Mask Register (GPT0_IM)  GPT Interrupt Status Register (GPT0_ISS and GPT0_ISC)  GPT Interrupt Enable Register (GPT0_IE)  GPT Compare Timer Registers (GPT0_COMP0 - GPT0_COMP4)  GPT Compare Mask Registers (GPT0_MASK0 - GPT0_MASK4)  Chapter 13. Debugging  Development Tool Support  Debug Interfaces  IEEE 1149.1 Test Access Port (JTAG Debug Port)  JTAG Connector  JTAG Instructions                                                                                                            | 1-255<br>1-255<br>1-256<br>1-256<br>1-257<br>1-257<br>1-258<br>1-260<br>1-261<br>1-261<br>2-262<br>2-262<br>2-262<br>2-263<br>2-263                                              |

| Chapter 12. General Purpose Timers  GPT Features  GPT Operations  Time Base Counter  Compare Timers  Compare Timers Interrupt  GPT Registers  GPT Time Base Counter Register (GPT0_TBC)  GPT Interrupt Mask Register (GPT0_IM)  GPT Interrupt Status Register (GPT0_ISS and GPT0_ISC)  GPT Interrupt Enable Register (GPT0_IE)  GPT Compare Timer Registers (GPT0_COMP0 - GPT0_COMP4)  GPT Compare Mask Registers (GPT0_MASK0 - GPT0_MASK4)  Chapter 13. Debugging  Development Tool Support  Debug Interfaces  IEEE 1149.1 Test Access Port (JTAG Debug Port)  JTAG Connector  JTAG Instructions  JTAG Boundary Scan                                                                                        | 1-255<br>1-255<br>1-256<br>1-256<br>1-257<br>1-257<br>1-258<br>1-259<br>1-261<br>1-261<br>1-261<br>2-262<br>2-262<br>2-262<br>2-263<br>2-263<br>2-263                            |

| Chapter 12. General Purpose Timers  GPT Features  GPT Operations  Time Base Counter  Compare Timers  Compare Timers Interrupt  GPT Registers  GPT Time Base Counter Register (GPT0_TBC)  GPT Interrupt Mask Register (GPT0_IM)  GPT Interrupt Status Register (GPT0_IS and GPT0_ISC)  GPT Interrupt Enable Register (GPT0_IE)  GPT Compare Timer Registers (GPT0_IE)  GPT Compare Timer Registers (GPT0_COMP0 - GPT0_COMP4)  GPT Compare Mask Registers (GPT0_MASK0 - GPT0_MASK4)  Chapter 13. Debugging  Development Tool Support  Debug Interfaces  IEEE 1149.1 Test Access Port (JTAG Debug Port)  JTAG Connector  JTAG Instructions  JTAG Boundary Scan  JTAG Implementation                             | 1-255<br>1-255<br>1-256<br>1-256<br>1-257<br>1-257<br>1-258<br>1-259<br>1-260<br>1-261<br>1-261<br>2-262<br>2-262<br>2-262<br>2-263<br>2-263<br>2-263                            |

| Chapter 12. General Purpose Timers  GPT Features  GPT Operations  Time Base Counter  Compare Timers  Compare Timers Interrupt  GPT Registers  GPT Interrupt Mask Register (GPT0_TBC)  GPT Interrupt Status Register (GPT0_IM)  GPT Interrupt Status Register (GPT0_IE)  GPT Compare Timer Register (GPT0_IE)  GPT Compare Timer Registers (GPT0_COMP0 - GPT0_COMP4)  GPT Compare Mask Registers (GPT0_MASK0 - GPT0_MASK4)  Chapter 13. Debugging  Development Tool Support  Debug Interfaces  IEEE 1149.1 Test Access Port (JTAG Debug Port)  JTAG Connector  JTAG Instructions  JTAG Boundary Scan  JTAG Implementation  JTAG Implementation  JTAG Implementation  JTAG Implementation  JTAG Inglementation | 1-255<br>1-255<br>1-256<br>1-256<br>1-257<br>1-257<br>1-258<br>1-259<br>1-260<br>1-261<br>1-261<br>2-262<br>2-262<br>2-262<br>2-262<br>2-263<br>2-263<br>2-263<br>2-264          |

| Chapter 12. General Purpose Timers  GPT Features  GPT Operations  Time Base Counter  Compare Timers  Compare Timers Interrupt  GPT Registers  GPT Time Base Counter Register (GPT0_TBC)  GPT Interrupt Mask Register (GPT0_IM)  GPT Interrupt Status Register (GPT0_ISS and GPT0_ISC)  GPT Interrupt Enable Register (GPT0_IE)  GPT Compare Timer Registers (GPT0_COMP0 - GPT0_COMP4)  GPT Compare Mask Registers (GPT0_MASK0 - GPT0_MASK4)  Chapter 13. Debugging  Development Tool Support  Debug Interfaces  IEEE 1149.1 Test Access Port (JTAG Debug Port)  JTAG Connector  JTAG Boundary Scan  JTAG Implementation  JTAG In Register (CPC0_JTAGID)  Trace Port                                          | 1-255<br>1-255<br>1-256<br>1-256<br>1-257<br>1-257<br>1-258<br>1-259<br>1-260<br>1-261<br>1-261<br>2-262<br>2-262<br>2-262<br>2-262<br>2-263<br>2-263<br>2-263<br>2-264<br>2-264 |

| Chapter 12. General Purpose Timers  GPT Features  GPT Operations  Time Base Counter  Compare Timers Interrupt  GPT Registers  GPT Time Base Counter Register (GPT0_TBC)  GPT Interrupt Mask Register (GPT0_IM)  GPT Interrupt Status Register (GPT0_ISS and GPT0_ISC)  GPT Interrupt Enable Register (GPT0_IE)  GPT Compare Timer Registers (GPT0_COMP0 - GPT0_COMP4)  GPT Compare Mask Registers (GPT0_MASK0 - GPT0_MASK4)  Chapter 13. Debugging  Development Tool Support  Debug Interfaces  IEEE 1149.1 Test Access Port (JTAG Debug Port)  JTAG Connector  JTAG Instructions  JTAG Instructions  JTAG Inplementation  JTAG ID Register (CPC0_JTAGID)  Trace Port  Debug Modes                           | 1-255<br>1-255<br>1-256<br>1-256<br>1-257<br>1-257<br>1-259<br>1-260<br>1-261<br>1-261<br>2-262<br>2-262<br>2-262<br>2-262<br>2-263<br>2-263<br>2-263<br>2-264<br>2-264<br>2-264 |

| Chapter 12. General Purpose Timers  GPT Features  GPT Operations  Time Base Counter  Compare Timers  Compare Timers Interrupt  GPT Registers  GPT Time Base Counter Register (GPT0_TBC)  GPT Interrupt Mask Register (GPT0_IM)  GPT Interrupt Status Register (GPT0_ISS and GPT0_ISC)  GPT Interrupt Enable Register (GPT0_IE)  GPT Compare Timer Registers (GPT0_COMP0 - GPT0_COMP4)  GPT Compare Mask Registers (GPT0_MASK0 - GPT0_MASK4)  Chapter 13. Debugging  Development Tool Support  Debug Interfaces  IEEE 1149.1 Test Access Port (JTAG Debug Port)  JTAG Connector  JTAG Boundary Scan  JTAG Implementation  JTAG In Register (CPC0_JTAGID)  Trace Port                                          | 1-255 1-255 1-256 1-256 1-257 1-257 1-258 1-259 1-260 1-261 1-261 2-262 2-262 2-262 2-262 2-262 2-263 2-263 2-264 2-264 2-265 2-265                                              |

| Chapter 12. General Purpose Timers  GPT Features GPT Operations Time Base Counter Compare Timers Compare Timers Interrupt GPT Registers GPT Time Base Counter Register (GPT0_TBC) GPT Interrupt Mask Register (GPT0_IM) GPT Interrupt Status Register (GPT0_ISS and GPT0_ISC) GPT Interrupt Enable Register (GPT0_IE) GPT Compare Timer Registers (GPT0_COMP0 - GPT0_COMP4) GPT Compare Mask Registers (GPT0_MASK0 - GPT0_MASK4)  Chapter 13. Debugging  Development Tool Support Debug Interfaces IEEE 1149.1 Test Access Port (JTAG Debug Port) JTAG Connector JTAG Instructions JTAG Boundary Scan JTAG Boundary Scan JTAG In Register (CPC0_JTAGID) Trace Port Debug Modes Internal Debug Mode           | 1-255 1-255 1-256 1-256 1-257 1-257 1-258 1-259 1-260 1-261 1-261 2-262 2-262 2-262 2-262 2-263 2-263 2-264 2-264 2-264 2-265 2-265                                              |

| Real-time Trace Debug Mode                              | 2-266 |

|---------------------------------------------------------|-------|

| Processor Control                                       | 2-267 |

| Processor Status                                        |       |

| Debug Registers                                         | 2-267 |

| Debug Control Registers                                 | 2-268 |

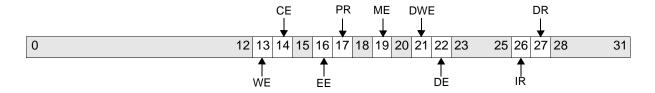

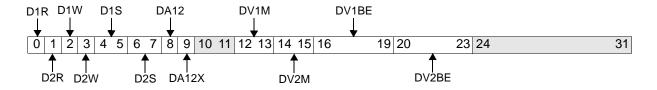

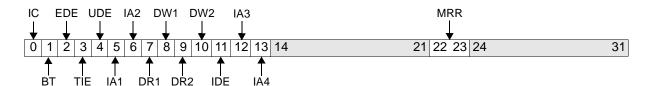

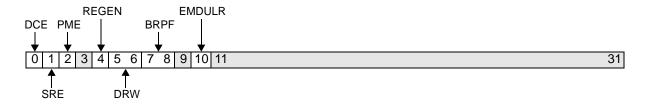

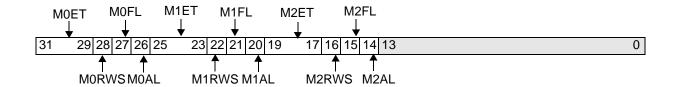

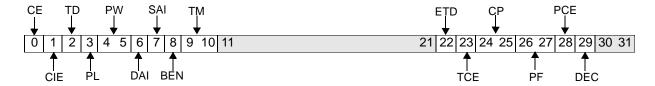

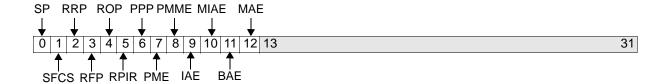

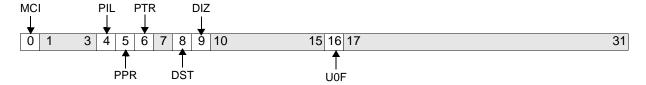

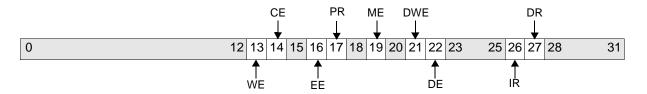

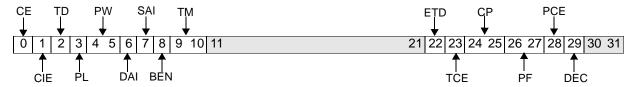

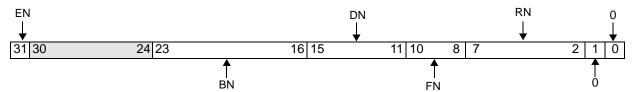

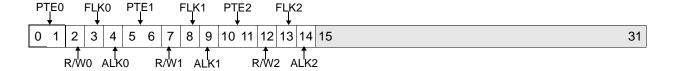

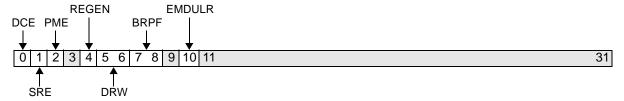

| Debug Control Register 0 (DBCR0)                        | 2-268 |

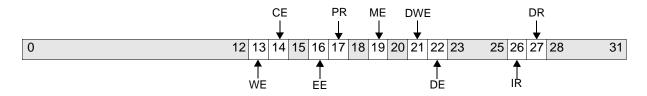

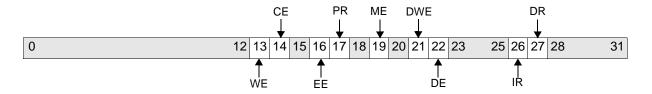

| Debug Control Register1 (DBCR1)                         | 2-269 |

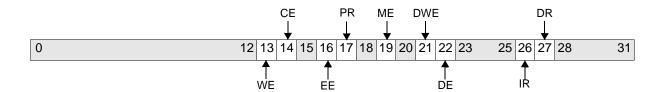

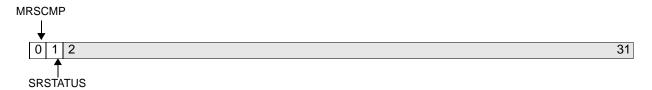

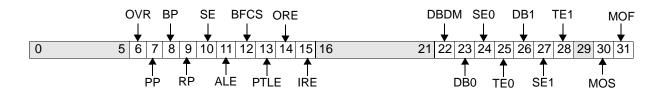

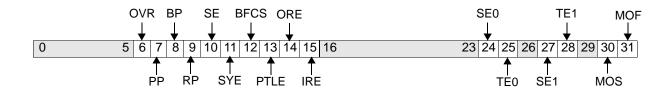

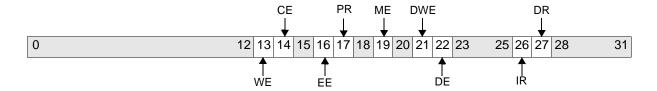

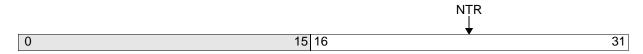

| Debug Status Register (DBSR)                            | 2-271 |

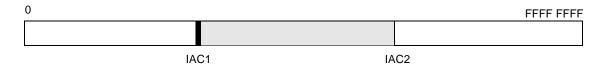

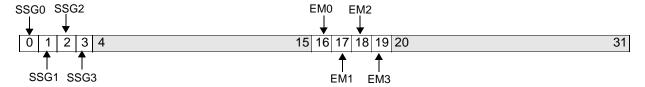

| Instruction Address Compare Registers (IAC1-IAC4)       | 2-273 |

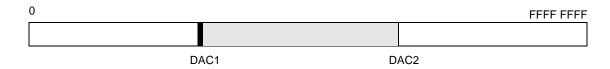

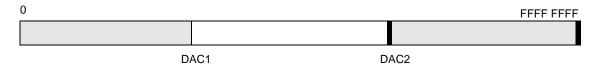

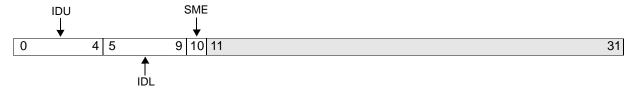

| Data Address Compare Registers (DAC1-DAC2)              | 2-273 |

| Data Value Compare Registers (DVC1-DVC2)                | 2-274 |

| Debug Events                                            |       |

| Instruction Complete Debug Event                        | 2-275 |

| Branch Taken Debug Event                                | 2-275 |

| Exception Taken Debug Event                             | 2-275 |

| Trap Taken Debug Event                                  | 2-275 |

| Unconditional Debug Event                               | 2-275 |

| IAC Debug Event                                         | 2-276 |

| IAC Exact Address Compare                               | 2-276 |

| IAC Range Address Compare                               | 2-276 |

| DAC Debug Event                                         | 2-277 |

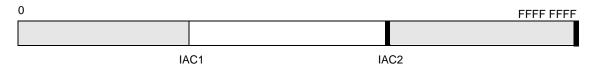

| DAC Exact Address Compare                               | 2-277 |

| DAC Range Address Compare                               | 2-278 |

| DAC Applied to Cache Instructions                       | 2-279 |

| DAC Applied to String Instructions                      | 2-280 |

| Data Value Compare Debug Event                          | 2-280 |

| Imprecise Debug Event                                   | 2-282 |

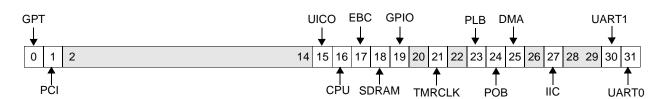

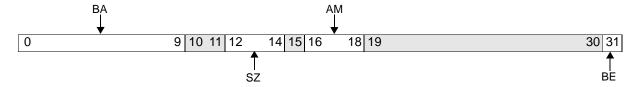

| Chapter 14. Clock and Power Management                  | 3-284 |

| -                                                       |       |

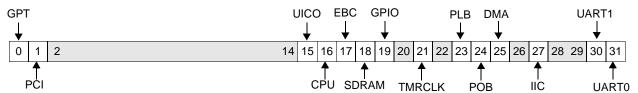

| CPM Enable Register (CRC) ER)                           |       |

| CPM Force Register (CPC0_ER)                            |       |

| CPM Status Posister (CPC0_FR)                           |       |

| CPM Status Register (CPC0_SR)                           |       |

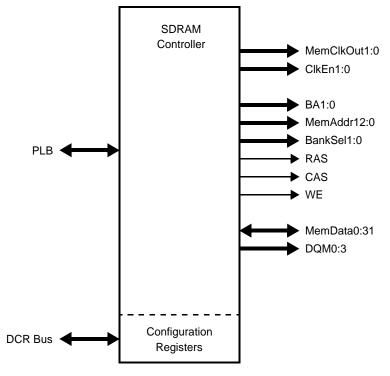

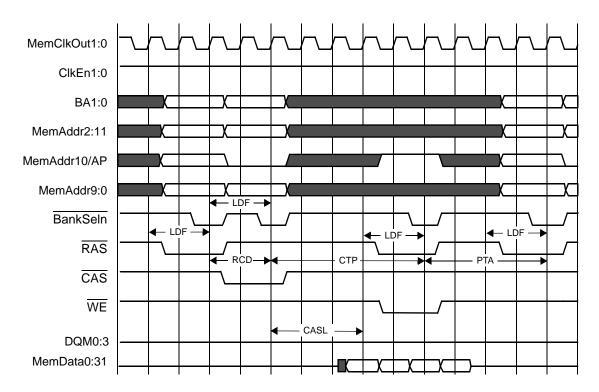

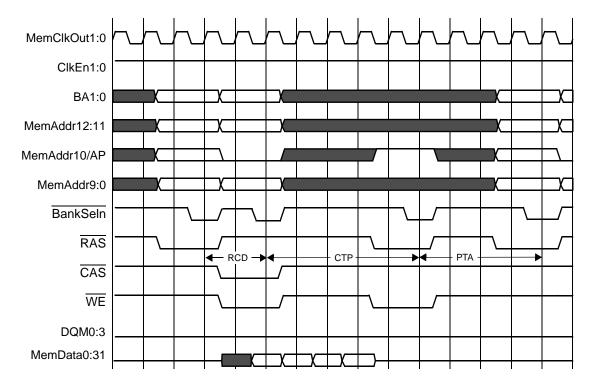

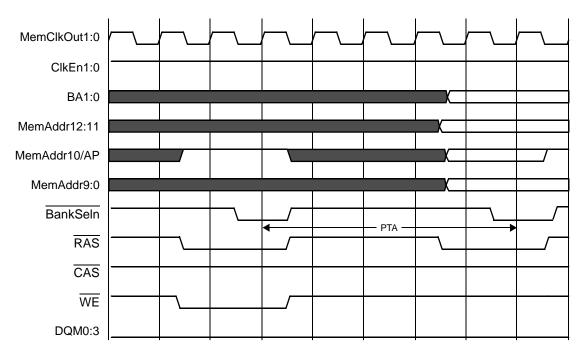

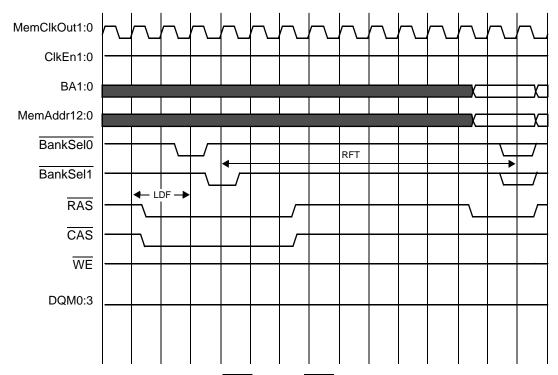

| Chapter 15. SDRAM Controller                            | 5-290 |

| Interface Signals                                       | 5-290 |

| Accessing SDRAM Registers                               |       |

| SDRAM Controller Configuration and Status               |       |

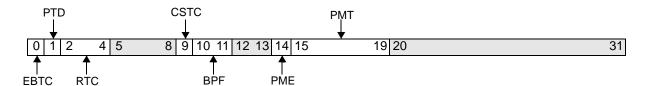

| Memory Controller Configuration Register (SDRAM0_CFG)   |       |

| Memory Controller Status (SDRAM0_STATUS)                |       |

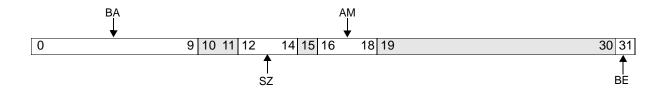

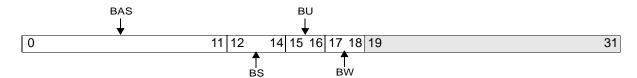

| Memory Bank 0–1 Configuration (SDRAM0_B0CR-SDRAM0_B1CR) |       |

| Page Management                                         |       |

| Logical Address to Memory Address Mapping               |       |

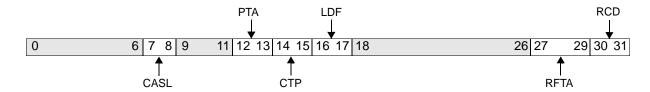

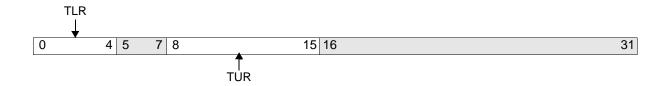

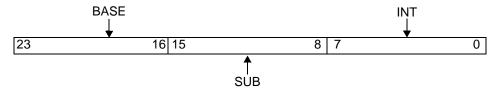

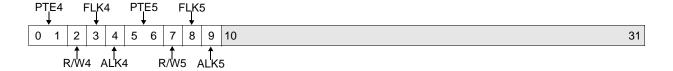

| SDRAM Timing Register (SDRAM0_TR)                       |       |

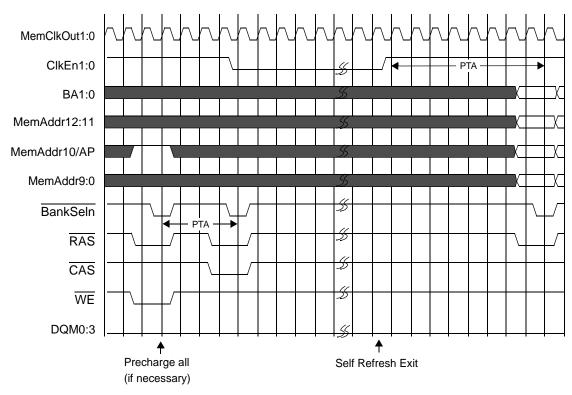

| Selected Timing Diagrams                                |       |

| Auto (CAS Before RAS) Refresh                           |       |

| Refresh Timer Register (SDRAM0_RTR)                     |       |

| Self-Refresh                                            |       |

| Power Management                                        |       |

| Sleep Mode Entry                                        |       |

| Power Management Idle Timer (SDRAM0_PMIT)               |       |

| Sleep Mode Exit                                         |       |

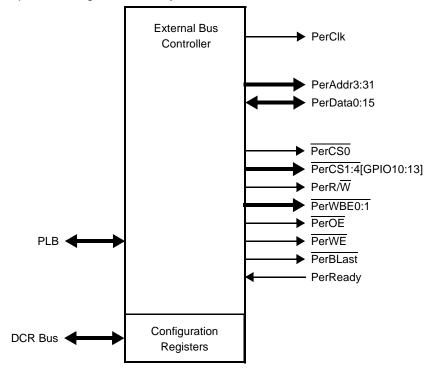

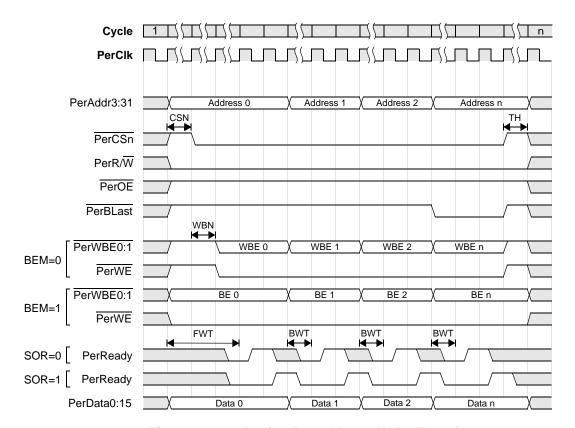

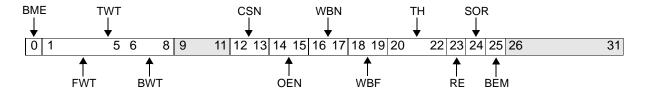

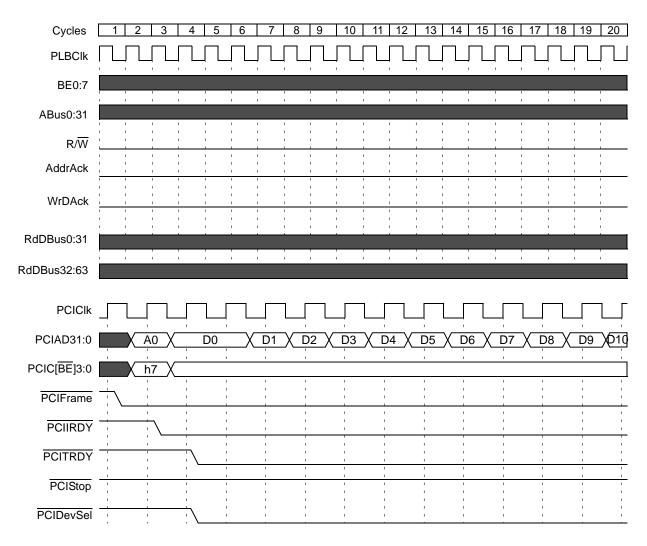

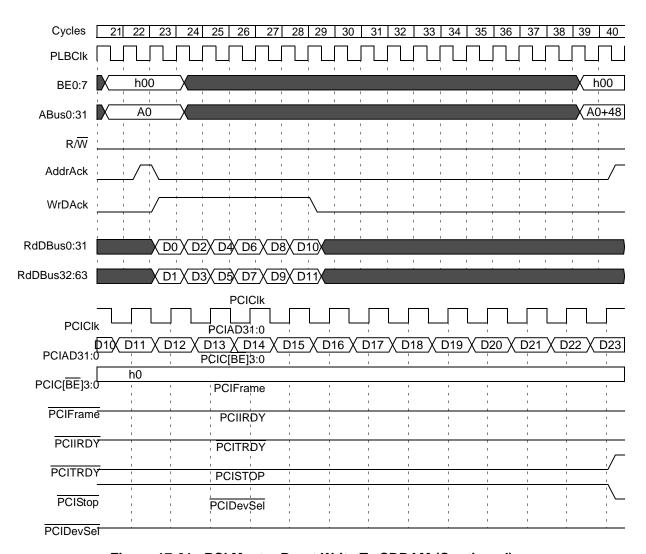

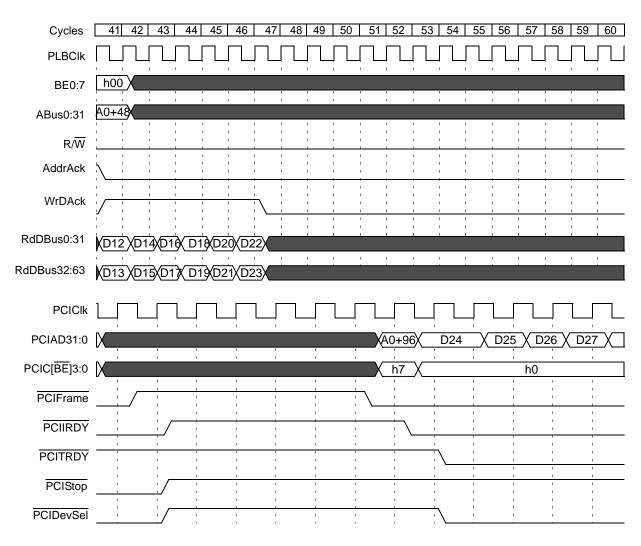

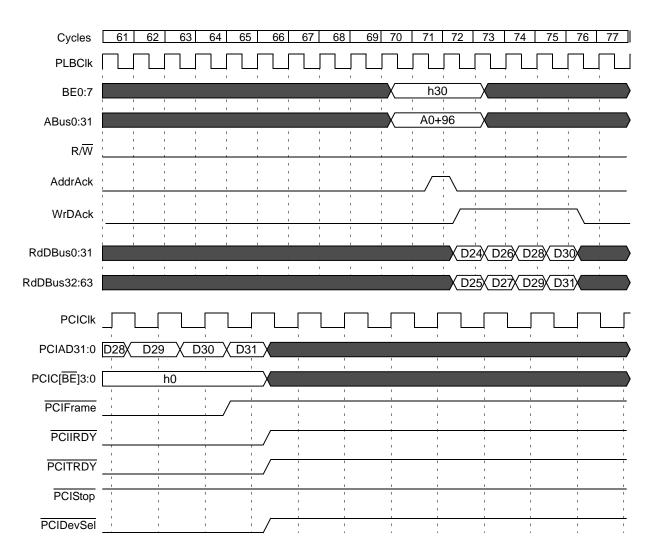

| Chapter 16. External Bus Controller                     | 6-306 |

| Interface Signals                                       | 6-306 |

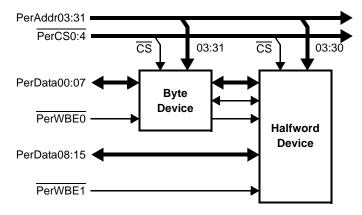

| Interfacing to Byte and Halfword Devices                |       |

| Driver Enables                                          |       |

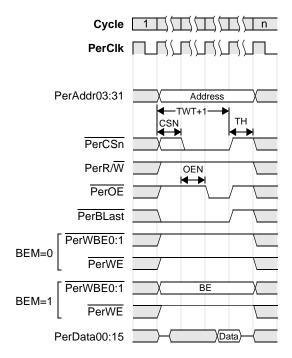

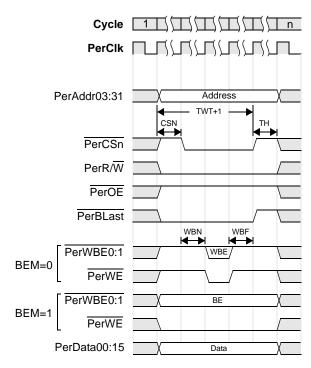

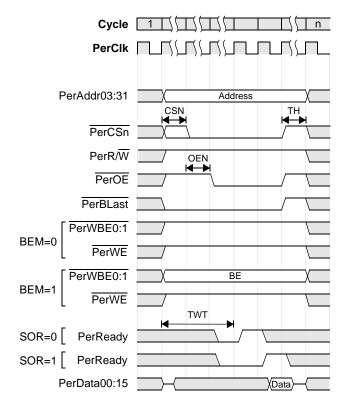

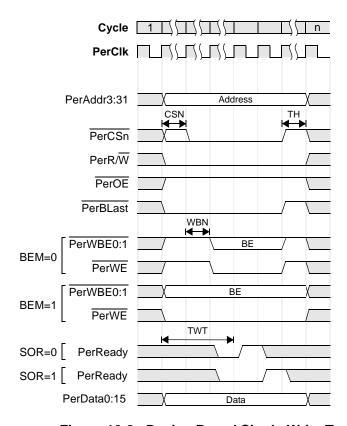

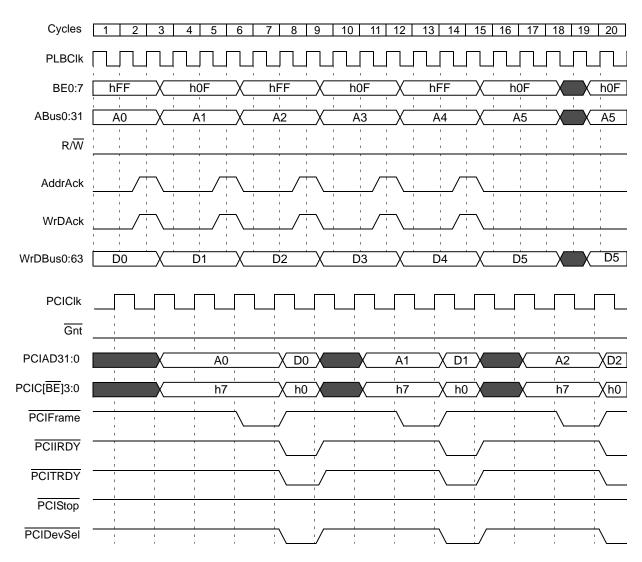

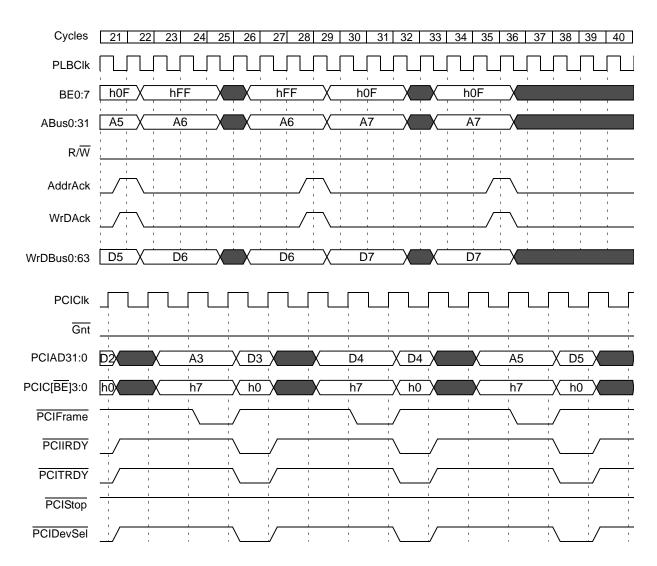

| Non-Burst Peripheral Bus Transactions                   |       |

|                                                         |       |

| Single Read Transfer                                |         |

|-----------------------------------------------------|---------|

| Single Write Transfer                               |         |

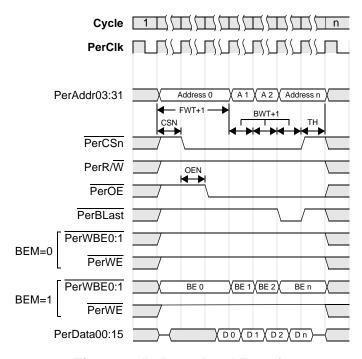

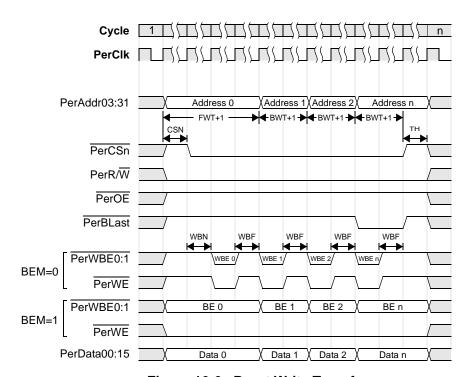

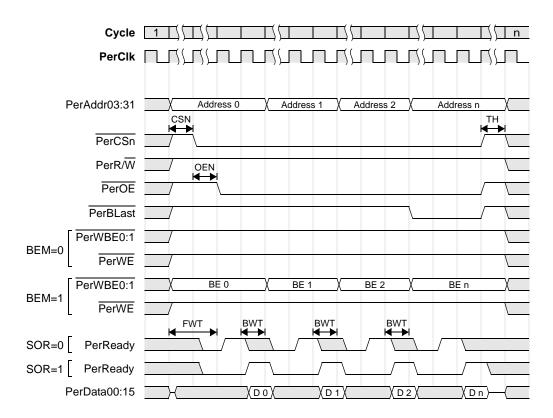

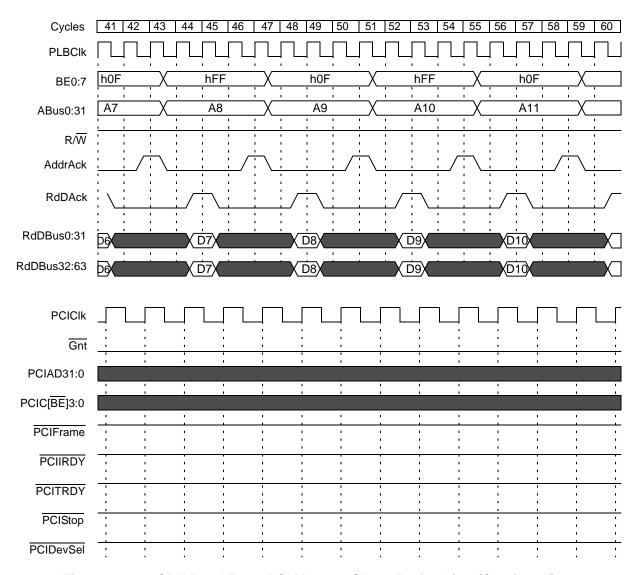

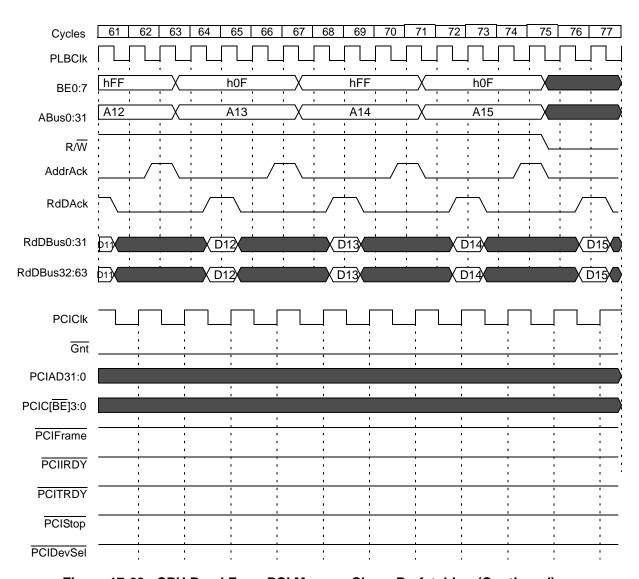

| Burst Transactions                                  | 6-312   |

| Burst Read Transfer                                 | 6-313   |

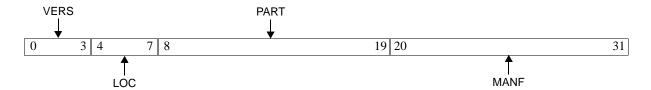

| Burst Write Transfer                                |         |